Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Obsolete                                                                      |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 23                                                                            |

| Program Memory Size        | 8KB (2.75K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 1K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5V                                                                       |

| Data Converters            | A/D 19x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-VQFN Exposed Pad                                                           |

| Supplier Device Package    | 28-QFN (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fv08km102-i-ml |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| PINOUT DESCRIPTION (CONTINUED) | FV | Pin Number | 20-Pin 28-Pin 28-Pin 28-Pin 28-Pin 28-Pin 28-Pin 28-Din 28 | 12 17 14 44 48 I/O 12C MSSP1 I <sup>2</sup> C Clock | 13 18 15 1 1 1/0 12C MSSP1 1 <sup>2</sup> C Data | - 7 4 24 26 I/O I2C MSSP2 I <sup>2</sup> C Clock | - 6 3 23 25 I/O I2C MSSP2 I <sup>2</sup> C Data | 10 12 9 34 37 I ST Secondary Clock Digital Input | 9 11 8 33 36 I ANA Secondary Oscillator Input | 10 12 9 34 37 I ANA Secondary Oscillator Output | 13 18 15 1 1 1 ST Timer1 Digital Input Cock | 18 26 23 15 16 1 ST MCCP/SCCP Time Base Clock Input A | 6 6 3 23 25 I ST MCCP/SCCP Time Base Clock Input B | 12 17 14 44 48 I ST UART1 Clear-To-Send Input | 13 18 15 1 1 0 — UART1 Request-To-Send Output | 13 18 15 1 1 0 — UART1 16x Baud Rate Clock Output | 6 6 3 2 2 I ST UART1 Receive | 11 16 13 3 3 0 — UART1 Transmit | 12 9 34 37 1 ST UART2 Clear-To-Send Input | 11 8 33 36 0 UART2 Request-To-Send Output | 13 18 15 1 1 0 — UART2 16x Baud Rate Clock Output | - 5 2 2 24 I ST UART2 Receive | 4 1 21 23 0 - UART2 Transmit | 4 4 1 21 23 I ANA Ultra Low-Power Wake-up Input | 14 20 17 7 P – Regulator External Filter Capacitor Connection | 20 28 25 17,28,28 18,30,30 P — Device Positive Supply Voltage | 14 20 17 7 P – Microcontroller Core Supply Voltage | 1 1 26 18 19 P — High-Voltage Programming Pin | 2 2 2 27 19 21 I ANA A/D Reference Voltage Positive Input | 3 3 3 28 20 22 I ANA A/D Reference Voltage Negative Input | 19 27 24 16,29,29 17,31,31 P — Device Ground Return Voltage | ANA = Analog level input/outbut, ST = Schmitt Trigger input buffer, I <sup>2</sup> C <sup>TM</sup> = I <sup>2</sup> C/SMBus input buffer |

|--------------------------------|----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--------------------------------------------------|--------------------------------------------------|-------------------------------------------------|--------------------------------------------------|-----------------------------------------------|-------------------------------------------------|---------------------------------------------|-------------------------------------------------------|----------------------------------------------------|-----------------------------------------------|-----------------------------------------------|---------------------------------------------------|------------------------------|---------------------------------|-------------------------------------------|-------------------------------------------|---------------------------------------------------|-------------------------------|------------------------------|-------------------------------------------------|---------------------------------------------------------------|---------------------------------------------------------------|----------------------------------------------------|-----------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| UT DESC                        |    |            | 48-Pin PD<br>JQFN SSC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 48 1                                                | 1                                                | 26 –                                             | - 25                                            | 37 1                                             |                                               | 37 1                                            | 1                                           |                                                       | 25 6                                               | 48 1                                          | 1                                             | 1                                                 | 2 6                          |                                 | 37 –                                      | 36 –                                      |                                                   | 24 –                          | - 23                         | 23 23                                           | -                                                             | 18,30,30 2                                                    | -                                                  | 19 1                                          | 21 21                                                     | 22                                                        | 7,31,31 1                                                   | gger input bu                                                                                                                            |

|                                |    | -          | 44-Pin<br>QFN/<br>LU<br>TQFP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 44                                                  | -                                                | 24                                               | 23                                              | 34                                               | 33                                            | 34                                              | 1                                           | 15                                                    | 23                                                 | 44                                            | 1                                             | 1                                                 | 2                            | 3                               | 34                                        | 33                                        | -                                                 | 22                            | 21                           | 21                                              |                                                               | 17,28,28 18                                                   |                                                    | 18                                            | 19                                                        | 20                                                        | 16,29,29 17                                                 | = Schmitt Tri                                                                                                                            |

| 204 FAN                        | н  | Pin Number | 28-Pin<br>QFN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 14                                                  | 15                                               | 4                                                | 3                                               | 6                                                | 8                                             | 6                                               | 15                                          | 23                                                    | 3                                                  | 14                                            | 15                                            | 15                                                | 3                            | 13                              | 6                                         | 8                                         | 15                                                | 2                             | 1                            | 1                                               |                                                               | 25                                                            |                                                    | 26                                            | 27                                                        | 28                                                        | 24                                                          | output, ST                                                                                                                               |

| PIC24FV16KM204 FAMILY          |    | ш          | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 17                                                  | 18                                               | 7                                                | 9                                               | 12                                               | 11                                            | 12                                              | 18                                          | 26                                                    | 6                                                  | 17                                            | 18                                            | 18                                                | 6                            | 16                              | 12                                        | 11                                        | 18                                                | 5                             | 4                            | 4                                               |                                                               | 28                                                            |                                                    | 1                                             | 2                                                         | 3                                                         | 27                                                          | evel input/                                                                                                                              |

| PIC24F                         |    |            | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 12                                                  | 13                                               |                                                  | Ι                                               | 10                                               | 6                                             | 10                                              | 13                                          | 18                                                    | 9                                                  | 12                                            | 13                                            | 13                                                | 9                            | 11                              |                                           | I                                         | 13                                                |                               |                              | 4                                               |                                                               | 20                                                            |                                                    | 1                                             | 2                                                         | 3                                                         | 19                                                          | = Analog Iu                                                                                                                              |

| TABLE 1-5:                     |    |            | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SCL1                                                | SDA1                                             | SCL2                                             | SDA2                                            | SCLKI                                            | SOSCI                                         | sosco                                           | T1CK                                        | TCKIA                                                 | TCKIB                                              | UICTS                                         | UIRTS                                         | U1BCLK                                            | U1RX                         | U1TX                            | U2CTS                                     | UZRTS                                     | U2BCLK                                            | U2RX                          | U2TX                         | ULPWU                                           | VCAP                                                          | VDD                                                           | VDDCORE                                            | νрр                                           | VREF+                                                     | VREF-                                                     | Vss                                                         | Leaend: ANA :                                                                                                                            |

# 0 Ò ( 5

### PIC24FV16KM204 FAMILY

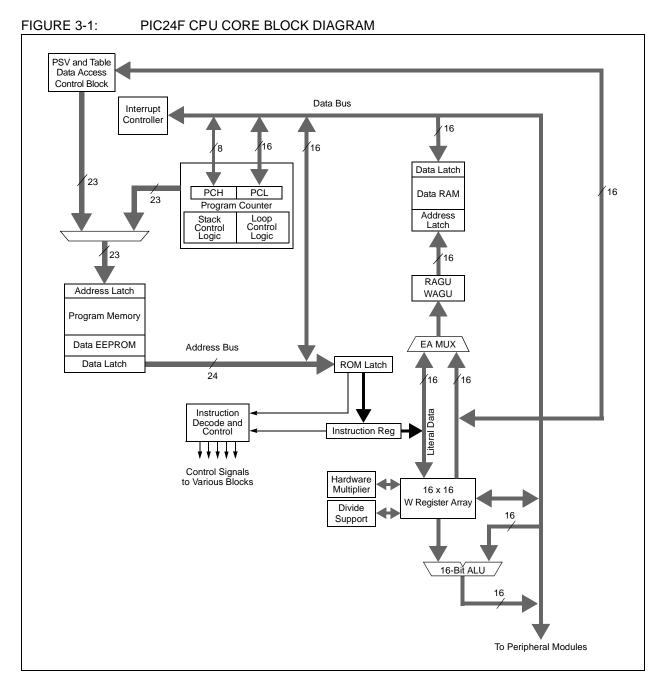

| Register(s) Name | Description                                    |

|------------------|------------------------------------------------|

| W0 through W15   | Working Register Array                         |

| PC               | 23-Bit Program Counter                         |

| SR               | ALU STATUS Register                            |

| SPLIM            | Stack Pointer Limit Value Register             |

| TBLPAG           | Table Memory Page Address Register             |

| PSVPAG           | Program Space Visibility Page Address Register |

| RCOUNT           | Repeat Loop Counter Register                   |

| CORCON           | CPU Control Register                           |

#### TABLE 4-10: MCCP3 REGISTER MAP

| File Name                | Addr. | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11  | Bit 10  | Bit 9   | Bit 8       | Bit 7         | Bit 6                                      | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |  |  |  |  |  |

|--------------------------|-------|---------|--------|---------|--------|---------|---------|---------|-------------|---------------|--------------------------------------------|---------|---------|---------|---------|---------|---------|---------------|--|--|--|--|--|

| CCP3CON1L <sup>(1)</sup> | 188h  | CCPON   |        | CCPSIDL | r      | TMRSYNC | CLKSEL2 | CLKSEL1 | CLKSEL0     | TMRPS1        | TMRPS0                                     | T32     | CCSEL   | MOD3    | MOD2    | MOD1    | MOD0    | 0000          |  |  |  |  |  |

| CCP3CON1H <sup>(1)</sup> | 18Ah  | OPSSRC  | RTRGEN | _       | _      | IOPS3   | IOPS2   | IOPS1   | IOPS0       | TRIGEN        | ONESHOT                                    | ALTSYNC | SYNC4   | SYNC3   | SYNC2   | SYNC1   | SYNC0   | 0000          |  |  |  |  |  |

| CCP3CON2L <sup>(1)</sup> | 18Ch  | PWMRSEN | ASDGM  | _       | SSDG   | _       | _       | _       | _           | ASDG7         | ASDG6                                      | ASDG5   | ASDG4   | ASDG3   | ASDG2   | ASDG1   | ASDG0   | 0000          |  |  |  |  |  |

| CCP3CON2H <sup>(1)</sup> | 18Eh  | OENSYNC | _      | OCFEN   | OCEEN  | OCDEN   | OCCEN   | OCBEN   | OCAEN       | ICGSM1        | ICGSM0                                     | _       | AUXOUT1 | AUXOUT0 | ICS2    | ICS1    | ICS0    | 0100          |  |  |  |  |  |

| CCP3CON3L <sup>(1)</sup> | 190h  | _       | _      |         | _      |         |         | _       | —           |               |                                            | DT5     | DT4     | DT3     | DT2     | DT1     | DT0     | 0000          |  |  |  |  |  |

| CCP3CON3H <sup>(1)</sup> | 192h  | OETRIG  | OSCNT2 | OSCNT1  | OSCNT0 |         | OUTM2   | OUTM1   | OUTM0       |               |                                            | POLACE  | POLBDF  | PSSACE1 | PSSACE0 | PSSBDF1 | PSSBDF0 | 0000          |  |  |  |  |  |

| CCP3STAT <sup>(1)</sup>  | 194h  | _       | _      |         | _      |         |         | _       | —           | CCPTRIG       | TRSET                                      | TRCLR   | ASEVT   | SCEVT   | ICDIS   | ICOV    | ICBNE   | 0000          |  |  |  |  |  |

| CCP3TMRL <sup>(1)</sup>  | 198h  |         |        |         |        |         |         | MCCF    | P3 Time Bas | se Register   | Low Word                                   |         |         |         |         |         |         | 0000          |  |  |  |  |  |

| CCP3TMRH <sup>(1)</sup>  | 19Ah  |         |        |         |        |         |         | MCCF    | 23 Time Bas | se Register   | High Word                                  |         |         |         |         |         |         | 0000          |  |  |  |  |  |

| CCP3PRL <sup>(1)</sup>   | 19Ch  |         |        |         |        |         |         | MCCP3 1 | Time Base F | Period Regis  | ster Low Wor                               | d       |         |         |         |         |         | FFFF          |  |  |  |  |  |

| CCP3PRH <sup>(1)</sup>   | 19Eh  |         |        |         |        |         |         | МССРЗ Т | ïme Base P  | eriod Regis   | ter High Wor                               | d       |         |         |         |         |         | FFFF          |  |  |  |  |  |

| CCP3RAL <sup>(1)</sup>   | 1A0h  |         |        |         |        |         |         | Οι      | utput Compa | are 3 Data V  | Vord A                                     |         |         |         |         |         |         | 0000          |  |  |  |  |  |

| CCP3RBL <sup>(1)</sup>   | 1A4h  |         |        |         |        |         |         | Ou      | utput Compa | are 3 Data V  | Vord B                                     |         |         |         |         |         |         | 0000          |  |  |  |  |  |

| CCP3BUFL <sup>(1)</sup>  | 1A8h  |         |        |         |        |         |         | Input   | Capture 3 [ | Data Buffer I | Low Word                                   |         |         |         |         |         |         | 0000          |  |  |  |  |  |

| CCP3BUFH <sup>(1)</sup>  | 1AAh  |         |        |         |        |         |         | Input   | Capture 3 D | Data Buffer H | Input Capture 3 Data Buffer High Word 0000 |         |         |         |         |         |         |               |  |  |  |  |  |

$\label{eq:legend: Legend: Legend: u = unknown, u = unkn$

Note 1: These registers are available only on PIC24F(V)16KM2XX devices.

### TABLE 4-11: SCCP4 REGISTER MAP

| File Name                | Addr. | Bit 15  | Bit 14                                   | Bit 13  | Bit 12 | Bit 11  | Bit 10  | Bit 9     | Bit 8       | Bit 7          | Bit 6       | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1  | Bit 0  | All<br>Resets |

|--------------------------|-------|---------|------------------------------------------|---------|--------|---------|---------|-----------|-------------|----------------|-------------|---------|---------|---------|---------|--------|--------|---------------|

| CCP4CON1L <sup>(1)</sup> | 1ACh  | CCPON   | _                                        | CCPSIDL | r      | TMRSYNC | CLKSEL2 | CLKSEL1   | CLKSEL0     | TMRPS1         | TMRPS0      | T32     | CCSEL   | MOD3    | MOD2    | MOD1   | MOD0   | 0000          |

| CCP4CON1H <sup>(1)</sup> | 1AEh  | OPSSRC  | RTRGEN                                   | _       | _      | IOPS3   | IOPS2   | IOPS1     | IOPS0       | TRIGEN         | ONESHOT     | ALTSYNC | SYNC4   | SYNC3   | SYNC2   | SYNC1  | SYNC0  | 0000          |

| CCP4CON2L <sup>(1)</sup> | 1B0h  | PWMRSEN | ASDGM                                    | _       | SSDG   | _       | _       | _         | _           | ASDG7          | ASDG6       | ASDG5   | ASDG4   | ASDG3   | ASDG2   | ASDG1  | ASDG0  | 0000          |

| CCP4CON2H <sup>(1)</sup> | 1B2h  | OENSYNC | _                                        | _       | _      | _       | _       | _         | OCAEN       | ICGSM1         | ICGSM0      | _       | AUXOUT1 | AUXOUT0 | ICSEL2  | ICSEL1 | ICSEL0 | 0100          |

| CCP4CON3H <sup>(1)</sup> | 1B6h  | OETRIG  | OSCNT2                                   | OSCNT1  | OSCNT0 | _       | _       | _         | _           | _              | _           | POLACE  | _       | PSSACE1 | PSSACE0 | _      | _      | 0000          |

| CCP4STATL <sup>(1)</sup> | 1B8h  | _       | _                                        | _       | _      | _       | _       | _         | _           | CCPTRIG        | TRSET       | TRCLR   | ASEVT   | SCEVT   | ICDIS   | ICOV   | ICBNE  | 0000          |

| CCP4TMRL <sup>(1)</sup>  | 1BCh  |         |                                          |         |        |         |         | SCCP      | 1 Time Base | Register Lo    | w Word      |         |         |         |         |        |        | 0000          |

| CCP4TMRH <sup>(1)</sup>  | 1BEh  |         |                                          |         |        |         |         | SCCP4     | Time Base   | Register Hi    | gh Word     |         |         |         |         |        |        | 0000          |

| CCP4PRL <sup>(1)</sup>   | 1C0h  |         |                                          |         |        |         |         | SCCP4 Ti  | me Base Pe  | riod Registe   | r Low Word  |         |         |         |         |        |        | FFFF          |

| CCP4PRH <sup>(1)</sup>   | 1C2h  |         |                                          |         |        |         |         | SCCP4 Tir | ne Base Pe  | riod Registe   | r High Word |         |         |         |         |        |        | FFFF          |

| CCP4RAL <sup>(1)</sup>   | 1C4h  |         |                                          |         |        |         |         | Out       | put Compa   | re 4 Data Wo   | ord A       |         |         |         |         |        |        | 0000          |

| CCP4RBL <sup>(1)</sup>   | 1C8h  |         |                                          |         |        |         |         | Out       | put Compai  | re 4 Data Wo   | ord B       |         |         |         |         |        |        | 0000          |

| CCP4BUFL <sup>(1)</sup>  | 1CCh  |         | Input Capture 4 Data Buffer Low Word 000 |         |        |         |         |           |             |                |             |         |         |         |         | 0000   |        |               |

| CCP4BUFH <sup>(1)</sup>  | 1CEh  |         |                                          |         |        |         |         | Input C   | apture 4 Da | ata Buffer Hig | gh Word     |         |         |         |         |        |        | 0000          |

PIC24FV16KM204 FAMILY

Legend: x = unknown, u = unchanged, - = unimplemented, q = value depends on condition, r = reserved.

Note 1: These registers are available only on PIC24F(V)16KM2XX devices.

### REGISTER 8-7: IFS2: INTERRUPT FLAG STATUS REGISTER 2

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0, HS | U-0   |

|--------|-----|-----|-----|-----|-----|-----------|-------|

| _      | —   | —   | —   | —   | —   | CCT5IF    |       |

| bit 15 |     |     |     |     |     |           | bit 8 |

|        |     |     |     |     |     |           |       |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| —     | —   |     | —   | —   |     |     | —     |

| bit 7 |     |     |     |     |     |     | bit 0 |

| Legend:           | HS = Hardware Settable bit |                             |                    |

|-------------------|----------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-10 | Unimplemented: Read as '0'                                |

|-----------|-----------------------------------------------------------|

| bit 9     | CCT5IF: Capture/Compare 5 Timer Interrupt Flag Status bit |

|           | 1 = Interrupt request has occurred                        |

|           | 0 = Interrupt request has not occurred                    |

| bit 8-0   | Unimplemented: Read as '0'                                |

### REGISTER 8-8: IFS3: INTERRUPT FLAG STATUS REGISTER 3

| U-0    | R/W-0, HS | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----------|-----|-----|-----|-----|-----|-------|

| —      | RTCIF     | —   | —   | —   | —   | —   | —     |

| bit 15 |           |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0, HS | R/W-0, HS | U-0   |

|-------|-----|-----|-----|-----|-----------|-----------|-------|

| —     | —   | —   | —   | —   | BCL2IF    | SSP2IF    | —     |

| bit 7 |     |     |     |     |           |           | bit 0 |

| Legend:           | HS = Hardware Settable bit |                             |                    |

|-------------------|----------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15   | Unimplemented: Read as '0'                                                                          |

|----------|-----------------------------------------------------------------------------------------------------|

| bit 14   | RTCIF: Real-Time Clock and Calendar Interrupt Flag Status bit                                       |

|          | <ul><li>1 = Interrupt request has occurred</li><li>0 = Interrupt request has not occurred</li></ul> |

| bit 13-3 | Unimplemented: Read as '0'                                                                          |

| bit 2    | BCL2IF: MSSP2 I <sup>2</sup> C <sup>™</sup> Bus Collision Interrupt Flag Status bit                 |

|          | <ul><li>1 = Interrupt request has occurred</li><li>0 = Interrupt request has not occurred</li></ul> |

| bit 1    | SSP2IF: MSSP2 SPI/I <sup>2</sup> C Event Interrupt Flag Status bit                                  |

|          | 1 = Interrupt request has occurred                                                                  |

|          | 0 = Interrupt request has not occurred                                                              |

| bit 0    | Unimplemented: Read as '0'                                                                          |

|          |                                                                                                     |

### REGISTER 8-10: IFS5: INTERRUPT FLAG STATUS REGISTER 5

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0, HS |

|-------|-----|-----|-----|-----|-----|-----|-----------|

| —     | —   | —   | —   | —   | —   | —   | ULPWUIF   |

| bit 7 |     |     |     |     |     |     | bit 0     |

| Legend:           | HS = Hardware Settable bit |                             |                    |  |

|-------------------|----------------------------|-----------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read | d as '0'           |  |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |  |

bit 15-1 Unimplemented: Read as '0'

bit 0 ULPWUIF: Ultra Low-Power Wake-up Interrupt Flag Status bit

1 = Interrupt request has occurred

0 = Interrupt request has not occurred

### REGISTER 8-11: IFS6: INTERR UPT FLAG STATUS REGISTER 6

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0, HS | R/W-0, HS |

|-------|-----|-----|-----|-----|-----|-----------|-----------|

| —     | —   | —   | —   | —   | —   | CLC2IF    | CLC1IF    |

| bit 7 |     |     |     |     |     |           | bit 0     |

| Legend:           | HS = Hardware Settable bit |                             |                    |

|-------------------|----------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-2 Unimplemented: Read as '0'

bit 1 CLC2IF: Configurable Logic Cell 2 Interrupt Flag Status bit 1 = Interrupt request has occurred 0 = Interrupt request has not occurred

bit 0 CLC1IF: Configurable Logic Cell 1 Interrupt Flag Status bit

1 = Interrupt request has occurred

0 = Interrupt request has not occurred

### REGISTER 8-17: IEC5: INTERRUPT ENABLE CONTROL REGISTER 5

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0     |

|---------|-----|-----|-----|-----|-----|-----|---------|

|         | —   | _   | _   |     |     |     | _       |

| bit 15  |     |     |     |     |     |     | bit 8   |

|         |     |     |     |     |     |     |         |

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0   |

|         | —   | —   | —   |     |     |     | ULPWUIE |

| bit 7   |     |     |     |     |     |     | bit 0   |

|         |     |     |     |     |     |     |         |

| Legend: |     |     |     |     |     |     |         |

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 15-1 Unimplemented: Read as '0'

bit 0 ULPWUIE: Ultra Low-Power Wake-up Interrupt Enable bit

1 = Interrupt request is enabled

0 = Interrupt request is not enabled

### REGISTER 8-18: IEC6: INTERRUPT ENABLE CONTROL REGISTER 5

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  | R/W-0  |

|-------|-----|-----|-----|-----|-----|--------|--------|

| —     | —   | —   | —   | —   | —   | CLC2IE | CLC1IE |

| bit 7 |     |     |     |     |     |        | bit 0  |

| Legend:           |                                                     |                      |                    |  |  |

|-------------------|-----------------------------------------------------|----------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared | x = Bit is unknown |  |  |

bit 15-2 Unimplemented: Read as '0'

bit 1 CLC2IE: Configurable Logic Cell 2 Interrupt Enable bit

1 = Interrupt request is enabled

0 = Interrupt request is not enabled

bit 0 CLC1IE: Configurable Logic Cell 1 Interrupt Enable bit

1 = Interrupt request is enabled

0 = Interrupt request is not enabled

| U-0        | U-0                              | U-0                                                                                                                                                                                 | U-0              | U-0                                                | U-0             | U-0                | U-0 |  |  |  |

|------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------|-----------------|--------------------|-----|--|--|--|

| _          | —                                |                                                                                                                                                                                     | —                | —                                                  | —               | —                  | _   |  |  |  |

| oit 15     |                                  |                                                                                                                                                                                     |                  |                                                    |                 |                    | bit |  |  |  |

| R/W-0      | R/W-0                            | R-0                                                                                                                                                                                 | R-0              | R-0                                                | R-0             | R-0                | R-0 |  |  |  |

| SMP        | CKE                              | D/A                                                                                                                                                                                 | P <sup>(1)</sup> | S <sup>(1)</sup>                                   | R/W             | UA                 | BF  |  |  |  |

| bit 7      |                                  |                                                                                                                                                                                     |                  |                                                    |                 |                    | bit |  |  |  |

| Legend:    |                                  |                                                                                                                                                                                     |                  |                                                    |                 |                    |     |  |  |  |

| R = Reada  | ıble bit                         | W = Writable                                                                                                                                                                        | bit              | U = Unimpler                                       | nented bit, rea | d as '0'           |     |  |  |  |

| -n = Value |                                  | '1' = Bit is set                                                                                                                                                                    |                  | U = Unimplemented bit, rea<br>'0' = Bit is cleared |                 | x = Bit is unknown |     |  |  |  |

|            |                                  |                                                                                                                                                                                     |                  |                                                    |                 |                    |     |  |  |  |

| bit 15-8   | •                                | ited: Read as '                                                                                                                                                                     | )'               |                                                    |                 |                    |     |  |  |  |

| bit 7      |                                  | Rate Control bit                                                                                                                                                                    |                  |                                                    |                 |                    |     |  |  |  |

|            |                                  | Slave mode:<br>e control is disat                                                                                                                                                   | oled for Standa  | rd Speed mode                                      | e (100 kHz and  | 1 MHz)             |     |  |  |  |

|            |                                  | e control is enab                                                                                                                                                                   |                  |                                                    |                 | /                  |     |  |  |  |

| bit 6      | CKE: SMBu                        | s Select bit                                                                                                                                                                        |                  |                                                    |                 |                    |     |  |  |  |

|            |                                  | Slave mode:                                                                                                                                                                         |                  |                                                    |                 |                    |     |  |  |  |

|            |                                  | 1 = Enables SMBus-specific inputs<br>0 = Disables SMBus-specific inputs                                                                                                             |                  |                                                    |                 |                    |     |  |  |  |

| bit 5      | D/A: Data/A                      | •                                                                                                                                                                                   |                  |                                                    |                 |                    |     |  |  |  |

|            | <u>In Master mo</u><br>Reserved. |                                                                                                                                                                                     |                  |                                                    |                 |                    |     |  |  |  |

|            | In Slave mod                     | de:                                                                                                                                                                                 |                  |                                                    |                 |                    |     |  |  |  |

|            |                                  | s that the last by<br>s that the last by                                                                                                                                            |                  |                                                    |                 |                    |     |  |  |  |

| bit 4      | P: Stop bit <sup>(1)</sup>       | 1                                                                                                                                                                                   |                  |                                                    |                 |                    |     |  |  |  |

|            |                                  | s that a Stop bit I was not detected                                                                                                                                                |                  | cted last                                          |                 |                    |     |  |  |  |

| bit 3      | S: Start bit <sup>(1)</sup>      | )                                                                                                                                                                                   |                  |                                                    |                 |                    |     |  |  |  |

|            |                                  | s that a Start bit was not detected                                                                                                                                                 |                  | cted last                                          |                 |                    |     |  |  |  |

| bit 2      | R/W: Read/                       | Write Information                                                                                                                                                                   | n bit            |                                                    |                 |                    |     |  |  |  |

|            | In Slave mod                     | <u>de:</u> <sup>(2)</sup>                                                                                                                                                           |                  |                                                    |                 |                    |     |  |  |  |

|            | 1 = Read<br>0 = Write            |                                                                                                                                                                                     |                  |                                                    |                 |                    |     |  |  |  |

|            | In Master me                     | ode <sup>.(3)</sup>                                                                                                                                                                 |                  |                                                    |                 |                    |     |  |  |  |

|            | 1 = Transmit                     | is in progress                                                                                                                                                                      |                  |                                                    |                 |                    |     |  |  |  |

|            | 0 = Transmit                     | is not in progre                                                                                                                                                                    | SS               |                                                    |                 |                    |     |  |  |  |

| bit 1      | •                                | Address bit (10-                                                                                                                                                                    |                  | • ·                                                |                 |                    |     |  |  |  |

|            |                                  | s that the user no<br>does not need t                                                                                                                                               |                  | the address in                                     | the SSPxADI     | D register         |     |  |  |  |

|            | This bit is cleare               |                                                                                                                                                                                     |                  |                                                    |                 |                    |     |  |  |  |

|            |                                  | This bit holds the $R/\overline{W}$ bit information following the last address match. This bit is only valid from the address match to the next Start bit, Stop bit or not ACK bit. |                  |                                                    |                 |                    |     |  |  |  |

|            |                                  | Ring this bit with SEN, RSEN, PEN, RCEN or ACKEN will indicate if the MSSPx is in Active mode.                                                                                      |                  |                                                    |                 |                    |     |  |  |  |

| REGISTE                                                 | R 14-4: SSP                  | CON1: MSSP                                                      | X CONTROL           | REGISTER             | I (I <sup>2</sup> C™ MOE | DE)                  |                      |  |  |  |  |

|---------------------------------------------------------|------------------------------|-----------------------------------------------------------------|---------------------|----------------------|--------------------------|----------------------|----------------------|--|--|--|--|

| U-0                                                     | U-0                          | U-0                                                             | U-0                 | U-0                  | U-0                      | U-0                  | U-0                  |  |  |  |  |

|                                                         | <u> </u>                     |                                                                 |                     |                      |                          |                      |                      |  |  |  |  |

| bit 15                                                  |                              |                                                                 |                     |                      |                          |                      | bit 8                |  |  |  |  |

| <b>D</b> AM 0                                           | <b>D</b> 444 a               |                                                                 | <b>D</b> 444 0      | 54440                | <b>D</b> /11/0           | <b>D</b> 444 o       | <b>D</b> 444 o       |  |  |  |  |

| R/W-0                                                   | R/W-0                        | R/W-0                                                           | R/W-0               | R/W-0                | R/W-0                    | R/W-0                | R/W-0                |  |  |  |  |

| WCOL                                                    | SSPOV                        | SSPEN <sup>(1)</sup>                                            | CKP                 | SSPM3 <sup>(2)</sup> | SSPM2 <sup>(2)</sup>     | SSPM1 <sup>(2)</sup> | SSPM0 <sup>(2)</sup> |  |  |  |  |

| bit 7                                                   |                              |                                                                 |                     |                      |                          |                      | bit 0                |  |  |  |  |

| Legend:                                                 |                              |                                                                 |                     |                      |                          |                      |                      |  |  |  |  |

| R = Reada                                               | able bit                     | W = Writable b                                                  | oit                 | U = Unimplem         | nented bit, read         | as '0'               |                      |  |  |  |  |

| -n = Value at POR (1' = Bit is set (0' = Bit is cleared |                              |                                                                 |                     |                      |                          | x = Bit is unkn      | iown                 |  |  |  |  |

|                                                         |                              |                                                                 |                     |                      |                          |                      |                      |  |  |  |  |

| bit 15-8                                                | Unimplemen                   | ted: Read as '0                                                 | ,                   |                      |                          |                      |                      |  |  |  |  |

| bit 7                                                   | WCOL: Write                  | e Collision Detec                                               | t bit               |                      |                          |                      |                      |  |  |  |  |

|                                                         | In Master Tra                | ansmit mode:                                                    |                     |                      |                          |                      |                      |  |  |  |  |

|                                                         |                              | to the SSPxBU                                                   |                     |                      |                          | nditions were r      | not valid for a      |  |  |  |  |

|                                                         | 0 = No collis                | ssion to be starte                                              |                     | eared in Soltwar     | e)                       |                      |                      |  |  |  |  |

|                                                         | In Slave Trai                | nsmit mode:                                                     |                     |                      |                          |                      |                      |  |  |  |  |

|                                                         |                              | PxBUF register i                                                | s written while     | e it is still transm | itting the previo        | ous word (mus        | t be cleared in      |  |  |  |  |

|                                                         |                              | software)<br>0 = No collision                                   |                     |                      |                          |                      |                      |  |  |  |  |

|                                                         |                              | node (Master or                                                 | Slave modes)        |                      |                          |                      |                      |  |  |  |  |

|                                                         | This is a "do                |                                                                 | <u>olavo modooj</u> | <u>.</u>             |                          |                      |                      |  |  |  |  |

| bit 6                                                   | SSPOV: Ma                    | ster Synchronou                                                 | s Serial Port F     | Receive Overflov     | w Indicator bit          |                      |                      |  |  |  |  |

|                                                         | <u>In Receive m</u>          |                                                                 |                     |                      |                          |                      |                      |  |  |  |  |

|                                                         | -                            | s received while t                                              | he SSPxBUF          | register is still h  | olding the prev          | ious byte (mus       | t be cleared in      |  |  |  |  |

|                                                         | software<br>0 = No over      |                                                                 |                     |                      |                          |                      |                      |  |  |  |  |

|                                                         | In Transmit r                |                                                                 |                     |                      |                          |                      |                      |  |  |  |  |

|                                                         |                              | n't care" bit in Tra                                            | ansmit mode.        |                      |                          |                      |                      |  |  |  |  |

| bit 5                                                   | SSPEN: Ma                    | SSPEN: Master Synchronous Serial Port Enable bit <sup>(1)</sup> |                     |                      |                          |                      |                      |  |  |  |  |

|                                                         |                              | the serial port ar                                              |                     |                      |                          | e serial port pi     | ns                   |  |  |  |  |

| L:1. 4                                                  |                              | the serial port a                                               | -                   | these pins as I/     | O port pins              |                      |                      |  |  |  |  |

| bit 4                                                   |                              | Release Control                                                 | DIT                 |                      |                          |                      |                      |  |  |  |  |

|                                                         | In Slave mod<br>1 = Releases |                                                                 |                     |                      |                          |                      |                      |  |  |  |  |

|                                                         |                              | ock low (clock sti                                              | etch), used to      | ensure data se       | etup time                |                      |                      |  |  |  |  |

|                                                         | In Master mo                 |                                                                 |                     |                      |                          |                      |                      |  |  |  |  |

|                                                         | Unused in th                 |                                                                 |                     |                      | (2)                      |                      |                      |  |  |  |  |

| bit 3-0                                                 | -                            | Master Synchro                                                  |                     |                      |                          |                      |                      |  |  |  |  |

|                                                         |                              | Slave mode, 10-l<br>Slave mode, 7-bi                            |                     |                      |                          |                      |                      |  |  |  |  |

|                                                         |                              | Firmware Contro                                                 |                     |                      |                          | labioa               |                      |  |  |  |  |

|                                                         | $1000 = I^2 C I$             | Master mode, Cl                                                 | ock = Fosc/(2       |                      |                          |                      |                      |  |  |  |  |

|                                                         |                              | Slave mode, 10-l<br>Slave mode, 7-bi                            |                     |                      |                          |                      |                      |  |  |  |  |

|                                                         | 0110 = 103                   |                                                                 | 1 2001622           |                      |                          |                      |                      |  |  |  |  |

| Note 1:                                                 | When enabled, t              |                                                                 | -                   | -                    | -                        |                      |                      |  |  |  |  |

| 2:                                                      | Bit combinations             | not specifically                                                |                     |                      | -                        |                      | -                    |  |  |  |  |

3: SSPxADD values of 0, 1 or 2 are not supported when the Baud Rate Generator is used with  $I^2C$  mode.

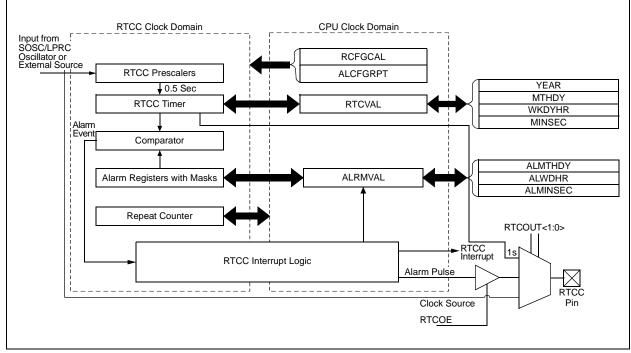

## 16.0 REAL-TIME CLOCK AND CALENDAR (RTCC)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the Real-Time Clock and Calendar, refer to the "PIC24F Family Reference Manual", "Real-Time Clock and Calendar (RTCC)" (DS39696).

The RTCC provides the user with a Real-Time Clock and Calendar (RTCC) function that can be calibrated.

Key features of the RTCC module are:

- · Operates in Sleep and Retention Sleep modes

- Selectable clock source

- Provides hours, minutes and seconds using 24-hour format

- · Visibility of one half second period

- Provides calendar weekday, date, month and year

- Alarm-configurable for half a second, one second, 10 seconds, one minute, 10 minutes, one hour, one day, one week, one month or one year

- Alarm repeat with decrementing counter

- Alarm with indefinite repeat chime

- Year 2000 to 2099 leap year correction

- · BCD format for smaller software overhead

- Optimized for long term battery operation

- User calibration of the 32.768 kHz clock crystal/32K INTRC frequency with periodic auto-adjust

- Optimized for long term battery operation

- · Fractional second synchronization

- Calibration to within ±2.64 seconds error per month

- · Calibrates up to 260 ppm of crystal error

- Ability to periodically wake-up external devices without CPU intervention (external power control)

- · Power control output for external circuit control

- · Calibration takes effect every 15 seconds

- Runs from any one of the following:

- External Real-Time Clock of 32.768 kHz

- Internal 31.25 kHz LPRC Clock

- 50 Hz or 60 Hz External Input

### 16.1 RTCC Source Clock

The user can select between the SOSC crystal oscillator, LPRC internal oscillator or an external 50 Hz/60 Hz power line input as the clock reference for the RTCC module. This gives the user an option to trade off system cost, accuracy and power consumption, based on the overall system needs.

### FIGURE 16-1: RTCC BLOCK DIAGRAM

### 16.3 Calibration

The real-time crystal input can be calibrated using the periodic auto-adjust feature. When properly calibrated, the RTCC can provide an error of less than 3 seconds per month. This is accomplished by finding the number of error clock pulses and storing the value into the lower half of the RCFGCAL register. The 8-bit signed value, loaded into the lower half of RCFGCAL, is multiplied by four and will be either added or subtracted from the RTCC timer, once every minute. Refer to the steps below for RTCC calibration:

- 1. Using another timer resource on the device, the user must find the error of the 32.768 kHz crystal.

- 2. Once the error is known, it must be converted to the number of error clock pulses per minute.

- 3. a) If the oscillator is faster than ideal (negative result from Step 2), the RCFGCAL register value must be negative. This causes the specified number of clock pulses to be subtracted from the timer counter, once every minute.