# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 23                                                                            |

| Program Memory Size        | 8КВ (2.75К х 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 1K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5V                                                                       |

| Data Converters            | A/D 19x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Through Hole                                                                  |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                       |

| Supplier Device Package    | 28-SPDIP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fv08km102-i-sp |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

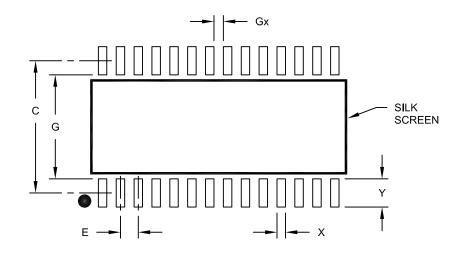

### Pin Diagrams (Continued)

|     | 20-Pin QFN<br>$\begin{array}{c ccccccccccccccccccccccccccccccccccc$              |  |  |  |  |  |  |

|-----|----------------------------------------------------------------------------------|--|--|--|--|--|--|

| Dia | Pin Features                                                                     |  |  |  |  |  |  |

| Pin | PIC24F08KM101 PIC24FV08KM101                                                     |  |  |  |  |  |  |

| 1   | PGED1/AN2/CTCMP/ULPWU/C1IND/OC2A/CN4/RB0                                         |  |  |  |  |  |  |

| 2   | PGEC1/AN3/C1INC/CTED12/CN5/RB1                                                   |  |  |  |  |  |  |

| 3   | AN4/U1RX/TCKIB/CTED13/CN6/RB2                                                    |  |  |  |  |  |  |

| 4   | OSCI/CLKI/AN13/C1INB/CN30/RA2                                                    |  |  |  |  |  |  |

| 5   | OSCO/CLKO/AN14/C1INA/CN29/RA3                                                    |  |  |  |  |  |  |

| 6   | PGED3/SOSCI/AN15/CLCINA/CN1/RB4                                                  |  |  |  |  |  |  |

| 7   | PGEC3/SOSCO/SCLKI/AN16/PWRLCLK/CLCINB/CN0/RA4                                    |  |  |  |  |  |  |

| 8   | AN19/U1TX/CTED1/INT0/CN23/RB7 AN19/U1TX/IC1/OC1A/CTED1/INT0/CN23/RB7             |  |  |  |  |  |  |

| 9   | AN20/SCL1/UICTS/OC1B/CTED10/CN22/RB8                                             |  |  |  |  |  |  |

| 10  | AN21/SDA1/T1CK/U1RTS/U1BCLK/IC2/CLC10/CTED4/CN21/RB9                             |  |  |  |  |  |  |

| 11  | IC1/OC1A/INT2/CN8/RA6 VCAP OR VDDCORE                                            |  |  |  |  |  |  |

| 12  | AN12/HLVDIN/SCK1/OC1C/CTED2/CN14/RB12 AN12/HLVDIN/SCK1/OC1C/CTED2/INT2/CN14/RB12 |  |  |  |  |  |  |

| 13  | AN11/SDO1/OCFB/OC1D/CTPLS/CN13/RB13                                              |  |  |  |  |  |  |

| 14  | CVREF/AN10/SDI1/C1OUT/OCFA/CTED5/INT1/CN12/RB14                                  |  |  |  |  |  |  |

| 15  | AN9/REFO/SS1/TCKIA/CTED6/CN11/RB15                                               |  |  |  |  |  |  |

| 16  | Vss/AVss                                                                         |  |  |  |  |  |  |

| 17  | Vdd/AVdd                                                                         |  |  |  |  |  |  |

| 18  | MCLR/Vpp/RA5                                                                     |  |  |  |  |  |  |

| 19  | PGEC2/CVREF+/VREF+/AN0/CN2/RA0                                                   |  |  |  |  |  |  |

| 20  | PGED2/CVReF-/VReF-/AN1/CN3/RA1                                                   |  |  |  |  |  |  |

### Pin Diagrams (Continued)

|                                                                                                                                                              |          | Pin Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 44-Pin TQFP/QFN <sup>(1)</sup>                                                                                                                               | Pin      | PIC24FXXKMX04 PIC24FVXXKMX04                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ∞ <b>८ ७ 0 ° ∿ 0 4 0 0 4</b>                                                                                                                                 | 1        | AN21/SDA1/T1CK/U1RTS/U1BCLK/IC2/ /CLC10/CTED4/CN21/RB9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| RB3<br>RB4<br>RB5<br>RB5<br>RB5<br>RB3<br>RB3<br>RB3<br>RB3<br>RB3<br>RB3<br>RB3<br>RB3<br>RB3<br>RB3                                                        | 2        | U1RX/ /CN18/RC6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4                                                                                                                        | 3        | U1TX/ /CN17/RC7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| RB9 1 33 RB4                                                                                                                                                 |          | /CN20/RC8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| RC6         2         32         RA8           RC7         3         31         RA3                                                                          |          | IC4/OC2F/CTED7/CN19/RC9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| RC7 3 31 RA3<br>RC8 4 30 RA2                                                                                                                                 | 6        | IC1/ / /CTED3/CN9/RA7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RC9 5 PIC24FXXKMX04 29 Vss                                                                                                                                   | 7        | /OC1A/CTED1/INT2/CN8/RA6 VCAP or VDDCORE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RA7 6 28 VDD<br>RA6 7 27 RC2                                                                                                                                 | 8        | PGED2/SDI1/OC1C/CTED11/CN16/RB10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| RB10 8 26 RC1                                                                                                                                                | 9        | PGEC2/SCK1/OC2A/CTED9/CN15/RB11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| RB11         9         25         RC0           RB12         10         24         RB3                                                                       |          | /AN12/HLVDIN/ /CTED2/ /AN12/HLVDIN/ /CTED2/INT2/<br>CN14/RB12 CN14/RB12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| RB13 11 23 RB2                                                                                                                                               |          | / /AN11/SD01/OC1D/CTPLS/CN13/RB13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 221011111111111111111111111111111111111                                                                                                                      | 12       | / /CN35/RA10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| RA10<br>RA11<br>RB15<br>AVDD<br>AVDD<br>RA10<br>RA10<br>RA10<br>RA10<br>RA10<br>RA10<br>RA10<br>RA10                                                         | 13       | / /CTED8/CN36/RA11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                              | 14       | /CVREF/ / /AN10/ / /C1OUT/OCFA/CTED5/INT1/CN12/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| RA10<br>RA11<br>RB14<br>RB14<br>AV815<br>AV815<br>AV815<br>MOCLR/RA5<br>RA01<br>RA10<br>RA10<br>RA10<br>RA10<br>RA10<br>RA11<br>RA10<br>RA11<br>RA10<br>RA11 |          | RB14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                              | 15       | / /AN9/ /REFO/SS1/TCKIA/CTED6/CN11/RB15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                              | 16       | AVss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                              | 17       | AVDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                              | 18       | MCLR/Vpp/RA5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                              | 19       | CVREF+/VREF+/         /AN0/         /CN2/         CVREF+/VREF+/         /AN0/         /           RA0         CTED1/CN2/RA0         CTED |

|                                                                                                                                                              | 20       | CVREF-/VREF-/AN1/CN3/RA1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                              | 21       | PGED1/AN2/CTCMP/ULPWU/C1IND/ / / /CN4/RB0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                              | 22       | PGEC1/ / /AN3/C1INC/ / /CTED12/CN5//RB1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                              | 23       | / /AN4/C1INB/ / /TCKIB/CTED13/CN6/RB2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                              | 24       | /AN5/C1INA/ / /CN7/RB3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                              | 25       | AN6/CN32/RC0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                              | 26       | AN7/CN31/RC1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                              | 27       | AN8/CN10/RC2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                              | 28       | VDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                              | 29       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                              | 30<br>31 | OSCI/CLKI/AN13/CN30/RA2<br>OSCO/CLKO/AN14/CN29/RA3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                              | 32       | OSCO/CLRO/AN 14/CN29/RAS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                              | 32       | SOSCI/AN15/ / /CN1/RB4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                              | 33       | SOSCO/SCLKI/AN16/PWRLCLK/ /CN0/RA4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                              | 34       | /CN34/RA9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                              | 36       | /CN28/RC3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                              | 37       | /CN25/RC4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                              | 38       | /CN26/RC5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Legend: Values in indicate pin                                                                                                                               | 39       | Vss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| function differences between                                                                                                                                 | 40       | VDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| PIC24F(V)XXKM202 and                                                                                                                                         | 41       | PGED3/AN17/ASDA1/OC1E/CLCINA/CN27/RB5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                              |          | PGEC3/AN18/ASCL1/OC1F/CLCINB/CN24/RB6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| PIC24F(V)XXKM102 devices.                                                                                                                                    | 42       | FGEG3/ANTO/AGGET/OCTF/GEGIND/GN24/RD0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

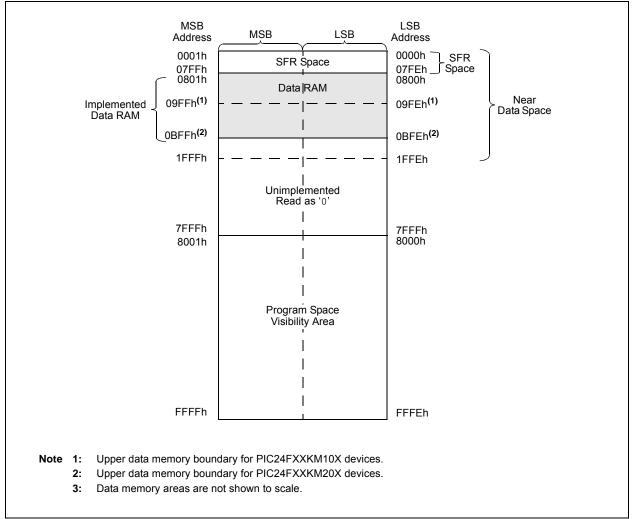

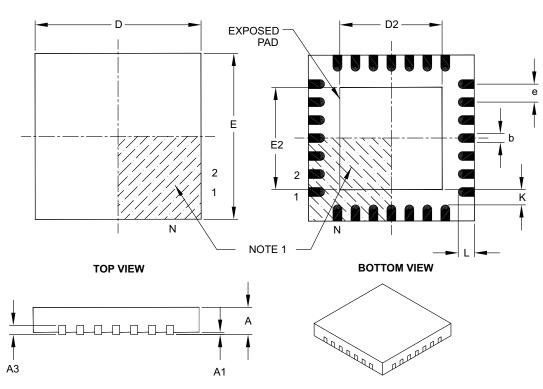

| Note 1: Exposed pad on underside of                                                                                                                          | 42<br>43 | AN19/INT0/CN23/RB7 AN19/ /OC1A/INT0/CN23/RB7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |