#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-><F

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                      |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 23                                                                            |

| Program Memory Size        | 8KB (2.75K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 1K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5V                                                                       |

| Data Converters            | A/D 19x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                |

| Supplier Device Package    | 28-SSOP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fv08km102-i-ss |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                |      | N                     | lemory       | 1               |                   |              |                  |      |      | Pe                  | riphe     | rals   |             |      |      |     |           |

|----------------|------|-----------------------|--------------|-----------------|-------------------|--------------|------------------|------|------|---------------------|-----------|--------|-------------|------|------|-----|-----------|

| Device         | Pins | Flash Program (bytes) | SRAM (bytes) | EE Data (bytes) | Voltage Range (V) | 16-Bit Timer | 16-Bit MCCP/SCCP | MSSP | UART | 12-Bit A/D Channels | 8-Bit DAC | Op Amp | Comparators | CTMU | RTCC | CLC | ICD BRKPT |

|                |      |                       |              |                 |                   | 5V           | Devic            | es   |      |                     |           |        |             |      |      |     |           |

| PIC24FV16KM204 | 44   | 16K                   | 2K           | 512             | 2.0-5.5           | 1            | 3/2              | 2    | 2    | 22                  | 2         | 2      | 3           | Yes  | Yes  | 2   | 3         |

| PIC24FV16KM202 | 28   | 16K                   | 2K           | 512             | 2.0-5.5           | 1            | 3/2              | 2    | 2    | 19                  | 2         | 2      | 3           | Yes  | Yes  | 2   | 3         |

| PIC24FV08KM204 | 44   | 8K                    | 2K           | 512             | 2.0-5.5           | 1            | 3/2              | 2    | 2    | 22                  | 2         | 2      | 3           | Yes  | Yes  | 2   | 3         |

| PIC24FV08KM202 | 28   | 8K                    | 2K           | 512             | 2.0-5.5           | 1            | 3/2              | 2    | 2    | 19                  | 2         | 2      | 3           | Yes  | Yes  | 2   | 3         |

| PIC24FV16KM104 | 44   | 16K                   | 1K           | 512             | 2.0-5.5           | 1            | 1/1              | 1    | 1    | 22                  | —         | _      | 1           | Yes  | _    | 1   | 3         |

| PIC24FV16KM102 | 28   | 16K                   | 1K           | 512             | 2.0-5.5           | 1            | 1/1              | 1    | 1    | 19                  | _         | _      | 1           | Yes  | _    | 1   | 3         |

| PIC24FV08KM102 | 28   | 8K                    | 1K           | 512             | 2.0-5.5           | 1            | 1/1              | 1    | 1    | 19                  | _         | _      | 1           | Yes  | _    | 1   | 3         |

| PIC24FV08KM101 | 20   | 8K                    | 1K           | 512             | 2.0-5.5           | 1            | 1/1              | 1    | 1    | 16                  | _         | -      | 1           | Yes  | _    | 1   | 3         |

|                |      |                       |              |                 |                   | 3V           | Devic            | es   |      |                     |           |        |             |      |      |     |           |

| PIC24F16KM204  | 44   | 16K                   | 2K           | 512             | 1.8-3.6           | 1            | 3/2              | 2    | 2    | 22                  | 2         | 2      | 3           | Yes  | Yes  | 2   | 3         |

| PIC24F16KM202  | 28   | 16K                   | 2K           | 512             | 1.8-3.6           | 1            | 3/2              | 2    | 2    | 19                  | 2         | 2      | 3           | Yes  | Yes  | 2   | 3         |

| PIC24F08KM204  | 44   | 8K                    | 2K           | 512             | 1.8-3.6           | 1            | 3/2              | 2    | 2    | 22                  | 2         | 2      | 3           | Yes  | Yes  | 2   | 3         |

| PIC24F08KM202  | 28   | 8K                    | 2K           | 512             | 1.8-3.6           | 1            | 3/2              | 2    | 2    | 19                  | 2         | 2      | 3           | Yes  | Yes  | 2   | 3         |

| PIC24F16KM104  | 44   | 16K                   | 1K           | 512             | 1.8-3.6           | 1            | 1/1              | 1    | 1    | 22                  | _         | —      | 1           | Yes  | —    | 1   | 3         |

| PIC24F16KM102  | 28   | 16K                   | 1K           | 512             | 1.8-3.6           | 1            | 1/1              | 1    | 1    | 19                  | _         | _      | 1           | Yes  | _    | 1   | 3         |

| PIC24F08KM102  | 28   | 8K                    | 1K           | 512             | 1.8-3.6           | 1            | 1/1              | 1    | 1    | 19                  | —         | —      | 1           | Yes  | —    | 1   | 3         |

| PIC24F08KM101  | 20   | 8K                    | 1K           | 512             | 1.8-3.6           | 1            | 1/1              | 1    | 1    | 16                  |           |        | 1           | Yes  | _    | 1   | 3         |

## **Table of Contents**

| 1.0   | Device Overview                                             |       |

|-------|-------------------------------------------------------------|-------|

| 2.0   | Guidelines for Getting Started with 16-Bit Microcontrollers | 29    |

| 3.0   | CPU                                                         | 35    |

| 4.0   | Memory Organization                                         | 41    |

| 5.0   | Flash Program Memory                                        | 67    |

| 6.0   | Data EEPROM Memory                                          | 73    |

| 7.0   | Resets                                                      | 79    |

| 8.0   | Interrupt Controller                                        | 85    |

| 9.0   | Oscillator Configuration                                    | . 121 |

| 10.0  | Power-Saving Features                                       | . 131 |

| 11.0  | I/O Ports                                                   | . 137 |

| 12.0  | Timer1                                                      |       |

| 13.0  | Capture/Compare/PWM/Timer Modules (MCCP and SCCP)           | . 143 |

| 14.0  | Master Synchronous Serial Port (MSSP)                       |       |

| 15.0  | Universal Asynchronous Receiver Transmitter (UART)          | . 173 |

| 16.0  | Real-Time Clock and Calendar (RTCC)                         | . 181 |

| 17.0  | Configurable Logic Cell (CLC)                               | . 195 |

| 18.0  | High/Low-Voltage Detect (HLVD)                              | . 207 |

|       | 12-Bit A/D Converter with Threshold Detect                  |       |

| 20.0  | 8-Bit Digital-to-Analog Converter (DAC)                     | . 229 |

| 21.0  | Dual Operational Amplifier Module                           | . 233 |

| 22.0  | Comparator Module                                           |       |

| 23.0  | Comparator Voltage Reference                                | . 239 |

| 24.0  | Charge Time Measurement Unit (CTMU)                         | . 241 |

| 25.0  | Special Features                                            | . 249 |

| 26.0  | Development Support                                         | . 261 |

| 27.0  | Electrical Characteristics                                  | . 265 |

| 28.0  | Packaging Information                                       | . 297 |

| Appe  | ndix A: Revision History                                    | . 325 |

| Index | · · · · · · · · · · · · · · · · · · ·                       | 327   |

|       | /icrochip Web Site                                          |       |

| Custo | omer Change Notification Service                            | . 333 |

| Custo | omer Support                                                | . 333 |

| Produ | uct Identification System                                   | . 335 |

| TABLE 4-29: | COMPARATOR REGISTER MAP |

|-------------|-------------------------|

|             |                         |

| File Name             | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10               | Bit 9                | Bit 8 | Bit 7  | Bit 6  | Bit 5 | Bit 4                | Bit 3 | Bit 2                | Bit 1                | Bit 0 | All<br>Resets |

|-----------------------|-------|--------|--------|--------|--------|--------|----------------------|----------------------|-------|--------|--------|-------|----------------------|-------|----------------------|----------------------|-------|---------------|

| CMSTAT                | 630h  | CMIDL  | _      | —      | —      |        | C3EVT <sup>(1)</sup> | C2EVT <sup>(1)</sup> | C1EVT | —      | _      | _     | —                    | —     | C3OUT <sup>(1)</sup> | C2OUT <sup>(1)</sup> | C1OUT | 0000          |

| CVRCON                | 632h  | —      | _      | _      | _      | _      | _                    | _                    | _     | CVREN  | CVROE  | CVRSS | CVR4                 | CVR3  | CVR2                 | CVR1                 | CVR0  | 0000          |

| CM1CON                | 634h  | CON    | COE    | CPOL   | CLPWR  |        | _                    | CEVT                 | COUT  | EVPOL1 | EVPOL0 | _     | CREF1                | CREF0 | —                    | CCH1                 | CCH0  | 0000          |

| CM2CON <sup>(1)</sup> | 636h  | CON    | COE    | CPOL   | CLPWR  |        | —                    | CEVT                 | COUT  | EVPOL1 | EVPOL0 | _     | CREF1 <sup>(1)</sup> | CREF0 | —                    | CCH1                 | CCH0  | 0000          |

| CM3CON <sup>(1)</sup> | 638h  | CON    | COE    | CPOL   | CLPWR  |        | —                    | CEVT                 | COUT  | EVPOL1 | EVPOL0 | _     | CREF1 <sup>(1)</sup> | CREF0 | —                    | CCH1                 | CCH0  | 0000          |

$\label{eq:legend: second condition, u = unchanged, --= unimplemented, q = value depends on condition, r = reserved.$

Note 1: These registers and bits are available only on PIC24F(V)16KM2XX devices.

#### TABLE 4-30: BAND GAP BUFFER CONTROL REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1   | Bit 0   | All<br>Resets |

|-----------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|---------|---------|---------------|

| BUFCON0   | 670h  |        | _      |        | _      |        | _      | _     |       | _     |       |       |       |       | _     | BUFREF1 | BUFREF0 | 0001          |

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition, r = reserved.

#### TABLE 4-31: CLOCK CONTROL REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7   | Bit 6 | Bit 5  | Bit 4 | Bit 3  | Bit 2   | Bit 1  | Bit 0  | All<br>Resets |

|-----------|-------|--------|--------|--------|--------|--------|--------|--------|--------|---------|-------|--------|-------|--------|---------|--------|--------|---------------|

| RCON      | 740h  | TRAPR  | IOPUWR | SBOREN | RETEN  |        |        | СМ     | PMSLP  | EXTR    | SWR   | SWDTEN | WDTO  | SLEEP  | IDLE    | BOR    | POR    | (Note 1)      |

| OSCCON    | 742h  | _      | COSC2  | COSC1  | COSC0  | _      | NOSC2  | NOSC1  | NOSC0  | CLKLOCK | _     | LOCK   | _     | CF     | SOSCDRV | SOSCEN | OSWEN  | (Note 2)      |

| CLKDIV    | 744h  | ROI    | DOZE2  | DOZE1  | DOZE0  | DOZEN  | RCDIV2 | RCDIV1 | RCDIV0 | _       | _     | _      | _     | _      | _       | _      | _      | 0100          |

| OSCTUN    | 748h  | _      | _      | _      | _      | _      | _      | _      | _      | _       | _     | TUN5   | TUN4  | TUN3   | TUN2    | TUN1   | TUN0   | 0000          |

| REFOCON   | 74Eh  | ROEN   | —      | ROSSLP | ROSEL  | RODIV3 | RODIV2 | RODIV1 | RODIV0 | _       | _     | _      | —     | —      | —       | _      | _      | 0000          |

| HLVDCON   | 756h  | HLVDEN | —      | HLSIDL | _      | _      | —      | _      | _      | VDIR    | BGVST | IRVST  | _     | HLVDL3 | HLVDL2  | HLVDL1 | HLVDL0 | 0000          |

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

Note 1: RCON register Reset values are dependent on the type of Reset.

2: OSCCON register Reset values are dependent on Configuration fuses and by type of Reset.

#### TABLE 4-32: NVM REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-----------|-------|--------|--------|--------|---------|--------|--------|-------|-------|---------|---------|---------|---------|---------|---------|---------|---------|---------------|

| NVMCON    | 760h  | WR     | WREN   | WRERR  | PGMONLY |        |        | _     |       | _       | ERASE   | NVMOP5  | NVMOP4  | NVMOP3  | NVMOP2  | NVMOP1  | NVMOP0  | 0000          |

| NVMKEY    | 766h  | —      |        |        | _       |        | _      |       |       | NVMKEY7 | NVMKEY6 | NVMKEY5 | NVMKEY4 | NVMKEY3 | NVMKEY2 | NVMKEY1 | NVMKEY0 | 0000          |

Legend: x = unknown, u = unchanged, - = unimplemented, q = value depends on condition, r = reserved.

#### TABLE 4-33: ULTRA LOW-POWER WAKE-UP REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|--------|--------|---------|--------|--------|--------|-------|---------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| ULPWCON   | 768h  | ULPEN  |        | ULPSIDL | _      | _      | _      | —     | ULPSINK | —     |       | —     | _     | _     | _     |       |       | 0000          |

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

### TABLE 4-34: PMD REGISTER MAP

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8 | Bit 7  | Bit 6                 | Bit 5                 | Bit 4                 | Bit 3                 | Bit 2                 | Bit 1                 | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|-------|--------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|--------|---------------|

| PMD1         | 770h  | _      | _      |        | _      | T1MD   |        | _      | _     | SSP1MD | U2MD <sup>(1)</sup>   | U1MD                  | _                     | _                     | _                     | _                     | ADCMD  | 0000          |

| PMD2         | 772h  |        | _      | _      | _      |        | _      | _      | _     | _      | -                     | _                     | CCP5MD <sup>(1)</sup> | CCP4MD <sup>(1)</sup> | CCP3MD <sup>(1)</sup> | CCP2MD                | CCP1MD | 0000          |

| PMD3         | 774h  |        | _      |        | _      |        | CMPMD  | RTCCMD | _     | _      | DAC1MD <sup>(1)</sup> | _                     | _                     | _                     | _                     | SSP2MD <sup>(1)</sup> | _      | 0000          |

| PMD4         | 776h  |        | _      |        | _      |        | _      | _      | _     | _      | ULPWUMD               | _                     | _                     | REFOMD                | CTMUMD                | HLVDMD                | _      | 0000          |

| PMD6         | 77Ah  |        | _      |        | _      |        | _      | _      | _     | _      | -                     | AMP1MD <sup>(1)</sup> | DAC2MD <sup>(1)</sup> | AMP2MD <sup>(1)</sup> | _                     | _                     | _      | 0000          |

| PMD8         | 77Eh  | _      | _      | —      | _      | _      | -      | _      | _     | _      | _                     | _                     | —                     | CLC2MD <sup>(1)</sup> | CLC1MD                | _                     | _      | 0000          |

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition, r = reserved.

Note 1: These bits are available only on PIC24F(V)16KM2XX devices.

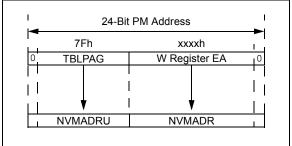

### 6.3 NVM Address Register

As with Flash program memory, the NVM Address registers, NVMADRU and NVMADR, form the 24-bit Effective Address (EA) of the selected row or word for data EEPROM operations. The NVMADRU register is used to hold the upper 8 bits of the EA, while the NVMADR register is used to hold the lower 16 bits of the EA. These registers are not mapped into the Special Function Register (SFR) space; instead, they directly capture the EA<23:0> of the last Table Write instruction that has been executed and select the data EEPROM row to erase. Figure 6-1 depicts the program memory EA that is formed for programming and erase operations.

Like program memory operations, the Least Significant bit (LSb) of NVMADR is restricted to even addresses. This is because any given address in the data EEPROM space consists of only the lower word of the program memory width; the upper word, including the uppermost "phantom byte", are unavailable. This means that the LSb of a data EEPROM address will always be '0'.

Similarly, the Most Significant bit (MSb) of NVMADRU is always '0', since all addresses lie in the user program space.

### FIGURE 6-1: DATA EEPROM ADDRESSING WITH TBLPAG AND NVM ADDRESS REGISTERS

### 6.4 Data EEPROM Operations

The EEPROM block is accessed using Table Read and Write operations, similar to those used for program memory. The TBLWTH and TBLRDH instructions are not required for data EEPROM operations since the memory is only 16 bits wide (data on the lower address is valid only). The following programming operations can be performed on the data EEPROM:

- · Erase one, four or eight words

- Bulk erase the entire data EEPROM

- Write one word

- Read one word

Note 1: Unexpected results will be obtained if the user attempts to read the EEPROM while a programming or erase operation is underway.

2: The XC16 C compiler includes library procedures to automatically perform the Table Read and Table Write operations, manage the Table Pointer and write buffers, and unlock and initiate memory write sequences. This eliminates the need to create assembler macros or time critical routines in C for each application.

The library procedures are used in the code examples detailed in the following sections. General descriptions of each process are provided for users who are not using the XC16 compiler libraries.

| R/W-0, HS       | U-0             | R/W-0, HS                         | R/W-0, HS        | R/W-0, HS         | U-0             | U-0             | R/W-0, HS |

|-----------------|-----------------|-----------------------------------|------------------|-------------------|-----------------|-----------------|-----------|

| NVMIF           | —               | AD1IF                             | U1TXIF           | U1RXIF            | _               | —               | CCT2IF    |

| bit 15          |                 |                                   |                  |                   |                 |                 | bit       |

|                 |                 |                                   |                  |                   |                 |                 |           |

| R/W-0, HS       | R/W-0, HS       | R/W-0, HS                         | U-0              | R/W-0, HS         | R/W-0, HS       | R/W-0, HS       | R/W-0, HS |

| CCT1IF          | CCP4IF          | CCP3IF                            |                  | T1IF              | CCP2IF          | CCP1IF          | INTOIF    |

| bit 7           |                 |                                   |                  |                   |                 |                 | bit       |

| Legend:         |                 | HS = Hardwa                       | re Settable bit  |                   |                 |                 |           |

| R = Readable    | bit             | W = Writable                      |                  | U = Unimplem      | ented bit. read | l as '0'        |           |

| -n = Value at F | POR             | '1' = Bit is set                  |                  | '0' = Bit is clea |                 | x = Bit is unkr | nown      |

|                 |                 |                                   |                  |                   |                 |                 |           |

| bit 15          |                 | Interrupt Flag                    |                  |                   |                 |                 |           |

|                 |                 | equest has occ                    |                  |                   |                 |                 |           |

|                 |                 | equest has not                    |                  |                   |                 |                 |           |

| bit 14          | -               | ted: Read as '                    |                  |                   |                 |                 |           |

| bit 13          |                 |                                   | -                | Flag Status bit   |                 |                 |           |

|                 |                 | equest has occ<br>equest has not  |                  |                   |                 |                 |           |

| bit 12          | -               | -                                 | Interrupt Flag   | Status bit        |                 |                 |           |

|                 |                 | equest has occ                    |                  | Status bit        |                 |                 |           |

|                 | •               | equest has not                    |                  |                   |                 |                 |           |

| bit 11          | -               | -                                 | terrupt Flag St  | atus bit          |                 |                 |           |

|                 |                 | equest has occ                    |                  |                   |                 |                 |           |

|                 |                 | equest has not                    |                  |                   |                 |                 |           |

| bit 10-9        | Unimplement     | ted: Read as '                    | כ'               |                   |                 |                 |           |

| bit 8           | CCT2IF: Capt    | ture/Compare 2                    | 2 Timer Interrup | ot Flag Status b  | it              |                 |           |

|                 | 1 = Interrupt r | equest has occ                    | curred           |                   |                 |                 |           |

|                 | -               | equest has not                    |                  |                   |                 |                 |           |

| bit 7           | -               |                                   | -                | ot Flag Status b  | it              |                 |           |

|                 |                 | equest has occ                    |                  |                   |                 |                 |           |

|                 |                 | equest has not                    |                  |                   |                 |                 |           |

| bit 6           | -               | -                                 |                  | ot Flag Status b  | oit             |                 |           |

|                 |                 | equest has occ                    |                  |                   |                 |                 |           |

| bit 5           | •               | equest has not                    |                  | at Elag Status h  | .;+             |                 |           |

| DIUS            | -               | equest has occ                    |                  | pt Flag Status b  | 11              |                 |           |

|                 |                 | equest has oct                    |                  |                   |                 |                 |           |

| bit 4           |                 | ted: Read as '                    |                  |                   |                 |                 |           |

| bit 3           | -               | Interrupt Flag S                  |                  |                   |                 |                 |           |

|                 |                 | equest has occ                    |                  |                   |                 |                 |           |

|                 | •               | equest has not                    |                  |                   |                 |                 |           |

| bit 2           | CCP2IF: Cap     | ture/Compare 2                    | 2 Event Interru  | ot Flag Status b  | oit             |                 |           |

|                 | 1 = Interrupt r | equest has occ                    | curred           | -                 |                 |                 |           |

|                 | 0 = Interrupt r | equest has not                    | occurred         |                   |                 |                 |           |

| bit 1           | CCP1IF: Cap     | ture/Compare                      | 1 Event Interru  | ot Flag Status b  | bit             |                 |           |

|                 |                 | equest has occ                    |                  |                   |                 |                 |           |

|                 | -               | equest has not                    |                  |                   |                 |                 |           |

|                 | INTOIL Evitor   |                                   | Elaa Statua hit  |                   |                 |                 |           |

| bit 0           |                 | nal Interrupt 0<br>equest has occ | -                |                   |                 |                 |           |

|                       | R/W-1                                                                                     | R/W-0                                                                                                                                          | R/W-0                                                                 | U-0                                         | R/W-1            | R/W-0           | R/W-0   |

|-----------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|---------------------------------------------|------------------|-----------------|---------|

| —                     | U2TXIP2                                                                                   | U2TXIP1                                                                                                                                        | U2TXIP0                                                               |                                             | U2RXIP2          | U2RXIP1         | U2RXIP0 |

| bit 15                |                                                                                           |                                                                                                                                                |                                                                       |                                             |                  |                 | bit     |

| U-0                   | R/W-1                                                                                     | R/W-0                                                                                                                                          | R/W-0                                                                 | U-0                                         | R/W-1            | R/W-0           | R/W-0   |

|                       | INT2IP2                                                                                   | INT2IP1                                                                                                                                        | INT2IP0                                                               | _                                           | CCT4IP2          | CCT4IP1         | CCT4IP0 |

| bit 7                 |                                                                                           |                                                                                                                                                |                                                                       |                                             |                  |                 | bit     |

|                       |                                                                                           |                                                                                                                                                |                                                                       |                                             |                  |                 |         |

| Legend:<br>R = Readat | ole hit                                                                                   | W = Writable                                                                                                                                   | hit                                                                   | II = Unimple                                | mented bit, read | 1 as '0'        |         |

| -n = Value a          |                                                                                           | '1' = Bit is set                                                                                                                               |                                                                       | '0' = Bit is cle                            |                  | x = Bit is unkr | iown    |

|                       |                                                                                           |                                                                                                                                                |                                                                       |                                             |                  |                 |         |

| bit 15                | Unimplemen                                                                                | ted: Read as 'o                                                                                                                                | )'                                                                    |                                             |                  |                 |         |

| bit 14-12             |                                                                                           | : UART2 Trans                                                                                                                                  |                                                                       |                                             |                  |                 |         |

|                       | 111 = Interru                                                                             | pt is Priority 7(                                                                                                                              | highest priority                                                      | interrupt)                                  |                  |                 |         |

|                       | •                                                                                         |                                                                                                                                                |                                                                       |                                             |                  |                 |         |

|                       | •                                                                                         |                                                                                                                                                |                                                                       |                                             |                  |                 |         |

|                       | 001 = Interru                                                                             | pt is Priority 1<br>pt source is dis                                                                                                           | abled                                                                 |                                             |                  |                 |         |

| bit 11                |                                                                                           | ted: Read as '                                                                                                                                 |                                                                       |                                             |                  |                 |         |

| bit 10-8              | -                                                                                         | : UART2 Rece                                                                                                                                   |                                                                       | Priority bits                               |                  |                 |         |

|                       |                                                                                           | pt is Priority 7 (                                                                                                                             |                                                                       |                                             |                  |                 |         |

|                       | •                                                                                         | · · · ·                                                                                                                                        | • • •                                                                 |                                             |                  |                 |         |

|                       | •                                                                                         |                                                                                                                                                |                                                                       |                                             |                  |                 |         |

|                       | 001 = Interru                                                                             | pt is Priority 1                                                                                                                               |                                                                       |                                             |                  |                 |         |

|                       | 000 = Interru                                                                             | pt source is dis                                                                                                                               | abled                                                                 |                                             |                  |                 |         |

| bit 7                 | Unimplemen                                                                                | ted: Read as 'o                                                                                                                                |                                                                       |                                             |                  |                 |         |

|                       |                                                                                           |                                                                                                                                                | )'                                                                    |                                             |                  |                 |         |

| bit 6-4               |                                                                                           | External Interr                                                                                                                                | upt 2 Priority b                                                      |                                             |                  |                 |         |

|                       | 111 = Interru                                                                             |                                                                                                                                                | upt 2 Priority b                                                      |                                             |                  |                 |         |

|                       |                                                                                           | External Interr                                                                                                                                | upt 2 Priority b                                                      |                                             |                  |                 |         |

|                       | 111 = Interru<br>•<br>•                                                                   | External Interr<br>pt is Priority 7(                                                                                                           | upt 2 Priority b                                                      |                                             |                  |                 |         |

|                       | 111 = Interru<br>•<br>•<br>001 = Interru                                                  | External Interr<br>pt is Priority 7(<br>pt is Priority 1                                                                                       | upt 2 Priority t<br>highest priority                                  |                                             |                  |                 |         |

| bit 6-4               | 111 = Interru<br>•<br>•<br>001 = Interru<br>000 = Interru                                 | External Interr<br>pt is Priority 7(<br>pt is Priority 1<br>pt source is dis                                                                   | upt 2 Priority b<br>highest priority<br>abled                         |                                             |                  |                 |         |

| bit 6-4<br>bit 3      | 111 = Interru<br>•<br>•<br>001 = Interru<br>000 = Interru<br>Unimplemen                   | External Interr<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '(                                        | upt 2 Priority b<br>highest priority<br>abled<br>)'                   | v interrupt)                                | av hits          |                 |         |

|                       | 111 = Interrup<br>•<br>•<br>001 = Interrup<br>000 = Interrup<br>Unimplemen<br>CCT4IP<2:0> | External Interr<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '(<br>-: Capture/Com                      | upt 2 Priority b<br>highest priority<br>abled<br>o'<br>pare 4 Timer I | <sup>,</sup> interrupt)<br>nterrupt Priorit | y bits           |                 |         |

| bit 6-4<br>bit 3      | 111 = Interrup<br>•<br>•<br>001 = Interrup<br>000 = Interrup<br>Unimplemen<br>CCT4IP<2:0> | External Interr<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '(                                        | upt 2 Priority b<br>highest priority<br>abled<br>o'<br>pare 4 Timer I | <sup>,</sup> interrupt)<br>nterrupt Priorit | y bits           |                 |         |

| bit 6-4<br>bit 3      | 111 = Interrup<br>•<br>•<br>001 = Interrup<br>000 = Interrup<br>Unimplemen<br>CCT4IP<2:0> | External Interr<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '(<br>-: Capture/Com                      | upt 2 Priority b<br>highest priority<br>abled<br>o'<br>pare 4 Timer I | <sup>,</sup> interrupt)<br>nterrupt Priorit | y bits           |                 |         |

| bit 6-4<br>bit 3      | 111 = Interrup<br>•<br>•<br>001 = Interrup<br>000 = Interrup<br>Unimplemen<br>CCT4IP<2:0> | External Interr<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '<br>•: Capture/Com<br>pt is Priority 7 ( | upt 2 Priority b<br>highest priority<br>abled<br>o'<br>pare 4 Timer I | <sup>,</sup> interrupt)<br>nterrupt Priorit | ty bits          |                 |         |

### REGISTER 8-26: IPC7: INTERRUPT PRIORITY CONTROL REGISTER 7

| U-0             | U-0                | U-0                 | U-0                       | U-0                                     | U-0                 | U-0                 | U-0                 |  |

|-----------------|--------------------|---------------------|---------------------------|-----------------------------------------|---------------------|---------------------|---------------------|--|

|                 | —                  | —                   | —                         | —                                       | —                   | —                   | —                   |  |

| bit 15          |                    |                     |                           |                                         |                     |                     | bit 8               |  |

|                 |                    |                     |                           |                                         |                     |                     |                     |  |

| U-0             | U-0                | R/W-0               | R/W-0                     | R/W-0                                   | R/W-0               | R/W-0               | R/W-0               |  |

| —               | —                  | TUN5 <sup>(1)</sup> | TUN4 <sup>(1)</sup>       | TUN3 <sup>(1)</sup>                     | TUN2 <sup>(1)</sup> | TUN1 <sup>(1)</sup> | TUN0 <sup>(1)</sup> |  |

| bit 7           |                    |                     |                           |                                         |                     |                     | bit 0               |  |

|                 |                    |                     |                           |                                         |                     |                     |                     |  |

| Legend:         |                    |                     |                           |                                         |                     |                     |                     |  |

| R = Readable    | bit                | W = Writable        | bit                       | U = Unimplem                            | nented bit, read    | l as '0'            |                     |  |

| -n = Value at I | POR                | '1' = Bit is set    |                           | '0' = Bit is cleared x = Bit is unknown |                     |                     |                     |  |

|                 |                    |                     |                           |                                         |                     |                     |                     |  |

| bit 15-6        | Unimplement        | ted: Read as 'd     | )'                        |                                         |                     |                     |                     |  |

| bit 5-0         | TUN<5:0>: FI       | RC Oscillator T     | uning bits <sup>(1)</sup> |                                         |                     |                     |                     |  |

|                 |                    | ximum frequen       | cy deviation              |                                         |                     |                     |                     |  |

|                 | 011110             |                     |                           |                                         |                     |                     |                     |  |

|                 | •                  |                     |                           |                                         |                     |                     |                     |  |

|                 | •                  |                     |                           |                                         |                     |                     |                     |  |

|                 | 000001             |                     |                           |                                         |                     |                     |                     |  |

|                 | 000000 <b>= Ce</b> | nter frequency,     | oscillator is ru          | nning at factory                        | calibrated free     | quency              |                     |  |

|                 | 111111             |                     |                           |                                         |                     |                     |                     |  |

|                 | •                  |                     |                           |                                         |                     |                     |                     |  |

|                 | •                  |                     |                           |                                         |                     |                     |                     |  |

|                 | 100001             |                     |                           |                                         |                     |                     |                     |  |

|                 |                    | nimum frequen       | cv deviation              |                                         |                     |                     |                     |  |

**Note 1:** Increments or decrements of TUN<5:0> may not change the FRC frequency in equal steps over the FRC tuning range and may not be monotonic.

### REGISTER 9-3: OSCTUN: FRC OSCILLATOR TUNE REGISTER

### 10.2.2 IDLE MODE

Idle mode includes these features:

- · The CPU will stop executing instructions.

- · The WDT is automatically cleared.

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 10.6 "Selective Peripheral Module Control").

- If the WDT or FSCM is enabled, the LPRC will also remain active.

The device will wake from Idle mode on any of these events:

- · Any interrupt that is individually enabled

- Any device Reset

- A WDT time-out

On wake-up from Idle, the clock is reapplied to the CPU and instruction execution begins immediately, starting with the instruction following the PWRSAV instruction or the first instruction in the ISR.

#### 10.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction will be held off until entry into Sleep or Idle mode has completed. The device will then wake-up from Sleep or Idle mode.

#### 10.2.3.1 Power-on Resets (PORs)

VDD voltage is monitored to produce PORs. When a true POR occurs, the entire device is reset.

### 10.3 Ultra Low-Power Wake-up

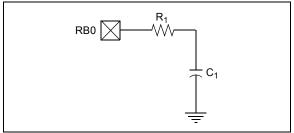

The Ultra Low-Power Wake-up (ULPWU) on pin, RB0, allows a slow falling voltage to generate an interrupt without excess current consumption.

To use this feature:

- 1. Charge the capacitor on RB0 by configuring the RB0 pin to an output and setting it to '1'.

- 2. Stop charging the capacitor by configuring RB0 as an input.

- 3. Discharge the capacitor by setting the ULPEN and ULPSINK bits in the ULPWCON register.

- 4. Configure Sleep mode.

- 5. Enter Sleep mode.

When the voltage on RB0 drops below VIL, the device wakes up and executes the next instruction.

This feature provides a low-power technique for periodically waking up the device from Sleep mode.

The time-out is dependent on the discharge time of the RC circuit on RB0.

When the ULPWU module wakes the device from Sleep mode, the ULPWUIF bit (IFS5<0>) is set. Software can check this bit upon wake-up to determine the wake-up source.

See Example 10-2 for initializing the ULPWU module.

### EXAMPLE 10-2: ULTRA LOW-POWER WAKE-UP INITIALIZATION

```

//********

// 1. Charge the capacitor on RBO

TRISBbits.TRISB0 = 0;

LATBbits.LATB0 = 1;

for(i = 0; i < 10000; i++) Nop();</pre>

//2. Stop Charging the capacitor

on RBO

11

//*******************************

TRISBbits.TRISB0 = 1;

//3. Enable ULPWU Interrupt

IFS5bits.ULPWUIF = 0;

IEC5bits.ULPWUIE = 1;

IPC21bits.ULPWUIP = 0x7;

//*********************************

//4. Enable the Ultra Low Power

11

Wakeup module and allow

11

capacitor discharge

ULPWCONbits.ULPEN = 1;

ULPWCONbit.ULPSINK = 1;

//5. Enter Sleep Mode

11

Sleep();

//for sleep, execution will

//resume here

```

A series resistor, between RB0 and the external capacitor provides overcurrent protection for the AN2/ULPWU/RB0 pin and enables software calibration of the time-out (see Figure 10-1).

#### FIGURE 10-1: SERIES RESISTOR

A timer can be used to measure the charge time and discharge time of the capacitor. The charge time can then be adjusted to provide the desired delay in Sleep. This technique compensates for the affects of temperature, voltage and component accuracy. The peripheral can also be configured as a simple, programmable Low-Voltage Detect (LVD) or temperature sensor.

NOTES:

## REGISTER 13-5: CCPxCON3L: CCPx CONTROL 3 LOW REGISTERS <sup>(1)</sup>

| U-0                                | U-0                                                                              | U-0             | U-0               | U-0          | U-0                | U-0      | U-0   |

|------------------------------------|----------------------------------------------------------------------------------|-----------------|-------------------|--------------|--------------------|----------|-------|

| _                                  | —                                                                                | —               | _                 | —            | —                  | —        | —     |

| bit 15                             |                                                                                  |                 |                   |              |                    |          | bit 8 |

|                                    |                                                                                  |                 |                   |              |                    |          |       |

| U-0                                | U-0                                                                              | R/W-0           | R/W-0             | R/W-0        | R/W-0              | R/W-0    | R/W-0 |

| _                                  | —                                                                                | DT5             | DT4               | DT3          | DT2                | DT1      | DT0   |

| bit 7                              |                                                                                  |                 |                   |              | •                  |          | bit 0 |

|                                    |                                                                                  |                 |                   |              |                    |          |       |

| Legend:                            |                                                                                  |                 |                   |              |                    |          |       |

| R = Readabl                        | e bit                                                                            | W = Writable    | bit               | U = Unimplem | nented bit, read   | l as '0' |       |

| -n = Value at POR '1' = Bit is set |                                                                                  |                 | '0' = Bit is clea | ared         | x = Bit is unknown |          |       |

|                                    |                                                                                  |                 |                   |              |                    |          |       |

| bit 15-6                           | Unimplemen                                                                       | ted: Read as 'd | )'                |              |                    |          |       |

| bit 5-0                            | DT<5:0>: CC                                                                      | Px Dead-Time    | Select bits       |              |                    |          |       |

|                                    | 111111 — Incert CO dood time delay, pariedo between complementary output signals |                 |                   |              |                    |          |       |

111111 = Insert 63 dead-time delay periods between complementary output signals

11110 = Insert 62 dead-time delay periods between complementary output signals

000010 = Insert 2 dead-time delay periods between complementary output signals

000001 = Insert 1 dead-time delay period between complementary output signals

000001 = Dead-time logic is disabled

Note 1: This register is implemented in MCCPx modules only.

| U-0    | R/W-0 | R/W-0 | R/W-0                | R/W-0                | R/W-0 | U-0   | U-0   |

|--------|-------|-------|----------------------|----------------------|-------|-------|-------|

| _      | CSS30 | CSS29 | CSS28                | CSS27                | CSS26 | —     | —     |

| bit 15 |       |       |                      |                      |       |       | bit 8 |

|        |       |       |                      |                      |       |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0                | R/W-0                | R/W-0 | R/W-0 | R/W-0 |

| CSS23  | CSS22 | CSS21 | CSS20 <sup>(2)</sup> | CSS19 <sup>(2)</sup> | CSS18 | CSS17 | CSS16 |

| bit 7  |       |       |                      |                      |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

- bit 14-10CSS<30:26>: A/D Input Scan Selection bits1 = Includes the corresponding channel for input scan0 = Skips the channel for input scanbit 9-8Unimplemented: Read as '0'bit 7-0CSS<23:16>: A/D Input Scan Selection bits<sup>(2)</sup>1 = Includes the corresponding channel for input scan0 = Skips the channel for input scan

- **Note 1:** Unimplemented channels are read as '0'. Do not select unimplemented channels for sampling as indeterminate results may be produced.

- 2: The CSS<20:19> bits are not implemented in 20-pin devices.

### REGISTER 19-9: AD1CSSL: A/D INPUT SCAN SELECT REGISTER (LOW WORD)<sup>(1)</sup>

| R/W-0                 | R/W-0               | R/W-0                      | R/W-0                                  | R/W-0                                                                                                     | R/W-0                                                                                                                                 | R/W-0                                                                                                                                              |

|-----------------------|---------------------|----------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| CSS14                 | CSS13               | CSS12                      | CSS11                                  | CSS10                                                                                                     | CSS9                                                                                                                                  | CSS8 <sup>(2,3)</sup>                                                                                                                              |

|                       |                     |                            |                                        |                                                                                                           |                                                                                                                                       | bit 8                                                                                                                                              |

|                       |                     |                            |                                        |                                                                                                           |                                                                                                                                       |                                                                                                                                                    |

| R/W-0                 | R/W-0               | R/W-0                      | R/W-0                                  | R/W-0                                                                                                     | R/W-0                                                                                                                                 | R/W-0                                                                                                                                              |

| CSS6 <sup>(2,3)</sup> | CSS5 <sup>(2)</sup> | CSS4                       | CSS3                                   | CSS2                                                                                                      | CSS1                                                                                                                                  | CSS0                                                                                                                                               |

|                       |                     |                            |                                        |                                                                                                           |                                                                                                                                       | bit 0                                                                                                                                              |

|                       | R/W-0               | CSS14 CSS13<br>R/W-0 R/W-0 | CSS14 CSS13 CSS12<br>R/W-0 R/W-0 R/W-0 | CSS14         CSS13         CSS12         CSS11           R/W-0         R/W-0         R/W-0         R/W-0 | CSS14         CSS13         CSS12         CSS11         CSS10           R/W-0         R/W-0         R/W-0         R/W-0         R/W-0 | CSS14         CSS13         CSS12         CSS11         CSS10         CSS9           R/W-0         R/W-0         R/W-0         R/W-0         R/W-0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 CSS<15:0>: A/D Input Scan Selection bits<sup>(2,3)</sup>

1 = Includes the corresponding ANx input for scan

- 0 = Skips the channel for input scan

- **Note 1:** Unimplemented channels are read as '0'. Do not select unimplemented channels for sampling as indeterminate results may be produced.

- 2: The CSS<8:5> bits are not implemented in 20-pin devices.

- 3: The CSS<8:6> bits are not implemented in 28-pin devices.

## 19.2 A/D Sampling Requirements

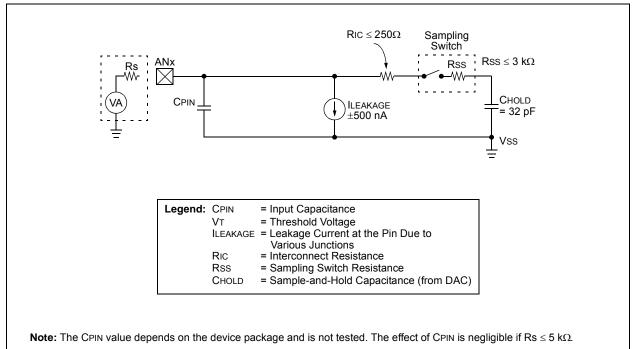

The analog input model of the 12-bit A/D Converter is shown in Figure 19-2. The total sampling time for the A/D is a function of the holding capacitor charge time.

For the A/D Converter to meet its specified accuracy, the Charge Holding Capacitor (CHOLD) must be allowed to fully charge to the voltage level on the analog input pin. The Source Impedance (Rs), the Interconnect Impedance (Rsc) and the Internal Sampling Switch Impedance (Rss) combine to directly affect the time required to charge CHOLD. The combined impedance of the analog sources must, therefore, be small enough to fully charge the holding capacitor within the chosen sample time. To minimize the effects of pin leakage currents on the accuracy of the A/D Converter, the maximum recommended source impedance, Rs, is  $2.5 \text{ k}\Omega$ . After the analog input channel is selected (changed), this sampling function

must be completed prior to starting the conversion. The internal holding capacitor will be in a discharged state prior to each sample operation.

At least 1 TAD time period should be allowed between conversions for the sample time. For more details, see **Section 27.0 "Electrical Characteristics"**.

## EQUATION 19-1: A/D CONVERSION CLOCK PERIOD

$$TAD = TCY (ADCS + 1)$$

$ADCS = \frac{TAD}{TCY} - 1$

**Note:** Based on Tcy = 2/Fosc; Doze mode and PLL are disabled.

### FIGURE 19-2: 12-BIT A/D CONVERTER ANALOG INPUT MODEL

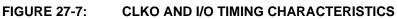

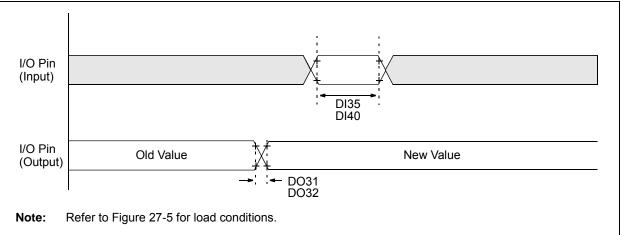

### TABLE 27-24: CLKO AND I/O TIMING REQUIREMENTS

| AC CHARACTERISTICS |      |                                       |     | <b>Operating</b>   |     | <b>2.0V to</b><br>-40°C ≤ | 3.6V (PIC24F16KM204)<br>5.5V (PIC24FV16KM204)<br>TA $\leq$ +85°C for Industrial<br>TA $\leq$ +125°C for Extended |

|--------------------|------|---------------------------------------|-----|--------------------|-----|---------------------------|------------------------------------------------------------------------------------------------------------------|

| Param<br>No.       | Sym  | Characteristic                        | Min | Typ <sup>(1)</sup> | Max | Units                     | Conditions                                                                                                       |

| DO31               | TIOR | Port Output Rise Time                 | _   | 10                 | 25  | ns                        |                                                                                                                  |

| DO32               | TIOF | Port Output Fall Time                 | —   | 10                 | 25  | ns                        |                                                                                                                  |

| DI35               | Tinp | INTx Pin High or Low Time<br>(output) | 20  | _                  | _   | ns                        |                                                                                                                  |

| DI40               | Trbp | CNx High or Low Time (input)          | 2   | _                  | _   | Тсү                       |                                                                                                                  |

**Note 1:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

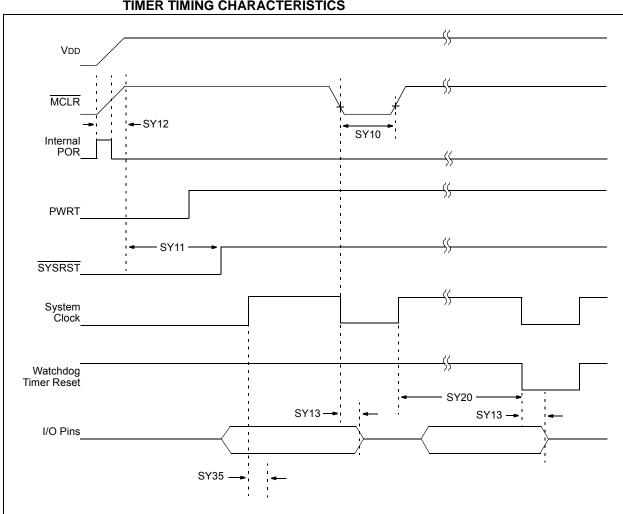

## FIGURE 27-8: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING CHARACTERISTICS

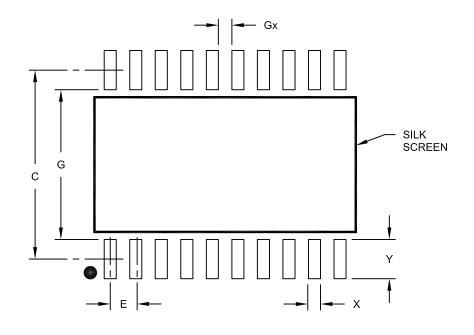

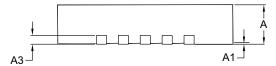

20-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                          | N   | <b>ILLIMETER</b> | S    |      |

|--------------------------|-----|------------------|------|------|

| Dimension                | MIN | NOM              | MAX  |      |

| Contact Pitch            | E   | 1.27 BSC         |      |      |

| Contact Pad Spacing      | С   |                  | 9.40 |      |

| Contact Pad Width (X20)  | Х   |                  |      | 0.60 |

| Contact Pad Length (X20) | Y   |                  |      | 1.95 |

| Distance Between Pads    | Gx  | 0.67             |      |      |

| Distance Between Pads    | G   | 7.45             |      |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2094A

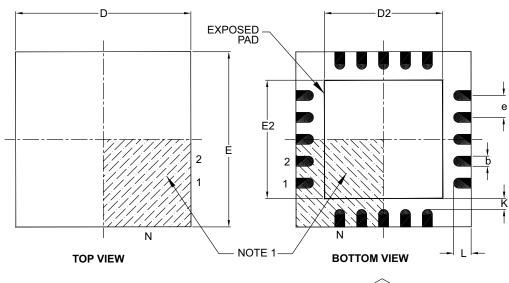

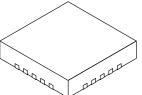

### 20-Lead Plastic Quad Flat, No Lead Package (ML) – 4x4x0.9 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units     | MILLIMETERS |          |      |

|------------------------|-----------|-------------|----------|------|

| Dimensi                | on Limits | MIN         | NOM      | MAX  |

| Number of Pins         | N         |             | 20       |      |

| Pitch                  | е         |             | 0.50 BSC |      |

| Overall Height         | Α         | 0.80        | 0.90     | 1.00 |

| Standoff               | A1        | 0.00        | 0.02     | 0.05 |

| Contact Thickness      | A3        |             | 0.20 REF |      |

| Overall Width          | E         | 4.00 BSC    |          |      |

| Exposed Pad Width      | E2        | 2.60        | 2.70     | 2.80 |

| Overall Length         | D         |             | 4.00 BSC |      |

| Exposed Pad Length     | D2        | 2.60        | 2.70     | 2.80 |

| Contact Width          | b         | 0.18        | 0.25     | 0.30 |

| Contact Length         | L         | 0.30        | 0.40     | 0.50 |

| Contact-to-Exposed Pad | К         | 0.20        | -        | _    |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-126B

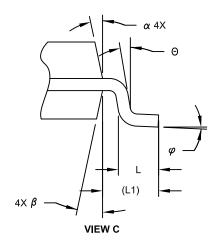

### 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |           |          |      |

|--------------------------|-------------|-----------|----------|------|

| Dimensior                | Limits      | MIN       | NOM      | MAX  |

| Number of Pins           | N           |           | 28       |      |

| Pitch                    | е           |           | 1.27 BSC |      |

| Overall Height           | A           | -         | -        | 2.65 |

| Molded Package Thickness | A2          | 2.05      | -        | -    |

| Standoff §               | A1          | 0.10      | -        | 0.30 |

| Overall Width            | E           | 10.30 BSC |          |      |

| Molded Package Width     | E1          | 7.50 BSC  |          |      |

| Overall Length           | D           | 17.90 BSC |          |      |

| Chamfer (Optional)       | h           | 0.25      | -        | 0.75 |

| Foot Length              | L           | 0.40      | -        | 1.27 |

| Footprint                | L1          |           | 1.40 REF |      |

| Lead Angle               | Θ           | 0°        | -        | -    |

| Foot Angle               | φ           | 0°        | -        | 8°   |

| Lead Thickness           | С           | 0.18      | -        | 0.33 |

| Lead Width               | b           | 0.31      | -        | 0.51 |

| Mold Draft Angle Top     | α           | 5°        | -        | 15°  |

| Mold Draft Angle Bottom  | β           | 5°        | -        | 15°  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- 3. Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing C04-052C Sheet 2 of 2

NOTES:

NOTES: