#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                     |

| Number of I/O              | 23                                                                             |

| Program Memory Size        | 8KB (2.75K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | 512 x 8                                                                        |

| RAM Size                   | 1K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5V                                                                        |

| Data Converters            | A/D 19x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                 |

| Supplier Device Package    | 28-SSOP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fv08km102t-i-ss |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 1-5: PIC24FV16KM204 FAMILY PINOUT DESCRIPTION (CONTINUED)

|          |                                  |                                  | F             |                        |                |                                  |                                  | FV            |                        |                |     |        |                                                |

|----------|----------------------------------|----------------------------------|---------------|------------------------|----------------|----------------------------------|----------------------------------|---------------|------------------------|----------------|-----|--------|------------------------------------------------|

|          |                                  | I                                | Pin Numb      | ber                    |                |                                  | I                                | Pin Numb      | er                     |                |     |        |                                                |

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | I/O | Buffer | Description                                    |

| SCL1     | 12                               | 17                               | 14            | 44                     | 48             | 12                               | 17                               | 14            | 44                     | 48             | I/O | I2C    | MSSP1 I <sup>2</sup> C Clock                   |

| SDA1     | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | I/O | I2C    | MSSP1 I <sup>2</sup> C Data                    |

| SCL2     | _                                | 7                                | 4             | 24                     | 26             | _                                | 7                                | 4             | 24                     | 26             | I/O | I2C    | MSSP2 I <sup>2</sup> C Clock                   |

| SDA2     | _                                | 6                                | 3             | 23                     | 25             | _                                | 6                                | 3             | 23                     | 25             | I/O | I2C    | MSSP2 I <sup>2</sup> C Data                    |

| SCLKI    | 10                               | 12                               | 9             | 34                     | 37             | 10                               | 12                               | 9             | 34                     | 37             | Ι   | ST     | Secondary Clock Digital Input                  |

| SOSCI    | 9                                | 11                               | 8             | 33                     | 36             | 9                                | 11                               | 8             | 33                     | 36             | Ι   | ANA    | Secondary Oscillator Input                     |

| SOSCO    | 10                               | 12                               | 9             | 34                     | 37             | 10                               | 12                               | 9             | 34                     | 37             | Ι   | ANA    | Secondary Oscillator Output                    |

| T1CK     | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | Ι   | ST     | Timer1 Digital Input Cock                      |

| TCKIA    | 18                               | 26                               | 23            | 15                     | 16             | 18                               | 26                               | 23            | 15                     | 16             | Ι   | ST     | MCCP/SCCP Time Base Clock Input A              |

| TCKIB    | 6                                | 6                                | 3             | 23                     | 25             | 6                                | 6                                | 3             | 23                     | 25             | Ι   | ST     | MCCP/SCCP Time Base Clock Input B              |

| U1CTS    | 12                               | 17                               | 14            | 44                     | 48             | 12                               | 17                               | 14            | 44                     | 48             | Ι   | ST     | UART1 Clear-To-Send Input                      |

| U1RTS    | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | 0   | _      | UART1 Request-To-Send Output                   |

| U1BCLK   | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | 0   | —      | UART1 16x Baud Rate Clock Output               |

| U1RX     | 6                                | 6                                | 3             | 2                      | 2              | 6                                | 6                                | 3             | 2                      | 2              | Ι   | ST     | UART1 Receive                                  |

| U1TX     | 11                               | 16                               | 13            | 3                      | 3              | 11                               | 16                               | 13            | 3                      | 3              | 0   | _      | UART1 Transmit                                 |

| U2CTS    | _                                | 12                               | 9             | 34                     | 37             | _                                | 12                               | 9             | 34                     | 37             | I   | ST     | UART2 Clear-To-Send Input                      |

| U2RTS    | _                                | 11                               | 8             | 33                     | 36             | _                                | 11                               | 8             | 33                     | 36             | 0   | _      | UART2 Request-To-Send Output                   |

| U2BCLK   | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | 0   | _      | UART2 16x Baud Rate Clock Output               |

| U2RX     | _                                | 5                                | 2             | 22                     | 24             | —                                | 5                                | 2             | 22                     | 24             | Ι   | ST     | UART2 Receive                                  |

| U2TX     | _                                | 4                                | 1             | 21                     | 23             | —                                | 4                                | 1             | 21                     | 23             | 0   | _      | UART2 Transmit                                 |

| ULPWU    | 4                                | 4                                | 1             | 21                     | 23             | 4                                | 4                                | 1             | 21                     | 23             | Ι   | ANA    | Ultra Low-Power Wake-up Input                  |

| VCAP     | _                                | _                                |               | —                      | _              | 14                               | 20                               | 17            | 7                      | 7              | Р   | —      | Regulator External Filter Capacitor Connection |

| Vdd      | 20                               | 28                               | 25            | 17,28,28               | 18,30,30       | 20                               | 28                               | 25            | 17,28,28               | 18,30,30       | Р   | —      | Device Positive Supply Voltage                 |

| VDDCORE  | _                                | _                                | _             | —                      | _              | 14                               | 20                               | 17            | 7                      | 7              | Р   | —      | Microcontroller Core Supply Voltage            |

| Vpp      | 1                                | 1                                | 26            | 18                     | 19             | 1                                | 1                                | 26            | 18                     | 19             | Р   | —      | High-Voltage Programming Pin                   |

| VREF+    | 2                                | 2                                | 27            | 19                     | 21             | 2                                | 2                                | 27            | 19                     | 21             | I   | ANA    | A/D Reference Voltage Positive Input           |

| VREF-    | 3                                | 3                                | 28            | 20                     | 22             | 3                                | 3                                | 28            | 20                     | 22             | Ι   | ANA    | A/D Reference Voltage Negative Input           |

| Vss      | 19                               | 27                               | 24            | 16,29,29               | 17,31,31       | 19                               | 27                               | 24            | 16,29,29               | 17,31,31       | Р   | —      | Device Ground Return Voltage                   |

Legend: ANA = Analog level input/output, ST = Schmitt Trigger input buffer, I<sup>2</sup>C<sup>™</sup> = I<sup>2</sup>C/SMBus input buffer

#### TABLE 4-3:CPU CORE REGISTERS MAP

| TABLE        | 4-3.  | UP                               |         | KE KEGI   | STERS     |           |           |          |          |            |          |          |          |          |          |          |          |               |

|--------------|-------|----------------------------------|---------|-----------|-----------|-----------|-----------|----------|----------|------------|----------|----------|----------|----------|----------|----------|----------|---------------|

| File<br>Name | Addr. | Bit 15                           | Bit 14  | Bit 13    | Bit 12    | Bit 11    | Bit 10    | Bit 9    | Bit 8    | Bit 7      | Bit 6    | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

| WREG0        | 0h    | WREG0 0                          |         |           |           |           |           |          |          |            |          |          | 0000     |          |          |          |          |               |

| WREG1        | 2h    |                                  |         |           |           |           |           |          | W        | /REG1      |          |          |          |          |          |          |          | 0000          |

| WREG2        | 4h    | WREG2                            |         |           |           |           |           |          |          |            |          | 0000     |          |          |          |          |          |               |

| WREG3        | 6h    | WREG3 0                          |         |           |           |           |           |          |          |            |          | 0000     |          |          |          |          |          |               |

| WREG4        | 8h    |                                  | WREG4 0 |           |           |           |           |          |          |            |          |          | 0000     |          |          |          |          |               |

| WREG5        | Ah    |                                  |         |           |           |           |           |          | W        | /REG5      |          |          |          |          |          |          |          | 0000          |

| WREG6        | Ch    |                                  |         |           |           |           |           |          | W        | /REG6      |          |          |          |          |          |          |          | 0000          |

| WREG7        | Eh    |                                  |         |           |           |           |           |          | W        | /REG7      |          |          |          |          |          |          |          | 0000          |

| WREG8        | 10h   |                                  |         |           |           |           |           |          | W        | /REG8      |          |          |          |          |          |          |          | 0000          |

| WREG9        | 12h   |                                  |         |           |           |           |           |          | W        | /REG9      |          |          |          |          |          |          |          | 0000          |

| WREG10       | 14h   |                                  |         |           |           |           |           |          | W        | REG10      |          |          |          |          |          |          |          | 0000          |

| WREG11       | 16h   |                                  |         |           |           |           |           |          | W        | REG11      |          |          |          |          |          |          |          | 0000          |

| WREG12       | 18h   |                                  |         |           |           |           |           |          | W        | REG12      |          |          |          |          |          |          |          | 0000          |

| WREG13       | 1Ah   |                                  |         |           |           |           |           |          | W        | REG13      |          |          |          |          |          |          |          | 0000          |

| WREG14       | 1Ch   |                                  |         |           |           |           |           |          | W        | REG14      |          |          |          |          |          |          |          | 0000          |

| WREG15       | 1Eh   |                                  |         |           |           |           |           |          | W        | REG15      |          |          |          |          |          |          |          | 0800          |

| SPLIM        | 20h   |                                  |         |           |           |           |           |          | SPLI     | V Register |          |          |          |          |          |          |          | xxxx          |

| PCL          | 2Eh   |                                  |         |           |           |           |           |          | PCL      | Register   |          |          |          |          |          |          |          | 0000          |

| PCH          | 30h   | _                                |         |           |           | —         | —         |          | —        | PCH7       | PCH6     | PCH5     | PCH4     | PCH3     | PCH2     | PCH1     | PCH0     | 0000          |

| TBLPAG       | 32h   | _                                |         |           |           | —         | —         |          | —        | TBLPAG7    | TBLPAG6  | TBLPAG5  | TBLPAG4  | TBLPAG3  | TBLPAG2  | TBLPAG1  | TBLPAG0  | 0000          |

| PSVPAG       | 34h   | _                                |         |           |           | -         | —         | _        | _        | PSVPAG7    | PSVPAG6  | PSVPAG5  | PSVPAG4  | PSVPAG3  | PSVPAG2  | PSVPAG1  | PSVPAG0  | 0000          |

| RCOUNT       | 36h   | RCOUNT Register x                |         |           |           |           |           |          |          | xxxx       |          |          |          |          |          |          |          |               |

| SR           | 42h   | DC IPL2 IPL1 IPL0 RA N OV Z C 00 |         |           |           |           |           |          |          |            | 0000     |          |          |          |          |          |          |               |

| CORCON       | 44h   | _                                |         | _         |           | -         | —         | _        | —        | —          | —        | _        | _        | IPL3     | PSV      | _        | —        | 0000          |

| DISICNT      | 52h   | _                                | -       | DISICNT13 | DISICNT12 | DISICNT11 | DISICNT10 | DISICNT9 | DISICNT8 | DISICNT7   | DISICNT6 | DISICNT5 | DISICNT4 | DISICNT3 | DISICNT2 | DISICNT1 | DISICNT0 | xxxx          |

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

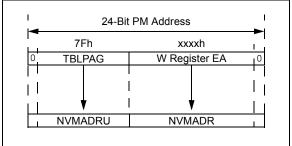

#### 6.3 NVM Address Register

As with Flash program memory, the NVM Address registers, NVMADRU and NVMADR, form the 24-bit Effective Address (EA) of the selected row or word for data EEPROM operations. The NVMADRU register is used to hold the upper 8 bits of the EA, while the NVMADR register is used to hold the lower 16 bits of the EA. These registers are not mapped into the Special Function Register (SFR) space; instead, they directly capture the EA<23:0> of the last Table Write instruction that has been executed and select the data EEPROM row to erase. Figure 6-1 depicts the program memory EA that is formed for programming and erase operations.

Like program memory operations, the Least Significant bit (LSb) of NVMADR is restricted to even addresses. This is because any given address in the data EEPROM space consists of only the lower word of the program memory width; the upper word, including the uppermost "phantom byte", are unavailable. This means that the LSb of a data EEPROM address will always be '0'.

Similarly, the Most Significant bit (MSb) of NVMADRU is always '0', since all addresses lie in the user program space.

#### FIGURE 6-1: DATA EEPROM ADDRESSING WITH TBLPAG AND NVM ADDRESS REGISTERS

#### 6.4 Data EEPROM Operations

The EEPROM block is accessed using Table Read and Write operations, similar to those used for program memory. The TBLWTH and TBLRDH instructions are not required for data EEPROM operations since the memory is only 16 bits wide (data on the lower address is valid only). The following programming operations can be performed on the data EEPROM:

- · Erase one, four or eight words

- Bulk erase the entire data EEPROM

- Write one word

- Read one word

Note 1: Unexpected results will be obtained if the user attempts to read the EEPROM while a programming or erase operation is underway.

2: The XC16 C compiler includes library procedures to automatically perform the Table Read and Table Write operations, manage the Table Pointer and write buffers, and unlock and initiate memory write sequences. This eliminates the need to create assembler macros or time critical routines in C for each application.

The library procedures are used in the code examples detailed in the following sections. General descriptions of each process are provided for users who are not using the XC16 compiler libraries.

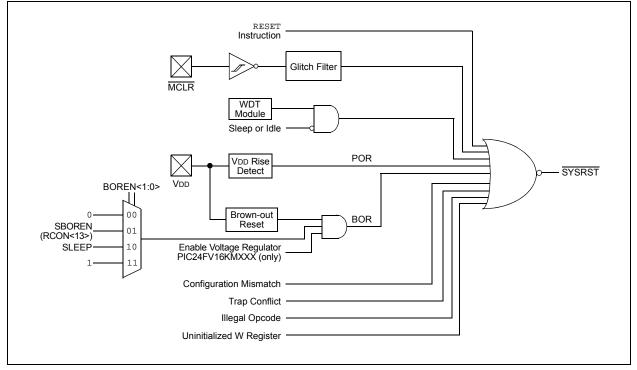

### 7.0 RESETS

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on Resets, refer to the "PIC24F Family Reference Manual", "Reset with Programmable Brown-out Reset" (DS39728).

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- · POR: Power-on Reset

- MCLR: Pin Reset

- SWR: RESET Instruction

- WDTR: Watchdog Timer Reset

- · BOR: Brown-out Reset

- LPBOR: Low-Power BOR

- TRAPR: Trap Conflict Reset

- IOPUWR: Illegal Opcode Reset

- UWR: Uninitialized W Register Reset

A simplified block diagram of the Reset module is shown in Figure 7-1.

Any active source of Reset will make the SYSRST signal active. Many registers associated with the CPU and peripherals are forced to a known Reset state. Most registers are unaffected by a Reset; their status is unknown on Power-on Reset (POR) and unchanged by all other Resets.

Note: Refer to the specific peripheral or Section 3.0 "CPU" of this data sheet for register Reset states.

All types of device Reset will set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 7-1). A Power-on Reset will clear all bits except for the BOR and POR bits (RCON<1:0>) which are set. The user may set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software will not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer (WDT) and device power-saving states. The function of these bits is discussed in other sections of this manual.

Note: The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset will be meaningful.

### FIGURE 7-1: RESET SYSTEM BLOCK DIAGRAM

#### REGISTER 8-10: IFS5: INTERRUPT FLAG STATUS REGISTER 5

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | _   | —   | _   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0, HS |

|-------|-----|-----|-----|-----|-----|-----|-----------|

| —     | —   | —   | _   | —   | _   | —   | ULPWUIF   |

| bit 7 |     |     |     |     |     |     | bit 0     |

| Legend:           | HS = Hardware Settable bit |                             |                    |

|-------------------|----------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-1 Unimplemented: Read as '0'

bit 0 ULPWUIF: Ultra Low-Power Wake-up Interrupt Flag Status bit

1 = Interrupt request has occurred

0 = Interrupt request has not occurred

#### REGISTER 8-11: IFS6: INTERRUPT FLAG STATUS REGISTER 6

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0, HS | R/W-0, HS |

|-------|-----|-----|-----|-----|-----|-----------|-----------|

| —     | —   | —   | —   | —   | —   | CLC2IF    | CLC1IF    |

| bit 7 |     |     |     |     |     |           | bit 0     |

| Legend:           | HS = Hardware Settable bit |                             |                    |

|-------------------|----------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-2 Unimplemented: Read as '0'

bit 1 CLC2IF: Configurable Logic Cell 2 Interrupt Flag Status bit 1 = Interrupt request has occurred 0 = Interrupt request has not occurred

bit 0 CLC1IF: Configurable Logic Cell 1 Interrupt Flag Status bit

1 = Interrupt request has occurred

0 = Interrupt request has not occurred

#### REGISTER 8-17: IEC5: INTERRUPT ENABLE CONTROL REGISTER 5

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0     |

|---------|-----|-----|-----|-----|-----|-----|---------|

| —       | —   | —   | —   | —   | —   | —   | —       |

| bit 15  |     |     |     |     |     |     | bit 8   |

|         |     |     |     |     |     |     |         |

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0   |

| —       | —   | —   | —   | —   | —   | —   | ULPWUIE |

| bit 7   |     |     |     |     |     |     | bit 0   |

|         |     |     |     |     |     |     |         |

| Legend: |     |     |     |     |     |     |         |

| Logena.           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 15-1 Unimplemented: Read as '0'

bit 0 ULPWUIE: Ultra Low-Power Wake-up Interrupt Enable bit

1 = Interrupt request is enabled

0 = Interrupt request is not enabled

#### REGISTER 8-18: IEC6: INTERRUPT ENABLE CONTROL REGISTER 5

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  | R/W-0  |

|-------|-----|-----|-----|-----|-----|--------|--------|

| —     | —   | —   | —   | —   | _   | CLC2IE | CLC1IE |

| bit 7 |     |     |     |     |     |        | bit 0  |

| Legend:                           |                  |                                    |                    |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 15-2 Unimplemented: Read as '0'

bit 1 CLC2IE: Configurable Logic Cell 2 Interrupt Enable bit

1 = Interrupt request is enabled

0 = Interrupt request is not enabled

bit 0 CLC1IE: Configurable Logic Cell 1 Interrupt Enable bit

1 = Interrupt request is enabled

0 = Interrupt request is not enabled

#### 9.3 Control Registers

The operation of the oscillator is controlled by three Special Function Registers (SFRs):

- OSCCON

- CLKDIV

- OSCTUN

The OSCCON register (Register 9-1) is the main control register for the oscillator. It controls clock source switching and allows the monitoring of clock sources.

The Clock Divider register (Register 9-2) controls the features associated with Doze mode, as well as the postscaler for the FRC Oscillator.

The FRC Oscillator Tune register (Register 9-3) allows the user to fine-tune the FRC Oscillator over a range of approximately  $\pm 5.25\%$ . Each bit increment or decrement changes the factory calibrated frequency of the FRC Oscillator by a fixed amount.

#### REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER

| U-0    | R-0, HSC | R-0, HSC | R-0, HSC | U-0 | R/W-x <sup>(1)</sup> | R/W-x <sup>(1)</sup> | R/W-x <sup>(1)</sup> |

|--------|----------|----------|----------|-----|----------------------|----------------------|----------------------|

| —      | COSC2    | COSC1    | COSC0    | —   | NOSC2                | NOSC1                | NOSC0                |

| bit 15 |          |          |          |     |                      |                      | bit 8                |

| R/SO-0, HSC | U-0 | R-0, HSC <sup>(2)</sup> | U-0 | R/CO-0, HS | R/W-0 <sup>(3)</sup> | R/W-0  | R/W-0 |

|-------------|-----|-------------------------|-----|------------|----------------------|--------|-------|

| CLKLOCK     | —   | LOCK                    | —   | CF         | SOSCDRV              | SOSCEN | OSWEN |

| bit 7       |     |                         |     |            |                      |        | bit 0 |

| Legend:                    | HSC = Hardware Settable/Clearable bit |                                    |                    |  |  |  |

|----------------------------|---------------------------------------|------------------------------------|--------------------|--|--|--|

| HS = Hardware Settable bit | CO = Clearable Only bit               | SO = Settable Only bit             |                    |  |  |  |

| R = Readable bit           | W = Writable bit                      | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR          | '1' = Bit is set                      | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

| bit 15    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14-12 | COSC<2:0>: Current Oscillator Selection bits                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|           | <ul> <li>111 = 8 MHz Fast RC Oscillator with Postscaler (FRCDIV)</li> <li>110 = 500 kHz Low-Power Fast RC Oscillator (FRC) with Postscaler (LPFRCDIV)</li> <li>101 = Low-Power RC Oscillator (LPRC)</li> <li>100 = Secondary Oscillator (SOSC)</li> <li>011 = Primary Oscillator with PLL module (XTPLL, HSPLL, ECPLL)</li> <li>010 = Primary Oscillator (XT, HS, EC)</li> <li>001 = 8 MHz FRC Oscillator with Postscaler and PLL module (FRCPLL)</li> <li>000 = 8 MHz FRC Oscillator (FRC)</li> </ul> |

| bit 11    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| bit 10-8  | NOSC<2:0>: New Oscillator Selection bits <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|           | <ul> <li>111 = 8 MHz Fast RC Oscillator with Postscaler (FRCDIV)</li> <li>110 = 500 kHz Low-Power Fast RC Oscillator (FRC) with Postscaler (LPFRCDIV)</li> <li>101 = Low-Power RC Oscillator (LPRC)</li> <li>100 = Secondary Oscillator (SOSC)</li> <li>011 = Primary Oscillator with PLL module (XTPLL, HSPLL, ECPLL)</li> <li>010 = Primary Oscillator (XT, HS, EC)</li> <li>001 = 8 MHz FRC Oscillator with Postscaler and PLL module (FRCPLL)</li> <li>000 = 8 MHz FRC Oscillator (FRC)</li> </ul> |

| Note 1:   | Reset values for these bits are determined by the FNOSCx Configuration bits.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2:        | This bit also resets to '0' during any valid clock switch or whenever a non-PLL Clock mode is selected.                                                                                                                                                                                                                                                                                                                                                                                                |

**3:** When SOSC is selected to run from a digital clock input, rather than an external crystal (SOSCSRC = 0), this bit has no effect.

| R/W-0         | U-0                                                                                                                           | R/W-0                                                                                                                                                                            | R/W-0                                                                                                 | R/W-0                                    | R/W-0            | R/W-0            | R/W-0     |  |  |  |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|------------------------------------------|------------------|------------------|-----------|--|--|--|--|

| ROEN          | _                                                                                                                             | ROSSLP                                                                                                                                                                           | ROSEL                                                                                                 | RODIV3                                   | RODIV2           | RODIV1           | RODIV0    |  |  |  |  |

| bit 15        |                                                                                                                               |                                                                                                                                                                                  |                                                                                                       |                                          |                  |                  | bit       |  |  |  |  |

| U-0           | U-0                                                                                                                           | U-0                                                                                                                                                                              | U-0                                                                                                   | U-0                                      | U-0              | U-0              | U-0       |  |  |  |  |

|               |                                                                                                                               |                                                                                                                                                                                  | _                                                                                                     | _                                        |                  | _                |           |  |  |  |  |

| bit 7         |                                                                                                                               |                                                                                                                                                                                  |                                                                                                       |                                          |                  |                  | bit       |  |  |  |  |

| Legend:       |                                                                                                                               |                                                                                                                                                                                  |                                                                                                       |                                          |                  |                  |           |  |  |  |  |

| R = Readable  | e bit                                                                                                                         | W = Writable I                                                                                                                                                                   | oit                                                                                                   | U = Unimplem                             | nented bit, read | 1 as '0'         |           |  |  |  |  |

| -n = Value at | POR                                                                                                                           | '1' = Bit is set                                                                                                                                                                 |                                                                                                       | '0' = Bit is clea                        |                  | x = Bit is unkr  | iown      |  |  |  |  |

| bit 15        | 1 = Reference                                                                                                                 | ence Oscillator<br>e Oscillator is e<br>e Oscillator is d                                                                                                                        | nabled on the                                                                                         |                                          |                  |                  |           |  |  |  |  |

| bit 14        | Unimplemented: Read as '0'                                                                                                    |                                                                                                                                                                                  |                                                                                                       |                                          |                  |                  |           |  |  |  |  |

| bit 13        | ROSSLP: Reference Oscillator Output Stop in Sleep bit                                                                         |                                                                                                                                                                                  |                                                                                                       |                                          |                  |                  |           |  |  |  |  |

|               | <ul> <li>1 = Reference Oscillator continues to run in Sleep</li> <li>0 = Reference Oscillator is disabled in Sleep</li> </ul> |                                                                                                                                                                                  |                                                                                                       |                                          |                  |                  |           |  |  |  |  |

| bit 12        | ROSEL: Reference Oscillator Source Select bit                                                                                 |                                                                                                                                                                                  |                                                                                                       |                                          |                  |                  |           |  |  |  |  |

|               | 1 = Primary (<br>0 = System c                                                                                                 | Oscillator is use<br>clock is used as                                                                                                                                            | d as the base the base cloc                                                                           | clock <sup>(1)</sup><br>k; base clock re | flects any cloc  | k switching of t | he device |  |  |  |  |

| bit 11-8      | 1111 = Base<br>1110 = Base<br>1101 = Base<br>1100 = Base                                                                      | Reference Osi<br>clock value divi<br>clock value divi<br>clock value divi<br>clock value divi<br>clock value divi<br>clock value divi                                            | ded by 32,768<br>ded by 16,384<br>ded by 8,192<br>ded by 4,096<br>ded by 2,048                        | 3                                        |                  |                  |           |  |  |  |  |

|               | 1001 = Base<br>1000 = Base<br>0111 = Base<br>0110 = Base<br>0101 = Base<br>0100 = Base<br>0011 = Base<br>0010 = Base          | clock value divi<br>clock value divi | ded by 512<br>ded by 256<br>ded by 128<br>ded by 64<br>ded by 32<br>ded by 16<br>ded by 8<br>ded by 4 |                                          |                  |                  |           |  |  |  |  |

#### REGISTER 9-4: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

**Note 1:** The crystal oscillator must be enabled using the FOSC<2:0> bits; the crystal maintains the operation in Sleep mode.

### **10.0 POWER-SAVING FEATURES**

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the *"PIC24F Family Reference Manual"*, "Power-Saving Features with VBAT" (DS30622).

This FRM describes some features which

are not implemented in this device. Sections related to the VBAT pin and Deep Sleep do not apply to the PIC24FV16KM204 family.

The PIC24FV16KM204 family of devices provides the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of circuits being clocked constitutes lower consumed power. All PIC24F devices manage power consumption in four different ways:

- Clock Frequency

- Instruction-Based Sleep and Idle modes

- · Software Controlled Doze mode

- Selective Peripheral Control in Software

Combinations of these methods can be used to selectively tailor an application's power consumption, while still maintaining critical application features, such as timing-sensitive communications.

### 10.1 Clock Frequency and Clock Switching

PIC24F devices allow for a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or high-precision oscillators by simply changing the NOSCx bits. The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in **Section 9.0** "Oscillator Configuration".

#### 10.2 Instruction-Based Power-Saving Modes

PIC24F devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution; Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The 'C' syntax of the  $\ensuremath{\mathtt{PWRSAV}}$  instruction is shown in Example 10-1.

Note: SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to "wake-up".

#### 10.2.1 SLEEP MODE

Sleep mode includes these features:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption will be reduced to a minimum provided that no I/O pin is sourcing current.

- The I/O pin directions and states are frozen.

- The Fail-Safe Clock Monitor does not operate during Sleep mode since the system clock source is disabled.

- The LPRC clock will continue to run in Sleep mode if the WDT or RTCC with LPRC as the clock source is enabled.

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode.

- Some device features or peripherals may continue to operate in Sleep mode. This includes items, such as the Input Change Notification on the I/O ports or peripherals that use an External Clock input. Any peripheral that requires the system clock source for its operation will be disabled in Sleep mode.

The device will wake-up from Sleep mode on any of these events:

- On any interrupt source that is individually enabled

- · On any form of device Reset

- · On a WDT time-out

On wake-up from Sleep, the processor will restart with the same clock source that was active when Sleep mode was entered.

#### EXAMPLE 10-1: 'C' POWER-SAVING ENTRY

| R/W-0         | U-0                                                                                              | R/W-0                                                         | R/W-0                            | R/W-0                             | R/W-0                | R/W-0                                                  | R/W-0    |  |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------|----------------------------------|-----------------------------------|----------------------|--------------------------------------------------------|----------|--|--|--|--|

| OENSYNC       |                                                                                                  | OCFEN <sup>(1)</sup>                                          | OCEEN <sup>(1)</sup>             | OCDEN <sup>(1)</sup>              | OCCEN <sup>(1)</sup> | OCBEN <sup>(1)</sup>                                   | OCAEN    |  |  |  |  |

| bit 15        |                                                                                                  |                                                               |                                  |                                   |                      |                                                        | bit      |  |  |  |  |

| R/W-0         | R/W-0                                                                                            | U-0                                                           | R/W-0                            | R/W-0                             | R/W-0                | R/W-0                                                  | R/W-0    |  |  |  |  |

| ICGSM1        | ICGSM0                                                                                           | _                                                             | AUXOUT1                          | AUXOUT0                           | ICS2                 | ICS1                                                   | ICS0     |  |  |  |  |

| bit 7         |                                                                                                  |                                                               |                                  |                                   |                      | 1                                                      | bit      |  |  |  |  |

| Legend:       |                                                                                                  |                                                               |                                  |                                   |                      |                                                        |          |  |  |  |  |

| R = Readable  | e bit                                                                                            | W = Writable                                                  | bit                              | U = Unimplem                      | nented bit, read     | 1 as '0'                                               |          |  |  |  |  |

| -n = Value at | POR                                                                                              | '1' = Bit is set                                              |                                  | '0' = Bit is clea                 | ared                 | x = Bit is unkn                                        | own      |  |  |  |  |

| bit 15        | 1 = Update b                                                                                     | Dutput Enable S<br>by output enable<br>by output enable       | e bits occurs or                 | n the next Time                   | Base Reset or        | rollover                                               |          |  |  |  |  |

| bit 14        | Unimplemen                                                                                       | ted: Read as '                                                | )'                               |                                   |                      |                                                        |          |  |  |  |  |

| bit 13-8      | 1 = OCx pin<br>0 = OCx pin                                                                       |                                                               | the CCPx moded by the CCP        | dule and produc                   |                      | compare or PWI<br>e to the port log                    |          |  |  |  |  |

| bit 7-6       | ICGSM<1:0>: Input Capture Gating Source Mode Control bits                                        |                                                               |                                  |                                   |                      |                                                        |          |  |  |  |  |

|               | 01 = One-Sh<br>00 = Level-Se                                                                     | ot mode: Falling<br>ot mode: Rising                           | edge from gat<br>A high level fr | ting source ena<br>om gating sour | bles future cap      | pture events (IC<br>oture events (IC<br>future capture | DIS = 0) |  |  |  |  |

| bit 5         | Unimplemen                                                                                       | ted: Read as '                                                | )'                               |                                   |                      |                                                        |          |  |  |  |  |

| bit 4-3       | AUXOUT<1:0                                                                                       | <b>0&gt;:</b> Auxiliary Oເ                                    | tput Signal on                   | Event Selectio                    | n bits               |                                                        |          |  |  |  |  |

|               | 10 = Signal c                                                                                    | pture or output<br>output is defined<br>ise rollover eve<br>d | l by module op                   |                                   |                      | )                                                      |          |  |  |  |  |

| bit 2-0       | 111 = Unuse<br>110 = CLC2<br>101 = CLC1<br>100 = Unuse<br>011 = Comp<br>010 = Comp<br>001 = Comp | output<br>output                                              |                                  | 3                                 |                      |                                                        |          |  |  |  |  |

#### REGISTER 13-4: CCPxCON2H: CCPx CONTROL 2 HIGH REGISTERS

#### **Note 1:** OCFEN through OCBEN (bits<13:9>) are implemented in MCCPx modules only.

#### 15.1 UARTx Baud Rate Generator (BRG)

The UARTx module includes a dedicated 16-bit Baud Rate Generator (BRG). The UxBRG register controls the period of a free-running, 16-bit timer. Equation 15-1 provides the formula for computation of the baud rate with BRGH = 0.

### EQUATION 15-1: UARTX BAUD RATE WITH BRGH = $0^{(1)}$

Baud Rate =  $\frac{FCY}{16 \cdot (UxBRG + 1)}$   $UxBRG = \frac{FCY}{16 \cdot Baud Rate} - 1$ Note 1: Based on FCY = FOSC/2; Doze mode and PLL are disabled.

Example 15-1 provides the calculation of the baud rate error for the following conditions:

- Fcy = 4 MHz

- Desired Baud Rate = 9600

The maximum baud rate (BRGH = 0) possible is FCY/16 (for UxBRG = 0) and the minimum baud rate possible is FCY/(16 \* 65536).

Equation 15-2 shows the formula for computation of the baud rate with BRGH = 1.

### EQUATION 15-2: UARTx BAUD RATE WITH BRGH = $1^{(1)}$

|      | Ba | ud Rate = | $\frac{FCY}{4 \bullet (UxBRG + 1)}$ |          |

|------|----|-----------|-------------------------------------|----------|

|      | Ux | BRG =     | FCY<br>4 • Baud Rate                | - 1      |

| Note | 1: |           | n Fcy = Fosc/2; D<br>are disabled.  | oze mode |

The maximum baud rate (BRGH = 1) possible is FcY/4 (for UxBRG = 0) and the minimum baud rate possible is FcY/(4 \* 65536).

Writing a new value to the UxBRG register causes the BRG timer to be reset (cleared). This ensures the BRG does not wait for a timer overflow before generating the new baud rate.

#### EXAMPLE 15-1: BAUD RATE ERROR CALCULATION (BRGH = 0)<sup>(1)</sup>

| Desired Baud Rate    | =   | FCY/(16 (UxBRG + 1))                                                                  |

|----------------------|-----|---------------------------------------------------------------------------------------|

| Solving for UxBRG va | lue | :                                                                                     |

| UxBRG<br>UxBRG       | =   | ((FCY/Desired Baud Rate)/16) – 1<br>((4000000/9600)/16) – 1                           |

| UxBRG                |     | 25                                                                                    |

| Calculated Baud Rate |     | 4000000/(16 (25 + 1))<br>9615                                                         |

| Error                |     | (Calculated Baud Rate – Desired Baud Rate)<br>Desired Baud Rate<br>(9615 – 9600)/9600 |

|                      | =   | 0.16%                                                                                 |

| Note 1: Based on     | Fc  | Y = FOSC/2; Doze mode and PLL are disabled.                                           |

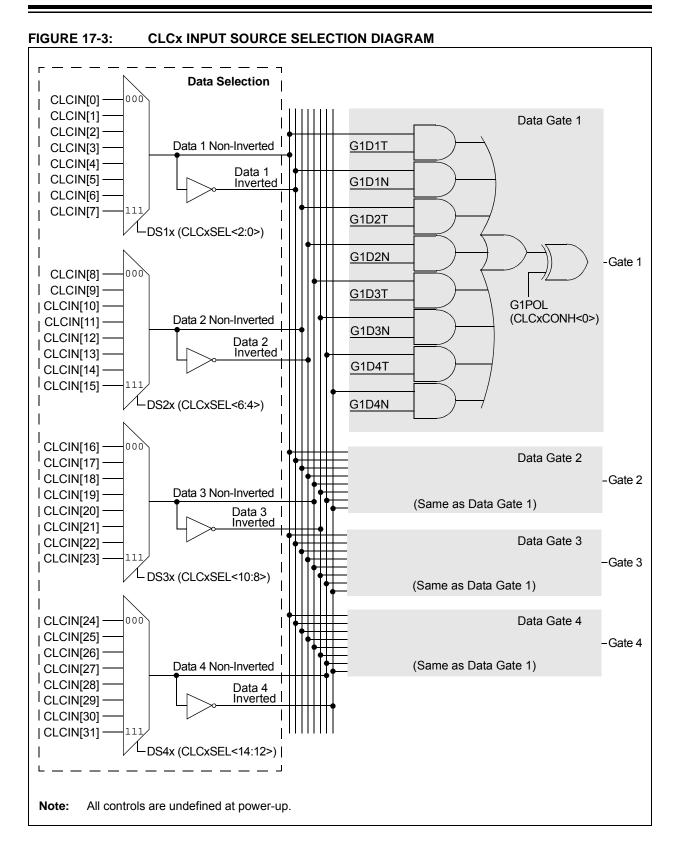

#### REGISTER 17-5: CLCxGLSH: CLCx GATE LOGIC INPUT SELECT HIGH REGISTER

| R/W-0                   | R/W-0                                                                                                                                              | R/W-0                            | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0 |  |  |  |  |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|------------------|------------------|------------------|-----------------|-------|--|--|--|--|

| G4D4T                   | G4D4N                                                                                                                                              | G4D3T                            | G4D3N            | G4D2T            | G4D2N            | G4D1T           | G4D1N |  |  |  |  |

| bit 15                  |                                                                                                                                                    |                                  |                  |                  |                  |                 | bit 8 |  |  |  |  |

|                         |                                                                                                                                                    |                                  |                  |                  |                  |                 |       |  |  |  |  |

| R/W-0                   | R/W-0                                                                                                                                              | R/W-0                            | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0 |  |  |  |  |

| G3D4T                   | G3D4N                                                                                                                                              | G3D3T                            | G3D3N            | G3D2T            | G3D2N            | G3D1T           | G3D1N |  |  |  |  |

| bit 7                   |                                                                                                                                                    |                                  |                  |                  |                  |                 | bit 0 |  |  |  |  |

| Logondy                 |                                                                                                                                                    |                                  |                  |                  |                  |                 |       |  |  |  |  |

| Legend:<br>R = Readable | , bit                                                                                                                                              | W = Writable                     | oit              | II – Unimplor    | nented bit, read | d ac '0'        |       |  |  |  |  |

| -n = Value at           |                                                                                                                                                    | '1' = Bit is set                 | JIL              | '0' = Bit is cle |                  | x = Bit is unkr |       |  |  |  |  |

|                         | FOR                                                                                                                                                | i – Dit is set                   |                  |                  | areu             |                 | IOWIT |  |  |  |  |

| bit 15                  | G4D4T: Gate                                                                                                                                        | 4 Data Source                    | 4 True Enable    | e bit            |                  |                 |       |  |  |  |  |

|                         | <b>G4D4T:</b> Gate 4 Data Source 4 True Enable bit<br>1 = The Data Source 4 inverted signal is enabled for Gate 4                                  |                                  |                  |                  |                  |                 |       |  |  |  |  |

|                         | <ul> <li>a The Data Source 4 inverted signal is disabled for Gate 4</li> <li>a The Data Source 4 inverted signal is disabled for Gate 4</li> </ul> |                                  |                  |                  |                  |                 |       |  |  |  |  |

| bit 14                  | G4D4N: Gate                                                                                                                                        | e 4 Data Source                  | 4 Negated Er     | nable bit        |                  |                 |       |  |  |  |  |

|                         |                                                                                                                                                    | Source 4 inver                   |                  |                  |                  |                 |       |  |  |  |  |

|                         |                                                                                                                                                    | Source 4 inver                   | •                |                  | e 4              |                 |       |  |  |  |  |

| bit 13                  | <b>G4D3T:</b> Gate 4 Data Source 3 True Enable bit<br>1 = The Data Source 3 inverted signal is enabled for Gate 4                                  |                                  |                  |                  |                  |                 |       |  |  |  |  |

|                         |                                                                                                                                                    | Source 3 inver<br>Source 3 inver |                  |                  |                  |                 |       |  |  |  |  |

| bit 12                  |                                                                                                                                                    |                                  | •                |                  |                  |                 |       |  |  |  |  |

|                         | <b>G4D3N:</b> Gate 4 Data Source 3 Negated Enable bit<br>1 = The Data Source 3 inverted signal is enabled for Gate 4                               |                                  |                  |                  |                  |                 |       |  |  |  |  |

|                         |                                                                                                                                                    | Source 3 inver                   | •                |                  |                  |                 |       |  |  |  |  |

| bit 11                  | G4D2T: Gate                                                                                                                                        | 4 Data Source                    | 2 True Enable    | e bit            |                  |                 |       |  |  |  |  |

|                         |                                                                                                                                                    | Source 2 inver                   |                  |                  |                  |                 |       |  |  |  |  |

| hit 10                  |                                                                                                                                                    | Source 2 inver                   | -                |                  | 94               |                 |       |  |  |  |  |

| bit 10                  | <b>G4D2N:</b> Gate 4 Data Source 2 Negated Enable bit<br>1 = The Data Source 2 inverted signal is enabled for Gate 4                               |                                  |                  |                  |                  |                 |       |  |  |  |  |

|                         |                                                                                                                                                    | Source 2 inver                   |                  |                  |                  |                 |       |  |  |  |  |

| bit 9                   |                                                                                                                                                    | 4 Data Source                    | •                |                  |                  |                 |       |  |  |  |  |

|                         | 1 = The Data                                                                                                                                       | Source 1 inver                   | ted signal is ei | nabled for Gate  | e 4              |                 |       |  |  |  |  |

|                         | 0 = The Data                                                                                                                                       | Source 1 inver                   | ted signal is di | sabled for Gate  | e 4              |                 |       |  |  |  |  |

| bit 8                   | G4D1N: Gate                                                                                                                                        | e 4 Data Source                  | 1 Negated Er     | nable bit        |                  |                 |       |  |  |  |  |

|                         |                                                                                                                                                    | Source 1 inver                   |                  |                  |                  |                 |       |  |  |  |  |

| hit 7                   |                                                                                                                                                    | Source 1 inver                   | -                |                  | 9 4              |                 |       |  |  |  |  |

| bit 7                   |                                                                                                                                                    | 3 Data Source                    |                  |                  | . 2              |                 |       |  |  |  |  |

|                         |                                                                                                                                                    | Source 4 inver<br>Source 4 inver |                  |                  |                  |                 |       |  |  |  |  |

| bit 6                   |                                                                                                                                                    | e 3 Data Source                  | -                |                  |                  |                 |       |  |  |  |  |

|                         |                                                                                                                                                    | Source 4 inver                   | -                |                  | 93               |                 |       |  |  |  |  |

|                         | 0 = The Data                                                                                                                                       | Source 4 inver                   | ted signal is di | sabled for Gate  | e 3              |                 |       |  |  |  |  |

| bit 5                   | G3D3T: Gate                                                                                                                                        | 3 Data Source                    | 3 True Enable    | e bit            |                  |                 |       |  |  |  |  |

|                         |                                                                                                                                                    | Source 3 inver                   |                  |                  |                  |                 |       |  |  |  |  |

| 1.11.4                  |                                                                                                                                                    | Source 3 inver                   | -                |                  | 93               |                 |       |  |  |  |  |

| bit 4                   | G3D3N: Gate                                                                                                                                        | e 3 Data Source                  | 3 Negated Er     | hable bit        |                  |                 |       |  |  |  |  |

|                         |                                                                                                                                                    | Source 3 inver                   |                  |                  |                  |                 |       |  |  |  |  |

### REGISTER 19-7: AD1CHITL: A/D SCAN COMPARE HIT REGISTER (LOW WORD)<sup>(1)</sup>

| R/W-0                              | R/W-0                     | R/W-0               | R/W-0                     | R/W-0                                   | R/W-0            | R/W-0    | R/W-0                 |  |

|------------------------------------|---------------------------|---------------------|---------------------------|-----------------------------------------|------------------|----------|-----------------------|--|

| CHH15                              | CHH14                     | CHH13               | CHH12                     | CHH11                                   | CHH10            | CHH9     | CHH8 <sup>(2,3)</sup> |  |

| bit 15                             |                           |                     |                           |                                         |                  |          | bit 8                 |  |

|                                    |                           |                     |                           |                                         |                  |          |                       |  |

| R/W-0                              | R/W-0                     | R/W-0               | R/W-0                     | R/W-0                                   | R/W-0            | R/W-0    | R/W-0                 |  |

| CHH7 <sup>(2,3)</sup>              | CHH6 <sup>(2,3)</sup>     | CHH5 <sup>(2)</sup> | CHH4                      | CHH3                                    | CHH2             | CHH1     | CHH0                  |  |

| bit 7                              |                           |                     |                           |                                         | ·                |          | bit 0                 |  |

|                                    |                           |                     |                           |                                         |                  |          |                       |  |

| Legend:                            |                           |                     |                           |                                         |                  |          |                       |  |

| R = Readable                       | e bit                     | W = Writable b      | pit                       | U = Unimpler                            | nented bit, read | d as '0' |                       |  |

| -n = Value at POR '1' = Bit is set |                           |                     |                           | '0' = Bit is cleared x = Bit is unknown |                  |          |                       |  |

|                                    |                           |                     |                           |                                         |                  |          |                       |  |

| bit 15-0                           | CHH<15:0>:                | A/D Compare H       | lit bits <sup>(2,3)</sup> |                                         |                  |          |                       |  |

|                                    | <u>If CM&lt;1:0&gt; =</u> | <u>11:</u>          |                           |                                         |                  |          |                       |  |

|                                    | 1 = A/D Res               | ult Buffer x has    | been written              | with data or a m                        | atch has occur   | red      |                       |  |

0 = A/D Result Buffer x has not been written with data

For All Other Values of CM<1:0>:

1 = A match has occurred on A/D Result Channel x

0 = No match has occurred on A/D Result Channel x

#### Note 1: Unimplemented channels are read as '0'.

2: The CHH<8:5> bits are not implemented in 20-pin devices.

**3:** The CHH<8:6> bits are not implemented in 28-pin devices.

#### REGISTER 22-1: CMxCON: COMPARATOR x CONTROL REGISTERS (CONTINUED)

- bit 2 Unimplemented: Read as '0'