Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                      |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 23                                                                            |

| Program Memory Size        | 8KB (2.75K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5V                                                                       |

| Data Converters            | A/D 19x10b/12b; D/A 2x8b                                                      |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-VQFN Exposed Pad                                                           |

| Supplier Device Package    | 28-QFN (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fv08km202-e-ml |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Pin Diagrams**

| 20-Pin PDIP/SSOP/SOIC | RA5       1       20       VDD         RA0       2       19       VSs         RA1       3       18       RB15         RB0       4       17       RB14         RB1       5       RB12         RA2       6       9       16         RA3       8       00       VDC         RA4       10       11       RB7 |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Dia |                                               | Pin Features                               |  |  |  |  |  |  |  |  |  |  |

|-----|-----------------------------------------------|--------------------------------------------|--|--|--|--|--|--|--|--|--|--|

| Pin | PIC24F08KM101                                 | PIC24FVKM08KM101                           |  |  |  |  |  |  |  |  |  |  |

| 1   | MCLR/Vpp/RA5                                  |                                            |  |  |  |  |  |  |  |  |  |  |

| 2   | PGEC2/CVREF+/VREF+/AN0/CN2/RA0                |                                            |  |  |  |  |  |  |  |  |  |  |

| 3   | PGED2/CVREF-/VREF-/AN1/CN3/RA1                |                                            |  |  |  |  |  |  |  |  |  |  |

| 4   | PGED1/AN2/CTCMP/ULPWU/C1IND/OC2A/CN4/RB0      |                                            |  |  |  |  |  |  |  |  |  |  |

| 5   | PGEC1/AN3/C1INC/CTED12/CN5/RB1                |                                            |  |  |  |  |  |  |  |  |  |  |

| 6   | AN4/U1RX/TCKIB/CTED13/CN6/RB2                 |                                            |  |  |  |  |  |  |  |  |  |  |

| 7   | OSCI/CLKI/AN13/C1INB/CN30/RA2                 |                                            |  |  |  |  |  |  |  |  |  |  |

| 8   | OSCO/CLKO/AN14/C1INA/CN29/RA3                 |                                            |  |  |  |  |  |  |  |  |  |  |

| 9   | PGED3/SOSCI/AN15/CLCINA/CN1/RB4               |                                            |  |  |  |  |  |  |  |  |  |  |

| 10  | PGEC3/SOSCO/SCLKI/AN16/PWRLCLK/CLCINB/CN0/    | RA4                                        |  |  |  |  |  |  |  |  |  |  |

| 11  | AN19/U1TX/CTED1/INT0/CN23/RB7                 | AN19/U1TX/IC1/OC1A/CTED1/INT0/CN23/RB7     |  |  |  |  |  |  |  |  |  |  |

| 12  | AN20/SCL1/U1CTS/OC1B/CTED10/CN22/RB8          |                                            |  |  |  |  |  |  |  |  |  |  |

| 13  | AN21/SDA1/T1CK/U1RTS/U1BCLK/IC2/CLC10/CTED4   | /CN21/RB9                                  |  |  |  |  |  |  |  |  |  |  |

| 14  | IC1/OC1A/INT2/CN8/RA6                         | VCAP OR VDDCORE                            |  |  |  |  |  |  |  |  |  |  |

| 15  | AN12/HLVDIN/SCK1/OC1C/CTED2/CN14/RB12         | AN12/HLVDIN/SCK1/OC1C/CTED2/INT2/CN14/RB12 |  |  |  |  |  |  |  |  |  |  |

| 16  | AN11/SDO1/OCFB/OC1D/CTPLS/CN13/RB13           |                                            |  |  |  |  |  |  |  |  |  |  |

| 17  | CVREF/AN10/SDI1/C1OUT/OCFA/CTED5/INT1/CN12/RE | 814                                        |  |  |  |  |  |  |  |  |  |  |

| 18  | AN9/REFO/SS1/TCKIA/CTED6/CN11/RB15            |                                            |  |  |  |  |  |  |  |  |  |  |

| 19  | Vss/AVss                                      |                                            |  |  |  |  |  |  |  |  |  |  |

| 20  | Vdd/AVdd                                      |                                            |  |  |  |  |  |  |  |  |  |  |

### TABLE 1-2: DEVICE FEATURES FOR THE PIC24F16KM104 FAMILY

|                                                     |                                          |                    |                       | 1                                        |

|-----------------------------------------------------|------------------------------------------|--------------------|-----------------------|------------------------------------------|

| Features                                            | PIC24F16KM104                            | PIC24F16KM102      | PIC24F08KM102         | PIC24F08KM101                            |

| Operating Frequency                                 |                                          | DC-3               | 2 MHz                 |                                          |

| Program Memory (bytes)                              | 16K                                      | 16K                | 8K                    | 8K                                       |

| Program Memory (instructions)                       | 5632                                     | 5632               | 2816                  | 2816                                     |

| Data Memory (bytes)                                 |                                          | 10                 | 24                    |                                          |

| Data EEPROM Memory (bytes)                          |                                          | 5                  | 12                    |                                          |

| Interrupt Sources (soft vectors/NMI traps)          |                                          | 25 (2              | 21/4)                 |                                          |

| Voltage Range                                       |                                          | 1.8-               | 3.6V                  |                                          |

| I/O Ports                                           | PORTA<11:0><br>PORTB<15:0><br>PORTC<9:0> | PORTA<br>PORTB     |                       | PORTA<6:0><br>PORTB<15:12,9:7,<br>4,2:0> |

| Total I/O Pins                                      | 38                                       | 24                 | ŀ                     | 18                                       |

| Timers                                              | (One 16-bit timer, t                     |                    | 5<br>Ps with up to tv | vo 16/32 timers each)                    |

| Capture/Compare/PWM modules<br>MCCP<br>SCCP         |                                          |                    | 1                     |                                          |

| Serial Communications<br>MSSP<br>UART               |                                          |                    | 1                     |                                          |

| Input Change Notification Interrupt                 | 37                                       | 23                 | }                     | 17                                       |

| 12-Bit Analog-to-Digital Module<br>(input channels) | 22                                       | 19                 | )                     | 16                                       |

| Analog Comparators                                  |                                          |                    | 1                     |                                          |

| 8-Bit Digital-to-Analog Converters                  |                                          | _                  | _                     |                                          |

| Operational Amplifiers                              |                                          | -                  | _                     |                                          |

| Charge Time Measurement Unit (CTMU)                 |                                          | Y                  | es                    |                                          |

| Real-Time Clock and Calendar (RTCC)                 |                                          | -                  | _                     |                                          |

| Configurable Logic Cell (CLC)                       |                                          |                    | 1                     |                                          |

| Resets (and delays)                                 |                                          |                    |                       | , Illegal Opcode,<br>tion Word Mismatch  |

| Instruction Set                                     | 76 Base Inst                             | ructions, Multiple | e Addressing N        | Iode Variations                          |

| Packages                                            | 44-Pin<br>QFN/TQFP,<br>48-Pin UQFN       | 28-F<br>SPDIP/SSOP |                       | 20-Pin<br>SOIC/SSOP/PDIP                 |

### TABLE 4-6: TIMER1 REGISTER MAP

|           |       |        | -            | -      |        |        |        |                |        |              |       |        |        |       |       |       |       |               |

|-----------|-------|--------|--------------|--------|--------|--------|--------|----------------|--------|--------------|-------|--------|--------|-------|-------|-------|-------|---------------|

| File Name | Addr. | Bit 15 | Bit 14       | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9          | Bit 8  | Bit 7        | Bit 6 | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| TMR1      | 100h  |        |              |        |        |        |        |                | Time   | er1 Register |       |        |        |       |       |       |       | xxxx          |

| PR1       | 102h  |        |              |        |        |        |        |                | Timer1 | Period Regis | ster  |        |        |       |       |       |       | FFFF          |

| T1CON     | 104h  | TON    | —            | TSIDL  | _      | _      | _      | TECS1          | TECS0  | _            | TGATE | TCKPS1 | TCKPS0 | _     | TSYNC | TCS   | _     | 0000          |

| Lanandi   |       |        | le ave a a d |        |        |        |        | and the second |        |              |       |        |        |       |       |       |       |               |

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition, r = reserved.

### TABLE 4-7: CLC1-2 REGISTER MAP

| File Name               | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| CLC1CONL                | 122h  | LCEN   | —      | _      | —      | INTP   | INTN   | —     | —     | LCOE  | LCOUT | LCPOL | —     | _     | MODE2 | MODE1 | MODE0 | 0000          |

| CLC1CONH                | 124h  | _      | _      |        | _      | _      | _      | _     | _     | _     | _     | _     | _     | G4POL | G3POL | G2POL | G1POL | 0000          |

| CLC1SEL                 | 126h  | _      | DS42   | DS41   | DS40   |        | DS32   | DS31  | DS30  | —     | DS22  | DS21  | DS20  | _     | DS12  | DS11  | DS10  | 0000          |

| CLC1GLSL                | 12Ah  | G2D4T  | G2D4N  | G2D3T  | G2D3N  | G2D2T  | G2D2N  | G2D1T | G2D1N | G1D4T | G1D4N | G1D3T | G1D3N | G1D2T | G1D2N | G1D1T | G1D1N | 0000          |

| CLC1GLSH                | 12Ch  | G4D4T  | G4D4N  | G4D3T  | G4D3N  | G4D2T  | G4D2N  | G4D1T | G4D1N | G3D4T | G3D4N | G3D3T | G3D3N | G3D2T | G3D2N | G3D1T | G3D1N | 0000          |

| CLC2CONL <sup>(1)</sup> | 12Eh  | LCEN   | _      | -      | _      | INTP   | INTN   | _     | _     | LCOE  | LCOUT | LCPOL | _     | _     | MODE2 | MODE1 | MODE0 | 0000          |

| CLC2CONH <sup>(1)</sup> | 130h  | —      | —      | _      | —      | _      | _      | —     | _     | _     | _     | _     | —     | G4POL | G3POL | G2POL | G1POL | 0000          |

| CLC2SEL <sup>(1)</sup>  | 132h  | —      | DS42   | DS41   | DS40   | _      | DS32   | DS31  | DS30  | _     | DS22  | DS21  | DS20  | —     | DS12  | DS11  | DS10  | 0000          |

| CLC2GLSL <sup>(1)</sup> | 136h  | G2D4T  | G2D4N  | G2D3T  | G2D3N  | G2D2T  | G2D2N  | G2D1T | G2D1N | G1D4T | G1D4N | G1D3T | G1D3N | G1D2T | G1D2N | G1D1T | G1D1N | 0000          |

| CLC2GLSH <sup>(1)</sup> | 138h  | G4D4T  | G4D4N  | G4D3T  | G4D3N  | G4D2T  | G4D2N  | G4D1T | G4D1N | G3D4T | G3D4N | G3D3T | G3D3N | G3D2T | G3D2N | G3D1T | G3D1N | 0000          |

**Legend:** x = unknown, u = unchanged, --- = unimplemented, q = value depends on condition, r = reserved.

Note 1: These registers are available only on PIC24F(V)16KM2XX devices.

### TABLE 4-21: PORTA REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 <sup>(4,5)</sup> | Bit 10 <sup>(4,5)</sup> | Bit 9 <sup>(4,5)</sup> | Bit 8 <sup>(4,5)</sup> | Bit 7 <sup>(4)</sup> | Bit 6 <sup>(3)</sup> | Bit 5 <sup>(2)</sup> | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets       |

|-----------|-------|--------|--------|--------|--------|-------------------------|-------------------------|------------------------|------------------------|----------------------|----------------------|----------------------|--------|--------|--------|--------|--------|---------------------|

| TRISA     | 2C0h  |        | _      | _      | _      | TRISA11                 | TRISA10                 | TRISA9                 | TRISA8                 | TRISA7               | TRISA6               | _                    | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 0FDF <sup>(1)</sup> |

| PORTA     | 2C2h  | _      | —      | —      |        | RA11                    | RA10                    | RA9                    | RA8                    | RA7                  | RA6                  | RA5                  | RA4    | RA3    | RA2    | RA1    | RA0    | xxxx                |

| LATA      | 2C4h  | _      | —      | —      |        | LATA11                  | LATA10                  | LATA9                  | LATA8                  | LATA7                | LATA6                | _                    | LATA4  | LATA3  | LATA2  | LATA1  | LATA0  | xxxx                |

| ODCA      | 2C6h  | _      | _      | _      | _      | ODA11                   | ODA10                   | ODA9                   | ODA8                   | ODA7                 | ODA6                 | _                    | ODA4   | ODA3   | ODA2   | ODA1   | ODA0   | 0000                |

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition, r = reserved.

Note 1: Reset value depends on the device type; the PIC24F16KM204 value is shown.

2: These bits are only available when MCLRE (FPOR<7>) = 0.

3: These bits are not implemented in FV devices.

4: These bits are not implemented in 20-pin devices.

5: These bits are not implemented in 28-pin devices.

### TABLE 4-22: PORTB REGISTER MAP

| File Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11 <sup>(2)</sup> | Bit 10 <sup>(2)</sup> | Bit 9  | Bit 8  | Bit 7  | Bit 6 <sup>(2)</sup> | Bit 5 <sup>(2)</sup> | Bit 4  | Bit 3 <sup>(2)</sup> | Bit 2  | Bit 1  | Bit 0  | All<br>Resets       |

|-----------|-------|---------|---------|---------|---------|-----------------------|-----------------------|--------|--------|--------|----------------------|----------------------|--------|----------------------|--------|--------|--------|---------------------|

| TRISB     | 2C8h  | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11               | TRISB10               | TRISB9 | TRISB8 | TRISB7 | TRISB6               | TRISB5               | TRISB4 | TRISB3               | TRISB2 | TRISB1 | TRISB0 | <sub>FFFF</sub> (1) |

| PORTB     | 2CAh  | RB15    | RB14    | RB13    | RB12    | RB11                  | RB10                  | RB9    | RB8    | RB7    | RB6                  | RB5                  | RB4    | RB3                  | RB2    | RB1    | RB0    | xxxx                |

| LATB      | 2CCh  | LATB15  | LATB14  | LATB13  | LATB12  | LATB11                | LATB10                | LATB9  | LATB8  | LATB7  | LATB6                | LATB5                | LATB4  | LATB3                | LATB2  | LATB1  | LATB0  | xxxx                |

| ODCB      | 2CEh  | ODB15   | ODB14   | ODB13   | ODB12   | ODB11                 | ODB10                 | ODB9   | ODB8   | ODB7   | ODB6                 | ODB5                 | ODB4   | ODB3                 | ODB2   | ODB1   | ODB0   | 0000                |

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition, r = reserved.

Note 1: Reset value depends on the device type; the PIC24F16KM204 value is shown.

2: These bits are not implemented in 20-pin devices.

### TABLE 4-23: PORTC REGISTER MAP

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 <sup>(2,3)</sup> | Bit 8 <sup>(2,3)</sup> | Bit 7 <sup>(2,3)</sup> | Bit 6 <sup>(2,3)</sup> | Bit 5 <sup>(2,3)</sup> | Bit 4 <sup>(2,3)</sup> | Bit 3 <sup>(2,3)</sup> | Bit 2 <sup>(2,3)</sup> | Bit 1 <sup>(2,3)</sup> | Bit 0 <sup>(2,3)</sup> | All<br>Resets       |

|--------------|-------|--------|--------|--------|--------|--------|--------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|---------------------|

| TRISC        | 2D0h  | _      | _      |        | _      | —      | _      | TRISC9                 | TRISC8                 | TRISC7                 | TRISC6                 | TRISC5                 | TRISC4                 | TRISC3                 | TRISC2                 | TRISC1                 | TRISC0                 | 03FF <sup>(1)</sup> |

| PORTC        | 2D2h  | —      | _      | _      | -      | —      | _      | RC9                    | RC8                    | RC7                    | RC6                    | RC5                    | RC4                    | RC3                    | RC2                    | RC1                    | RC0                    | xxxx                |

| LATTC        | 2D4h  | —      | _      | _      | -      | —      | _      | LATC9                  | LATC8                  | LATC7                  | LATC6                  | LATC5                  | LATC4                  | LATC3                  | LATC2                  | LATC1                  | LATC0                  | xxxx                |

| ODCC         | 2D6h  | _      | _      | —      | -      | —      | _      | ODC9                   | ODC8                   | ODC7                   | ODC6                   | ODC5                   | ODC4                   | ODC3                   | ODC2                   | ODC1                   | ODC0                   | 0000                |

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

Note 1: Reset value depends on the device type; the PIC24F16KM204 value is shown.

**2:** These bits are not implemented in 20-pin devices.

3: These bits are not implemented in 28-pin devices.

### 6.4.1 ERASE DATA EEPROM

The data EEPROM can be fully erased, or can be partially erased, at three different sizes: one word, four words or eight words. The bits, NVMOP<1:0> (NVMCON<1:0>), decide the number of words to be erased. To erase partially from the data EEPROM, the following sequence must be followed:

- 1. Configure NVMCON to erase the required number of words: one, four or eight.

- 2. Load TBLPAG and WREG with the EEPROM address to be erased.

- 3. Clear the NVMIF status bit and enable the NVM interrupt (optional).

- 4. Write the key sequence to NVMKEY.

- 5. Set the WR bit to begin the erase cycle.

- 6. Either poll the WR bit or wait for the NVM interrupt (NVMIF is set).

A typical erase sequence is provided in Example 6-2. This example shows how to do a one-word erase. Similarly, a four-word erase and an eight-word erase can be done. This example uses C library procedures to manage the Table Pointer (builtin\_tblpage and builtin\_tbloffset) and the Erase Page Pointer (builtin\_tblwt1). The memory unlock sequence (builtin\_write\_NVM) also sets the WR bit to initiate the operation and returns control when complete.

### EXAMPLE 6-2: SINGLE-WORD ERASE

```

int __attribute__ ((space(eedata))) eeData = 0x1234;

/*_____

The variable eeData must be a Global variable declared outside of any method

the code following this comment can be written inside the method that will execute the erase

_____

*/

unsigned int offset;

// Set up NVMCON to erase one word of data EEPROM

NVMCON = 0 \times 4058;

// Set up a pointer to the EEPROM location to be erased

TBLPAG = __builtin_tblpage(&eeData); // Initialize EE Data page pointer

offset = __builtin_tbloffset(&eeData);

// Initizlize lower word of address

__builtin_tblwtl(offset, 0);

// Write EEPROM data to write latch

asm volatile ("disi #5");

// Disable Interrupts For 5 Instructions

__builtin_write_NVM();

// Issue Unlock Sequence & Start Write Cycle

while(NVMCONbits.WR=1);

// Optional: Poll WR bit to wait for

// write sequence to complete

```

# 8.0 INTERRUPT CONTROLLER

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the Interrupt Controller, refer to the *"PIC24F Family Reference Manual"*, **"Interrupts"** (DS39707).

The PIC24F interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the CPU. It has the following features:

- Up to Eight Processor Exceptions and Software Traps

- Seven User-Selectable Priority Levels

- Interrupt Vector Table (IVT) with up to 118 Vectors

- Unique Vector for Each Interrupt or Exception Source

- Fixed Priority within a Specified User Priority Level

- Alternate Interrupt Vector Table (AIVT) for Debug Support

- Fixed Interrupt Entry and Return Latencies

# 8.1 Interrupt Vector Table (IVT)

The IVT is shown in Figure 8-1. The IVT resides in the program memory, starting at location, 000004h. The IVT contains 126 vectors, consisting of eight non-maskable trap vectors, plus up to 118 sources of interrupt. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit-wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR).

Interrupt vectors are prioritized in terms of their natural priority; this is linked to their position in the vector table. All other things being equal, lower addresses have a higher natural priority. For example, the interrupt associated with Vector 0 will take priority over interrupts at any other vector address.

PIC24FV16KM204 family devices implement non-maskable traps and unique interrupts; these are summarized in Table 8-1.

### 8.1.1 ALTERNATE INTERRUPT VECTOR TABLE (AIVT)

The Alternate Interrupt Vector Table (AIVT) is located after the IVT, as shown in Figure 8-1. Access to the AIVT is provided by the ALTIVT control bit (INTCON2<15>). If the ALTIVT bit is set, all interrupt and exception processes will use the alternate vectors instead of the default vectors. The alternate vectors are organized in the same manner as the default vectors.

The AIVT supports emulation and debugging efforts by providing a means to switch between an application and a support environment without requiring the interrupt vectors to be reprogrammed. This feature also enables switching between applications for evaluation of different software algorithms at run time. If the AIVT is not needed, the AIVT should be programmed with the same addresses used in the IVT.

# 8.2 Reset Sequence

A device Reset is not a true exception, because the interrupt controller is not involved in the Reset process. The PIC24F devices clear their registers in response to a Reset, which forces the Program Counter (PC) to zero. The microcontroller then begins program execution at location, 000000h. The user programs a GOTO instruction at the Reset address, which redirects the program execution to the appropriate start-up routine.

**Note:** Any unimplemented or unused vector locations in the IVT and AIVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

## REGISTER 8-7: IFS2: INTERRUPT FLAG STATUS REGISTER 2

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0, HS | U-0   |

|--------|-----|-----|-----|-----|-----|-----------|-------|

| —      | —   | —   | —   | —   | —   | CCT5IF    | —     |

| bit 15 |     |     |     |     |     |           | bit 8 |

|        |     |     |     |     |     |           |       |

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0       | U-0   |

|        |     | _   | _   |     | _   |           | _     |

| bit 7  |     |     |     |     |     |           | bit 0 |

| Legend:           | HS = Hardware Settable bit |                             |                    |

|-------------------|----------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-10 | Unimplemented: Read as '0'                                |

|-----------|-----------------------------------------------------------|

| bit 9     | CCT5IF: Capture/Compare 5 Timer Interrupt Flag Status bit |

|           | 1 = Interrupt request has occurred                        |

|           | 0 = Interrupt request has not occurred                    |

|           |                                                           |

bit 8-0 Unimplemented: Read as '0'

### REGISTER 8-8: IFS3: INTERRUPT FLAG STATUS REGISTER 3

| U-0    | R/W-0, HS | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----------|-----|-----|-----|-----|-----|-------|

| —      | RTCIF     | —   | —   | —   | —   | —   | —     |

| bit 15 |           |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0, HS | R/W-0, HS | U-0   |

|-------|-----|-----|-----|-----|-----------|-----------|-------|

| —     | —   | —   | —   | —   | BCL2IF    | SSP2IF    | —     |

| bit 7 |     |     |     |     |           |           | bit 0 |

| Legend:           | HS = Hardware Settable bit |                             |                    |

|-------------------|----------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15   | Unimplemented: Read as '0'                                                          |

|----------|-------------------------------------------------------------------------------------|

| bit 14   | RTCIF: Real-Time Clock and Calendar Interrupt Flag Status bit                       |

|          | 1 = Interrupt request has occurred                                                  |

|          | 0 = Interrupt request has not occurred                                              |

| bit 13-3 | Unimplemented: Read as '0'                                                          |

| bit 2    | BCL2IF: MSSP2 I <sup>2</sup> C <sup>™</sup> Bus Collision Interrupt Flag Status bit |

|          | 1 = Interrupt request has occurred                                                  |

|          | 0 = Interrupt request has not occurred                                              |

| bit 1    | SSP2IF: MSSP2 SPI/I <sup>2</sup> C Event Interrupt Flag Status bit                  |

|          | 1 = Interrupt request has occurred                                                  |

|          | 0 = Interrupt request has not occurred                                              |

| bit 0    | Unimplemented: Read as '0'                                                          |

|          |                                                                                     |

## 10.2.2 IDLE MODE

Idle mode includes these features:

- · The CPU will stop executing instructions.

- · The WDT is automatically cleared.

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 10.6 "Selective Peripheral Module Control").

- If the WDT or FSCM is enabled, the LPRC will also remain active.

The device will wake from Idle mode on any of these events:

- · Any interrupt that is individually enabled

- Any device Reset

- A WDT time-out

On wake-up from Idle, the clock is reapplied to the CPU and instruction execution begins immediately, starting with the instruction following the PWRSAV instruction or the first instruction in the ISR.

### 10.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction will be held off until entry into Sleep or Idle mode has completed. The device will then wake-up from Sleep or Idle mode.

### 10.2.3.1 Power-on Resets (PORs)

VDD voltage is monitored to produce PORs. When a true POR occurs, the entire device is reset.

### 10.3 Ultra Low-Power Wake-up

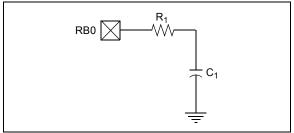

The Ultra Low-Power Wake-up (ULPWU) on pin, RB0, allows a slow falling voltage to generate an interrupt without excess current consumption.

To use this feature:

- 1. Charge the capacitor on RB0 by configuring the RB0 pin to an output and setting it to '1'.

- 2. Stop charging the capacitor by configuring RB0 as an input.

- 3. Discharge the capacitor by setting the ULPEN and ULPSINK bits in the ULPWCON register.

- 4. Configure Sleep mode.

- 5. Enter Sleep mode.

When the voltage on RB0 drops below VIL, the device wakes up and executes the next instruction.

This feature provides a low-power technique for periodically waking up the device from Sleep mode.

The time-out is dependent on the discharge time of the RC circuit on RB0.

When the ULPWU module wakes the device from Sleep mode, the ULPWUIF bit (IFS5<0>) is set. Software can check this bit upon wake-up to determine the wake-up source.

See Example 10-2 for initializing the ULPWU module.

### EXAMPLE 10-2: ULTRA LOW-POWER WAKE-UP INITIALIZATION

```

//********

// 1. Charge the capacitor on RBO

TRISBbits.TRISB0 = 0;

LATBbits.LATB0 = 1;

for(i = 0; i < 10000; i++) Nop();</pre>

//2. Stop Charging the capacitor

on RBO

11

//*******************************

TRISBbits.TRISB0 = 1;

//3. Enable ULPWU Interrupt

IFS5bits.ULPWUIF = 0;

IEC5bits.ULPWUIE = 1;

IPC21bits.ULPWUIP = 0x7;

//*********************************

//4. Enable the Ultra Low Power

11

Wakeup module and allow

11

capacitor discharge

ULPWCONbits.ULPEN = 1;

ULPWCONbit.ULPSINK = 1;

//5. Enter Sleep Mode

11

Sleep();

//for sleep, execution will

//resume here

```

A series resistor, between RB0 and the external capacitor provides overcurrent protection for the AN2/ULPWU/RB0 pin and enables software calibration of the time-out (see Figure 10-1).

### FIGURE 10-1: SERIES RESISTOR

A timer can be used to measure the charge time and discharge time of the capacitor. The charge time can then be adjusted to provide the desired delay in Sleep. This technique compensates for the affects of temperature, voltage and component accuracy. The peripheral can also be configured as a simple, programmable Low-Voltage Detect (LVD) or temperature sensor.

### REGISTER 10-1: ULPWCON: ULPWU CONTROL REGISTER

| R/W-0                                 | U-0           | R/W-0            | U-0              | U-0               | U-0                                | U-0             | R/W-0   |  |  |  |

|---------------------------------------|---------------|------------------|------------------|-------------------|------------------------------------|-----------------|---------|--|--|--|

| ULPEN                                 |               | ULPSIDL          | _                | —                 | _                                  | _               | ULPSINK |  |  |  |

| bit 15                                |               |                  |                  |                   |                                    |                 | bit 8   |  |  |  |

|                                       |               |                  |                  |                   |                                    |                 |         |  |  |  |

| U-0                                   | U-0           | U-0              | U-0              | U-0               | U-0                                | U-0             | U-0     |  |  |  |

| _                                     | _             | —                |                  | —                 | _                                  | _               | —       |  |  |  |

| bit 7                                 | ·             | · · ·            |                  |                   |                                    |                 | bit 0   |  |  |  |

|                                       |               |                  |                  |                   |                                    |                 |         |  |  |  |

| Legend:                               |               |                  |                  |                   |                                    |                 |         |  |  |  |

| R = Readable bit W = Writable bit U = |               |                  |                  |                   | U = Unimplemented bit, read as '0' |                 |         |  |  |  |

| -n = Value at                         | POR           | '1' = Bit is set |                  | '0' = Bit is clea | ared                               | x = Bit is unkr | nown    |  |  |  |

|                                       |               |                  |                  |                   |                                    |                 |         |  |  |  |

| bit 15                                | ULPEN: ULF    | PWU Module En    | able bit         |                   |                                    |                 |         |  |  |  |

|                                       | 1 = Module i  |                  |                  |                   |                                    |                 |         |  |  |  |

|                                       | 0 = Module i  | s disabled       |                  |                   |                                    |                 |         |  |  |  |

| bit 14                                | Unimpleme     | nted: Read as '0 | ,                |                   |                                    |                 |         |  |  |  |

| bit 13                                | ULPSIDL: U    | LPWU Stop in Ic  | lle Select bit   |                   |                                    |                 |         |  |  |  |

|                                       |               | nues module ope  |                  |                   | Idle mode                          |                 |         |  |  |  |

|                                       | 0 = Continue  | es module operat | tion in Idle mod | e                 |                                    |                 |         |  |  |  |

| bit 12-9                              | Unimpleme     | nted: Read as '0 | ,                |                   |                                    |                 |         |  |  |  |

| bit 8                                 | ULPSINK: U    | ILPWU Current S  | Sink Enable bit  |                   |                                    |                 |         |  |  |  |

|                                       | 1 = Current   | sink is enabled  |                  |                   |                                    |                 |         |  |  |  |

|                                       | 0 = Current s | sink is disabled |                  |                   |                                    |                 |         |  |  |  |

| bit 7-0                               | Unimpleme     | nted: Read as '0 | 3                |                   |                                    |                 |         |  |  |  |

### 11.2.2 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation, and a read operation of the same port. Typically, this instruction would be a NOP.

# 11.3 Input Change Notification (ICN)

The Input Change Notification function of the I/O ports allows the PIC24FXXXXX family of devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature is capable of detecting input Change-of-States, even in Sleep mode, when the clocks are disabled. Depending on the device pin count, there are up to 37 external signals (CN0 through CN36) that may be selected (enabled) for generating an interrupt request on a Change-of-State.

There are six control registers associated with the CN module. The CNEN1 and CNEN3 registers contain the interrupt enable control bits for each of the CNx input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each CNx pin also has a weak pull-up/pull-down connected to it. The pull-ups act as a current source that is connected to the pin. The pull-downs act as a current sink to eliminate the need for external resistors when push button or keypad devices are connected.

On any pin, only the pull-up resistor or the pull-down resistor should be enabled, but not both of them. If the push button or the keypad is connected to VDD, enable the pull-down, or if they are connected to VSS, enable the pull-up resistors. The pull-ups are enabled separately using the CNPU1 and CNPU3 registers, which contain the control bits for each of the CNx pins.

Setting any of the control bits enables the weak pull-ups for the corresponding pins. The pull-downs are enabled separately using the CNPD1 and CNPD3 registers, which contain the control bits for each of the CNx pins. Setting any of the control bits enables the weak pull-downs for the corresponding pins.

When the internal pull-up is selected, the pin uses VDD as the pull-up source voltage. When the internal pull-down is selected, the pins are pulled down to Vss by an internal resistor. Make sure that there is no external pull-up source/pull-down sink when the internal pull-ups/pull-downs are enabled.

Note: Pull-ups and pull-downs on Change Notification (CN) pins should always be disabled whenever the port pin is configured as a digital output.

# EXAMPLE 11-1: PORT WRITE/READ EXAMPLE

| MOV 0xFF00, W0;<br>MOV W0, TRISB;                                                 | //Configure PORTB<15:8> as inputs and PORTB<7:0> as outputs                                                                                          |

|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| NOP ;                                                                             | //Delay 1 cycle                                                                                                                                      |

| BTSS PORTB, #13;                                                                  | //Next Instruction                                                                                                                                   |

| <pre>Equivalent `C' Code TRISB = 0xFF00; NOP(); if(PORTBbits.RB13 == 1) { }</pre> | <pre>//Configure PORTB&lt;15:8&gt; as inputs and PORTB&lt;7:0&gt; as outputs //Delay 1 cycle // execute following code if PORTB pin 13 is set.</pre> |

# REGISTER 14-3: SSPxCON1: MSSPx CONTROL REGISTER 1 (SPI MODE)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   |     | —   | —   | —   |     | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0 | R/W-0                | R/W-0                | R/W-0 | R/W-0                | R/W-0                | R/W-0                | R/W-0                |

|-------|----------------------|----------------------|-------|----------------------|----------------------|----------------------|----------------------|

| WCOL  | SSPOV <sup>(1)</sup> | SSPEN <sup>(2)</sup> | CKP   | SSPM3 <sup>(3)</sup> | SSPM2 <sup>(3)</sup> | SSPM1 <sup>(3)</sup> | SSPM0 <sup>(3)</sup> |

| bit 7 |                      |                      |       |                      |                      |                      | bit 0                |

| Legend:    |                   |                                 |                                                                                   |                                                |

|------------|-------------------|---------------------------------|-----------------------------------------------------------------------------------|------------------------------------------------|

| R = Read   | able bit          | W = Writable bit                | U = Unimplemented bit                                                             | , read as '0'                                  |

| -n = Value | e at POR          | '1' = Bit is set                | '0' = Bit is cleared                                                              | x = Bit is unknown                             |

|            |                   |                                 |                                                                                   |                                                |

| bit 15-8   | Unimple           | mented: Read as '0'             |                                                                                   |                                                |

| bit 7      | WCOL: \           | Vrite Collision Detect bit      |                                                                                   |                                                |

|            |                   | •                               | while it is still transmitting the                                                | previous word (must be cleared in              |

|            | softw<br>0 = No c | ,                               |                                                                                   |                                                |

| bit 6      |                   |                                 | Port Receive Overflow Indicate                                                    | or bit(1)                                      |

| bit 0      | SPI Slav          |                                 |                                                                                   |                                                |

|            |                   |                                 | SPxBUF register is still holding                                                  | g the previous data. In case of over-          |

|            |                   |                                 |                                                                                   | ave mode. The user must read the               |

|            | 0 = No c          |                                 | g data, to avoid setting overflo                                                  | w (must be cleared in software).               |

| bit 5      |                   | Master Synchronous Serial F     | Port Enable bit(2)                                                                |                                                |

| DIL 5      |                   | •                               | ures SCKx, SDOx, SDIx and                                                         | SSx as serial nort nins                        |

|            |                   |                                 | jures these pins as I/O port pi                                                   | · ·                                            |

| bit 4      | CKP: Clo          | ock Polarity Select bit         |                                                                                   |                                                |

|            | 1 = Idle s        | state for clock is a high level |                                                                                   |                                                |

|            |                   | state for clock is a low level  |                                                                                   |                                                |

| bit 3-0    | SSPM<3            | :0>: Master Synchronous Se      | rial Port Mode Select bits <sup>(3)</sup>                                         |                                                |

|            |                   | SPI Master mode, Clock = Fo     |                                                                                   |                                                |

|            |                   |                                 | x pin; <u>SSx</u> pin control is disabl<br>(x pin; <u>SSx</u> pin control is enab | ed, $\overline{SSx}$ can be used as an I/O pin |

|            |                   | SPI Master mode, Clock = TM     |                                                                                   |                                                |

|            |                   | SPI Master mode, Clock = Fo     | •                                                                                 |                                                |

|            |                   | PI Master mode, Clock = Fo      |                                                                                   |                                                |

|            | 0000 = 5          | SPI Master mode, Clock = Fo     | SC/2                                                                              |                                                |

| Note 1:    | In Master mo      | de, the overflow bit is not set | t since each new reception (a                                                     | nd transmission) is initiated by               |

|            | writing to the    | SSPxBUF register.               |                                                                                   |                                                |

- 2: When enabled, these pins must be properly configured as inputs or outputs.

- **3:** Bit combinations not specifically listed here are either reserved or implemented in  $I^2C^{TM}$  mode only.

# REGISTER 14-7: SSPxCON3: MSSPx CONTROL REGISTER 3 (I<sup>2</sup>C<sup>™</sup> MODE)

| U-0                           | U-0                                           | U-0                                   | U-0            | U-0                            | U-0              | U-0                               | U-0             |  |  |

|-------------------------------|-----------------------------------------------|---------------------------------------|----------------|--------------------------------|------------------|-----------------------------------|-----------------|--|--|

|                               | _                                             | —                                     |                | —                              | —                |                                   | —               |  |  |

| bit 15                        |                                               |                                       |                |                                |                  |                                   | bit             |  |  |

|                               |                                               |                                       |                |                                |                  |                                   |                 |  |  |

| R-0                           | R/W-0                                         | R/W-0                                 | R/W-0          | R/W-0                          | R/W-0            | R/W-0                             | R/W-0           |  |  |

| ACKTIM <sup>(1)</sup>         | PCIE                                          | SCIE                                  | BOEN           | SDAHT                          | SBCDE            | E AHEN D                          |                 |  |  |

| bit 7                         |                                               |                                       |                |                                |                  |                                   | bit (           |  |  |

| 1                             |                                               |                                       |                |                                |                  |                                   |                 |  |  |

| Legend:<br>R = Readable       | , hit                                         | M = Mritable k                        |                |                                | opted bit read   |                                   |                 |  |  |

| R = Readable<br>-n = Value at |                                               | W = Writable t<br>'1' = Bit is set    | אנ             | 0 = Unimpien                   |                  | read as '0'<br>x = Bit is unknown |                 |  |  |

|                               | FUR                                           | I – DILIS SEL                         |                |                                | areu             | X - DILISUIK                      | nown            |  |  |

| bit 15-8                      | Unimplemen                                    | ted: Read as '0                       | 3              |                                |                  |                                   |                 |  |  |

| bit 7                         | -                                             | knowledge Time                        |                |                                |                  |                                   |                 |  |  |

|                               | 1 = Indicates                                 | the I <sup>2</sup> C bus is ir        | an Acknowlee   |                                |                  |                                   | the SCLx cloc   |  |  |

|                               |                                               | knowledge seq                         |                | d on the 9 <sup>th</sup> risii | ng edge of the   | SCLx clock                        |                 |  |  |

| bit 6                         |                                               | ondition Interrup                     |                |                                |                  |                                   |                 |  |  |

|                               |                                               | nterrupt on dete<br>ction interrupts  |                |                                |                  |                                   |                 |  |  |

| bit 5                         | •                                             | ondition Interru                      |                |                                |                  |                                   |                 |  |  |

|                               |                                               | nterrupt on dete                      |                | t or Restart cor               | dition           |                                   |                 |  |  |

|                               |                                               | ction interrupts                      |                |                                |                  |                                   |                 |  |  |

| bit 4                         | BOEN: Buffer                                  | r Overwrite Ena                       | ble bit        |                                |                  |                                   |                 |  |  |

|                               | I <sup>2</sup> C Master m                     |                                       |                |                                |                  |                                   |                 |  |  |

|                               | This bit is igno<br>I <sup>2</sup> C Slave mo |                                       |                |                                |                  |                                   |                 |  |  |

|                               |                                               | F is updated and                      | d an ACK is ge | enerated for a re              | eceived addres   | s/data byte, igr                  | noring the stat |  |  |

|                               | of the SS                                     | SPOV bit only if                      | the BF bit = 0 |                                |                  |                                   | •               |  |  |

| L:1 0                         |                                               | F is only update                      |                | IV is clear                    |                  |                                   |                 |  |  |

| bit 3                         |                                               | x Hold Time Se<br>of 300 ns hold t    |                | ofter the folling              |                  |                                   |                 |  |  |

|                               |                                               | of 100 ns hold t                      |                |                                |                  |                                   |                 |  |  |

| bit 2                         |                                               | ve Mode Bus Co                        |                | -                              | -                |                                   |                 |  |  |

|                               | 1 = Enables s                                 | ave bus collision                     | on interrupts  |                                |                  |                                   |                 |  |  |

|                               |                                               | s collision interru                   | •              |                                |                  |                                   |                 |  |  |

| bit 1                         |                                               | ess Hold Enable                       | -              | • •                            |                  |                                   |                 |  |  |

|                               |                                               | g the 8th falling<br>N1 register will |                |                                |                  | ddress byte;                      | CKP bit of the  |  |  |

|                               |                                               | holding is disab                      |                |                                |                  |                                   |                 |  |  |

| bit 0                         | DHEN: Data                                    | Hold Enable bit                       | (Slave mode of | only)                          |                  |                                   |                 |  |  |

|                               |                                               | g the 8th falling                     | -              |                                | lata byte; slave | hardware clea                     | ars the CKP bi  |  |  |

|                               |                                               | SPxCON1 regist<br>ding is disabled    | er and SCLx is | s held low                     |                  |                                   |                 |  |  |

|                               |                                               |                                       |                |                                |                  |                                   |                 |  |  |

| Note 1: Th                    |                                               | fect in Slave mo                      |                |                                |                  |                                   |                 |  |  |

2: The ACKTIM status bit is active only when the AHEN bit or DHEN bit is set.

NOTES:

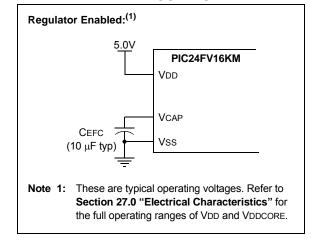

# 25.2 On-Chip Voltage Regulator

All of the PIC24FXXXXX family devices power their core digital logic at a nominal 3.0V. This may create an issue for designs that are required to operate at a higher typical voltage, as high as 5.0V. To simplify system design, all devices in the "FV" family incorporate an on-chip regulator that allows the device core to run at 3.0V, while the I/O is powered by VDD at a higher voltage.

The regulator is always enabled and provides power to the core from the other VDD pins. A low-ESR capacitor (such as ceramic) must be connected to the VCAP pin (Figure 25-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in Section 27.1 "DC Characteristics" and discussed in detail in Section 2.0 "Guidelines for Getting Started with 16-Bit Microcontrollers".

In all of the "F" family of devices, the regulator is disabled. Instead, the core logic is directly powered from VDD. "F" devices operate at a lower range of VDD voltage, from 1.8V-3.6V.

### 25.2.1 VOLTAGE REGULATOR TRACKING MODE AND LOW-VOLTAGE DETECTION

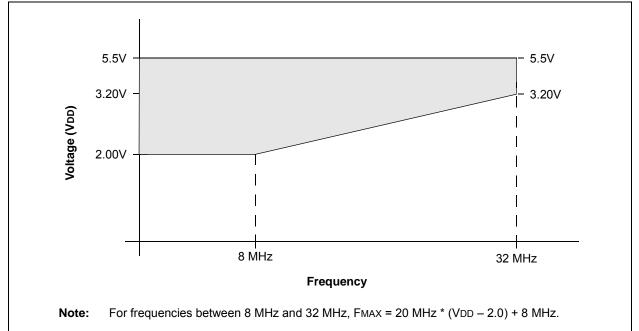

For all PIC24FXXXXX devices, the on-chip regulator provides a constant voltage of 3.0V nominal to the digital core logic. The regulator can provide this level from a VDD of about 3.2V, all the way up to the device's VDDMAX. It does not have the capability to boost VDD levels below 3.2V. In order to prevent "brown out" conditions when the voltage drops too low for the regulator, the regulator enters Tracking mode. In Tracking mode, the regulator output follows VDD with a typical voltage drop of 150 mV.

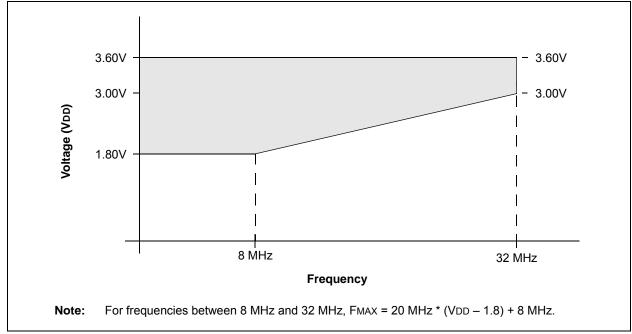

When the device enters Tracking mode, it is no longer possible to operate at full speed. To provide information about when the device enters Tracking mode, the on-chip High/Low-Voltage Detect (HLVD) module can be used. The HLVD trip point should be configured so that if VDD drops close to the minimum voltage for the operating frequency of the device, the HLVD Interrupt Flag, HLVDIF (IFS4<8>), will occur. This can be used to generate an interrupt and put the application into a low-power operational mode or trigger an orderly shutdown. Refer to **Section 27.1 "DC Characteristics"** for the specifications detailing the maximum operating speed based on the applied VDD voltage.

# FIGURE 25-1:

#### CONNECTIONS FOR THE ON-CHIP VOLTAGE REGULATOR

# 25.2.2 VOLTAGE REGULATOR START-UP TIME

For PIC24FXXXX family devices, it takes a short time, designated as TPM, for the regulator to generate a stable output. During this time, code execution is disabled. TPM is applied every time the device resumes operation after any power-down, including Sleep mode. TPM is specified in Section 27.2 "AC Characteristics and Timing Parameters".

# 25.3 Watchdog Timer (WDT)

For the PIC24FXXXXX family of devices, the WDT is driven by the LPRC Oscillator. When the WDT is enabled, the clock source is also enabled.

The nominal WDT clock source from LPRC is 31 kHz. This feeds a prescaler that can be configured for either 5-bit (divide-by-32) or 7-bit (divide-by-128) operation. The prescaler is set by the FWPSA Configuration bit. With a 31 kHz input, the prescaler yields a nominal WDT Time-out period (TWDT) of 1 ms in 5-bit mode or 4 ms in 7-bit mode.

A variable postscaler divides down the WDT prescaler output and allows for a wide range of time-out periods. The postscaler is controlled by the Configuration bits, WDTPS<3:0> (FWDT<3:0>), which allow the selection of a total of 16 settings, from 1:1 to 1:32,768. Using the prescaler and postscaler time-out periods, ranges from 1 ms to 131 seconds can be achieved.

# 26.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

### 26.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

### 26.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

# 26.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

# 26.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

# 27.1 DC Characteristics

### FIGURE 27-2: PIC24F16KM204 FAMILY VOLTAGE-FREQUENCY GRAPH (INDUSTRIAL)

## TABLE 27-1: THERMAL OPERATING CONDITIONS

| Rating                                                                                                                                                                                                                                                                                                                        | Symbol | Min           | Тур         | Max  | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------|-------------|------|------|

| Operating Junction Temperature Range                                                                                                                                                                                                                                                                                          | TJ     | -40           | _           | +140 | °C   |

| Operating Ambient Temperature Range                                                                                                                                                                                                                                                                                           | TA     | -40           | _           | +125 | °C   |

| $\begin{array}{l} \mbox{Power Dissipation} \\ \mbox{Internal Chip Power Dissipation:} \\ \mbox{PINT} = \mbox{VDD } x \ (\mbox{IDD} - \Sigma \ \mbox{IOH}) \\ \mbox{I/O Pin Power Dissipation:} \\ \mbox{PI/O} = \Sigma \ (\{\mbox{VDD} - \mbox{VOH} \} \ x \ \mbox{IOH}) + \Sigma \ (\mbox{VOL } x \ \mbox{IOL}) \end{array}$ | PD     |               | Pint + Pi/c | )    | W    |

| Maximum Allowed Power Dissipation                                                                                                                                                                                                                                                                                             | PDMAX  | (TJ – TA)/θJA |             |      | W    |

## TABLE 27-2: THERMAL PACKAGING CHARACTERISTICS

| Characteristic                           | Symbol | Тур  | Max | Unit | Notes |

|------------------------------------------|--------|------|-----|------|-------|

| Package Thermal Resistance, 20-Pin PDIP  | θJA    | 62.4 | _   | °C/W | 1     |

| Package Thermal Resistance, 28-Pin SPDIP | θJA    | 60   |     | °C/W | 1     |

| Package Thermal Resistance, 20-Pin SSOP  | θJA    | 108  | -   | °C/W | 1     |

| Package Thermal Resistance, 28-Pin SSOP  | θJA    | 71   | _   | °C/W | 1     |

| Package Thermal Resistance, 20-Pin SOIC  | θJA    | 75   | _   | °C/W | 1     |

| Package Thermal Resistance, 28-Pin SOIC  | θJA    | 80.2 | _   | °C/W | 1     |

| Package Thermal Resistance, 20-Pin QFN   | θJA    | 43   | _   | °C/W | 1     |

| Package Thermal Resistance, 28-Pin QFN   | θJA    | 32   | _   | °C/W | 1     |

| Package Thermal Resistance, 44-Pin QFN   | θJA    | 29   | _   | °C/W | 1     |

| Package Thermal Resistance, 44-Pin TQFP  | θJA    | 40   | _   | °C/W | 1     |

| Package Thermal Resistance, 48-Pin UQFN  | θJA    | 41   | _   | °C/W | 1     |

**Note 1:** Junction to ambient thermal resistance, Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.

### TABLE 27-3: DC CHARACTERISTICS: TEMPERATURE AND VOLTAGE SPECIFICATIONS

| DC CHARACTERISTICS |                                              | Standard Operating Conditions                                    |      |                    |     | s: 1.8V to 3.6V (PIC24F16KMXXX)<br>2.0V to 5.5V (PIC24FV16KMXXX)<br>$-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                                   |  |

|--------------------|----------------------------------------------|------------------------------------------------------------------|------|--------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--|

| Param<br>No.       | Symbol                                       | Characteristic                                                   | Min  | Typ <sup>(1)</sup> | Max | Units                                                                                                                                                                             | Conditions                        |  |

| DC10               | Vdd                                          | Supply Voltage                                                   | 1.8  | —                  | 3.6 | V                                                                                                                                                                                 | For PIC24F devices                |  |

|                    |                                              |                                                                  | 2.0  | _                  | 5.5 | V                                                                                                                                                                                 | For PIC24FV devices               |  |

| DC12 VDR           | RAM Data Retention<br>Voltage <sup>(2)</sup> | 1.6                                                              | _    | —                  | V   | For PIC24F devices                                                                                                                                                                |                                   |  |

|                    |                                              | 1.8                                                              | —    | —                  | V   | For PIC24FV devices                                                                                                                                                               |                                   |  |

| DC16               | VPOR                                         | VDD Start Voltage<br>to Ensure Internal<br>Power-on Reset Signal | Vss  | —                  | 0.7 | V                                                                                                                                                                                 |                                   |  |

| DC17               | SVDD                                         | VDD Rise Rate<br>to Ensure Internal<br>Power-on Reset Signal     | 0.05 | _                  | —   | V/ms                                                                                                                                                                              | 0-3.3V in 0.1s<br>0-2.5V in 60 ms |  |

**Note 1:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**2:** This is the limit to which VDD can be lowered without losing RAM data.

| Param.<br>No. Symbol        |                                            | Characteristic                  |              | Min         | Max  | Units                                      | Conditions                                 |  |

|-----------------------------|--------------------------------------------|---------------------------------|--------------|-------------|------|--------------------------------------------|--------------------------------------------|--|

| 100                         | Тнідн                                      | Clock High Time                 | 100 kHz mode | 4.0         | -    | μS                                         | Must operate at a minimum of 1.5 MHz       |  |

|                             |                                            |                                 | 400 kHz mode | 0.6         | -    | μS                                         | Must operate at a minimum of 10 MHz        |  |

|                             |                                            |                                 | MSSPx module | 1.5 TCY     |      | _                                          |                                            |  |

| 101 Tı                      | TLOW                                       | Clock Low Time                  | 100 kHz mode | 4.7         | —    | μS                                         | Must operate at a minimum of 1.5 MHz       |  |