#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                      |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 23                                                                            |

| Program Memory Size        | 8KB (2.75K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5V                                                                       |

| Data Converters            | A/D 19x10b/12b; D/A 2x8b                                                      |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                |

| Supplier Device Package    | 28-SSOP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fv08km202-e-ss |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.2 CPU Control Registers

### REGISTER 3-1: SR: ALU STATUS REGISTER

|                    |                                             |                                                                                                                         |                          |                   |                              |                  | <b>DM</b> (0):000 |  |  |  |

|--------------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--------------------------|-------------------|------------------------------|------------------|-------------------|--|--|--|

| U-0                | U-0                                         | U-0                                                                                                                     | U-0                      | U-0               | U-0                          | U-0              | R/W-0, HSC        |  |  |  |

|                    |                                             |                                                                                                                         |                          | —                 | —                            | —                | DC                |  |  |  |

| bit 15             |                                             |                                                                                                                         |                          |                   |                              |                  | bit 8             |  |  |  |

| R/W-0, HS          | SC <sup>(1)</sup> R/W-0, HSC <sup>(1)</sup> | R/W-0, HSC <sup>(1)</sup>                                                                                               | R-0, HSC                 | R/W-0, HSC        | R/W-0, HSC                   | R/W-0, HSC       | R/W-0, HSC        |  |  |  |

| IPL2 <sup>(2</sup> |                                             | IPL0 <sup>(2)</sup>                                                                                                     | R-0, 1130                | N N               | OV                           | Z                | C                 |  |  |  |

| bit 7              |                                             | 11 2011                                                                                                                 |                          | IN                | 00                           | 2                | bit 0             |  |  |  |

| Sit 1              |                                             |                                                                                                                         |                          |                   |                              |                  |                   |  |  |  |

| Legend:            |                                             | HSC = Hardwa                                                                                                            | re Settable/0            | Clearable bit     |                              |                  |                   |  |  |  |

| R = Reada          | able bit                                    | W = Writable bi                                                                                                         | t                        | U = Unimplei      | mented bit, rea              | id as '0'        |                   |  |  |  |

| -n = Value         | at POR                                      | '1' = Bit is set                                                                                                        |                          | '0' = Bit is cle  | ared                         | x = Bit is unk   | nown              |  |  |  |

|                    |                                             |                                                                                                                         |                          |                   |                              |                  |                   |  |  |  |

| bit 15-9           | Unimplement                                 | ed: Read as '0'                                                                                                         |                          |                   |                              |                  |                   |  |  |  |

| bit 8              |                                             | Carry/Borrow bit                                                                                                        |                          |                   |                              |                  |                   |  |  |  |

|                    |                                             | It from the 4 <sup>th</sup> low-                                                                                        | -order bit (foi          | byte-sized da     | ta) or 8 <sup>th</sup> Iow-o | rder bit (for wo | rd-sized data)    |  |  |  |

|                    |                                             | ult occurred<br>out from the 4 <sup>th</sup> or                                                                         | 8 <sup>th</sup> low-orde | er bit of the res | sult has occurr              | ed               |                   |  |  |  |

| bit 7-5            | •                                           | J Interrupt Priority                                                                                                    |                          |                   |                              |                  |                   |  |  |  |

|                    |                                             |                                                                                                                         |                          |                   | s are disabled               |                  |                   |  |  |  |

|                    |                                             | 111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled 110 = CPU Interrupt Priority Level is 6 (14) |                          |                   |                              |                  |                   |  |  |  |

|                    |                                             | 101 = CPU Interrupt Priority Level is 5 (13)<br>100 = CPU Interrupt Priority Level is 4 (12)                            |                          |                   |                              |                  |                   |  |  |  |

|                    |                                             | errupt Priority Le                                                                                                      |                          |                   |                              |                  |                   |  |  |  |

|                    |                                             | errupt Priority Le                                                                                                      |                          |                   |                              |                  |                   |  |  |  |

|                    |                                             | errupt Priority Lev<br>errupt Priority Lev                                                                              |                          |                   |                              |                  |                   |  |  |  |

| bit 4              | RA: REPEAT L                                |                                                                                                                         |                          |                   |                              |                  |                   |  |  |  |

|                    | 1 = REPEAT <b>IO</b>                        | •                                                                                                                       |                          |                   |                              |                  |                   |  |  |  |

|                    | 0 = REPEAT IO                               | op not in progres                                                                                                       | S                        |                   |                              |                  |                   |  |  |  |

| bit 3              | N: ALU Negati                               |                                                                                                                         |                          |                   |                              |                  |                   |  |  |  |

|                    | 1 = Result was                              | s negative<br>s non-negative (ze                                                                                        | oro or popitiv           | (D)               |                              |                  |                   |  |  |  |

| bit 2              | OV: ALU Over                                |                                                                                                                         |                          | (6)               |                              |                  |                   |  |  |  |

|                    |                                             | occurred for signe                                                                                                      | d (2's compl             | ement) arithm     | etic in this arith           | metic operatio   | on                |  |  |  |

|                    |                                             | w has occurred                                                                                                          | - (                      | ,                 |                              |                  |                   |  |  |  |

| bit 1              | Z: ALU Zero b                               | it                                                                                                                      |                          |                   |                              |                  |                   |  |  |  |

|                    | •                                           | on, which effects                                                                                                       |                          |                   |                              |                  | 10                |  |  |  |

| L:1 0              | _                                           | recent operation,                                                                                                       | which effects            | s the Z bit, has  | s cleared it (i.e.           | , a non-zero re  | esuit)            |  |  |  |

| bit 0              | <b>C:</b> ALU Carry/<br>1 = A carry-ou      | Borrow bit<br>t from the Most S                                                                                         | ionificant bit           | (MSb) of the r    | esult occurred               |                  |                   |  |  |  |

|                    |                                             | ut from the Most                                                                                                        |                          |                   |                              |                  |                   |  |  |  |

| Note 1:            | The IPLx Status bits                        | are read-only wh                                                                                                        | en NSTDIS                | (INTCON1<1        | 5>) = 1.                     |                  |                   |  |  |  |

| 2:                 | The IPL<2:0> Status                         | •                                                                                                                       |                          |                   | -                            | o form the CPL   | J Interrupt       |  |  |  |

|                    | Priority Level (IPL).                       |                                                                                                                         |                          |                   |                              |                  | •                 |  |  |  |

|                    |                                             |                                                                                                                         |                          |                   |                              |                  |                   |  |  |  |

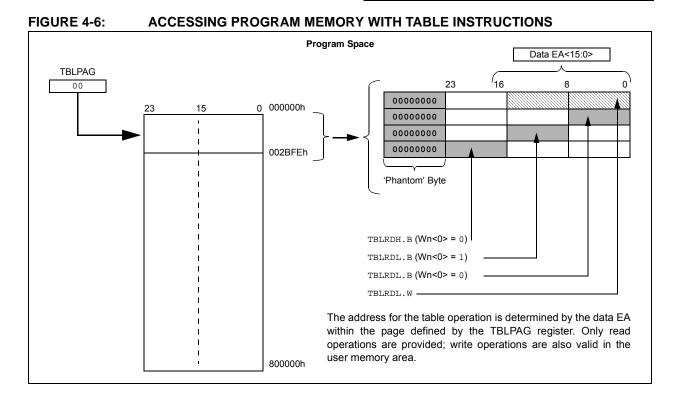

#### 4.3.2 DATA ACCESS FROM PROGRAM MEMORY AND DATA EEPROM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program memory without going through Data Space. It also offers a direct method of reading or writing a word of any address within data EEPROM memory. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

Note: The TBLRDH and TBLWTH instructions are not used while accessing data EEPROM memory.

The PC is incremented by 2 for each successive 24-bit program word. This allows program memory addresses to directly map to Data Space addresses. Program memory can thus be regarded as two 16-bit, word-wide address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space which contains the least significant data word, and TBLRDH and TBLWTH access the space which contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from program space. Both function as either byte or word operations.

TBLRDL (Table Read Low): In Word mode, it maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>). In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when byte select is '1'; the lower byte is selected when it is '0'.

TBLRDH (Table Read High): In Word mode, it maps the entire upper word of a program address (P<23:16>) to a data address. Note that D<15:8>, the 'phantom' byte, will always be '0'.

In Byte mode, it maps the upper or lower byte of the program word to D<7:0> of the data address, as above. Note that the data will always be '0' when the upper 'phantom' byte is selected (Byte Select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in **Section 5.0 "Flash Program Memory"**.

For all table operations, the area of program memory space to be accessed is determined by the Table Memory Page Address register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

**Note:** Only Table Read operations will execute in the configuration memory space, and only then, in implemented areas, such as the Device ID. Table Write operations are not allowed.

© 2013 Microchip Technology Inc.

**IFS1: INTERRUPT FLAG STATUS REGISTER 1**

**REGISTER 8-6:**

| R/W-0, HS     | R/W-0, HS       | R/W-0, HS                       | R/W-0, HS       | R/W-0, HS         | U-0              | U-0             | U-0       |

|---------------|-----------------|---------------------------------|-----------------|-------------------|------------------|-----------------|-----------|

| U2TXIF        | U2RXIF          | INT2IF                          | CCT4IF          | CCT3IF            |                  | —               | —         |

| bit 15        |                 |                                 |                 |                   |                  |                 | bit 8     |

|               |                 |                                 |                 |                   |                  |                 |           |

| U-0           | R/W-0, HS       | U-0                             | R/W-0, HS       | R/W-0, HS         | R/W-0, HS        | R/W-0, HS       | R/W-0, HS |

| —             | CCP5IF          | —                               | INT1IF          | CNIF              | CMIF             | BCL1IF          | SSP1IF    |

| bit 7         |                 |                                 |                 |                   |                  |                 | bit 0     |

|               |                 |                                 |                 |                   |                  |                 |           |

| Legend:       |                 |                                 | re Settable bit |                   |                  |                 |           |

| R = Readable  |                 | W = Writable                    |                 | -                 | nented bit, read | d as '0'        |           |

| -n = Value at | POR             | '1' = Bit is set                |                 | '0' = Bit is clea | ared             | x = Bit is unkr | nown      |

|               |                 |                                 |                 |                   |                  |                 |           |

| bit 15        |                 | T2 Transmitter                  |                 | Status bit        |                  |                 |           |

|               |                 | equest has oc<br>equest has no  |                 |                   |                  |                 |           |

| bit 14        | -               | RT2 Receiver Ir                 |                 | atus hit          |                  |                 |           |

|               |                 | request has oc                  |                 |                   |                  |                 |           |

|               |                 | equest has not                  |                 |                   |                  |                 |           |

| bit 13        | INT2IF: Exter   | nal Interrupt 2                 | Flag Status bit |                   |                  |                 |           |

|               |                 | equest has oc                   |                 |                   |                  |                 |           |

|               | •               | equest has not                  |                 |                   |                  |                 |           |

| bit 12        |                 | -                               |                 | pt Flag Status b  | bit              |                 |           |

|               |                 | equest has oc                   |                 |                   |                  |                 |           |

| bit 11        | -               | equest has not                  |                 | nt Elan Statua k  | -:+              |                 |           |

|               | -               | request has oc                  |                 | pt Flag Status b  | JIL              |                 |           |

|               |                 | request has not                 |                 |                   |                  |                 |           |

| bit 10-7      | -               | ted: Read as '                  |                 |                   |                  |                 |           |

| bit 6         | CCP5IF: Cap     | ture/Compare                    | 5 Event Interru | pt Flag Status I  | bit              |                 |           |

|               | 1 = Interrupt r | equest has oc                   | curred          |                   |                  |                 |           |

|               | 0 = Interrupt r | equest has no                   | occurred        |                   |                  |                 |           |

| bit 5         | •               | ted: Read as '                  |                 |                   |                  |                 |           |

| bit 4         |                 | nal Interrupt 1                 | •               |                   |                  |                 |           |

|               |                 | equest has oc<br>equest has no  |                 |                   |                  |                 |           |

| bit 3         |                 | •                               |                 | lag Status bit    |                  |                 |           |

| DIUS          | -               | hange Notifica<br>equest has oc | -               | lay Status bit    |                  |                 |           |

|               | •               | request has not                 |                 |                   |                  |                 |           |

| bit 2         | CMIF: Compa     | arator Interrupt                | Flag Status Bit | t                 |                  |                 |           |

|               | -               | equest has oc                   | -               |                   |                  |                 |           |

|               | -               | equest has no                   |                 |                   |                  |                 |           |

| bit 1         |                 |                                 |                 | upt Flag Status   | bit              |                 |           |

|               |                 | equest has oc                   |                 |                   |                  |                 |           |

| <b>L</b> H 0  | -               | equest has not                  |                 |                   |                  |                 |           |

| bit 0         |                 | SP1 SPI/I <sup>2</sup> C Ev     | •               | lag Status bit    |                  |                 |           |

|               |                 | equest has oc<br>equest has no  |                 |                   |                  |                 |           |

|               | 5 monupti       |                                 |                 |                   |                  |                 |           |

| U-0                          | U-0                                                                                                                                                                                                                         | U-0                                                                         | U-0     | U-0              | R/W-1            | R/W-0           | R/W-0   |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|---------|------------------|------------------|-----------------|---------|

| _                            |                                                                                                                                                                                                                             |                                                                             |         |                  | U2ERIP2          | U2ERIP1         | U2ERIP0 |

| oit 15                       |                                                                                                                                                                                                                             |                                                                             | •       |                  |                  | •               | bit 8   |

|                              |                                                                                                                                                                                                                             |                                                                             |         |                  |                  |                 |         |

| U-0                          | R/W-1                                                                                                                                                                                                                       | R/W-0                                                                       | R/W-0   | U-0              | U-0              | U-0             | U-0     |

| —                            | U1ERIP2                                                                                                                                                                                                                     | U1ERIP1                                                                     | U1ERIP0 | —                | —                | —               | —       |

| bit 7                        |                                                                                                                                                                                                                             |                                                                             |         |                  |                  |                 | bit 0   |

|                              |                                                                                                                                                                                                                             |                                                                             |         |                  |                  |                 |         |

| Legend:                      |                                                                                                                                                                                                                             |                                                                             |         |                  |                  |                 |         |

| R = Readab                   | ole bit                                                                                                                                                                                                                     | W = Writable                                                                | bit     | U = Unimpler     | mented bit, read | d as '0'        |         |

| -n = Value at POR            |                                                                                                                                                                                                                             | '1' = Bit is set                                                            |         | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |

| bit 10-8<br>bit 7<br>bit 6-4 | <ul> <li>111 = Interrupt is Priority 7 (highest priority interrupt)</li> <li> <ul> <li>001 = Interrupt is Priority 1</li> <li>000 = Interrupt source is disabled</li> </ul> </li> <li>Unimplemented: Read as '0'</li> </ul> |                                                                             |         |                  |                  |                 |         |

| bit 3-0                      | •<br>•<br>001 = Interru<br>000 = Interru                                                                                                                                                                                    | pt is Priority 1<br>pt is Priority 1<br>pt source is dis<br>nted: Read as ' | abled   | interrupt)       |                  |                 |         |

### REGISTER 8-30: IPC16: INTERRUPT PRIORITY CONTROL REGISTER 16

| U-0                                | U-0                | U-0                 | U-0                                     | U-0                 | U-0                 | U-0                 | U-0                 |

|------------------------------------|--------------------|---------------------|-----------------------------------------|---------------------|---------------------|---------------------|---------------------|

|                                    | —                  | —                   | —                                       | —                   | —                   | —                   | —                   |

| bit 15                             |                    |                     |                                         |                     |                     |                     | bit 8               |

|                                    |                    |                     |                                         |                     |                     |                     |                     |

| U-0                                | U-0                | R/W-0               | R/W-0                                   | R/W-0               | R/W-0               | R/W-0               | R/W-0               |

| —                                  | —                  | TUN5 <sup>(1)</sup> | TUN4 <sup>(1)</sup>                     | TUN3 <sup>(1)</sup> | TUN2 <sup>(1)</sup> | TUN1 <sup>(1)</sup> | TUN0 <sup>(1)</sup> |

| bit 7                              |                    |                     |                                         |                     |                     |                     | bit 0               |

|                                    |                    |                     |                                         |                     |                     |                     |                     |

| Legend:                            |                    |                     |                                         |                     |                     |                     |                     |

| R = Readable bit W = Writable bit  |                    |                     |                                         | U = Unimplem        | nented bit, read    | l as '0'            |                     |

| -n = Value at POR (1' = Bit is set |                    |                     | '0' = Bit is cleared x = Bit is unknown |                     |                     |                     |                     |

|                                    |                    |                     |                                         |                     |                     |                     |                     |

| bit 15-6                           | Unimplement        | ted: Read as 'd     | )'                                      |                     |                     |                     |                     |

| bit 5-0                            | TUN<5:0>: FI       | RC Oscillator T     | uning bits <sup>(1)</sup>               |                     |                     |                     |                     |

|                                    |                    | ximum frequen       | cy deviation                            |                     |                     |                     |                     |

|                                    | 011110             |                     |                                         |                     |                     |                     |                     |

|                                    | •                  |                     |                                         |                     |                     |                     |                     |

|                                    | •                  |                     |                                         |                     |                     |                     |                     |

|                                    | 000001             |                     |                                         |                     |                     |                     |                     |

|                                    | 000000 <b>= Ce</b> | nter frequency,     | oscillator is ru                        | nning at factory    | calibrated free     | quency              |                     |

|                                    | 111111             |                     |                                         |                     |                     |                     |                     |

|                                    | •                  |                     |                                         |                     |                     |                     |                     |

|                                    | •                  |                     |                                         |                     |                     |                     |                     |

|                                    | 100001             |                     |                                         |                     |                     |                     |                     |

|                                    |                    | nimum frequen       | cv deviation                            |                     |                     |                     |                     |

**Note 1:** Increments or decrements of TUN<5:0> may not change the FRC frequency in equal steps over the FRC tuning range and may not be monotonic.

# REGISTER 9-3: OSCTUN: FRC OSCILLATOR TUNE REGISTER

# 11.2.2 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation, and a read operation of the same port. Typically, this instruction would be a NOP.

# 11.3 Input Change Notification (ICN)

The Input Change Notification function of the I/O ports allows the PIC24FXXXXX family of devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature is capable of detecting input Change-of-States, even in Sleep mode, when the clocks are disabled. Depending on the device pin count, there are up to 37 external signals (CN0 through CN36) that may be selected (enabled) for generating an interrupt request on a Change-of-State.

There are six control registers associated with the CN module. The CNEN1 and CNEN3 registers contain the interrupt enable control bits for each of the CNx input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each CNx pin also has a weak pull-up/pull-down connected to it. The pull-ups act as a current source that is connected to the pin. The pull-downs act as a current sink to eliminate the need for external resistors when push button or keypad devices are connected.

On any pin, only the pull-up resistor or the pull-down resistor should be enabled, but not both of them. If the push button or the keypad is connected to VDD, enable the pull-down, or if they are connected to VSS, enable the pull-up resistors. The pull-ups are enabled separately using the CNPU1 and CNPU3 registers, which contain the control bits for each of the CNx pins.

Setting any of the control bits enables the weak pull-ups for the corresponding pins. The pull-downs are enabled separately using the CNPD1 and CNPD3 registers, which contain the control bits for each of the CNx pins. Setting any of the control bits enables the weak pull-downs for the corresponding pins.

When the internal pull-up is selected, the pin uses VDD as the pull-up source voltage. When the internal pull-down is selected, the pins are pulled down to Vss by an internal resistor. Make sure that there is no external pull-up source/pull-down sink when the internal pull-ups/pull-downs are enabled.

Note: Pull-ups and pull-downs on Change Notification (CN) pins should always be disabled whenever the port pin is configured as a digital output.

# EXAMPLE 11-1: PORT WRITE/READ EXAMPLE

| MOV 0xFF00, W0;<br>MOV W0, TRISB;                                                 | //Configure PORTB<15:8> as inputs and PORTB<7:0> as outputs                                                                                          |

|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| NOP ;                                                                             | //Delay 1 cycle                                                                                                                                      |

| BTSS PORTB, #13;                                                                  | //Next Instruction                                                                                                                                   |

| <pre>Equivalent `C' Code TRISB = 0xFF00; NOP(); if(PORTBbits.RB13 == 1) { }</pre> | <pre>//Configure PORTB&lt;15:8&gt; as inputs and PORTB&lt;7:0&gt; as outputs //Delay 1 cycle // execute following code if PORTB pin 13 is set.</pre> |

#### SSPxCON1: MSSPx CONTROL REGISTER 1 (I<sup>2</sup>C<sup>™</sup> MODE) REGISTER 14-4: U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 bit 15 bit 8 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 SSPM0<sup>(2)</sup> SSPOV SSPEN<sup>(1)</sup> CKP SSPM3<sup>(2)</sup> SSPM2(2) SSPM1<sup>(2)</sup> WCOL bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15-8 Unimplemented: Read as '0' bit 7 WCOL: Write Collision Detect bit In Master Transmit mode: 1 = A write to the SSPxBUF register was attempted while the I<sup>2</sup>C conditions were not valid for a transmission to be started (must be cleared in software) 0 = No collisionIn Slave Transmit mode: 1 = The SSPxBUF register is written while it is still transmitting the previous word (must be cleared in software) 0 = No collision In Receive mode (Master or Slave modes): This is a "don't care" bit. bit 6 SSPOV: Master Synchronous Serial Port Receive Overflow Indicator bit In Receive mode: 1 = A byte is received while the SSPxBUF register is still holding the previous byte (must be cleared in software) 0 = No overflow In Transmit mode: This is a "don't care" bit in Transmit mode. SSPEN: Master Synchronous Serial Port Enable bit<sup>(1)</sup> bit 5 1 = Enables the serial port and configures the SDAx and SCLx pins as the serial port pins 0 = Disables the serial port and configures these pins as I/O port pins bit 4 CKP: SCLx Release Control bit In Slave mode: 1 = Releases clock 0 = Holds clock low (clock stretch), used to ensure data setup time In Master mode: Unused in this mode. SSPM<3:0>: Master Synchronous Serial Port Mode Select bits<sup>(2)</sup> bit 3-0 1111 = $I^2C$ Slave mode, 10-bit address with Start and Stop bit interrupts enabled 1110 = $I^2C$ Slave mode, 7-bit address with Start and Stop bit interrupts enabled $1011 = I^2C$ Firmware Controlled Master mode (Slave Idle) 1000 = $I^2C$ Master mode, Clock = Fosc/(2 \* ([SSPxADD] + 1))<sup>(3)</sup> 0111 = $I^2C$ Slave mode, 10-bit address $0110 = I^2C$ Slave mode, 7-bit address Note 1: When enabled, the SDAx and SCLx pins must be configured as inputs.

- 2: Bit combinations not specifically listed here are either reserved or implemented in SPI mode only.

- 3: SSPxADD values of 0, 1 or 2 are not supported when the Baud Rate Generator is used with I<sup>2</sup>C mode.

# 15.2 Transmitting in 8-Bit Data Mode

- 1. Set up the UARTx:

- a) Write the appropriate values for data, parity and Stop bits.

- b) Write the appropriate baud rate value to the UxBRG register.

- c) Set up transmit and receive interrupt enable and priority bits.

- 2. Enable the UARTx.

- 3. Set the UTXEN bit (causes a transmit interrupt, two cycles after being set).

- 4. Write the data byte to the lower byte of the UxTXREG word. The value will be immediately transferred to the Transmit Shift Register (TSR) and the serial bit stream will start shifting out with the next rising edge of the baud clock.

- Alternately, the data byte may be transferred while UTXEN = 0, and then, the user may set UTXEN. This will cause the serial bit stream to begin immediately, because the baud clock will start from a cleared state.

- 6. A transmit interrupt will be generated as per interrupt control bit, UTXISELx.

# 15.3 Transmitting in 9-Bit Data Mode

- 1. Set up the UARTx (as described in **Section 15.2** "**Transmitting in 8-Bit Data Mode**").

- 2. Enable the UARTx.

- 3. Set the UTXEN bit (causes a transmit interrupt, two cycles after being set).

- 4. Write UxTXREG as a 16-bit value only.

- 5. A word write to UxTXREG triggers the transfer of the 9-bit data to the TSR. The serial bit stream will start shifting out with the first rising edge of the baud clock.

- 6. A transmit interrupt will be generated as per the setting of control bit, UTXISELx.

# 15.4 Break and Sync Transmit Sequence

The following sequence will send a message frame header, made up of a Break, followed by an Auto-Baud Sync byte.

- 1. Configure the UARTx for the desired mode.

- 2. Set UTXEN and UTXBRK this sets up the Break character.

- 3. Load the UxTXREG with a dummy character to initiate transmission (value is ignored).

- 4. Write '55h' to UxTXREG loads the Sync character into the transmit FIFO.

- 5. After the Break has been sent, the UTXBRK bit is reset by hardware. The Sync character now transmits.

# 15.5 Receiving in 8-Bit or 9-Bit Data Mode

- 1. Set up the UARTx (as described in Section 15.2 "Transmitting in 8-Bit Data Mode").

- 2. Enable the UARTx.

- 3. A receive interrupt will be generated when one or more data characters have been received, as per interrupt control bit, URXISELx.

- 4. Read the OERR bit to determine if an overrun error has occurred. The OERR bit must be reset in software.

- 5. Read UxRXREG.

The act of reading the UxRXREG character will move the next character to the top of the receive FIFO, including a new set of PERR and FERR values.

# 15.6 Operation of UxCTS and UxRTS Control Pins

UARTx Clear-To-Send (UxCTS) and Request-To-Send (UxRTS) are the two hardware controlled pins that are associated with the UARTx module. These two pins allow the UARTx to operate in Simplex and Flow Control modes. They are implemented to control the transmission and reception between the Data Terminal Equipment (DTE). The UEN<1:0> bits in the UxMODE register configure these pins.

# 15.7 Infrared Support

The UARTx module provides two types of infrared UARTx support: one is the IrDA clock output to support an external IrDA encoder and decoder device (legacy module support), and the other is the full implementation of the IrDA encoder and decoder.

As the IrDA modes require a 16x baud clock, they will only work when the BRGH bit (UxMODE<3>) is '0'.

#### 15.7.1 EXTERNAL IrDA SUPPORT – IrDA CLOCK OUTPUT

To support external IrDA encoder and decoder devices, the UxBCLK pin (same as the UxRTS pin) can be configured to generate the 16x baud clock. When UEN<1:0> = 11, the UxBCLK pin will output the 16x baud clock if the UARTx module is enabled; it can be used to support the IrDA codec chip.

# 15.7.2 BUILT-IN IrDA ENCODER AND DECODER

The UARTx has full implementation of the IrDA encoder and decoder as part of the UARTx module. The built-in IrDA encoder and decoder functionality is enabled using the IREN bit (UxMODE<12>). When enabled (IREN = 1), the receive pin (UxRX) acts as the input from the infrared receiver. The transmit pin (UxTX) acts as the output to the infrared transmitter.

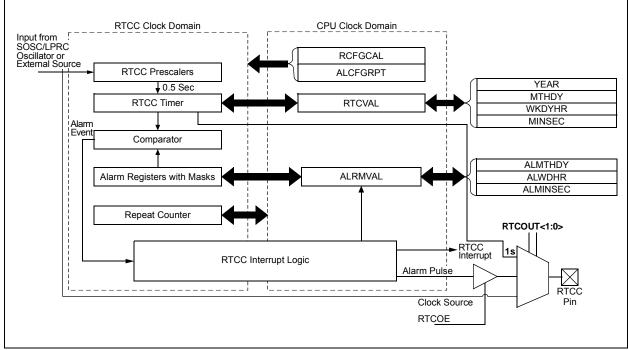

# 16.0 REAL-TIME CLOCK AND CALENDAR (RTCC)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the Real-Time Clock and Calendar, refer to the "PIC24F Family Reference Manual", "Real-Time Clock and Calendar (RTCC)" (DS39696).

The RTCC provides the user with a Real-Time Clock and Calendar (RTCC) function that can be calibrated.

Key features of the RTCC module are:

- · Operates in Sleep and Retention Sleep modes

- · Selectable clock source

- Provides hours, minutes and seconds using 24-hour format

- · Visibility of one half second period

- Provides calendar weekday, date, month and year

- Alarm-configurable for half a second, one second, 10 seconds, one minute, 10 minutes, one hour, one day, one week, one month or one year

- · Alarm repeat with decrementing counter

- · Alarm with indefinite repeat chime

- Year 2000 to 2099 leap year correction

- · BCD format for smaller software overhead

- Optimized for long term battery operation

- User calibration of the 32.768 kHz clock crystal/32K INTRC frequency with periodic auto-adjust

- · Optimized for long term battery operation

- · Fractional second synchronization

- Calibration to within ±2.64 seconds error per month

- · Calibrates up to 260 ppm of crystal error

- Ability to periodically wake-up external devices without CPU intervention (external power control)

- · Power control output for external circuit control

- · Calibration takes effect every 15 seconds

- · Runs from any one of the following:

- External Real-Time Clock of 32.768 kHz

- Internal 31.25 kHz LPRC Clock

- 50 Hz or 60 Hz External Input

# 16.1 RTCC Source Clock

The user can select between the SOSC crystal oscillator, LPRC internal oscillator or an external 50 Hz/60 Hz power line input as the clock reference for the RTCC module. This gives the user an option to trade off system cost, accuracy and power consumption, based on the overall system needs.

# FIGURE 16-1: RTCC BLOCK DIAGRAM

# 16.2 RTCC Module Registers

The RTCC module registers are organized into three categories:

- RTCC Control Registers

- RTCC Value Registers

- · Alarm Value Registers

#### 16.2.1 REGISTER MAPPING

To limit the register interface, the RTCC Timer and Alarm Time registers are accessed through corresponding register pointers. The RTCC Value register window (RTCVALH and RTCVALL) uses the RTCPTRx bits (RCFGCAL<9:8>) to select the desired Timer register pair (see Table 16-1).

By writing the RTCVALH byte, the RTCC Pointer value, the RTCPTR<1:0> bits decrement by one until they reach '00'. Once they reach '00', the MINUTES and SECONDS value will be accessible through RTCVALH and RTCVALL until the pointer value is manually changed.

TABLE 16-1: RTCVAL REGISTER MAPPING

| RTCPTR<1:0> | RTCC Value Register Window |             |  |  |  |

|-------------|----------------------------|-------------|--|--|--|

|             | RTCVAL<15:8>               | RTCVAL<7:0> |  |  |  |

| 00          | MINUTES                    | SECONDS     |  |  |  |

| 01          | WEEKDAY                    | HOURS       |  |  |  |

| 10          | MONTH                      | DAY         |  |  |  |

| 11          | _                          | YEAR        |  |  |  |

The Alarm Value register window (ALRMVALH and ALRMVALL) uses the ALRMPTRx bits (ALCFGRPT<9:8>) to select the desired Alarm register pair (see Table 16-2).

By writing the ALRMVALH byte, the ALRMPTR<1:0> bits (Alarm Pointer value) decrement by one until they reach '00'. Once they reach '00', the ALRMMIN and ALRMSEC value will be accessible through ALRMVALH and ALRMVALL, until the pointer value is manually changed.

#### TABLE 16-2: ALRMVAL REGISTER MAPPING

| ALRMPTR | Alarm Value Register Window |               |  |  |  |

|---------|-----------------------------|---------------|--|--|--|

| <1:0>   | ALRMVALH<15:8>              | ALRMVALL<7:0> |  |  |  |

| 00      | ALRMMIN                     | ALRMSEC       |  |  |  |

| 01      | ALRMWD                      | ALRMHR        |  |  |  |

| 10      | ALRMMNTH                    | ALRMDAY       |  |  |  |

| 11      | PWCSTAB                     | PWCSAMP       |  |  |  |

Considering that the 16-bit core does not distinguish between 8-bit and 16-bit read operations, the user must be aware that when reading either the ALRMVALH or ALRMVALL bytes, the ALRMPTR<1:0> value will be decremented. The same applies to the RTCVALH or RTCVALL bytes with the RTCPTR<1:0> being decremented.

**Note:** This only applies to read operations and not write operations.

### 16.2.2 WRITE LOCK

In order to perform a write to any of the RTCC Timer registers, the RTCWREN bit (RCFGCAL<13>) must be set (see Example 16-1 and Example 16-2).

| Note: | To avoid accidental writes to the timer, it is recommended that the RTCWREN bit (RCFGCAL<13>) is kept clear at any |

|-------|--------------------------------------------------------------------------------------------------------------------|

|       | other time. For the RTCWREN bit to be                                                                              |

|       | set, there is only one instruction cycle time                                                                      |

|       | window allowed between the 55h/AA                                                                                  |

|       | sequence and the setting of RTCWREN.                                                                               |

|       | Therefore, it is recommended that code                                                                             |

|       | follow the procedure in Example 16-2.                                                                              |

# 16.2.3 SELECTING RTCC CLOCK SOURCE

There are four reference source clock options that can be selected for the RTCC using the RTCCLK<1:0> bits (RTCPWC<11:10>): 00 = Secondary Oscillator, 01 = LPRC, 10 = 50 Hz External Clock and 11 = 60 Hz External Clock.

|  | EXAMPLE 16-1: | SETTING THE RTCWREN BIT IN ASSEMBLY |

|--|---------------|-------------------------------------|

|--|---------------|-------------------------------------|

| push<br>push | w7<br>w8     | ; Store W7 and W8 values on the stack.                   |

|--------------|--------------|----------------------------------------------------------|

| disi         | #5           | ; Disable interrupts until sequence is complete.         |

| mov          | #0x55, w7    | ; Write 0x55 unlock value to NVMKEY.                     |

| mov          | w7, NVMKEY   |                                                          |

| mov          | #0xAA, w8    | ; Write 0xAA unlock value to NVMKEY.                     |

| mov          | w8, NVMKEY   |                                                          |

| bset         | RCFGCAL, #13 | ; Set the RTCWREN bit.                                   |

| pop          | w8           | ; Restore the original W register values from the stack. |

| pop          | w7           |                                                          |

#### EXAMPLE 16-2: SETTING THE RTCWREN BIT IN 'C'

//This builtin function executes implements the unlock sequence and sets

//the RTCWREN bit.

\_\_builtin\_write\_RTCWEN();

NOTES:

| R/W-0        | U-0                                                                                                                    | R/W-0                                                                                                                                                     | R/W-0          | R/W-0                            | U-0              | R/W-0           | R/W-0        |  |

|--------------|------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------------------------|------------------|-----------------|--------------|--|

| DACEN        |                                                                                                                        | DACSIDL                                                                                                                                                   | DACSLP         | DACFM                            |                  | SRDIS           | DACTRIG      |  |

| bit 15       |                                                                                                                        |                                                                                                                                                           | 27.002         |                                  |                  | 0.12.0          | bit 8        |  |

| R/W-0        | R/W-0                                                                                                                  | R/W-0                                                                                                                                                     | R/W-0          | R/W-0                            | R/W-0            | R/W-0           | R/W-0        |  |

| DACOE        | DACTSEL4                                                                                                               | DACTSEL3                                                                                                                                                  | DACTSEL2       | DACTSEL1                         | DACTSEL0         | DACREF1         | DACREF0      |  |

| bit 7        |                                                                                                                        |                                                                                                                                                           |                |                                  |                  |                 | bit 0        |  |

| Legend:      |                                                                                                                        |                                                                                                                                                           |                |                                  |                  |                 |              |  |

| R = Readab   | le bit                                                                                                                 | W = Writable                                                                                                                                              | bit            | U = Unimplen                     | nented bit, read | l as '0'        |              |  |

| -n = Value a | t POR                                                                                                                  | '1' = Bit is set                                                                                                                                          |                | '0' = Bit is clea                |                  | x = Bit is unkr | nown         |  |

|              |                                                                                                                        |                                                                                                                                                           |                |                                  |                  |                 | -            |  |

| bit 15       | DACEN: DAC                                                                                                             | x Enable bit                                                                                                                                              |                |                                  |                  |                 |              |  |

|              | 1 = Module is                                                                                                          | s enabled                                                                                                                                                 |                |                                  |                  |                 |              |  |

|              | 0 = Module is                                                                                                          | s disabled                                                                                                                                                |                |                                  |                  |                 |              |  |

| bit 14       | Unimplement                                                                                                            | ted: Read as 'd                                                                                                                                           | )'             |                                  |                  |                 |              |  |

| bit 13       | DACSIDL: DACx Stop in Idle Mode bit                                                                                    |                                                                                                                                                           |                |                                  |                  |                 |              |  |

|              |                                                                                                                        | ues module op<br>s module opera                                                                                                                           |                | device enters lo<br>ode          | lle mode         |                 |              |  |

| bit 12       | DACSLP: DA                                                                                                             | Cx Enable Per                                                                                                                                             | ipheral During | Sleep bit                        |                  |                 |              |  |

|              |                                                                                                                        |                                                                                                                                                           |                | ent value of DA<br>; DACxOUT pi  |                  |                 | nd LATx bits |  |

| bit 11       | DACFM: DAC                                                                                                             | x Data Format                                                                                                                                             | Select bit     |                                  |                  |                 |              |  |

|              | 1 = Data is left justified (data stored in DACxDAT<15:8>)<br>0 = Data is right justified (data stored in DACxDAT<7:0>) |                                                                                                                                                           |                |                                  |                  |                 |              |  |

| bit 10       | Unimplement                                                                                                            | ted: Read as '0                                                                                                                                           | )'             |                                  |                  |                 |              |  |

| bit 9        | SRDIS: Soft F                                                                                                          | Reset Disable b                                                                                                                                           | oit            |                                  |                  |                 |              |  |

|              |                                                                                                                        | <ul> <li>1 = DACxCON and DACxDAT SFRs reset only on a POR or BOR Reset</li> <li>0 = DACxCON and DACxDAT SFRs reset on any type of device Reset</li> </ul> |                |                                  |                  |                 |              |  |

| bit 8        |                                                                                                                        | ACx Trigger Inp                                                                                                                                           |                |                                  |                  |                 |              |  |

|              |                                                                                                                        |                                                                                                                                                           |                | selected (by D<br>as DACxDAT is  |                  |                 | ed)          |  |

| bit 7        | DACOE: DAC                                                                                                             | Cx Output Enab                                                                                                                                            | le bit         |                                  |                  |                 |              |  |

|              | 1 = DACx out                                                                                                           | put pin is enabl                                                                                                                                          | led and driven | on the DACxO<br>put is available |                  | her peripherals | only         |  |

| Note 1.      |                                                                                                                        | in configuration                                                                                                                                          |                |                                  | -1.0~)           |                 | -            |  |

### REGISTER 20-1: DACxCON: DACx CONTROL REGISTER

**Note 1:** BGBUF1 voltage is configured by BUFREF<1:0> (BUFCON0<1:0>).

# REGISTER 25-8: DEVID: DEVICE ID REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0    |

|--------|-----|-----|-----|-----|-----|-----|--------|

| —      | —   | —   | —   | —   | —   | —   | —      |

| bit 23 |     |     |     |     |     |     | bit 16 |

| R      | R      | R      | R      | R      | R      | R      | R      |

|--------|--------|--------|--------|--------|--------|--------|--------|

| FAMID7 | FAMID6 | FAMID5 | FAMID4 | FAMID3 | FAMID2 | FAMID1 | FAMID0 |

| bit 15 |        |        |        |        |        |        | bit 8  |

| R     | R    | R    | R    | R    | R    | R    | R     |

|-------|------|------|------|------|------|------|-------|

| DEV7  | DEV6 | DEV5 | DEV4 | DEV3 | DEV2 | DEV1 | DEV0  |

| bit 7 |      |      |      |      |      |      | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 23-16 | Unimplemented: Read as '0'                  |

|-----------|---------------------------------------------|

| bit 15-8  | FAMID<7:0>: Device Family Identifier bits   |

|           | 01000101 = PIC24FV16KM204 family            |

| bit 7-0   | DEV<7:0>: Individual Device Identifier bits |

|           | 00011111 = PIC24FV16KM204                   |

|           | 00011011 = PIC24FV16KM202                   |

|           | 00010111 = PIC24FV08KM204                   |

|           | 00010011 = PIC24FV08KM202                   |

|           | 00001111 = PIC24FV16KM104                   |

|           | 00001011 = PIC24FV16KM102                   |

|           | 00000011 = PIC24FV08KM102                   |

|           | 00000001 = PIC24FV08KM101                   |

|           | 00011110 = PIC24F16KM204                    |

|           | 00011010 = PIC24F16KM202                    |

|           | 00010110 = PIC24F08KM204                    |

|           | 00010010 = PIC24F08KM202                    |

|           | 00001110 = PIC24F16KM104                    |

|           | 00001010 = PIC24F16KM102                    |

|           | 00000010 = PIC24F08KM102                    |

|           | 0000000 = PIC24F08KM101                     |

# 26.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16 and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

# 26.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

# 26.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 26.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- · MPLAB X IDE compatibility

# 26.11 Demonstration/Development Boards, Evaluation Kits and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

# 26.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

### TABLE 27-4: HIGH/LOW-VOLTAGE DETECT CHARACTERISTICS

|              | Standard Operating Conditions: 1.8V to 3.6V (PIC24F16KM204)<br>2.0V to 5.5V (PIC24FV16KM204)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                   |                                  |      |      |      |       |            |  |  |  |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------------------------|------|------|------|-------|------------|--|--|--|--|

| Param<br>No. | Symbol                                                                                                                                                                                                                          | Chara             | octeristic                       | Min  | Тур  | Max  | Units | Conditions |  |  |  |  |

| DC18         | Vhlvd                                                                                                                                                                                                                           | HLVD Voltage on   | HLVDL<3:0> = 0000 <sup>(2)</sup> | _    | _    | 1.90 | V     |            |  |  |  |  |

|              |                                                                                                                                                                                                                                 | VDD Transition    | HLVDL<3:0> = 0001                | 1.88 | —    | 2.13 | V     |            |  |  |  |  |

|              |                                                                                                                                                                                                                                 |                   | HLVDL<3:0> = 0010                | 2.09 | —    | 2.35 | V     |            |  |  |  |  |

|              |                                                                                                                                                                                                                                 | HLVDL<3:0> = 0011 | 2.25                             | —    | 2.53 | V    |       |            |  |  |  |  |

|              |                                                                                                                                                                                                                                 |                   | HLVDL<3:0> = 0100                | 2.35 | —    | 2.62 | V     |            |  |  |  |  |