Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

÷ХГ

| Product Status             | Active                                                                        |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 23                                                                            |

| Program Memory Size        | 8KB (2.75K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5V                                                                       |

| Data Converters            | A/D 19x10b/12b; D/A 2x8b                                                      |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

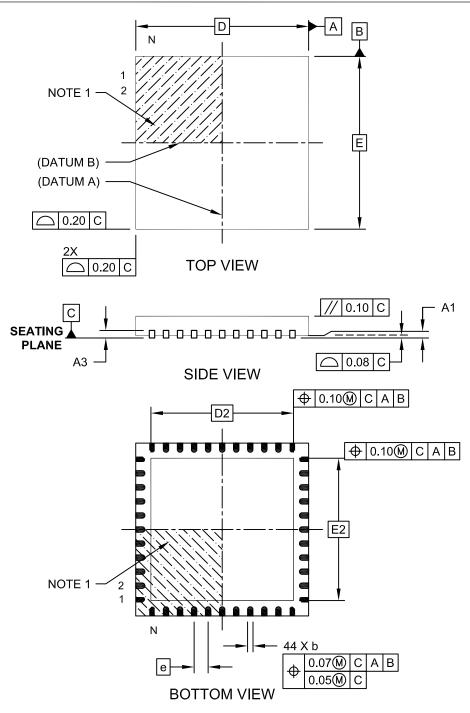

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-VQFN Exposed Pad                                                           |

| Supplier Device Package    | 28-QFN (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fv08km202-i-ml |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Pin Diagrams (Continued)

| 20-1     | Pin SPDIP/SSOP/SOIC       MCLR/RA5       1       28       AVDD         RA0       2       27       AVss         RA1       23       26       RB15         RB0       4       C25       RB14         RB1       5       24       RB13         RB2       6       23       RB12         RB3       7       22       RB11         Vss       8       21       RB10         RA3       10       C0       RA6 or Vbbcore         RA3       10       C0       RA7         RB4       111       18       RB9         RA4       112       17       RB8         Vob       13       16       RB7         RB5<       14       15       RB6 |  |  |  |  |  |  |  |  |  |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Pin      | Pin Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |  |

|          | PIC24FXXKMX02 PIC24FVXXKMX02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |  |

| 1        | MCLR/Vpp/RA5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |  |

| 2        | CVREF+/VREF+/ /AN0/ /CN2/RA0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |  |

| 3        | CVREF-/VREF-/AN1/CN3/RA1 CVREF-/VREF-/AN1/RA1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |

| 4        | PGED1/AN2/CTCMP/ULPWU/C1IND/ / / /CN4/RB0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |  |

| 5        | PGEC1/ / /AN3/C1INC/ / /CTED12/CN5/RB1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |  |

| 6        | / /AN4/C1INB/ / /U1RX/TCKIB/CTED13/CN6/RB2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |  |

| 7        | /AN5/C1INA/ / /CN7/RB3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |  |

| 8        | Vss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |

| 9        | OSCI/CLKI/AN13/CN30/RA2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |

| 10       | OSCO/CLKO/AN14/CN29/RA3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |

| 11       | SOSCI/AN15/ / /CN1/RB4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |  |

| 12       | SOSCO/SCLKI/AN16/PWRLCLK/ /CN0/RA4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |

| 13       | VDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |

| 14       | PGED3/AN17/ASDA1/ / /OC1E/CLCINA/CN27/RB5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |  |

| 15       | PGEC3/AN18/ASCL1/ / /OC1F/CLCINB/CN24/RB6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |  |

| 16       | AN19/U1TX/INT0/CN23/RB7 AN19/U1TX/ / /INT0/CN23/RB7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |

| 17       | AN20/SCL1/U1CTS/C3OUT/OC1B/CTED10/CN22/RB8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |  |

| 18       | AN21/SDA1/T1CK/U1RTS/U1BCLK/IC2/ /CLC10/CTED4/CN21/RB9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |  |

| 19       | /IC1/ / /CTED3/CN9/RA7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |  |

| 20       | /OC1A/CTED1/INT2/CN8/RA6 VCAP OR VDDCORE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |

| 21<br>22 | PGED2/SDI1/ /OC1C/CTED11/CN16/RB10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |

| 22<br>23 | PGEC2/SCK1/OC2A/CTED9/CN15/RB11           /AN12/HLVDIN/         /           /AN12/HLVDIN/         /           /B12         //                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |

| 24       | / /AN11/SD01/OCFB/ /OC1D/CTPLS/CN13/RB13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |

| 25       | /CVREF/ / /AN10/ / /C1OUT/OCFA/CTED5/INT1/CN12/RB14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |

| 26       | / /AN9/ /REFO/SS1/TCKIA/CTED6/CN11/RB15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |

| 27       | Vss/AVss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |

| 28       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |  |

Legend: Values in indicate pin function differences between PIC24F(V)XXKM202 and PIC24F(V)XXKM102 devices.

### TABLE 1-5: PIC24FV16KM204 FAMILY PINOUT DESCRIPTION (CONTINUED)

|          |                                  |                                  | F             |                        |                |                                  |                                  | FV            |                        |                |     |        |                                 |

|----------|----------------------------------|----------------------------------|---------------|------------------------|----------------|----------------------------------|----------------------------------|---------------|------------------------|----------------|-----|--------|---------------------------------|

|          |                                  |                                  | Pin Numb      | er                     |                |                                  |                                  | Pin Numb      | er                     |                |     |        |                                 |

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | I/O | Buffer | Description                     |

| RB9      | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | I/O | ST     | PORTB Pins                      |

| RB10     | —                                | 21                               | 18            | 8                      | 9              | _                                | 21                               | 18            | 8                      | 9              | I/O | ST     | PORTB Pins                      |

| RB11     | —                                | 22                               | 19            | 9                      | 10             | _                                | 22                               | 19            | 9                      | 10             | I/O | ST     | PORTB Pins                      |

| RB12     | 15                               | 23                               | 20            | 10                     | 11             | 15                               | 23                               | 20            | 10                     | 11             | I/O | ST     | PORTB Pins                      |

| RB13     | 16                               | 24                               | 21            | 11                     | 12             | 16                               | 24                               | 21            | 11                     | 12             | I/O | ST     | PORTB Pins                      |

| RB14     | 17                               | 25                               | 22            | 14                     | 15             | 17                               | 25                               | 22            | 14                     | 15             | I/O | ST     | PORTB Pins                      |

| RB15     | 18                               | 26                               | 23            | 15                     | 16             | 18                               | 26                               | 23            | 15                     | 16             | I/O | ST     | PORTB Pins                      |

| RC0      | —                                | _                                |               | 25                     | 27             | _                                |                                  |               | 25                     | 27             | I/O | ST     | PORTC Pins                      |

| RC1      | —                                | _                                | _             | 26                     | 28             | _                                | _                                | _             | 26                     | 28             | I/O | ST     | PORTC Pins                      |

| RC2      | —                                | _                                | _             | 27                     | 29             | _                                | _                                | _             | 27                     | 29             | I/O | ST     | PORTC Pins                      |

| RC3      | —                                | _                                | _             | 36                     | 39             | _                                | _                                | _             | 36                     | 39             | I/O | ST     | PORTC Pins                      |

| RC4      | —                                | _                                | _             | 37                     | 40             | _                                | _                                | _             | 37                     | 40             | I/O | ST     | PORTC Pins                      |

| RC5      | —                                | _                                | _             | 38                     | 41             | _                                | _                                | _             | 38                     | 41             | I/O | ST     | PORTC Pins                      |

| RC6      | —                                | _                                | _             | 2                      | 2              | _                                | _                                | _             | 2                      | 2              | I/O | ST     | PORTC Pins                      |

| RC7      | —                                | _                                | _             | 3                      | 3              | _                                | _                                | _             | 3                      | 3              | I/O | ST     | PORTC Pins                      |

| RC8      | —                                | _                                | _             | 4                      | 4              | _                                | _                                | _             | 4                      | 4              | I/O | ST     | PORTC Pins                      |

| RC9      | —                                | _                                | _             | 5                      | 5              | _                                | _                                | _             | 5                      | 5              | I/O | ST     | PORTC Pins                      |

| REFO     | 18                               | 26                               | 23            | 15                     | 16             | 18                               | 26                               | 23            | 15                     | 16             | 0   | _      | Reference Clock Output          |

| RTCC     | —                                | 25                               | 22            | 14                     | 15             | _                                | 25                               | 22            | 14                     | 15             | 0   | _      | Real-Time Clock/Calendar Output |

| SCK1     | 15                               | 22                               | 19            | 9                      | 10             | 15                               | 22                               | 19            | 9                      | 10             | I/O | ST     | MSSP1 SPI Clock                 |

| SDI1     | 17                               | 21                               | 18            | 8                      | 9              | 17                               | 21                               | 18            | 8                      | 9              | Ι   | ST     | MSSP1 SPI Data Input            |

| SDO1     | 16                               | 24                               | 21            | 11                     | 12             | 16                               | 24                               | 21            | 11                     | 12             | 0   |        | MSSP1 SPI Data Output           |

| SS1      | 18                               | 26                               | 23            | 15                     | 16             | 18                               | 26                               | 23            | 15                     | 16             | I   | ST     | MSSP1 SPI Slave Select Input    |

| SCK2     | —                                | 14                               | 11            | 38                     | 41             | _                                | 14                               | 11            | 38                     | 41             | I/O | ST     | MSSP2 SPI Clock                 |

| SDI2     | —                                | 19                               | 16            | 36                     | 39             | _                                | 19                               | 16            | 36                     | 39             | Ι   | ST     | MSSP2 SPI Data Input            |

| SDO2     | —                                | 15                               | 12            | 37                     | 40             | —                                | 15                               | 12            | 37                     | 40             | 0   |        | MSSP2 SPI Data Output           |

| SS2      | —                                | 23                               | 20            | 35                     | 38             | _                                | 23                               | 20            | 35                     | 38             | Ι   | ST     | MSSP2 SPI Slave Select Input    |

**Legend:** ANA = Analog level input/output, ST = Schmitt Trigger input buffer,  $I^2C^{TM} = I^2C/SMBus$  input buffer

### TABLE 4-11: SCCP4 REGISTER MAP

| File Name                | Addr. | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11  | Bit 10  | Bit 9     | Bit 8        | Bit 7         | Bit 6       | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1  | Bit 0  | All<br>Resets |

|--------------------------|-------|---------|--------|---------|--------|---------|---------|-----------|--------------|---------------|-------------|---------|---------|---------|---------|--------|--------|---------------|

| CCP4CON1L <sup>(1)</sup> | 1ACh  | CCPON   | _      | CCPSIDL | r      | TMRSYNC | CLKSEL2 | CLKSEL1   | CLKSEL0      | TMRPS1        | TMRPS0      | T32     | CCSEL   | MOD3    | MOD2    | MOD1   | MOD0   | 0000          |

| CCP4CON1H(1)             | 1AEh  | OPSSRC  | RTRGEN | —       | _      | IOPS3   | IOPS2   | IOPS1     | IOPS0        | TRIGEN        | ONESHOT     | ALTSYNC | SYNC4   | SYNC3   | SYNC2   | SYNC1  | SYNC0  | 0000          |

| CCP4CON2L <sup>(1)</sup> | 1B0h  | PWMRSEN | ASDGM  | _       | SSDG   | _       | _       | _         | _            | ASDG7         | ASDG6       | ASDG5   | ASDG4   | ASDG3   | ASDG2   | ASDG1  | ASDG0  | 0000          |

| CCP4CON2H <sup>(1)</sup> | 1B2h  | OENSYNC | _      | _       | _      | _       | _       | _         | OCAEN        | ICGSM1        | ICGSM0      | _       | AUXOUT1 | AUXOUT0 | ICSEL2  | ICSEL1 | ICSEL0 | 0100          |

| CCP4CON3H <sup>(1)</sup> | 1B6h  | OETRIG  | OSCNT2 | OSCNT1  | OSCNT0 | _       | _       | _         | —            | _             | _           | POLACE  | _       | PSSACE1 | PSSACE0 | _      | —      | 0000          |

| CCP4STATL <sup>(1)</sup> | 1B8h  | _       | _      | _       |        | -       | _       | _         | _            | CCPTRIG       | TRSET       | TRCLR   | ASEVT   | SCEVT   | ICDIS   | ICOV   | ICBNE  | 0000          |

| CCP4TMRL <sup>(1)</sup>  | 1BCh  |         |        |         |        |         |         | SCCP4     | 1 Time Base  | Register Lo   | ow Word     |         |         |         |         |        |        | 0000          |

| CCP4TMRH <sup>(1)</sup>  | 1BEh  |         |        |         |        |         |         | SCCP4     | Time Base    | Register Hi   | gh Word     |         |         |         |         |        |        | 0000          |

| CCP4PRL <sup>(1)</sup>   | 1C0h  |         |        |         |        |         |         | SCCP4 Tir | ne Base Pe   | riod Registe  | er Low Word |         |         |         |         |        |        | FFFF          |

| CCP4PRH <sup>(1)</sup>   | 1C2h  |         |        |         |        |         |         | SCCP4 Tir | ne Base Pe   | riod Registe  | r High Word |         |         |         |         |        |        | FFFF          |

| CCP4RAL <sup>(1)</sup>   | 1C4h  |         |        |         |        |         |         | Out       | put Compar   | e 4 Data Wo   | ord A       |         |         |         |         |        |        | 0000          |

| CCP4RBL <sup>(1)</sup>   | 1C8h  |         |        |         |        |         |         | Out       | put Compar   | e 4 Data Wo   | ord B       |         |         |         |         |        |        | 0000          |

| CCP4BUFL <sup>(1)</sup>  | 1CCh  |         |        |         |        |         |         | Input C   | Capture 4 Da | ata Buffer Lo | w Word      |         |         |         |         |        |        | 0000          |

| CCP4BUFH <sup>(1)</sup>  | 1CEh  |         |        |         |        |         |         | Input C   | apture 4 Da  | ita Buffer Hi | gh Word     |         |         |         |         |        |        | 0000          |

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

**Note 1:** These registers are available only on PIC24F(V)16KM2XX devices.

#### 6.4.1 ERASE DATA EEPROM

The data EEPROM can be fully erased, or can be partially erased, at three different sizes: one word, four words or eight words. The bits, NVMOP<1:0> (NVMCON<1:0>), decide the number of words to be erased. To erase partially from the data EEPROM, the following sequence must be followed:

- 1. Configure NVMCON to erase the required number of words: one, four or eight.

- 2. Load TBLPAG and WREG with the EEPROM address to be erased.

- 3. Clear the NVMIF status bit and enable the NVM interrupt (optional).

- 4. Write the key sequence to NVMKEY.

- 5. Set the WR bit to begin the erase cycle.

- 6. Either poll the WR bit or wait for the NVM interrupt (NVMIF is set).

A typical erase sequence is provided in Example 6-2. This example shows how to do a one-word erase. Similarly, a four-word erase and an eight-word erase can be done. This example uses C library procedures to manage the Table Pointer (builtin\_tblpage and builtin\_tbloffset) and the Erase Page Pointer (builtin\_tblwt1). The memory unlock sequence (builtin\_write\_NVM) also sets the WR bit to initiate the operation and returns control when complete.

#### EXAMPLE 6-2: SINGLE-WORD ERASE

```

int __attribute__ ((space(eedata))) eeData = 0x1234;

/*_____

The variable eeData must be a Global variable declared outside of any method

the code following this comment can be written inside the method that will execute the erase

_____

*/

unsigned int offset;

// Set up NVMCON to erase one word of data EEPROM

NVMCON = 0 \times 4058;

// Set up a pointer to the EEPROM location to be erased

TBLPAG = __builtin_tblpage(&eeData); // Initialize EE Data page pointer

offset = __builtin_tbloffset(&eeData);

// Initizlize lower word of address

__builtin_tblwtl(offset, 0);

// Write EEPROM data to write latch

asm volatile ("disi #5");

// Disable Interrupts For 5 Instructions

__builtin_write_NVM();

// Issue Unlock Sequence & Start Write Cycle

while(NVMCONbits.WR=1);

// Optional: Poll WR bit to wait for

// write sequence to complete

```

### REGISTER 8-2: CORCON: CPU CONTROL REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

|        | —   | —   | —   | —   |     |     | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | R/C-0, HSC          | R/W-0              | U-0 | U-0   |

|-------|-----|-----|-----|---------------------|--------------------|-----|-------|

| —     | —   | —   | —   | IPL3 <sup>(2)</sup> | PSV <sup>(1)</sup> | —   | —     |

| bit 7 |     |     |     |                     |                    |     | bit 0 |

| Legend:           | C = Clearable bit | HSC = Hardware Settal  | ble/Clearable bit  |

|-------------------|-------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-4 Unimplemented: Read as '0'

bit 3 IPL3: CPU Interrupt Priority Level Status bit<sup>(2)</sup> 1 = CPU Interrupt Priority Level is greater than 7 0 = CPU Interrupt Priority Level is 7 or less

bit 1-0 Unimplemented: Read as '0'

**Note 1:** See Register 3-2 for the description of this bit, which is not dedicated to interrupt control functions.

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

Note: Bit 2 is described in Section 3.0 "CPU".

### REGISTER 8-16: IEC4: INTERRUPT ENABLE CONTROL REGISTER 4

| DAC2IE                                         | R/W-0                                                                                                                                                                                                                                                                                                                           | R/W-0                                                                                                                                  | U-0                                                                                                           | U-0               | U-0             | U-0             | R/W-0  |  |

|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-------------------|-----------------|-----------------|--------|--|

| DROLL                                          | DAC1IE                                                                                                                                                                                                                                                                                                                          | CTMUIE                                                                                                                                 | _                                                                                                             |                   | _               | _               | HLVDIE |  |

| bit 15                                         |                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                        |                                                                                                               |                   |                 |                 | bit 8  |  |

|                                                |                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                        |                                                                                                               |                   | <b>D</b> 444 0  | <b>D</b> 444 0  |        |  |

| U-0                                            | U-0                                                                                                                                                                                                                                                                                                                             | U-0                                                                                                                                    | U-0                                                                                                           | U-0               | R/W-0           | R/W-0           | U-0    |  |

|                                                |                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                        | —                                                                                                             |                   | U2ERIE          | U1ERIE          |        |  |

| bit 7                                          |                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                        |                                                                                                               |                   |                 |                 | bit (  |  |

| Legend:                                        |                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                        |                                                                                                               |                   |                 |                 |        |  |

| R = Readable                                   | e bit                                                                                                                                                                                                                                                                                                                           | W = Writable b                                                                                                                         | pit                                                                                                           | U = Unimplem      | ented bit, read | d as '0'        |        |  |

| -n = Value at                                  | POR                                                                                                                                                                                                                                                                                                                             | '1' = Bit is set                                                                                                                       |                                                                                                               | '0' = Bit is clea | ired            | x = Bit is unkn | iown   |  |

| bit 13                                         | DAC1IE: Digital-to-Analog Converter 1 Interrupt Enable bit <ol> <li>I = Interrupt request is enabled</li> <li>Interrupt request is not enabled</li> </ol> CTMUIE: CTMU Interrupt Enable bit <ol> <li>I = Interrupt request is enabled</li> <li>Interrupt request is not enabled</li> </ol> 0 = Interrupt request is not enabled |                                                                                                                                        |                                                                                                               |                   |                 |                 |        |  |

|                                                | -                                                                                                                                                                                                                                                                                                                               | -                                                                                                                                      | nabled                                                                                                        |                   |                 |                 |        |  |

|                                                | Unimplemen<br>HLVDIE: High<br>1 = Interrupt r                                                                                                                                                                                                                                                                                   | request is not er<br>ted: Read as '0<br>n/Low-Voltage D<br>request is enabl<br>request is not er                                       | nabled<br>,<br>vetect Interrup<br>ed                                                                          | t Enable bit      |                 |                 |        |  |

| bit 8                                          | Unimplemen<br>HLVDIE: High<br>1 = Interrupt r<br>0 = Interrupt r                                                                                                                                                                                                                                                                | ted: Read as '0<br>n/Low-Voltage D<br>request is enabl                                                                                 | nabled<br>,<br>vetect Interrup<br>ed<br>nabled                                                                | t Enable bit      |                 |                 |        |  |

| bit 8<br>bit 7-3                               | Unimplemen<br>HLVDIE: High<br>1 = Interrupt r<br>0 = Interrupt r<br>Unimplemen                                                                                                                                                                                                                                                  | ted: Read as '0<br>n/Low-Voltage D<br>equest is enabl<br>equest is not er                                                              | nabled<br>,<br>vetect Interrup<br>ed<br>nabled<br>,                                                           | t Enable bit      |                 |                 |        |  |

| bit 8<br>bit 7-3                               | Unimplemen<br>HLVDIE: High<br>1 = Interrupt r<br>0 = Interrupt r<br>Unimplemen<br>U2ERIE: UAF<br>1 = Interrupt r                                                                                                                                                                                                                | ted: Read as '0<br>n/Low-Voltage D<br>request is enabl<br>request is not er<br>ted: Read as '0                                         | nabled<br>,<br>etect Interrup<br>ed<br>nabled<br>,<br>upt Enable bit<br>ed                                    | t Enable bit      |                 |                 |        |  |

| bit 12-9<br>bit 8<br>bit 7-3<br>bit 2<br>bit 1 | Unimplement<br>HLVDIE: High<br>1 = Interrupt r<br>0 = Interrupt r<br>Unimplement<br>U2ERIE: UAF<br>1 = Interrupt r<br>0 = Interrupt r<br>U1ERIE: UAF<br>1 = Interrupt r                                                                                                                                                         | ted: Read as '0<br>n/Low-Voltage D<br>request is enabl<br>request is not er<br>ted: Read as '0<br>RT2 Error Intern<br>request is enabl | nabled<br>,<br>vetect Interrup<br>ed<br>nabled<br>,<br>upt Enable bit<br>ed<br>nabled<br>upt Enable bit<br>ed | t Enable bit      |                 |                 |        |  |

### REGISTER 8-29: IPC15: INTERRUPT PRIORITY CONTROL REGISTER 15

| U-0           | U-0           | U-0                | U-0              | U-0               | R/W-1            | R/W-0              | R/W-0  |

|---------------|---------------|--------------------|------------------|-------------------|------------------|--------------------|--------|

|               | —             | _                  | —                |                   | RTCIP2           | RTCIP1             | RTCIP0 |

| bit 15        | -             | -                  |                  |                   |                  |                    | bit 8  |

|               |               |                    |                  |                   |                  |                    |        |

| U-0           | U-0           | U-0                | U-0              | U-0               | U-0              | U-0                | U-0    |

|               | —             | —                  | —                | —                 | —                | —                  | —      |

| bit 7         |               |                    |                  |                   |                  | -                  | bit 0  |

|               |               |                    |                  |                   |                  |                    |        |

| Legend:       |               |                    |                  |                   |                  |                    |        |

| R = Readable  | e bit         | W = Writable       | bit              | U = Unimplem      | nented bit, read | d as '0'           |        |

| -n = Value at | POR           | '1' = Bit is set   |                  | '0' = Bit is clea | ared             | x = Bit is unknown |        |

|               |               |                    |                  |                   |                  |                    |        |

| bit 15-11     | Unimplemen    | ted: Read as '     | )'               |                   |                  |                    |        |

| bit 10-8      | RTCIP<2:0>:   | Real-Time Clo      | ck and Calend    | ar Interrupt Pric | ority bits       |                    |        |

|               | 111 = Interru | pt is Priority 7 ( | highest priority | interrupt)        |                  |                    |        |

|               | •             |                    |                  |                   |                  |                    |        |

|               | •             |                    |                  |                   |                  |                    |        |

|               | •             |                    |                  |                   |                  |                    |        |

|               |               | pt is Priority 1   |                  |                   |                  |                    |        |

|               | 000 = Interru | pt source is dis   | abled            |                   |                  |                    |        |

| bit 7-0       | Unimplemen    | ted: Read as '     | )'               |                   |                  |                    |        |

|               |               |                    |                  |                   |                  |                    |        |

| R-0           | U-0                                                                                                                     | R/W-0                                                                                                                                                             | U-0              | R-0              | R-0               | R-0             | R-0              |  |  |  |  |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|-------------------|-----------------|------------------|--|--|--|--|--|

| CPUIRQ        |                                                                                                                         | VHOLD                                                                                                                                                             |                  | ILR3             | ILR2              | ILR1            | ILR0             |  |  |  |  |  |

| bit 15        |                                                                                                                         |                                                                                                                                                                   |                  |                  |                   |                 | bit 8            |  |  |  |  |  |

|               |                                                                                                                         |                                                                                                                                                                   |                  |                  |                   |                 |                  |  |  |  |  |  |

| U-0           |                                                                                                                         |                                                                                                                                                                   |                  |                  |                   | R-0             |                  |  |  |  |  |  |

| <br>bit 7     | VECNUM6                                                                                                                 | VECNUM5                                                                                                                                                           | VECNUM4          | VECNUM3          | VECNUM2           | VECNUM1         | VECNUM0<br>bit 0 |  |  |  |  |  |

|               |                                                                                                                         |                                                                                                                                                                   |                  |                  |                   |                 | 511 0            |  |  |  |  |  |

| Legend:       |                                                                                                                         |                                                                                                                                                                   |                  |                  |                   |                 |                  |  |  |  |  |  |

| R = Readable  | e bit                                                                                                                   | W = Writable                                                                                                                                                      | bit              | U = Unimpler     | nented bit, read  | l as '0'        |                  |  |  |  |  |  |

| -n = Value at | POR                                                                                                                     | '1' = Bit is set                                                                                                                                                  |                  | '0' = Bit is cle | ared              | x = Bit is unkr | nown             |  |  |  |  |  |

|               |                                                                                                                         |                                                                                                                                                                   |                  |                  |                   |                 |                  |  |  |  |  |  |

| bit 15        | CPUIRQ: Interrupt Request from Interrupt Controller CPU bit                                                             |                                                                                                                                                                   |                  |                  |                   |                 |                  |  |  |  |  |  |

|               |                                                                                                                         | 1 = An interrupt request has occurred but has not yet been Acknowledged by the CPU (this will happen when the CPU priority is higher than the interrupt priority) |                  |                  |                   |                 |                  |  |  |  |  |  |

|               |                                                                                                                         | upt request is l                                                                                                                                                  |                  |                  | (independency)    |                 |                  |  |  |  |  |  |

| bit 14        | Unimplemen                                                                                                              | ted: Read as '                                                                                                                                                    | 0'               |                  |                   |                 |                  |  |  |  |  |  |

| bit 13        | VHOLD: Vector Hold bit                                                                                                  |                                                                                                                                                                   |                  |                  |                   |                 |                  |  |  |  |  |  |

|               | Allows Vector Number Capture and Changes which Interrupt is Stored in the VECNUM<6:0> bits:                             |                                                                                                                                                                   |                  |                  |                   |                 |                  |  |  |  |  |  |

|               | 1 = VECNUM<6:0> will contain the value of the highest priority pending interrupt, instead of the                        |                                                                                                                                                                   |                  |                  |                   |                 |                  |  |  |  |  |  |

|               | current interrupt<br>0 = VECNUM<6:0> will contain the value of the last Acknowledged interrupt (last interrupt that has |                                                                                                                                                                   |                  |                  |                   |                 |                  |  |  |  |  |  |

|               |                                                                                                                         |                                                                                                                                                                   |                  |                  | ther interrupts a |                 | nupt that has    |  |  |  |  |  |

| bit 12        | Unimplemen                                                                                                              | ted: Read as '                                                                                                                                                    | 0'               |                  |                   |                 |                  |  |  |  |  |  |

| bit 11-8      | ILR<3:0>: Ne                                                                                                            | w CPU Interru                                                                                                                                                     | pt Priority Leve | el bits          |                   |                 |                  |  |  |  |  |  |

|               | 1111 <b>= CPU</b>                                                                                                       | Interrupt Priorit                                                                                                                                                 | ty Level is 15   |                  |                   |                 |                  |  |  |  |  |  |

|               | •                                                                                                                       |                                                                                                                                                                   |                  |                  |                   |                 |                  |  |  |  |  |  |

|               | •                                                                                                                       |                                                                                                                                                                   |                  |                  |                   |                 |                  |  |  |  |  |  |

|               | 0001 <b>= CPU</b>                                                                                                       | Interrupt Priorit                                                                                                                                                 | ty Level is 1    |                  |                   |                 |                  |  |  |  |  |  |

|               | 0000 <b>= CPU</b>                                                                                                       | Interrupt Priori                                                                                                                                                  | ty Level is 0    |                  |                   |                 |                  |  |  |  |  |  |

| bit 7         | Unimplemen                                                                                                              | ted: Read as '                                                                                                                                                    | 0'               |                  |                   |                 |                  |  |  |  |  |  |

| bit 6-0       | VECNUM<6:0                                                                                                              | 0>: Vector Nun                                                                                                                                                    | nber of Pendin   | g Interrupt bits | i                 |                 |                  |  |  |  |  |  |

|               | 0111111 <b>= In</b>                                                                                                     | terrupt vector                                                                                                                                                    | pending is Nur   | mber 135         |                   |                 |                  |  |  |  |  |  |

|               | •                                                                                                                       |                                                                                                                                                                   |                  |                  |                   |                 |                  |  |  |  |  |  |

|               | •                                                                                                                       |                                                                                                                                                                   |                  |                  |                   |                 |                  |  |  |  |  |  |

|               |                                                                                                                         | terrupt vector                                                                                                                                                    |                  |                  |                   |                 |                  |  |  |  |  |  |

|               | 0000000 = In                                                                                                            |                                                                                                                                                                   |                  |                  |                   |                 |                  |  |  |  |  |  |

#### REGISTER 8-35: INTTREG: INTERRUPT CONTROL AND STATUS REGISTER

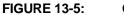

## 13.3 Output Compare Mode

Output Compare mode compares the Timer register value with the value of one or two Compare registers, depending on its mode of operation. The Output Compare x module on compare match events has the ability to generate a single output transition or a train of output

pulses. Like most PIC<sup>®</sup> MCU peripherals, the Output Compare x module can also generate interrupts on a compare match event.

Table 13-3 shows the various modes available in Output Compare modes.

| TABLE 13-3: | OUTPUT COMPARE/PWM MODES |

|-------------|--------------------------|

|-------------|--------------------------|

| MOD<3:0><br>(CCPxCON1L<3:0>) | T32<br>(CCPxCON1L<5>) | Operating Mode                         |                  |  |  |

|------------------------------|-----------------------|----------------------------------------|------------------|--|--|

| 0001                         | 0                     | Output High on Compare (16-bit)        |                  |  |  |

| 0001                         | 1                     | Output High on Compare (32-bit)        |                  |  |  |

| 0010                         | 0                     | Output Low on Compare (16-bit)         | Single Edge Mede |  |  |

| 0010                         | 1                     | Output Low on Compare (32-bit)         | Single Edge Mode |  |  |

| 0011                         | 0                     | Output Toggle on Compare (16-bit)      |                  |  |  |

| 0011                         | 1                     | Output Toggle on Compare (32-bit)      |                  |  |  |

| 0100                         | 0                     | Dual Edge Compare (16-bit)             | Dual Edge Mode   |  |  |

| 0101                         | 0                     | Dual Edge Compare (16-bit buffered)    | PWM Mode         |  |  |

| 0110                         | 0                     | Center-Aligned Pulse (16-bit buffered) | Center PWM       |  |  |

| 0111                         | 0                     | Variable Frequency Pulse (16-bit)      |                  |  |  |

| 0111                         | 1                     | Variable Frequency Pulse (32-bit)      |                  |  |  |

#### OUTPUT COMPARE x BLOCK DIAGRAM

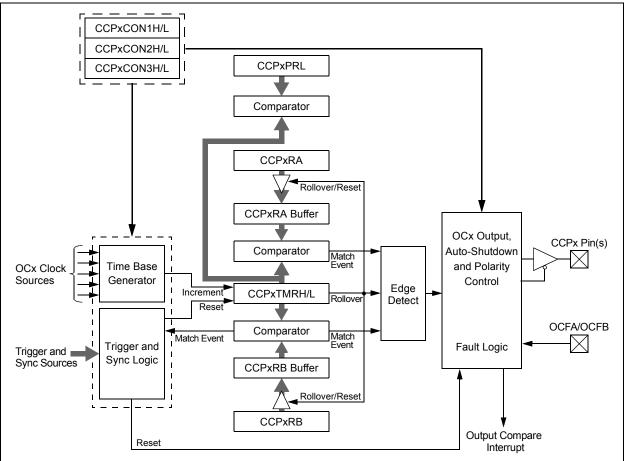

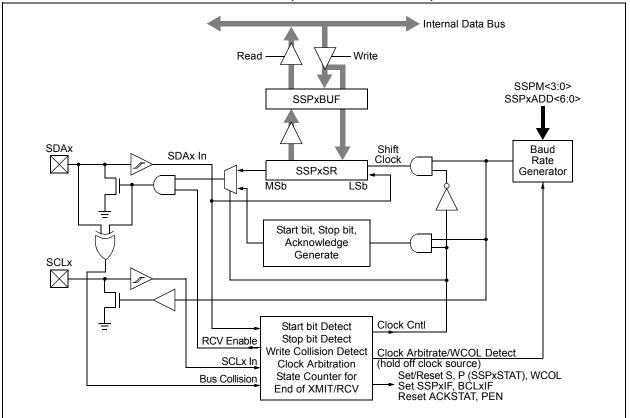

# FIGURE 14-4: MSSPx BLOCK DIAGRAM (I<sup>2</sup>C<sup>™</sup> MASTER MODE)

| U-0        | U-0                                                                                                                                                                                 | U-0                                                                                                                                                             | U-0              | U-0              | U-0              | U-0                | U-0      |  |  |  |  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|------------------|--------------------|----------|--|--|--|--|

| _          | _                                                                                                                                                                                   |                                                                                                                                                                 | _                | _                | —                | _                  |          |  |  |  |  |

| bit 15     |                                                                                                                                                                                     |                                                                                                                                                                 |                  |                  |                  |                    | bit      |  |  |  |  |

|            |                                                                                                                                                                                     |                                                                                                                                                                 |                  |                  |                  |                    |          |  |  |  |  |

| R/W-0      |                                                                                                                                                                                     | R-0                                                                                                                                                             | R-0              | R-0              | R-0              | R-0                | R-0      |  |  |  |  |

| SMP        | CKE                                                                                                                                                                                 | D/A                                                                                                                                                             | P <sup>(1)</sup> | S <sup>(1)</sup> | R/W              | UA                 | BF       |  |  |  |  |

| bit 7      |                                                                                                                                                                                     |                                                                                                                                                                 |                  |                  |                  |                    | bit      |  |  |  |  |

| Legend:    |                                                                                                                                                                                     |                                                                                                                                                                 |                  |                  |                  |                    |          |  |  |  |  |

| R = Read   | able bit                                                                                                                                                                            | W = Writable                                                                                                                                                    | bit              | U = Unimpler     | nented bit, read | d as '0'           |          |  |  |  |  |

| -n = Value | e at POR                                                                                                                                                                            | '1' = Bit is set '0' = Bit is cleared                                                                                                                           |                  |                  | ared             | x = Bit is unknown |          |  |  |  |  |