Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

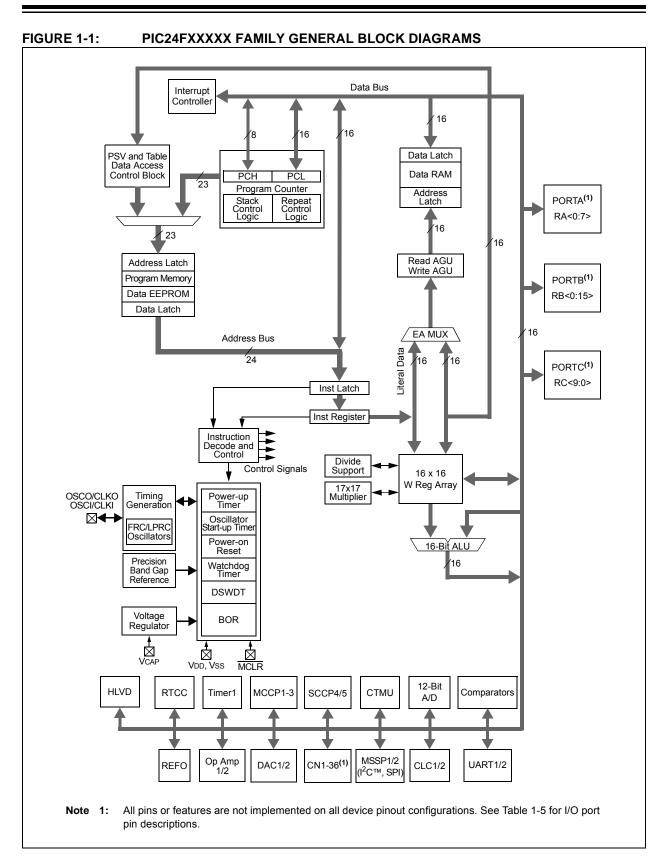

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                     |

| Number of I/O              | 23                                                                             |

| Program Memory Size        | 8KB (2.75K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | 512 x 8                                                                        |

| RAM Size                   | 2K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5V                                                                        |

| Data Converters            | A/D 19x10b/12b; D/A 2x8b                                                       |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 28-QFN (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fv08km202t-i-ml |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 7.1 Clock Source Selection at Reset

If clock switching is enabled, the system clock source at device Reset is chosen, as shown in Table 7-2. If clock switching is disabled, the system clock source is always selected according to the Oscillator Configuration bits. For more information, see **Section 9.0** "Oscillator Configuration".

# TABLE 7-2:OSCILLATOR SELECTION vs.TYPE OF RESET (CLOCK<br/>SWITCHING ENABLED)

| Reset Type | Clock Source Determinant      |

|------------|-------------------------------|

| POR        | FNOSC<2:0> Configuration bits |

| BOR        | (FOSCSEL<2:0>)                |

| MCLR       | COSC<2:0> Control bits        |

| WDTO       | (OSCCON<14:12>)               |

| SWR        |                               |

### 7.2 Device Reset Times

The Reset times for various types of device Reset are summarized in Table 7-3. Note that the system Reset signal, SYSRST, is released after the POR and PWRT delay times expire.

The time at which the device actually begins to execute code will also depend on the system oscillator delays, which include the Oscillator Start-up Timer (OST) and the PLL lock time. The OST and PLL lock times occur in parallel with the applicable SYSRST delay times.

The FSCM delay determines the time at which the FSCM begins to monitor the system clock source after the SYSRST signal is released.

| Reset Type         | Clock Source | SYSRST Delay | System Clock<br>Delay | Notes      |

|--------------------|--------------|--------------|-----------------------|------------|

| POR <sup>(6)</sup> | EC           | TPOR + TPWRT |                       | 1, 2       |

|                    | FRC, FRCDIV  | TPOR + TPWRT | TFRC                  | 1, 2, 3    |

|                    | LPRC         | TPOR + TPWRT | TLPRC                 | 1, 2, 3    |

|                    | ECPLL        | TPOR + TPWRT | Тьоск                 | 1, 2, 4    |

|                    | FRCPLL       | TPOR + TPWRT | TFRC + TLOCK          | 1, 2, 3, 4 |

|                    | XT, HS, SOSC | TPOR+ TPWRT  | Tost                  | 1, 2, 5    |

|                    | XTPLL, HSPLL | TPOR + TPWRT | TOST + TLOCK          | 1, 2, 4, 5 |

| BOR                | EC           | TPWRT        | —                     | 2          |

|                    | FRC, FRCDIV  | TPWRT        | TFRC                  | 2, 3       |

|                    | LPRC         | TPWRT        | TLPRC                 | 2, 3       |

|                    | ECPLL        | TPWRT        | Тьоск                 | 2, 4       |

|                    | FRCPLL       | TPWRT        | TFRC + TLOCK          | 2, 3, 4    |

|                    | XT, HS, SOSC | TPWRT        | Тоѕт                  | 2, 5       |

|                    | XTPLL, HSPLL | TPWRT        | TFRC + TLOCK          | 2, 3, 4    |

| All Others         | Any Clock    | _            | _                     | None       |

### TABLE 7-3: RESET DELAY TIMES FOR VARIOUS DEVICE RESETS

Note 1: TPOR = Power-on Reset delay.

- 2: TPWRT = 64 ms nominal if the Power-up Timer is enabled; otherwise, it is zero.

- **3:** TFRC and TLPRC = RC Oscillator start-up times.

- **4:** TLOCK = PLL Lock time.

- **5:** TOST = Oscillator Start-up Timer (OST). A 10-bit counter waits 1024 oscillator periods before releasing the oscillator clock to the system.

- 6: If Two-Speed Start-up is enabled, regardless of the Primary Oscillator selected, the device starts with FRC, and in such cases, FRC start-up time is valid.

Note: For detailed operating frequency and timing specifications, see Section 27.0 "Electrical Characteristics".

**IFS1: INTERRUPT FLAG STATUS REGISTER 1**

**REGISTER 8-6:**

| R/W-0, HS     | R/W-0, HS       | R/W-0, HS                       | R/W-0, HS       | R/W-0, HS         | U-0              | U-0             | U-0       |

|---------------|-----------------|---------------------------------|-----------------|-------------------|------------------|-----------------|-----------|

| U2TXIF        | U2RXIF          | INT2IF                          | CCT4IF          | CCT3IF            |                  | —               | —         |

| bit 15        |                 |                                 |                 |                   |                  |                 | bit 8     |

|               |                 |                                 |                 |                   |                  |                 |           |

| U-0           | R/W-0, HS       | U-0                             | R/W-0, HS       | R/W-0, HS         | R/W-0, HS        | R/W-0, HS       | R/W-0, HS |

| —             | CCP5IF          | —                               | INT1IF          | CNIF              | CMIF             | BCL1IF          | SSP1IF    |

| bit 7         |                 |                                 |                 |                   |                  |                 | bit 0     |

|               |                 |                                 |                 |                   |                  |                 |           |

| Legend:       |                 |                                 | re Settable bit |                   |                  |                 |           |

| R = Readable  |                 | W = Writable                    |                 | -                 | nented bit, read | d as '0'        |           |

| -n = Value at | POR             | '1' = Bit is set                |                 | '0' = Bit is clea | ared             | x = Bit is unkr | nown      |

|               |                 |                                 |                 |                   |                  |                 |           |

| bit 15        |                 | T2 Transmitter                  |                 | Status bit        |                  |                 |           |

|               |                 | equest has oc<br>equest has no  |                 |                   |                  |                 |           |

| bit 14        | -               | RT2 Receiver Ir                 |                 | atus hit          |                  |                 |           |

|               |                 | request has oc                  |                 |                   |                  |                 |           |

|               |                 | equest has not                  |                 |                   |                  |                 |           |

| bit 13        | INT2IF: Exter   | nal Interrupt 2                 | Flag Status bit |                   |                  |                 |           |

|               |                 | equest has oc                   |                 |                   |                  |                 |           |

|               | •               | equest has not                  |                 |                   |                  |                 |           |

| bit 12        |                 | -                               |                 | pt Flag Status b  | bit              |                 |           |

|               | •               | equest has oc                   |                 |                   |                  |                 |           |

| bit 11        | -               | equest has not                  |                 | nt Elan Statua k  | -:+              |                 |           |

|               | -               | request has oc                  |                 | pt Flag Status b  | JIL              |                 |           |

|               |                 | request has not                 |                 |                   |                  |                 |           |

| bit 10-7      | -               | ted: Read as '                  |                 |                   |                  |                 |           |

| bit 6         | CCP5IF: Cap     | ture/Compare                    | 5 Event Interru | pt Flag Status I  | bit              |                 |           |

|               | 1 = Interrupt r | equest has oc                   | curred          |                   |                  |                 |           |

|               | 0 = Interrupt r | equest has no                   | occurred        |                   |                  |                 |           |

| bit 5         | •               | ted: Read as '                  |                 |                   |                  |                 |           |

| bit 4         |                 | nal Interrupt 1                 | •               |                   |                  |                 |           |

|               |                 | equest has oc<br>equest has no  |                 |                   |                  |                 |           |

| bit 3         |                 | •                               |                 | lag Status bit    |                  |                 |           |

| DIUS          | -               | hange Notifica<br>equest has oc | -               | lay Status bit    |                  |                 |           |

|               | •               | request has not                 |                 |                   |                  |                 |           |

| bit 2         | CMIF: Compa     | arator Interrupt                | Flag Status Bit | t                 |                  |                 |           |

|               | -               | equest has oc                   | -               |                   |                  |                 |           |

|               | -               | equest has no                   |                 |                   |                  |                 |           |

| bit 1         |                 |                                 |                 | upt Flag Status   | bit              |                 |           |

|               |                 | equest has oc                   |                 |                   |                  |                 |           |

| <b>L</b> H 0  | -               | equest has not                  |                 |                   |                  |                 |           |

| bit 0         |                 | SP1 SPI/I <sup>2</sup> C Ev     | •               | lag Status bit    |                  |                 |           |

|               |                 | equest has oc<br>equest has no  |                 |                   |                  |                 |           |

|               | 5 monupti       |                                 |                 |                   |                  |                 |           |

### REGISTER 8-27: IPC10: INTERRUPT PRIORITY CONTROL REGISTER 10

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   |     | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

|        |     |     |     |     |     |     |       |

| U-0   | R/W-1   | R/W-0   | R/W-0   | U-0 | U-0 | U-0 | U-0   |

|-------|---------|---------|---------|-----|-----|-----|-------|

| —     | CCT5IP2 | CCT5IP1 | CCT5IP0 |     | _   | —   | —     |

| bit 7 |         |         |         |     |     |     | bit 0 |

| Legend:    |                            |                                 |                              |                    |  |  |  |  |

|------------|----------------------------|---------------------------------|------------------------------|--------------------|--|--|--|--|

| R = Reada  | ble bit                    | W = Writable bit                | U = Unimplemented bit        | , read as '0'      |  |  |  |  |

| -n = Value | at POR                     | '1' = Bit is set                | '0' = Bit is cleared         | x = Bit is unknown |  |  |  |  |

|            |                            |                                 |                              |                    |  |  |  |  |

| bit 15-7   | Unimplemented: Read as '0' |                                 |                              |                    |  |  |  |  |

| bit 6-4    | CCT5IP<                    | 2:0>: Capture/Compare 5 Ti      | imer Interrupt Priority bits |                    |  |  |  |  |

|            | 111 = Inte                 | errupt is Priority 7 (highest p | riority interrupt)           |                    |  |  |  |  |

|            | •                          |                                 |                              |                    |  |  |  |  |

|            | •                          |                                 |                              |                    |  |  |  |  |

|            | •                          |                                 |                              |                    |  |  |  |  |

|            | 001 = Inte                 | errupt is Priority 1            |                              |                    |  |  |  |  |

- 000 = Interrupt source is disabled

- bit 3-0 Unimplemented: Read as '0'

### 9.4 Clock Switching Operation

With few limitations, applications are free to switch between any of the four clock sources (POSC, SOSC, FRC and LPRC) under software control and at any time. To limit the possible side effects that could result from this flexibility, PIC24F devices have a safeguard lock built into the switching process.

Note: The Primary Oscillator mode has three different submodes (XT, HS and EC), which are determined by the POSCMDx Configuration bits. While an application can switch to and from Primary Oscillator mode in software, it cannot switch between the different primary submodes without reprogramming the device.

### 9.4.1 ENABLING CLOCK SWITCHING

To enable clock switching, the FCKSM1 Configuration bit in the FOSC Configuration register must be programmed to '0'. (Refer to **Section 25.0** "**Special Features**" for further details.) If the FCKSM1 Configuration bit is unprogrammed ('1'), the clock switching function and FSCM function are disabled; this is the default setting.

The NOSCx control bits (OSCCON<10:8>) do not control the clock selection when clock switching is disabled. However, the COSCx bits (OSCCON<14:12>) will reflect the clock source selected by the FNOSCx Configuration bits.

The OSWEN control bit (OSCCON<0>) has no effect when clock switching is disabled; it is held at '0' at all times.

#### 9.4.2 OSCILLATOR SWITCHING SEQUENCE

At a minimum, performing a clock switch requires this basic sequence:

- 1. If desired, read the COSCx bits (OSCCON<14:12>) to determine the current oscillator source.

- 2. Perform the unlock sequence to allow a write to the OSCCON register high byte.

- 3. Write the appropriate value to the NOSCx bits (OSCCON<10:8>) for the new oscillator source.

- 4. Perform the unlock sequence to allow a write to the OSCCON register low byte.

- 5. Set the OSWEN bit to initiate the oscillator switch.

Once the basic sequence is completed, the system clock hardware responds automatically, as follows:

- 1. The clock switching hardware compares the COSCx bits with the new value of the NOSCx bits. If they are the same, then the clock switch is a redundant operation. In this case, the OSWEN bit is cleared automatically and the clock switch is aborted.

- If a valid clock switch has been initiated, the LOCK (OSCCON<5>) and CF (OSCCON<3>) bits are cleared.

- The new oscillator is turned on by the hardware if it is not currently running. If a crystal oscillator must be turned on, the hardware will wait until the OST expires. If the new source is using the PLL, then the hardware waits until a PLL lock is detected (LOCK = 1).

- 4. The hardware waits for 10 clock cycles from the new clock source and then performs the clock switch.

- 5. The hardware clears the OSWEN bit to indicate a successful clock transition. In addition, the NOSCx bits value is transferred to the COSCx bits.

- The old clock source is turned off at this time, with the exception of LPRC (if WDT, FSCM or RTCC with LPRC as a clock source is enabled) or SOSC (if SOSCEN remains enabled).

Note 1: The processor will continue to execute code throughout the clock switching sequence. Timing-sensitive code should not be executed during this time.

2: Direct clock switches between any Primary Oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transitional clock source between the two PLL modes.

NOTES:

### 10.2.2 IDLE MODE

Idle mode includes these features:

- · The CPU will stop executing instructions.

- · The WDT is automatically cleared.

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 10.6 "Selective Peripheral Module Control").

- If the WDT or FSCM is enabled, the LPRC will also remain active.

The device will wake from Idle mode on any of these events:

- · Any interrupt that is individually enabled

- Any device Reset

- A WDT time-out

On wake-up from Idle, the clock is reapplied to the CPU and instruction execution begins immediately, starting with the instruction following the PWRSAV instruction or the first instruction in the ISR.

#### 10.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction will be held off until entry into Sleep or Idle mode has completed. The device will then wake-up from Sleep or Idle mode.

#### 10.2.3.1 Power-on Resets (PORs)

VDD voltage is monitored to produce PORs. When a true POR occurs, the entire device is reset.

### 10.3 Ultra Low-Power Wake-up

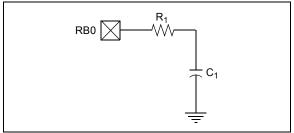

The Ultra Low-Power Wake-up (ULPWU) on pin, RB0, allows a slow falling voltage to generate an interrupt without excess current consumption.

To use this feature:

- 1. Charge the capacitor on RB0 by configuring the RB0 pin to an output and setting it to '1'.

- 2. Stop charging the capacitor by configuring RB0 as an input.

- 3. Discharge the capacitor by setting the ULPEN and ULPSINK bits in the ULPWCON register.

- 4. Configure Sleep mode.

- 5. Enter Sleep mode.

When the voltage on RB0 drops below VIL, the device wakes up and executes the next instruction.

This feature provides a low-power technique for periodically waking up the device from Sleep mode.

The time-out is dependent on the discharge time of the RC circuit on RB0.

When the ULPWU module wakes the device from Sleep mode, the ULPWUIF bit (IFS5<0>) is set. Software can check this bit upon wake-up to determine the wake-up source.

See Example 10-2 for initializing the ULPWU module.

### EXAMPLE 10-2: ULTRA LOW-POWER WAKE-UP INITIALIZATION

```

//*********

// 1. Charge the capacitor on RBO

TRISBbits.TRISB0 = 0;

LATBbits.LATB0 = 1;

for(i = 0; i < 10000; i++) Nop();</pre>

//2. Stop Charging the capacitor

on RBO

11

//*******************************

TRISBbits.TRISB0 = 1;

//3. Enable ULPWU Interrupt

IFS5bits.ULPWUIF = 0;

IEC5bits.ULPWUIE = 1;

IPC21bits.ULPWUIP = 0x7;

//*********************************

//4. Enable the Ultra Low Power

11

Wakeup module and allow

11

capacitor discharge

ULPWCONbits.ULPEN = 1;

ULPWCONbit.ULPSINK = 1;

//5. Enter Sleep Mode

11

Sleep();

//for sleep, execution will

//resume here

```

A series resistor, between RB0 and the external capacitor provides overcurrent protection for the AN2/ULPWU/RB0 pin and enables software calibration of the time-out (see Figure 10-1).

#### FIGURE 10-1: SERIES RESISTOR

A timer can be used to measure the charge time and discharge time of the capacitor. The charge time can then be adjusted to provide the desired delay in Sleep. This technique compensates for the affects of temperature, voltage and component accuracy. The peripheral can also be configured as a simple, programmable Low-Voltage Detect (LVD) or temperature sensor.

| R/W-0         | U-0                                                              | R/W-0                                  | r-0            | R/W-0                                | R/W-0                  | R/W-0                  | R/W-0                  |

|---------------|------------------------------------------------------------------|----------------------------------------|----------------|--------------------------------------|------------------------|------------------------|------------------------|

| CCPON         |                                                                  | CCPSIDL                                | r              | TMRSYNC                              | CLKSEL2 <sup>(1)</sup> | CLKSEL1 <sup>(1)</sup> | CLKSEL0 <sup>(1)</sup> |

| bit 15        |                                                                  |                                        |                |                                      | •                      | •                      | bit 8                  |

|               |                                                                  |                                        |                |                                      |                        |                        |                        |

| R/W-0         | R/W-0                                                            | R/W-0                                  | R/W-0          | R/W-0                                | R/W-0                  | R/W-0                  | R/W-0                  |

| TMRPS1        | TMRPS0                                                           | T32                                    | CCSEL          | MOD3                                 | MOD2                   | MOD1                   | MOD0                   |

| bit 7         |                                                                  |                                        |                |                                      |                        |                        | bit (                  |

|               |                                                                  |                                        |                |                                      |                        |                        |                        |

| Legend:       |                                                                  | r = Reserved I                         |                |                                      |                        |                        |                        |

| R = Readable  |                                                                  | W = Writable I                         | oit            |                                      | nented bit, read       |                        |                        |

| -n = Value at | POR                                                              | '1' = Bit is set                       |                | '0' = Bit is clea                    | ared                   | x = Bit is unkn        | own                    |

| bit 15        | CCPON: CCF                                                       | x Module Enat                          | ole bit        |                                      |                        |                        |                        |

|               | 1 = Module is<br>0 = Module is                                   |                                        | an operating r | node specified b                     | by the MOD<3:          | 0> control bits        |                        |

| bit 14        | Unimplemen                                                       | ted: Read as 'd                        | )'             |                                      |                        |                        |                        |

| bit 13        | CCPSIDL: CO                                                      | CPx Stop in Idle                       | Mode Bit       |                                      |                        |                        |                        |

|               |                                                                  | ues module op<br>s module opera        |                | device enters lo<br>ode              | lle mode               |                        |                        |

| bit 12        | Reserved: Ma                                                     | -                                      |                |                                      |                        |                        |                        |

| bit 11        | TMRSYNC: T                                                       | ime Base Cloc                          | k Synchroniza  | ation bit                            |                        |                        |                        |

|               | (CLKSEL<br>0 = Synchron                                          | <b>&lt;2:0&gt;</b> ≠ 000)              |                | k is selected and<br>lock is selecte | -                      |                        | -                      |

| bit 10-8      |                                                                  | >: CCPx Time                           | Base Clock S   | elect bits <sup>(1)</sup>            |                        |                        |                        |

|               | 110 = Externa<br>101 = CLC1<br>100 = Reserv<br>011 = LPRC (      | 31 kHz source<br>dary Oscillator<br>ed | t              |                                      |                        |                        |                        |

| bit 7-6       | TMRPS<1:0>                                                       | : Time Base Pr                         | escale Select  | t bits                               |                        |                        |                        |

|               | 11 = 1:64 Pre<br>10 = 1:16 Pre<br>01 = 1:4 Pres<br>00 = 1:1 Pres | scaler<br>caler                        |                |                                      |                        |                        |                        |

| bit 5         | T32: 32-Bit Ti                                                   | me Base Selec                          | t bit          |                                      |                        |                        |                        |

|               |                                                                  |                                        |                | e edge output co<br>e edge output co |                        |                        |                        |

| bit 4         |                                                                  | ure/Compare N                          |                |                                      |                        |                        |                        |

|               | 1 = Input Cap                                                    | -                                      |                |                                      |                        |                        |                        |

### REGISTER 13-1: CCPxCON1L: CCPx CONTROL 1 LOW REGISTERS

| U-0           | U-0                        | U-0                               | U-0              | U-0                | U-0            | U-0             | U-0              |

|---------------|----------------------------|-----------------------------------|------------------|--------------------|----------------|-----------------|------------------|

|               | —                          | —                                 |                  | —                  |                | _               |                  |

| bit 15        |                            |                                   |                  |                    |                |                 | bit 8            |

|               |                            |                                   |                  |                    |                |                 |                  |

| R/W-0         | R/W-0                      | R-0                               | R-0              | R-0                | R-0            | R-0             | R-0              |

| SMP           | CKE <sup>(1)</sup>         | D/Ā                               | Р                | S                  | R/W            | UA              | BF               |

| bit 7         |                            |                                   |                  |                    |                |                 | bit (            |

| Legend:       |                            |                                   |                  |                    |                |                 |                  |

| R = Readable  | e bit                      | W = Writable I                    | oit              | U = Unimplem       | ented bit. rea | d as '0'        |                  |

| -n = Value at |                            | '1' = Bit is set                  |                  | '0' = Bit is clea  |                | x = Bit is unkr | nown             |

|               |                            |                                   |                  |                    |                |                 |                  |

| bit 15-8      | Unimplemen                 | ted: Read as '0                   | )'               |                    |                |                 |                  |

| bit 7         | SMP: Sample                | e bit                             |                  |                    |                |                 |                  |

|               | SPI Master m               |                                   |                  |                    |                |                 |                  |

|               |                            | is sampled at                     |                  |                    |                |                 |                  |

|               | •                          | •                                 | the middle of o  | data output time   |                |                 |                  |

|               | SMP must be                | de:<br>cleared when \$            | SPI is used in   | Slave mode         |                |                 |                  |

| bit 6         |                            | ck Select bit <sup>(1)</sup>      |                  |                    |                |                 |                  |

|               | 1 = Transmit o             | occurs on trans                   | ition from acti  | ve to Idle clock s | state          |                 |                  |

|               | 0 = Transmit               | occurs on trans                   | ition from Idle  | to active clock s  | state          |                 |                  |

| bit 5         | D/A: Data/Ad               |                                   |                  |                    |                |                 |                  |

|               | Used in I <sup>2</sup> C™  | mode only.                        |                  |                    |                |                 |                  |

| bit 4         | P: Stop bit                |                                   |                  |                    |                |                 |                  |

|               |                            | node only. This                   | bit is cleared v | when the MSSP:     | x module is di | sabled; SSPEN   | l bit is cleared |

| bit 3         | S: Start bit               |                                   |                  |                    |                |                 |                  |

|               | Used in I <sup>2</sup> C m | •                                 |                  |                    |                |                 |                  |

| bit 2         |                            | rite Information                  | bit              |                    |                |                 |                  |

|               | Used in I <sup>2</sup> C m |                                   |                  |                    |                |                 |                  |

| bit 1         | UA: Update A               |                                   |                  |                    |                |                 |                  |

|               | Used in I <sup>2</sup> C m | ,                                 |                  |                    |                |                 |                  |

| bit 0         | BF: Buffer Fu              |                                   |                  |                    |                |                 |                  |

|               |                            | s complete, SS<br>s not complete, |                  | emntv              |                |                 |                  |

|               |                            | -                                 |                  |                    |                |                 |                  |

|               | plarity of clock s         | tata ia aat by th                 |                  | DUCONIA (A)        |                |                 |                  |

### REGISTER 14-1: SSPxSTAT: MSSPx STATUS REGISTER (SPI MODE)

| U-0        | U-0                                 | U-0                                 | U-0              | U-0                              | U-0              | U-0               | U-0      |

|------------|-------------------------------------|-------------------------------------|------------------|----------------------------------|------------------|-------------------|----------|

| _          | _                                   |                                     | _                | _                                | —                | _                 |          |

| bit 15     | ·                                   |                                     | ·                |                                  |                  |                   | bit      |

|            |                                     |                                     |                  |                                  |                  |                   |          |

| R/W-0      |                                     | R-0                                 | R-0              | R-0                              | R-0              | R-0               | R-0      |

| SMP        | CKE                                 | D/A                                 | P <sup>(1)</sup> | S <sup>(1)</sup>                 | R/W              | UA                | BF       |

| bit 7      |                                     |                                     |                  |                                  |                  |                   | bit      |

| Legend:    |                                     |                                     |                  |                                  |                  |                   |          |

| R = Read   | able bit                            | W = Writable                        | bit              | U = Unimpler                     | nented bit, read | d as '0'          |          |

| -n = Value | at POR                              | '1' = Bit is se                     | t                | '0' = Bit is cle                 | ared             | x = Bit is unkn   | iown     |

|            |                                     |                                     |                  |                                  |                  |                   |          |

| bit 15-8   | Unimplemen                          | ted: Read as                        | 0'               |                                  |                  |                   |          |

| bit 7      | SMP: Slew R                         | ate Control bit                     |                  |                                  |                  |                   |          |

|            | In Master or S                      |                                     |                  |                                  |                  |                   |          |

|            |                                     |                                     |                  | ard Speed mode                   |                  | I 1 MHz)          |          |

| bit 6      | CKE: SMBus                          |                                     |                  |                                  | (0 KHZ)          |                   |          |

| DIL O      | In Master or S                      |                                     |                  |                                  |                  |                   |          |

|            |                                     | SMBus-specific                      | c inputs         |                                  |                  |                   |          |

|            | 0 = Disables                        | SMBus-specifi                       | c inputs         |                                  |                  |                   |          |

| bit 5      | D/A: Data/Ad                        | ldress bit                          |                  |                                  |                  |                   |          |

|            | <u>In Master mo</u><br>Reserved.    | <u>de:</u>                          |                  |                                  |                  |                   |          |

|            | In Slave mod                        |                                     | (                |                                  |                  |                   |          |

|            |                                     |                                     |                  | transmitted wa<br>transmitted wa |                  |                   |          |

| bit 4      | P: Stop bit <sup>(1)</sup>          |                                     |                  |                                  | 5 4441055        |                   |          |

| bit 4      |                                     | that a Stop bit                     | has been dete    | ected last                       |                  |                   |          |

|            |                                     | vas not detecte                     |                  |                                  |                  |                   |          |

| bit 3      | S: Start bit <sup>(1)</sup>         |                                     |                  |                                  |                  |                   |          |

|            |                                     | that a Start bit<br>vas not detecte |                  | ected last                       |                  |                   |          |

| bit 2      | R/W: Read/W                         | Vrite Informatio                    | n bit            |                                  |                  |                   |          |

|            | In Slave mod                        | <u>e:</u> (2)                       |                  |                                  |                  |                   |          |

|            | 1 = Read                            |                                     |                  |                                  |                  |                   |          |

|            | 0 = Write<br>In Master mo           | do.(3)                              |                  |                                  |                  |                   |          |

|            |                                     | is in progress                      |                  |                                  |                  |                   |          |

|            |                                     | is not in progre                    | ess              |                                  |                  |                   |          |

| bit 1      | UA: Update /                        | Address bit (10                     | -Bit Slave mod   | le only)                         |                  |                   |          |

|            |                                     | that the user r<br>does not need    |                  | e the address ir                 | the SSPxADE      | ) register        |          |

| Note 1:    | This bit is cleared                 | d on Reset and                      | when SSPEN       | is cleared.                      |                  |                   |          |

| 2:         | This bit holds the address match to |                                     |                  |                                  | ss match. This   | bit is only valid | from the |

| 3:         | ORing this bit wit                  | h SEN, RSEN,                        | PEN. RCEN        | or ACKEN will in                 | ndicate if the M | SSPx is in Activ  | ve mode  |

### REGISTER 14-2: SSPxSTAT: MSSPx STATUS REGISTER (I<sup>2</sup>C<sup>™</sup> MODE)

### REGISTER 15-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

- bit 3 BRGH: High Baud Rate Enable bit

- 1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)

0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode)

- bit 2-1 **PDSEL<1:0>:** Parity and Data Selection bits

- 11 = 9-bit data, no parity

- 10 = 8-bit data, odd parity

- 01 = 8-bit data, even parity

- 00 = 8-bit data, no parity

- bit 0 STSEL: Stop Bit Selection bit

- 1 = Two Stop bits

- 0 = One Stop bit

- Note 1: This feature is is only available for the 16x BRG mode (BRGH = 0).

- 2: The bit availability depends on the pin availability.

### REGISTER 15-2: UxSTA: UARTx STATUS AND CONTROL REGISTER

| R/W-0    | R/W-0  | R/W-0    | U-0 | R/W-0, HC | R/W-0 | R-0, HSC | R-1, HSC |

|----------|--------|----------|-----|-----------|-------|----------|----------|

| UTXISEL1 | UTXINV | UTXISEL0 | —   | UTXBRK    | UTXEN | UTXBF    | TRMT     |

| bit 15   |        |          |     |           |       |          | bit 8    |

| R/W-0    | R/W-0    | R/W-0 | R-1, HSC | R-0, HSC | R-0, HSC | R/C-0, HS | R-0, HSC |

|----------|----------|-------|----------|----------|----------|-----------|----------|

| URXISEL1 | URXISEL0 | ADDEN | RIDLE    | PERR     | FERR     | OERR      | URXDA    |

| bit 7    |          |       |          |          |          |           | bit 0    |

| Legend:                    | HC = Hardware Clearable bit |                             |                    |

|----------------------------|-----------------------------|-----------------------------|--------------------|

| HS = Hardware Settable bit | C = Clearable bit           | HSC = Hardware Settable/Cle | earable bit        |

| R = Readable bit           | W = Writable bit            | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR          | '1' = Bit is set            | '0' = Bit is cleared        | x = Bit is unknown |

bit 15,13 UTXISEL<1:0>: UARTx Transmission Interrupt Mode Selection bits

- 11 = Reserved; do not use

- 10 = Interrupt when a character is transferred to the Transmit Shift Register (TSR) and as a result, the transmit buffer becomes empty

- 01 = Interrupt when the last character is shifted out of the Transmit Shift Register; all transmit operations are completed

- 00 = Interrupt when a character is transferred to the Transmit Shift Register (this implies there is at least one character open in the transmit buffer)

- bit 14 UTXINV: IrDA<sup>®</sup> Encoder Transmit Polarity Inversion bit

| bit 14  | UTXINV: IrDA <sup>®</sup> Encoder Transmit Polarity Inversion bit                                                                                                                                                                                                                                                                                                                                          |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <u>If IREN = 0:</u>                                                                                                                                                                                                                                                                                                                                                                                        |

|         | 1 = UxTX Idle '0'                                                                                                                                                                                                                                                                                                                                                                                          |

|         | 0 = UxTX Idle '1'                                                                                                                                                                                                                                                                                                                                                                                          |

|         | <u>If IREN = 1:</u>                                                                                                                                                                                                                                                                                                                                                                                        |

|         | 1 = UxTX Idle '1'                                                                                                                                                                                                                                                                                                                                                                                          |

|         | 0 = UxTX Idle '0'                                                                                                                                                                                                                                                                                                                                                                                          |

| bit 12  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                 |

| bit 11  | UTXBRK: UARTx Transmit Break bit                                                                                                                                                                                                                                                                                                                                                                           |

|         | <ul> <li>1 = Sends Sync Break on next transmission – Start bit, followed by twelve '0' bits, followed by Stop bit;<br/>cleared by hardware upon completion</li> </ul>                                                                                                                                                                                                                                      |

|         | 0 = Sync Break transmission is disabled or completed                                                                                                                                                                                                                                                                                                                                                       |

| bit 10  | UTXEN: UARTx Transmit Enable bit                                                                                                                                                                                                                                                                                                                                                                           |

|         | <ul> <li>1 = Transmit is enabled; UxTX pin is controlled by UARTx</li> <li>0 = Transmit is disabled; any pending transmission is aborted and the buffer is reset; UxTX pin is controlled by the PORT register</li> </ul>                                                                                                                                                                                   |

| bit 9   | UTXBF: UARTx Transmit Buffer Full Status bit (read-only)                                                                                                                                                                                                                                                                                                                                                   |

|         | 1 = Transmit buffer is full                                                                                                                                                                                                                                                                                                                                                                                |

|         | 0 = Transmit buffer is not full, at least one more character can be written                                                                                                                                                                                                                                                                                                                                |

| bit 8   | TRMT: Transmit Shift Register Empty bit (read-only)                                                                                                                                                                                                                                                                                                                                                        |

|         | <ul> <li>1 = Transmit Shift Register is empty and the transmit buffer is empty (the last transmission has<br/>completed)</li> </ul>                                                                                                                                                                                                                                                                        |

|         | 0 = Transmit Shift Register is not empty; a transmission is in progress or queued                                                                                                                                                                                                                                                                                                                          |

| bit 7-6 | URXISEL<1:0>: UARTx Receive Interrupt Mode Selection bits                                                                                                                                                                                                                                                                                                                                                  |

|         | <ul> <li>11 = Interrupt is set on an RSR transfer, making the receive buffer full (i.e., has 4 data characters)</li> <li>10 = Interrupt is set on an RSR transfer, making the receive buffer 3/4 full (i.e., has 3 data characters)</li> <li>0x = Interrupt is set when any character is received and transferred from the RSR to the receive buffer; receive buffer has one or more characters</li> </ul> |

|         |                                                                                                                                                                                                                                                                                                                                                                                                            |

### REGISTER 17-4: CLCxGLSL: CLCx GATE LOGIC INPUT SELECT LOW REGISTER (CONTINUED)

| bit 3 | G1D2T: Gate 1 Data Source 2 True Enable bit                                                                                                           |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = The Data Source 2 inverted signal is enabled for Gate 1</li> <li>0 = The Data Source 2 inverted signal is disabled for Gate 1</li> </ul> |

|       | -                                                                                                                                                     |

| bit 2 | G1D2N: Gate 1 Data Source 2 Negated Enable bit                                                                                                        |

|       | 1 = The Data Source 2 inverted signal is enabled for Gate 1                                                                                           |

|       | 0 = The Data Source 2 inverted signal is disabled for Gate 1                                                                                          |

| bit 1 | G1D1T: Gate 1 Data Source 1 True Enable bit                                                                                                           |

|       | 1 = The Data Source 1 inverted signal is enabled for Gate 1                                                                                           |

|       | 0 = The Data Source 1 inverted signal is disabled for Gate 1                                                                                          |

| bit 0 | G1D1N: Gate 1 Data Source 1 Negated Enable bit                                                                                                        |

|       | 1 = The Data Source 1 inverted signal is enabled for Gate 1                                                                                           |

|       | 0 = The Data Source 1 inverted signal is disabled for Gate 1                                                                                          |

### 24.0 CHARGE TIME MEASUREMENT UNIT (CTMU)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the Charge Time Measurement Unit, refer to the "PIC24F Family Reference Manual", "Charge Time Measurement Unit (CTMU) with Threshold Detect" (DS39743).

The Charge Time Measurement Unit (CTMU) is a flexible analog module that provides charge measurement, accurate differential time measurement between pulse sources and asynchronous pulse generation. Its key features include:

- Thirteen external edge input Trigger sources

- · Polarity control for each edge source

- · Control of edge sequence

- Control of response to edge levels or edge transitions

- · Time measurement resolution of one nanosecond

- Accurate current source suitable for capacitive measurement

Together with other on-chip analog modules, the CTMU can be used to precisely measure time, measure capacitance, measure relative changes in capacitance or generate output pulses that are independent of the system clock. The CTMU module is ideal for interfacing with capacitive-based touch sensors.

The CTMU is controlled through three registers: CTMUCON1, CTMUCON2 and CTMUICON. CTMUCON1 enables the module and controls the mode of operation of the CTMU, as well as controlling edge sequencing. CTMUCON2 controls edge source selection and edge source polarity selection. The CTMUICON register selects the current range of current source and trims the current.

### 24.1 Measuring Capacitance

The CTMU module measures capacitance by generating an output pulse, with a width equal to the time between edge events, on two separate input channels. The pulse edge events to both input channels can be selected from several internal peripheral modules (OC1, Timer1, any input capture or comparator module) and up to 13 external pins (CTED1 through CTED13). This pulse is used with the module's precision current source to calculate capacitance according to the relationship:

### EQUATION 24-1:

$$I = C \cdot \frac{dV}{dT}$$

For capacitance measurements, the A/D Converter samples an External Capacitor (CAPP) on one of its input channels after the CTMU output's pulse. A Precision Resistor (RPR) provides current source calibration on a second A/D channel. After the pulse ends, the converter determines the voltage on the capacitor. The actual calculation of capacitance is performed in software by the application.

Figure 24-1 illustrates the external connections used for capacitance measurements, and how the CTMU and A/D modules are related in this application. This example also shows the edge events coming from Timer1, but other configurations using external edge sources are possible. A detailed discussion on measuring capacitance and time with the CTMU module is provided in the "*PIC24F Family Reference Manual*".

### 25.4 Program Verification and Code Protection

For all devices in the PIC24FXXXXX family, code protection for the Boot Segment is controlled by the Configuration bit, BSS0, and the General Segment by the Configuration bit, GCP. These bits inhibit external reads and writes to the program memory space This has no direct effect in normal execution mode.

Write protection is controlled by bit, BWRP, for the Boot Segment and bit, GWRP, for the General Segment in the Configuration Word. When these bits are programmed to '0', internal write and erase operations to program memory are blocked.

### 25.5 In-Circuit Serial Programming

PIC24FXXXXX family microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock (PGECx) and data (PGEDx), and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

### 25.6 In-Circuit Debugger

When MPLAB<sup>®</sup> ICD 3, MPLAB REAL ICE<sup>™</sup> or PICkit<sup>™</sup> 3 is selected as a debugger, the in-circuit debugging functionality is enabled. This function allows simple debugging functions when used with MPLAB IDE. Debugging functionality is controlled through the PGECx and PGEDx pins.

To use the in-circuit debugger function of the device, the design must implement ICSP connections to MCLR, VDD, VSS, PGECx, PGEDx and the pin pair. In addition, when the feature is enabled, some of the resources are not available for general use. These resources include the first 80 bytes of data RAM and two I/O pins.

### 26.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

### 26.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

### 26.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

### 26.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

### 26.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

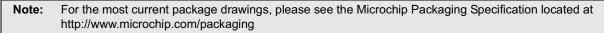

### 20-Lead Plastic Quad Flat, No Lead Package (ML) - 4x4 mm Body [QFN] With 0.40 mm Contact Length

| Units                      |    | MILLIMETERS |      |      |

|----------------------------|----|-------------|------|------|

| Dimension Limits           |    | MIN         | NOM  | MAX  |

| Contact Pitch              | E  | 0.50 BSC    |      |      |

| Optional Center Pad Width  | W2 |             |      | 2.50 |

| Optional Center Pad Length | T2 |             |      | 2.50 |

| Contact Pad Spacing        | C1 |             | 3.93 |      |

| Contact Pad Spacing        | C2 |             | 3.93 |      |

| Contact Pad Width          | X1 |             |      | 0.30 |

| Contact Pad Length         | Y1 |             |      | 0.73 |

| Distance Between Pads      | G  | 0.20        |      |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2126A

### **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| Product Group<br>Pin Count<br>Tape and Reel Fl |                                                                                                                                    | <ul> <li>Examples:</li> <li>a) PIC24FV16KM204-I/ML: Wide Voltage Range,<br/>General Purpose, 16-Kbyte Program Memory,<br/>44-Pin, Industrial Temp., QFN Package</li> <li>b) PIC24F08KM102-I/SS: Standard Voltage Range,<br/>General Purpose with Reduced Feature Set,<br/>8-Kbyte Program Memory, 28-Pin, Industrial<br/>Temp., SSOP Package</li> </ul> |

|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Architecture                                   | 24 = 16-bit modified Harvard without DSP                                                                                           |                                                                                                                                                                                                                                                                                                                                                         |

| Flash Memory Family                            | <ul><li>F = Standard voltage range Flash program memory</li><li>FV = Wide voltage range Flash program memory</li></ul>             |                                                                                                                                                                                                                                                                                                                                                         |

| Product Group                                  | KM2 = General Purpose PIC24F Lite Microcontroller<br>KM1 = General Purpose PIC24F Lite Microcontroller with<br>Reduced Feature Set |                                                                                                                                                                                                                                                                                                                                                         |

| Pin Count                                      | 01 = 20-pin<br>02 = 28-pin<br>04 = 44-pin                                                                                          |                                                                                                                                                                                                                                                                                                                                                         |

| Temperature Range                              | I = $-40^{\circ}$ C to $+85^{\circ}$ C (Industrial)<br>E = $-40^{\circ}$ C to $+125^{\circ}$ C (Extended)                          |                                                                                                                                                                                                                                                                                                                                                         |

| Package                                        | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                               |                                                                                                                                                                                                                                                                                                                                                         |

| Pattern                                        | Three-digit QTP, SQTP, Code or Special Requirements<br>(blank otherwise)<br>ES = Engineering Sample                                |                                                                                                                                                                                                                                                                                                                                                         |

### **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

**Chicago** Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 Australia - Sydney Tel: 61-2-9868-6733

Fax: 61-2-9868-6755

Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hangzhou** Tel: 86-571-2819-3187 Fax: 86-571-2819-3189

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

**India - New Delhi** Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Osaka** Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7828 Fax: 886-7-330-9305

**Taiwan - Taipei** Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820