#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                     |

| Number of I/O              | 23                                                                             |

| Program Memory Size        | 8KB (2.75K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | 512 x 8                                                                        |

| RAM Size                   | 2K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5V                                                                        |

| Data Converters            | A/D 19x10b/12b; D/A 2x8b                                                       |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                 |

| Supplier Device Package    | 28-SSOP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fv08km202t-i-ss |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Pin Diagrams (Continued)**

| 48-Pin UQFN <sup>(1)</sup>                                                                                                                                                                           |          | Pin Features                        |                                         |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------------------------------|-----------------------------------------|--|--|--|

|                                                                                                                                                                                                      |          | PIC24FXXKMX04                       | PIC24FVXXKMX04                          |  |  |  |

| RBS<br>VCDD<br>VCDD<br>VCDD<br>VCDD<br>RC3<br>RC3<br>RC3<br>RC3<br>RC3<br>RC3<br>RC3<br>RC3<br>RC3<br>RC3                                                                                            | 1        | AN21/SDA1/T1CK/U1RTS/U1BCLK/IC2/    | /CLC10/CTED4/CN21/RB9                   |  |  |  |

| $\overline{x} \overline{x} \overline{x} \overline{x} \overline{z} \overline{z} \overline{z} \overline{z} \overline{z} \overline{x} \overline{x} \overline{x} \overline{x} \overline{x} \overline{x}$ | 2        | U1RX/ /CN18/RC6                     |                                         |  |  |  |

| RB9 1 8 4 8 4 7 7 7 7 7 7 8 8 8 8 8 8 8 8 8 8                                                                                                                                                        | 3        | U1TX/ /CN17/RC7                     |                                         |  |  |  |

| RB9 1 36 RB4<br>RC6 2 35 RA8                                                                                                                                                                         |          | OC2/CN20/RC8                        |                                         |  |  |  |

| RC7 3 34 RA3<br>RC8 4 33 RA2                                                                                                                                                                         |          | IC4/OC2F/CTED7/CN19/RC9             |                                         |  |  |  |

| RC9 5 32 n/c                                                                                                                                                                                         | 6        | IC1/ / /CTED3/CN9/RA7               | 1                                       |  |  |  |

| RA7         6         PIC24FXXKMX04         31         Vss           RA6         7         PIC24FVXXKMX04         30         Vbb                                                                     |          | /OC1A/CTED1/INT2/CN8/RA6            | VDDCORE OF VCAP                         |  |  |  |

| n/c 8 29 RC2                                                                                                                                                                                         | 2 0      | n/c                                 | n/c                                     |  |  |  |

| RB10 9 28 RC <sup>2</sup><br>RB11 10 27 RC                                                                                                                                                           | <u> </u> | PGED2/SDI1/OC1C/CTED11/CN16/RB10    |                                         |  |  |  |

| RB12 11 26 RB3                                                                                                                                                                                       | 3 10     | PGEC2/SCK1/OC2A/CTED9/CN15/RB11     |                                         |  |  |  |

| RB13 12 25 RB2 25 RB2 25 RB2                                                                                                                                                                         | 2 11     | /AN12/HLVDIN/ /CTED2/<br>CN14/RB12  | /AN12/HLVDIN/ /CTED2/<br>INT2/CN14/RB12 |  |  |  |

|                                                                                                                                                                                                      | 12       | / /AN11/SDO1/OC1D/CTPLS             |                                         |  |  |  |

| RA10<br>RA11<br>RB14<br>RB14<br>Vss/AVsp<br>NCLR/RA5<br>N/C<br>R10<br>R10<br>R10<br>R10<br>R10<br>R10<br>R10<br>R10<br>R10<br>R10                                                                    | 13       | / /CN35/RA10                        |                                         |  |  |  |

| R R SSS/ANDI                                                                                                                                                                                         | 14       | / /CTED8/CN36/RA11                  |                                         |  |  |  |

| > >                                                                                                                                                                                                  | 15       | /CVREF/ / /AN10/                    | / /C1OUT/OCFA/CTED5/INT1/               |  |  |  |

|                                                                                                                                                                                                      |          | CN12/RB14                           |                                         |  |  |  |

|                                                                                                                                                                                                      | 16       |                                     | I/TCKIA/CTED6/CN11/RB15                 |  |  |  |

|                                                                                                                                                                                                      | 17       | Vss/AVss                            |                                         |  |  |  |

|                                                                                                                                                                                                      | 18       | VDD/AVDD                            |                                         |  |  |  |

|                                                                                                                                                                                                      | 19       | MCLR/VPP/RA5                        |                                         |  |  |  |

|                                                                                                                                                                                                      | 20<br>21 | n/c<br>CVREF+/VREF+/ +/AN0/ /       | CVREF+/VREF+/ +/AN0/ /                  |  |  |  |

|                                                                                                                                                                                                      | 21       | CN2/RA0                             | CTED1/CN2/RA0                           |  |  |  |

|                                                                                                                                                                                                      | 22       | CVREF-/VREF-/AN1/CN3/RA1            |                                         |  |  |  |

|                                                                                                                                                                                                      | 23       | PGED1/AN2/CTCMP/ULPWU/C1IND/        | / /CN4/RB0                              |  |  |  |

|                                                                                                                                                                                                      | 24       | PGEC1/ / /AN3/C1INC/                | / /CTED12/CN5/RB1                       |  |  |  |

|                                                                                                                                                                                                      | 25       | / /AN4/C1INB/ / /T                  | CKIB/CTED13/CN6/RB2                     |  |  |  |

|                                                                                                                                                                                                      | 26       | /AN5/C1INA/ / /CN7/RB3              |                                         |  |  |  |

|                                                                                                                                                                                                      | 27       | AN6/CN32/RC0                        |                                         |  |  |  |

|                                                                                                                                                                                                      | 28       |                                     |                                         |  |  |  |

|                                                                                                                                                                                                      | 29<br>30 | AN8/CN10/RC2<br>Vdd                 |                                         |  |  |  |

|                                                                                                                                                                                                      | 30       | Vss                                 |                                         |  |  |  |

|                                                                                                                                                                                                      | 32       | n/c                                 |                                         |  |  |  |

|                                                                                                                                                                                                      | 33       | OSCI/AN13/CLKI/CN30/RA2             |                                         |  |  |  |

|                                                                                                                                                                                                      | 34       | OSCO/CLKO/AN14/CN29/RA3             |                                         |  |  |  |

|                                                                                                                                                                                                      | 35       | OCFB/CN33/RA8                       |                                         |  |  |  |

|                                                                                                                                                                                                      | 36       | SOSCI/AN15/ / /CN1/RB4              |                                         |  |  |  |

|                                                                                                                                                                                                      | 37       | SOSCO/SCLKI/AN16/PWRLCLK/ /CN       | 0/RA4                                   |  |  |  |

|                                                                                                                                                                                                      | 38       | /CN34/RA9                           |                                         |  |  |  |

|                                                                                                                                                                                                      | 39       | /CN28/RC3                           |                                         |  |  |  |

|                                                                                                                                                                                                      | 40       | /CN25/RC4                           |                                         |  |  |  |

|                                                                                                                                                                                                      | 41       | /CN26/RC5                           |                                         |  |  |  |

| Legend: Values in indicate pin                                                                                                                                                                       | 42       | Vss                                 |                                         |  |  |  |

| Legend: Values in indicate pin<br>function differences between                                                                                                                                       | 43       | VDD                                 |                                         |  |  |  |

| PIC24F(V)XXKM202 and                                                                                                                                                                                 | 44       | n/c                                 |                                         |  |  |  |

| PIC24F(V)XXKM102 devices.                                                                                                                                                                            | 45       | PGED3/AN17/ASDA1/OC1E/CLCINA/CN27/F |                                         |  |  |  |

| Note 1: Exposed pad on underside of                                                                                                                                                                  | 46       | PGEC3/AN18/ASCL1/OC1F/CLCINB/CN24/F |                                         |  |  |  |

| device is connected to Vss.                                                                                                                                                                          | 47       | AN19/INT0/CN23/RB7                  | AN19/ /OC1A/INT0/CN23/RB7               |  |  |  |

|                                                                                                                                                                                                      | 48       | AN20/SCL1/U1CTS/C3OUT/OC1B/CTED10/  | CN22/RB8                                |  |  |  |

### 1.1.4 EASY MIGRATION

The PIC24FV16KM204 family devices have two variants. The KM20X variant provides the full feature set of the device, while the KM10X offers a reduced peripheral set, allowing for the balance of features and cost (refer to Table 1-1). Both variants allow for a smooth migration path as applications grow and evolve.

The consistent pinout scheme used throughout the entire family also helps in migrating to the next larger device. This is true when moving between devices with the same pin count, different die variants, or even moving from 20-pin or 28-pin devices to 44-pin/48-pin devices.

The PIC24F family is pin compatible with devices in the dsPIC33 family, and shares some compatibility with the pinout schema for PIC18 and dsPIC30. This extends the ability of applications to grow from the relatively simple to the powerful and complex, yet still selecting a Microchip device.

### 1.2 Other Special Features

- Communications: The PIC24FV16KM204 family incorporates a range of serial communication peripherals to handle a range of application requirements. There is an MSSP module which implements both SPI and I<sup>2</sup>C™ protocols, and supports both Master and Slave modes of operation for each. Devices also include one of two UARTs with built-in IrDA<sup>®</sup> encoders/decoders.

- Analog Features: Select members of the PIC24FV16KM204 family include two 8-bit Digital-to-Analog Converters which offer support in Idle mode, and left and right justified input data, as well as up to two operational amplifiers with selectable power and speed modes.

- Real-Time Clock/Calendar (RTCC): This module implements a full-featured clock and calendar with alarm functions in hardware, freeing up timer resources and program memory space for use of the core application.

- 12-Bit A/D Converter: This module incorporates programmable acquisition time, allowing for a channel to be selected and a conversion to be initiated without waiting for a sampling period, and faster sampling speed. The 16-deep result buffer can be used either in Sleep, to reduce power, or in Active mode to improve throughput.

- Charge Time Measurement Unit (CTMU) Interface: The PIC24FV16KM204 family includes the new CTMU interface module, which can be used for capacitive touch sensing, proximity sensing, and also for precision time measurement and pulse generation. The CTMU can also be connected to the operational amplifiers to provide active guarding, which provides increased robustness in the presence of noise in capacitive touch applications.

### 1.3 Details on Individual Family Members

Devices in the PIC24FV16KM204 family are available in 20-pin, 28-pin, 44-pin and 48-pin packages. The general block diagram for all devices is shown in Figure 1-1.

Members of the PIC24FV16KM204 family are available as both standard and high-voltage devices. High-voltage devices, designated with an "FV" in the part number (such as PIC24FV16KM204), accommodate an operating VDD range of 2.0V to 5.5V and have an on-board voltage regulator that powers the core. Peripherals operate at VDD.

Standard devices, designated by "F" (such as PIC24F16KM204), function over a lower VDD range of 1.8V to 3.6V. These parts do not have an internal regulator, and both the core and peripherals operate directly from VDD.

The PIC24FV16KM204 family may be thought of as two different device groups, both offering slightly different sets of features. These differ from each other in multiple ways:

- · The size of the Flash program memory

- The number of external analog channels available

- The number of Digital-to-Analog Converters

- · The number of operational amplifiers

- The number of analog comparators

- The presence of a Real-Time Clock and Calendar (RTCC)

- The number and type of CCP modules (i.e., MCCP vs. SCCP)

- The number of serial communication modules (both MSSPs and UARTs)

- The number of Configurable Logic Cell (CLC) modules

The general differences between the different sub-families are shown in Table 1-1 and Table 1-2.

A list of the pin features available on the PIC24FV16KM204 family devices, sorted by function, is provided in Table 1-5.

## TABLE 4-24: PAD CONFIGURATION REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11                 | Bit 10                 | Bit 9   | Bit 8   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|--------|--------|--------|--------|------------------------|------------------------|---------|---------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

|           |       |        |        |        |        |                        |                        |         |         |       |       |       |       |       |       |       |       |               |

| PADCFG1   | 2FCh  | _      | —      | _      | _      | SDO2DIS <sup>(1)</sup> | SCK2DIS <sup>(1)</sup> | SDO1DIS | SCK1DIS | _     | _     | _     | _     | _     | _     | _     | _     | 0000          |

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

Note 1: These bits are not available on the PIC24F(V)08KM101 device, read as '0'.

## 7.0 RESETS

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on Resets, refer to the "PIC24F Family Reference Manual", "Reset with Programmable Brown-out Reset" (DS39728).

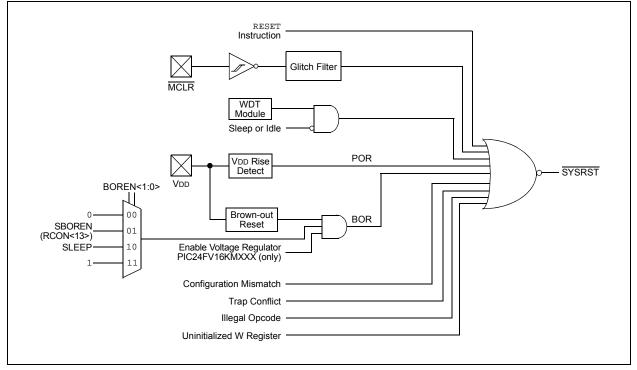

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- · POR: Power-on Reset

- MCLR: Pin Reset

- SWR: RESET Instruction

- WDTR: Watchdog Timer Reset

- · BOR: Brown-out Reset

- LPBOR: Low-Power BOR

- TRAPR: Trap Conflict Reset

- IOPUWR: Illegal Opcode Reset

- UWR: Uninitialized W Register Reset

A simplified block diagram of the Reset module is shown in Figure 7-1.

Any active source of Reset will make the SYSRST signal active. Many registers associated with the CPU and peripherals are forced to a known Reset state. Most registers are unaffected by a Reset; their status is unknown on Power-on Reset (POR) and unchanged by all other Resets.

Note: Refer to the specific peripheral or Section 3.0 "CPU" of this data sheet for register Reset states.

All types of device Reset will set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 7-1). A Power-on Reset will clear all bits except for the BOR and POR bits (RCON<1:0>) which are set. The user may set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software will not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer (WDT) and device power-saving states. The function of these bits is discussed in other sections of this manual.

Note: The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset will be meaningful.

### FIGURE 7-1: RESET SYSTEM BLOCK DIAGRAM

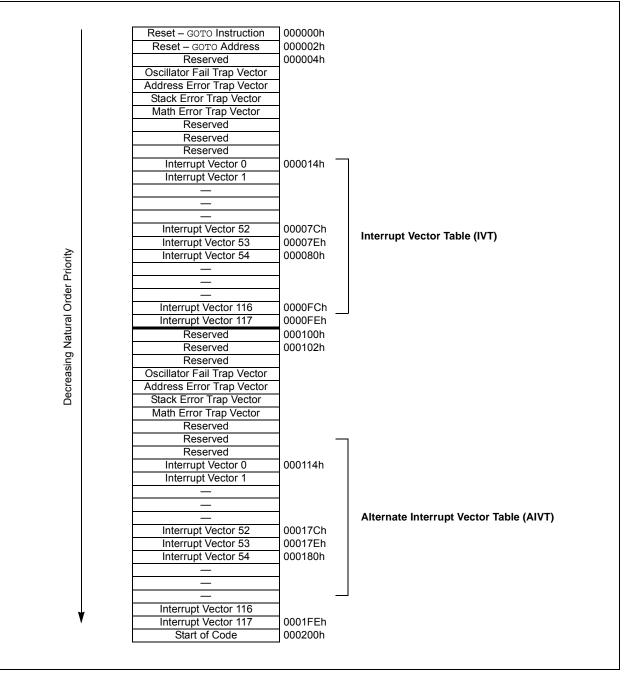

FIGURE 8-1: PIC24F INTERRUPT VECTOR TABLE

| R/W-0, HS       | U-0             | R/W-0, HS                         | R/W-0, HS        | R/W-0, HS         | U-0             | U-0             | R/W-0, HS |

|-----------------|-----------------|-----------------------------------|------------------|-------------------|-----------------|-----------------|-----------|

| NVMIF           | —               | AD1IF                             | U1TXIF           | U1RXIF            | _               | —               | CCT2IF    |

| bit 15          |                 |                                   |                  |                   |                 |                 | bit       |

|                 |                 |                                   |                  |                   |                 |                 |           |

| R/W-0, HS       | R/W-0, HS       | R/W-0, HS                         | U-0              | R/W-0, HS         | R/W-0, HS       | R/W-0, HS       | R/W-0, HS |

| CCT1IF          | CCP4IF          | CCP3IF                            |                  | T1IF              | CCP2IF          | CCP1IF          | INTOIF    |

| bit 7           |                 |                                   |                  |                   |                 |                 | bit       |

| Legend:         |                 | HS = Hardwa                       | re Settable bit  |                   |                 |                 |           |

| R = Readable    | bit             | W = Writable                      |                  | U = Unimplem      | ented bit. read | l as '0'        |           |

| -n = Value at F | POR             | '1' = Bit is set                  |                  | '0' = Bit is clea |                 | x = Bit is unkr | nown      |

|                 |                 |                                   |                  |                   |                 |                 |           |

| bit 15          |                 | Interrupt Flag                    |                  |                   |                 |                 |           |

|                 |                 | equest has occ                    |                  |                   |                 |                 |           |

|                 |                 | equest has not                    |                  |                   |                 |                 |           |

| bit 14          | -               | ted: Read as '                    |                  |                   |                 |                 |           |

| bit 13          |                 |                                   | -                | Flag Status bit   |                 |                 |           |

|                 |                 | equest has occ<br>equest has not  |                  |                   |                 |                 |           |

| bit 12          | -               | -                                 | Interrupt Flag   | Status bit        |                 |                 |           |

|                 |                 | equest has occ                    |                  | Status bit        |                 |                 |           |

|                 | •               | equest has not                    |                  |                   |                 |                 |           |

| bit 11          | -               | -                                 | terrupt Flag St  | atus bit          |                 |                 |           |

|                 |                 | equest has occ                    |                  |                   |                 |                 |           |

|                 |                 | equest has not                    |                  |                   |                 |                 |           |

| bit 10-9        | Unimplement     | ted: Read as '                    | כ'               |                   |                 |                 |           |

| bit 8           | CCT2IF: Capt    | ture/Compare 2                    | 2 Timer Interrup | ot Flag Status b  | it              |                 |           |

|                 | 1 = Interrupt r | equest has occ                    | curred           |                   |                 |                 |           |

|                 | -               | equest has not                    |                  |                   |                 |                 |           |

| bit 7           | -               |                                   | -                | ot Flag Status b  | it              |                 |           |

|                 |                 | equest has occ                    |                  |                   |                 |                 |           |

|                 |                 | equest has not                    |                  |                   |                 |                 |           |

| bit 6           | -               | -                                 |                  | ot Flag Status b  | oit             |                 |           |

|                 |                 | equest has occ                    |                  |                   |                 |                 |           |

| bit 5           | •               | equest has not                    |                  | at Elag Status h  | .;+             |                 |           |

| DIUS            | -               | equest has occ                    |                  | pt Flag Status b  | 11              |                 |           |

|                 |                 | equest has oct                    |                  |                   |                 |                 |           |

| bit 4           |                 | ted: Read as '                    |                  |                   |                 |                 |           |

| bit 3           | -               | Interrupt Flag S                  |                  |                   |                 |                 |           |

|                 |                 | equest has occ                    |                  |                   |                 |                 |           |

|                 | •               | equest has not                    |                  |                   |                 |                 |           |

| bit 2           | CCP2IF: Cap     | ture/Compare 2                    | 2 Event Interru  | ot Flag Status b  | oit             |                 |           |

|                 | 1 = Interrupt r | equest has occ                    | curred           | -                 |                 |                 |           |

|                 | 0 = Interrupt r | equest has not                    | occurred         |                   |                 |                 |           |

| bit 1           | CCP1IF: Cap     | ture/Compare                      | 1 Event Interru  | ot Flag Status b  | bit             |                 |           |

|                 |                 | equest has occ                    |                  |                   |                 |                 |           |

|                 | -               | equest has not                    |                  |                   |                 |                 |           |

|                 | INTOIL Evitor   |                                   | Elaa Statua hit  |                   |                 |                 |           |

| bit 0           |                 | nal Interrupt 0<br>equest has occ | -                |                   |                 |                 |           |

| R/W-0, HS       | R/W-0, HS                                                                                                     | R/W-0, HS                           | U-0              | U-0              | U-0              | U-0             | R/W-0, HS |  |

|-----------------|---------------------------------------------------------------------------------------------------------------|-------------------------------------|------------------|------------------|------------------|-----------------|-----------|--|

| DAC2IF          | DAC1IF                                                                                                        | CTMUIF                              | —                |                  | _                |                 | HLVDIF    |  |

| bit 15          |                                                                                                               |                                     |                  |                  |                  |                 | bit 8     |  |

|                 |                                                                                                               |                                     |                  |                  |                  |                 |           |  |

| U-0             | U-0                                                                                                           | U-0                                 | U-0              | U-0              | R/W-0, HS        | R/W-0, HS       | U-0       |  |

| —               | —                                                                                                             | —                                   | _                | —                | U2ERIF           | U1ERIF          | —         |  |

| bit 7           |                                                                                                               |                                     |                  |                  |                  |                 | bit 0     |  |

|                 |                                                                                                               |                                     |                  |                  |                  |                 |           |  |

| Legend:         |                                                                                                               | HS = Hardwar                        | re Settable bit  |                  |                  |                 |           |  |

| R = Readable    | e bit                                                                                                         | W = Writable I                      | oit              | U = Unimpler     | nented bit, read | l as '0'        |           |  |

| -n = Value at I | POR                                                                                                           | '1' = Bit is set                    |                  | '0' = Bit is cle | ared             | x = Bit is unkr | iown      |  |

|                 |                                                                                                               |                                     |                  |                  |                  |                 |           |  |

| bit 15          | •                                                                                                             | tal-to-Analog C                     |                  | rrupt Flag Stat  | us bit           |                 |           |  |

|                 |                                                                                                               | request has occ<br>request has not  |                  |                  |                  |                 |           |  |

| bit 14          |                                                                                                               | •                                   |                  | reunt Flog Stat  | ua hit           |                 |           |  |

| DIL 14          | •                                                                                                             | tal-to-Analog Co<br>request has occ |                  | mupt Flag Stat   |                  |                 |           |  |

|                 |                                                                                                               | request has not                     |                  |                  |                  |                 |           |  |

| bit 13          |                                                                                                               | MU Interrupt Fla                    |                  |                  |                  |                 |           |  |

|                 |                                                                                                               | request has occ                     | •                |                  |                  |                 |           |  |

|                 | 0 = Interrupt r                                                                                               | request has not                     | occurred         |                  |                  |                 |           |  |

| bit 12-9        | Unimplemen                                                                                                    | ted: Read as 'C                     | )'               |                  |                  |                 |           |  |

| bit 8           | HLVDIF: High                                                                                                  | n/Low-Voltage D                     | Detect Interrupt | t Flag Status bi | t                |                 |           |  |

|                 |                                                                                                               | request has occ                     |                  |                  |                  |                 |           |  |

|                 |                                                                                                               | request has not                     |                  |                  |                  |                 |           |  |

| bit 7-3         | -                                                                                                             | ted: Read as '0                     |                  |                  |                  |                 |           |  |

| bit 2           |                                                                                                               | RT2 Error Interro                   |                  | s bit            |                  |                 |           |  |

|                 |                                                                                                               | request has occ<br>request has not  |                  |                  |                  |                 |           |  |

| bit 1           | <ul> <li>Interrupt request has not occurred</li> <li>U1ERIF: UART1 Error Interrupt Flag Status bit</li> </ul> |                                     |                  |                  |                  |                 |           |  |

|                 |                                                                                                               | request has occ                     |                  |                  |                  |                 |           |  |

|                 |                                                                                                               | request has not                     |                  |                  |                  |                 |           |  |

| bit 0           | Unimplemen                                                                                                    | ted: Read as 'o                     | )'               |                  |                  |                 |           |  |

|                 | •                                                                                                             |                                     |                  |                  |                  |                 |           |  |

#### REGISTER 8-9: IFS4: INTERRUPT FLAG STATUS REGISTER 4

## **10.0 POWER-SAVING FEATURES**

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the *"PIC24F Family Reference Manual"*, "Power-Saving Features with VBAT" (DS30622).

This FRM describes some features which

are not implemented in this device. Sections related to the VBAT pin and Deep Sleep do not apply to the PIC24FV16KM204 family.

The PIC24FV16KM204 family of devices provides the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of circuits being clocked constitutes lower consumed power. All PIC24F devices manage power consumption in four different ways:

- Clock Frequency

- Instruction-Based Sleep and Idle modes

- · Software Controlled Doze mode

- Selective Peripheral Control in Software

Combinations of these methods can be used to selectively tailor an application's power consumption, while still maintaining critical application features, such as timing-sensitive communications.

### 10.1 Clock Frequency and Clock Switching

PIC24F devices allow for a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or high-precision oscillators by simply changing the NOSCx bits. The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in **Section 9.0** "Oscillator Configuration".

### 10.2 Instruction-Based Power-Saving Modes

PIC24F devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution; Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The 'C' syntax of the  $\ensuremath{\mathtt{PWRSAV}}$  instruction is shown in Example 10-1.

Note: SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to "wake-up".

#### 10.2.1 SLEEP MODE

Sleep mode includes these features:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption will be reduced to a minimum provided that no I/O pin is sourcing current.

- The I/O pin directions and states are frozen.

- The Fail-Safe Clock Monitor does not operate during Sleep mode since the system clock source is disabled.

- The LPRC clock will continue to run in Sleep mode if the WDT or RTCC with LPRC as the clock source is enabled.

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode.

- Some device features or peripherals may continue to operate in Sleep mode. This includes items, such as the Input Change Notification on the I/O ports or peripherals that use an External Clock input. Any peripheral that requires the system clock source for its operation will be disabled in Sleep mode.

The device will wake-up from Sleep mode on any of these events:

- On any interrupt source that is individually enabled

- · On any form of device Reset

- · On a WDT time-out

On wake-up from Sleep, the processor will restart with the same clock source that was active when Sleep mode was entered.

#### EXAMPLE 10-1: 'C' POWER-SAVING ENTRY

| -                     |                                                    |                                       |                                                 |                                                                                      |                                    |                     | ,                   |

|-----------------------|----------------------------------------------------|---------------------------------------|-------------------------------------------------|--------------------------------------------------------------------------------------|------------------------------------|---------------------|---------------------|

| R/W-0                 | R/W-0                                              | U-0                                   | U-0                                             | R/W-0                                                                                | R/W-0                              | R/W-0               | R/W-0               |

| OPSSRC <sup>(1)</sup> | RTRGEN <sup>(2)</sup>                              |                                       | —                                               | OPS3 <sup>(3)</sup>                                                                  | OPS2 <sup>(3)</sup>                | OPS1 <sup>(3)</sup> | OPS0 <sup>(3)</sup> |

| bit 15                |                                                    |                                       |                                                 |                                                                                      |                                    |                     | bit 8               |

|                       |                                                    |                                       |                                                 |                                                                                      |                                    |                     |                     |

| R/W-0                 | R/W-0                                              | R/W-0                                 | R/W-0                                           | R/W-0                                                                                | R/W-0                              | R/W-0               | R/W-0               |

| TRIGEN <sup>(4)</sup> | ONESHOT                                            | ALTSYNC                               | SYNC4                                           | SYNC3                                                                                | SYNC2                              | SYNC1               | SYNC0               |

| bit 7                 |                                                    |                                       |                                                 |                                                                                      |                                    |                     | bit 0               |

|                       |                                                    |                                       |                                                 |                                                                                      |                                    |                     |                     |

| Legend:               |                                                    |                                       |                                                 |                                                                                      |                                    |                     |                     |

| R = Readable          |                                                    | W = Writable I                        | oit                                             | -                                                                                    | nented bit, read                   | l as '0'            |                     |

| -n = Value at         | POR                                                | '1' = Bit is set                      |                                                 | '0' = Bit is clea                                                                    | ared                               | x = Bit is unkr     | iown                |

|                       |                                                    |                                       |                                                 | (1)                                                                                  |                                    |                     |                     |

| bit 15                |                                                    | tput Postscaler                       |                                                 |                                                                                      |                                    |                     |                     |

|                       |                                                    | ostscaler scales                      |                                                 | er output event                                                                      | IS                                 |                     |                     |

| bit 14                |                                                    | trigger Enable                        |                                                 |                                                                                      |                                    |                     |                     |

|                       |                                                    | e can be retrig                       |                                                 | RIGEN bit = 1                                                                        |                                    |                     |                     |

|                       |                                                    |                                       |                                                 | en TRIGEN bit =                                                                      | = 1                                |                     |                     |

| bit 13-12             | Unimplement                                        | ted: Read as 'o                       | )'                                              |                                                                                      |                                    |                     |                     |

| bit 11-8              | OPS3<3:0>: (                                       | CCPx Interrupt                        | Output Postso                                   | ale Select bits <sup>(</sup>                                                         | 3)                                 |                     |                     |

|                       |                                                    | upt every 16th t<br>upt every 15th t  |                                                 |                                                                                      |                                    |                     |                     |

|                       | 0011 = Interru<br>0010 = Interru<br>0001 = Interru | upt every 3rd tir<br>upt every 2nd ti | ne base perio<br>ne base perio<br>me base perio | d match<br>d match or 4th i<br>d match or 3rd<br>od match or 2nc<br>od match or inpi | input capture e<br>l input capture | event<br>event      |                     |

| bit 7                 | TRIGEN: CCF                                        | Px Trigger Enal                       | ole bit <sup>(4)</sup>                          |                                                                                      |                                    |                     |                     |

|                       |                                                    | peration of time<br>peration of time  |                                                 |                                                                                      |                                    |                     |                     |

| bit 6                 | ONESHOT: O                                         | ne-Shot Mode                          | Enable bit                                      |                                                                                      |                                    |                     |                     |

|                       |                                                    | t Trigger mode<br>t Trigger mode      |                                                 | igger duration is                                                                    | s set by OSCN                      | T<2:0>              |                     |

| bit 5                 | ALTSYNC: C                                         | CPx Clock Sele                        | ect bits                                        |                                                                                      |                                    |                     |                     |

|                       |                                                    |                                       |                                                 | ule synchroniza                                                                      |                                    |                     |                     |

|                       |                                                    | -                                     |                                                 | nal is the Time                                                                      | Base Reset/ro                      | ollover event       |                     |

| bit 4-0               |                                                    | CCPx Synchroi                         |                                                 | e Select bits                                                                        |                                    |                     |                     |

|                       | See lable 13-                                      | 6 for the definit                     | ion of inputs.                                  |                                                                                      |                                    |                     |                     |

| Note 1: Th            | nis control bit ha                                 | is no function ir                     | Input Capture                                   | e modes.                                                                             |                                    |                     |                     |

|                       | nis control bit ha                                 |                                       |                                                 |                                                                                      |                                    |                     |                     |

|                       | utput postscale s<br>odes.                         | settings from 1:8                     | 5 to 1:16 (0100                                 | )-1111) will resu                                                                    | ult in a FIFO but                  | ffer overflow for   | Input Capture       |

### REGISTER 13-2: CCPxCON1H: CCPx CONTROL 1 HIGH REGISTERS

4: Clock source options are limited when Trigger operation is enabled; refer to Table 13-1.

## 15.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

| Note: | This data sheet summarizes the features of  |  |  |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|--|--|

|       | this group of PIC24F devices. It is not     |  |  |  |  |  |  |  |

|       | intended to be a comprehensive reference    |  |  |  |  |  |  |  |

|       | source. For more information on the Univer- |  |  |  |  |  |  |  |

|       | sal Asynchronous Receiver Transmitter,      |  |  |  |  |  |  |  |

|       | refer to the "PIC24F Family Reference       |  |  |  |  |  |  |  |

|       | Manual", " <b>UART"</b> (DS39708).          |  |  |  |  |  |  |  |

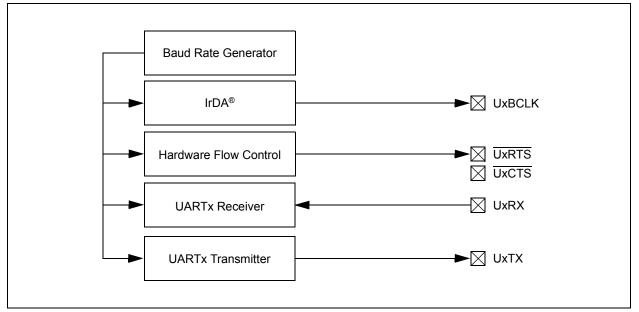

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in this PIC24F device family. The UART is a full-duplex, asynchronous system that can communicate with peripheral devices, such as personal computers, LIN/J2602, RS-232 and RS-485 interfaces. This module also supports a hardware flow control option with the UxCTS and UxRTS pins, and also includes an IrDA<sup>®</sup> encoder and decoder.

The primary features of the UART module are:

- Full-Duplex, 8-Bit or 9-Bit Data Transmission through the UxTX and UxRX Pins

- Even, Odd or No Parity Options (for 8-bit data)

- · One or Two Stop bits

- Hardware Flow Control Option with UxCTS and UxRTS Pins

- Fully Integrated Baud Rate Generator (IBRG) with 16-Bit Prescaler

- Baud Rates Ranging from 1 Mbps to 15 bps at 16 MIPS

- 4-Deep, First-In-First-Out (FIFO) Transmit Data Buffer

- · 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-Bit mode with Address Detect (9<sup>th</sup> bit = 1)

- · Transmit and Receive Interrupts

- · Loopback mode for Diagnostic Support

- · Support for Sync and Break Characters

- · Supports Automatic Baud Rate Detection

- IrDA<sup>®</sup> Encoder and Decoder Logic

- 16x Baud Clock Output for IrDA Support

A simplified block diagram of the UARTx module is shown in Figure 15-1. The UARTx module consists of these important hardware elements:

- Baud Rate Generator

- Asynchronous Transmitter

- · Asynchronous Receiver

- Note: Throughout this section, references to register and bit names that may be associated with a specific USART module are referred to generically by the use of 'x' in place of the specific module number. Thus, "UxSTA" might refer to the USART Status register for either USART1 or USART2.

### FIGURE 15-1: UARTX MODULE SIMPLIFIED BLOCK DIAGRAM

## REGISTER 16-1: RCFGCAL: RTCC CALIBRATION AND CONFIGURATION REGISTER<sup>(1)</sup> (CONTINUED)

- **Note 1:** The RCFGCAL register is only affected by a POR.

- 2: A write to the RTCEN bit is only allowed when RTCWREN = 1.

- 3: This bit is read-only; it is cleared to '0' on a write to the lower half of the MINSEC register.

### REGISTER 25-4: FOSC: OSCILLATOR CONFIGURATION REGISTER

| R/P-1  | R/P-1  | R/P-1   | R/P-1     | R/P-1     | R/P-1    | R/P-1   | R/P-1   |

|--------|--------|---------|-----------|-----------|----------|---------|---------|

| FCKSM1 | FCKSM0 | SOSCSEL | POSCFREQ1 | POSCFREQ0 | OSCIOFNC | POSCMD1 | POSCMD0 |

| bit 7  |        |         |           |           |          |         | bit 0   |

| Legend:           |                      |                            |                    |

|-------------------|----------------------|----------------------------|--------------------|

| R = Readable bit  | P = Programmable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared       | x = Bit is unknown |

| bit 7-6 | <b>FCKSM&lt;1:0&gt;:</b> Clock Switching and Fail-Safe Clock Monitor Selection Configuration bits<br>1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled<br>01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled<br>00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled                                            |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5   | <b>SOSCSEL:</b> Secondary Oscillator Power Selection Configuration bit<br>1 = Secondary Oscillator is configured for high-power operation<br>0 = Secondary Oscillator is configured for low-power operation                                                                                                                                                          |

| bit 4-3 | <b>POSCFREQ&lt;1:0&gt;:</b> Primary Oscillator Frequency Range Configuration bits<br>11 = Primary Oscillator/External Clock input frequency is greater than 8 MHz<br>10 = Primary Oscillator/External Clock input frequency is between 100 kHz and 8 MHz<br>01 = Primary Oscillator/External Clock input frequency is less than 100 kHz<br>00 = Reserved; do not use |

| bit 2   | <ul> <li>OSCIOFNC: CLKO Enable Configuration bit</li> <li>1 = CLKO output signal is active on the OSCO pin; Primary Oscillator must be disabled or configured for the External Clock (EC) mode for the CLKO to be active (POSCMD&lt;1:0&gt; = 11 or 00)</li> <li>0 = CLKO output is disabled</li> </ul>                                                              |

| bit 1-0 | POSCMD<1:0>: Primary Oscillator Configuration bits<br>11 = Primary Oscillator mode is disabled<br>10 = HS Oscillator mode is selected<br>01 = XT Oscillator mode is selected                                                                                                                                                                                         |

00 = External Clock mode is selected

NOTES:

| DC CHARACTERISTICS |                 | Standard C             |                              |       | s: 1.8V to 3.6V (PIC24F16KM204)<br>2.0V to 5.5V (PIC24FV16KM204)<br>-40°C $\leq$ TA $\leq$ +85°C for Industrial<br>-40°C $\leq$ TA $\leq$ +125°C for Extended |            |                           |  |  |

|--------------------|-----------------|------------------------|------------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------------------|--|--|

| Parameter<br>No.   | Device          | Typical <sup>(1)</sup> | cal <sup>(1)</sup> Max Units |       |                                                                                                                                                               | Conditions |                           |  |  |

| Power-Dow          | n Current (IPD) |                        |                              |       |                                                                                                                                                               |            |                           |  |  |

| DC60               | PIC24FV16KMXXX  |                        | _                            |       | -40°C                                                                                                                                                         |            |                           |  |  |

|                    |                 |                        | 8.0                          |       | +25°C                                                                                                                                                         |            |                           |  |  |

|                    |                 | 6.0                    | 8.5                          | μA    | +60°C                                                                                                                                                         | 2.0V       |                           |  |  |

|                    |                 |                        | 9.0                          |       | +85°C                                                                                                                                                         |            |                           |  |  |

|                    |                 |                        | 15.0                         |       | +125°C                                                                                                                                                        |            |                           |  |  |

|                    |                 |                        | —                            |       | -40°C                                                                                                                                                         |            |                           |  |  |

|                    |                 |                        | 8.0                          |       | +25°C                                                                                                                                                         |            |                           |  |  |

|                    |                 | 6.0                    | 9.0                          | μA    | +60°C                                                                                                                                                         | 5.0V       |                           |  |  |

|                    |                 |                        | 10.0                         |       | +85°C                                                                                                                                                         |            |                           |  |  |

|                    |                 |                        | 15.0                         |       | +125°C                                                                                                                                                        |            | Sleep Mode <sup>(2)</sup> |  |  |

|                    | PIC24F16KMXXX   |                        | _                            |       | -40°C                                                                                                                                                         |            |                           |  |  |

|                    |                 |                        | 0.80                         |       | +25°C                                                                                                                                                         |            |                           |  |  |

|                    |                 | 0.025                  | 1.5                          | μA    | +60°C                                                                                                                                                         | 1.8V       |                           |  |  |

|                    |                 |                        | 2.0                          |       | +85°C                                                                                                                                                         |            |                           |  |  |

|                    |                 |                        | 7.5                          |       | +125°C                                                                                                                                                        |            |                           |  |  |

|                    |                 |                        | —                            |       | -40°C                                                                                                                                                         |            |                           |  |  |

|                    |                 |                        | 1.0                          |       | +25°C                                                                                                                                                         |            |                           |  |  |

|                    |                 | 0.040                  | 2.0                          | μA    | +60°C                                                                                                                                                         | 3.3V       |                           |  |  |

|                    |                 |                        | 3.0                          |       | +85°C                                                                                                                                                         |            |                           |  |  |

|                    |                 |                        | 7.5                          |       | +125°C                                                                                                                                                        |            |                           |  |  |

| DC61               | PIC24FV16KMXXX  | 0.25                   | _                            | μA    | +85°C                                                                                                                                                         | 2.0V       |                           |  |  |

|                    |                 |                        | 7.5                          | P., 4 | +125°C                                                                                                                                                        |            | Low-Voltage               |  |  |

|                    |                 | 0.35                   | 3.0                          | μA    | +85°C                                                                                                                                                         | 5.0V       | Sleep Mode <sup>(2)</sup> |  |  |

|                    |                 |                        | 7.5                          | r     | +125°C                                                                                                                                                        |            |                           |  |  |

### TABLE 27-8: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

Legend: Unshaded rows represent PIC24F16KMXXX devices and shaded rows represent PIC24FV16KMXXX devices.

**Note 1:** Data in the Typical column is at 3.3V, +25°C (PIC24F16KMXXX) or 5.0V, +25°C (PIC24FV16KMXXX) unless otherwise stated. Parameters are for design guidance only and are not tested.

2: Base IPD is measured with all peripherals and clocks shut down. All I/Os are configured as outputs and set low. PMSLP is set to '0' and WDT, etc., are all switched off.

**3:** The ∆ current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

| Param<br>No. | Symbol | Characteristic                                         | Min | Тур | Max | Units | Comments |

|--------------|--------|--------------------------------------------------------|-----|-----|-----|-------|----------|

| 300          | TRESP  | Response Time <sup>*(1)</sup>                          | _   | 150 | 400 | ns    |          |

| 301          | Тмс2о∨ | Comparator Mode Change to<br>Output Valid <sup>*</sup> | —   | _   | 10  | μs    |          |

### TABLE 27-26: COMPARATOR TIMING REQUIREMENTS

Parameters are characterized but not tested.

\*

**Note 1:** Response time is measured with one comparator input at (VDD – 1.5)/2, while the other input transitions from Vss to VDD.

#### TABLE 27-27: COMPARATOR VOLTAGE REFERENCE SETTLING TIME SPECIFICATIONS

| Param<br>No. | Symbol | Characteristic               | Min | Тур | Max | Units | Comments |

|--------------|--------|------------------------------|-----|-----|-----|-------|----------|

| VR310        | TSET   | Settling Time <sup>(1)</sup> |     |     | 10  | μS    |          |

Note 1: Settling time is measured while CVRSS = 1 and the CVR<3:0> bits transition from '0000' to '1111'.

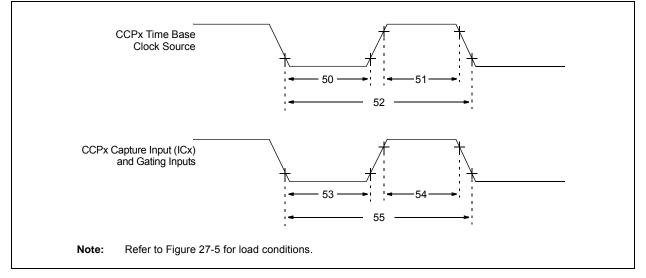

### FIGURE 27-10: CAPTURE/COMPARE/PWM TIMINGS (MCCPx, SCCPx MODULES)

### TABLE 27-28: CAPTURE/COMPARE/PWM REQUIREMENTS (MCCPx, SCCPx MODULES)

| Param<br>No. | Symbol | Characteristic                         | Min        | Max | Units | Conditions                         |

|--------------|--------|----------------------------------------|------------|-----|-------|------------------------------------|

| 50           | TCLKL  | CCPx Time Base Clock Source Low Time   | TCY/2      | _   | ns    |                                    |

| 51           | ТсікН  | CCPx Time Base Clock Source High Time  | Tcy/2      | _   | ns    |                                    |

| 52           | TCLK   | CCPx Time Base Clock Source Period     | Тсү        | -   | ns    |                                    |

| 53           | TccL   | CCPx Capture or Gating Input Low Time  | TCLK       | —   | ns    |                                    |

| 54           | ТссН   | CCPx Capture or Gating Input High Time | TCLK       | _   | ns    |                                    |

| 55           | TCCP   | CCPx Capture or Gating Input Period    | 2 * Tclk/N | —   | ns    | N = Prescale<br>Value (1, 4 or 16) |

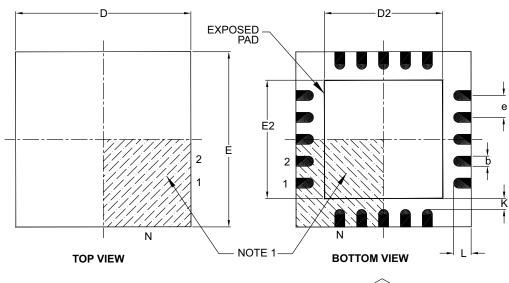

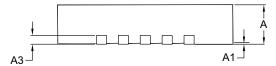

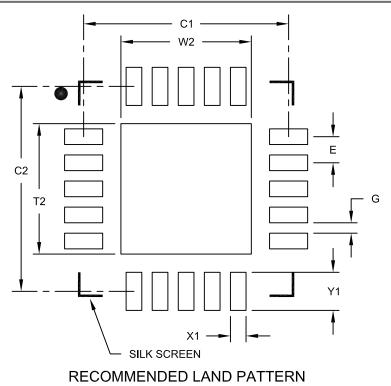

### 20-Lead Plastic Quad Flat, No Lead Package (ML) – 4x4x0.9 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units     | Jnits MILLIMETERS |          |      |

|------------------------|-----------|-------------------|----------|------|

| Dimensi                | on Limits | MIN               | NOM      | MAX  |

| Number of Pins         | Ν         | 20                |          |      |

| Pitch                  | е         |                   | 0.50 BSC |      |

| Overall Height         | Α         | 0.80              | 0.90     | 1.00 |

| Standoff               | A1        | 0.00 0.02 0.05    |          |      |

| Contact Thickness      | A3        | 0.20 REF          |          |      |

| Overall Width          | E         | 4.00 BSC          |          |      |

| Exposed Pad Width      | E2        | 2.60 2.70 2.80    |          |      |

| Overall Length         | D         | 4.00 BSC          |          |      |

| Exposed Pad Length     | D2        | 2.60              | 2.70     | 2.80 |

| Contact Width          | b         | 0.18              | 0.25     | 0.30 |

| Contact Length         | L         | 0.30 0.40 0.50    |          |      |

| Contact-to-Exposed Pad | К         | 0.20 – –          |          |      |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-126B

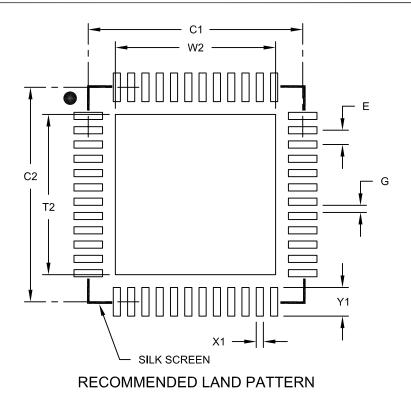

## 20-Lead Plastic Quad Flat, No Lead Package (ML) - 4x4 mm Body [QFN] With 0.40 mm Contact Length

|                            | MILLIMETERS |      |      |      |

|----------------------------|-------------|------|------|------|

| Dimension Limits           |             | MIN  | NOM  | MAX  |

| Contact Pitch              | E           |      |      |      |

| Optional Center Pad Width  | W2          |      |      | 2.50 |