Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                      |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 37                                                                            |

| Program Memory Size        | 8KB (2.75K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5V                                                                       |

| Data Converters            | A/D 22x10b/12b; D/A 2x8b                                                      |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 44-VQFN Exposed Pad                                                           |

| Supplier Device Package    | 44-QFN (8×8)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fv08km204-e-ml |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 1-2: DEVICE FEATURES FOR THE PIC24F16KM104 FAMILY

| Features                                            | PIC24F16KM104                                                                                                                                       | PIC24F16KM102                            | PIC24F08KM102 | PIC24F08KM101 |  |  |  |  |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|---------------|---------------|--|--|--|--|

| Operating Frequency                                 |                                                                                                                                                     | DC-3                                     | 2 MHz         |               |  |  |  |  |

| Program Memory (bytes)                              | 16K                                                                                                                                                 | 16K                                      | 8K            | 8K            |  |  |  |  |

| Program Memory (instructions)                       | 5632                                                                                                                                                | 5632                                     | 2816          | 2816          |  |  |  |  |

| Data Memory (bytes)                                 |                                                                                                                                                     | 10                                       | 24            |               |  |  |  |  |

| Data EEPROM Memory (bytes)                          |                                                                                                                                                     | 5                                        | 12            |               |  |  |  |  |

| Interrupt Sources (soft vectors/NMI traps)          |                                                                                                                                                     | 25 (2                                    | 21/4)         |               |  |  |  |  |

| Voltage Range                                       |                                                                                                                                                     | 1.8-                                     | 3.6V          |               |  |  |  |  |

| I/O Ports                                           | PORTA<11:0><br>PORTB<15:0><br>PORTC<9:0>                                                                                                            | PORTA<6:0><br>PORTB<15:12,9:7,<br>4,2:0> |               |               |  |  |  |  |

| Total I/O Pins                                      | 38 24 18                                                                                                                                            |                                          |               |               |  |  |  |  |

| Timers                                              | 5<br>(One 16-bit timer, two MCCPs/SCCPs with up to two 16/32 timers each                                                                            |                                          |               |               |  |  |  |  |

| Capture/Compare/PWM modules<br>MCCP<br>SCCP         |                                                                                                                                                     |                                          | 1             |               |  |  |  |  |

| Serial Communications<br>MSSP<br>UART               |                                                                                                                                                     |                                          | 1             |               |  |  |  |  |

| Input Change Notification Interrupt                 | 37                                                                                                                                                  | 23                                       | }             | 17            |  |  |  |  |

| 12-Bit Analog-to-Digital Module<br>(input channels) | 22                                                                                                                                                  | 19                                       | )             | 16            |  |  |  |  |

| Analog Comparators                                  |                                                                                                                                                     |                                          | 1             |               |  |  |  |  |

| 8-Bit Digital-to-Analog Converters                  |                                                                                                                                                     | _                                        | _             |               |  |  |  |  |

| Operational Amplifiers                              |                                                                                                                                                     | -                                        | _             |               |  |  |  |  |

| Charge Time Measurement Unit (CTMU)                 |                                                                                                                                                     | Y                                        | es            |               |  |  |  |  |

| Real-Time Clock and Calendar (RTCC)                 |                                                                                                                                                     | -                                        | _             |               |  |  |  |  |

| Configurable Logic Cell (CLC)                       | 1                                                                                                                                                   |                                          |               |               |  |  |  |  |

| Resets (and delays)                                 | POR, BOR, RESET Instruction, MCLR, WDT, Illegal Opcode,<br>REPEAT Instruction, Hardware Traps, Configuration Word Mismatch<br>(PWRT, OST, PLL Lock) |                                          |               |               |  |  |  |  |

| Instruction Set                                     | 76 Base Instructions, Multiple Addressing Mode Variations                                                                                           |                                          |               |               |  |  |  |  |

| Packages                                            | 44-Pin<br>QFN/TQFP,<br>48-Pin UQFN<br>28-Pin<br>SPDIP/SSOP/SOIC/QFN<br>SOIC/SSOP/F                                                                  |                                          |               |               |  |  |  |  |

## TABLE 4-17: OP AMP 1 REGISTER MAP

| File Name              | Addr. | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|------------------------|-------|--------|--------|---------|--------|--------|--------|-------|-------|--------|-------|---------|---------|---------|---------|---------|---------|---------------|

|                        |       |        |        |         |        |        |        |       |       |        |       |         |         |         |         |         |         |               |

| AMP1CON <sup>(1)</sup> | 24Ah  | AMPEN  | _      | AMPSIDL | AMPSLP | _      | _      | _     | —     | SPDSEL | _     | NINSEL2 | NINSEL1 | NINSEL0 | PINSEL2 | PINSEL1 | PINSEL0 | 0000          |

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

Note 1: This registers are available only on PIC24F(V)16KM2XX devices.

### TABLE 4-18: OP AMP 2 REGISTER MAP

| File Name              | Addr. | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|------------------------|-------|--------|--------|---------|--------|--------|--------|-------|-------|--------|-------|---------|---------|---------|---------|---------|---------|---------------|

| AMP2CON <sup>(1)</sup> | 24Ch  | AMPEN  | _      | AMPSIDL | AMPSLP | _      | _      | _     | _     | SPDSEL | —     | NINSEL2 | NINSEL1 | NINSEL0 | PINSEL2 | PINSEL1 | PINSEL0 | 0000          |

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

Note 1: This registers are available only on PIC24F(V)16KM2XX devices.

### TABLE 4-19: DAC1 REGISTER MAP

| File Name            | Addr.   | Bit 15                  | Bit 14                  | Bit 13      | Bit 12      | Bit 11      | Bit 10      | Bit 9      | Bit 8      | Bit 7                  | Bit 6      | Bit 5      | Bit 4                  | Bit 3      | Bit 2      | Bit 1      | Bit 0      | All<br>Resets |

|----------------------|---------|-------------------------|-------------------------|-------------|-------------|-------------|-------------|------------|------------|------------------------|------------|------------|------------------------|------------|------------|------------|------------|---------------|

| DAC1CON              | 1) 274h | DACEN                   | -                       | DACSIDL     | DACSLP      | DACFM       | -           | SRDIS      | DACTRIG    | DACOE                  | DACTSEL4   | DACTSEL3   | DACTSEL2               | DACTSEL1   | DACTSEL0   | DACREF1    | DACREF0    | 0000          |

| DAC1DAT <sup>(</sup> | ) 276h  | DACDAT15 <sup>(2)</sup> | DACDAT14 <sup>(2)</sup> | DACDAT13(2) | DACDAT12(2) | DACDAT11(2) | DACDAT10(2) | DACDAT9(2) | DACDAT8(2) | DACDAT7 <sup>(2)</sup> | DACDAT6(2) | DACDAT5(2) | DACDAT4 <sup>(2)</sup> | DACDAT3(2) | DACDAT2(2) | DACDAT1(2) | DACDAT0(2) | 0000          |

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

Note 1: These registers are available only on PIC24F(V)16KM1XX devices.

2: The 8-bit result format depends on the value of the DACFM control bit.

### TABLE 4-20: DAC2 REGISTER MAP

| File Name              | Addr. | Bit 15      | Bit 14      | Bit 13      | Bit 12      | Bit 11      | Bit 10      | Bit 9      | Bit 8      | Bit 7      | Bit 6      | Bit 5      | Bit 4      | Bit 3      | Bit 2      | Bit 1      | Bit 0      | All<br>Resets |

|------------------------|-------|-------------|-------------|-------------|-------------|-------------|-------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|---------------|

| DAC2CON <sup>(1)</sup> | 278h  | DACEN       | -           | DACSIDL     | DACSLP      | DACFM       | -           | SRDIS      | DACTRIG    | DACOE      | DACTSEL4   | DACTSEL3   | DACTSEL2   | DACTSEL1   | DACTSEL0   | DACREF1    | DACREF0    | 0000          |

| DAC2DAT <sup>(1)</sup> | 27Ah  | DACDAT15(2) | DACDAT14(2) | DACDAT13(2) | DACDAT12(2) | DACDAT11(2) | DACDAT10(2) | DACDAT9(2) | DACDAT8(2) | DACDAT7(2) | DACDAT6(2) | DACDAT5(2) | DACDAT4(2) | DACDAT3(2) | DACDAT2(2) | DACDAT1(2) | DACDATO(2) | 0000          |

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

Note 1: These registers are available only on PIC24F(V)16KM2XX devices.

2: The 8-bit result format depends on the value of the DACFM control bit.

## **REGISTER 7-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

| bit 4 | WDTO: Watchdog Timer Time-out Flag bit<br>1 = WDT time-out has occurred<br>0 = WDT time-out has not occurred                                           |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3 | SLEEP: Wake-up from Sleep Flag bit<br>1 = Device has been in Sleep mode<br>0 = Device has not been in Sleep mode                                       |

| bit 2 | IDLE: Wake-up from Idle Flag bit<br>1 = Device has been in Idle mode<br>0 = Device has not been in Idle mode                                           |

| bit 1 | <b>BOR:</b> Brown-out Reset Flag bit<br>1 = A Brown-out Reset has occurred (the BOR is also set after a POR)<br>0 = A Brown-out Reset has not occurred |

| bit 0 | <b>POR:</b> Power-on Reset Flag bit<br>1 = A Power-on Reset has occurred<br>0 = A Power-on Reset has not occurred                                      |

|       |                                                                                                                                                        |

- **Note 1:** All of the Reset status bits may be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the FWDTEN<1:0> Configuration bits are '11' (unprogrammed), the WDT is always enabled regardless of the SWDTEN bit setting.

- 3: This is implemented on PIC24FV16KMXXX parts only; not used on PIC24F16KMXXX devices.

### TABLE 7-1: RESET FLAG BIT OPERATION

| Flag Bit          | Setting Event                                     | Clearing Event          |

|-------------------|---------------------------------------------------|-------------------------|

| TRAPR (RCON<15>)  | Trap Conflict Event                               | POR                     |

| IOPUWR (RCON<14>) | Illegal Opcode or Uninitialized W Register Access | POR                     |

| CM (RCON<9>)      | Configuration Mismatch Reset                      | POR                     |

| EXTR (RCON<7>)    | MCLR Reset                                        | POR                     |

| SWR (RCON<6>)     | RESET Instruction                                 | POR                     |

| WDTO (RCON<4>)    | WDT Time-out                                      | PWRSAV Instruction, POR |

| SLEEP (RCON<3>)   | PWRSAV #SLEEP Instruction                         | POR                     |

| IDLE (RCON<2>)    | PWRSAV #IDLE Instruction                          | POR                     |

| BOR (RCON<1>)     | POR, BOR                                          | —                       |

| POR (RCON<0>)     | POR                                               | —                       |

Note: All Reset flag bits may be set or cleared by the user software.

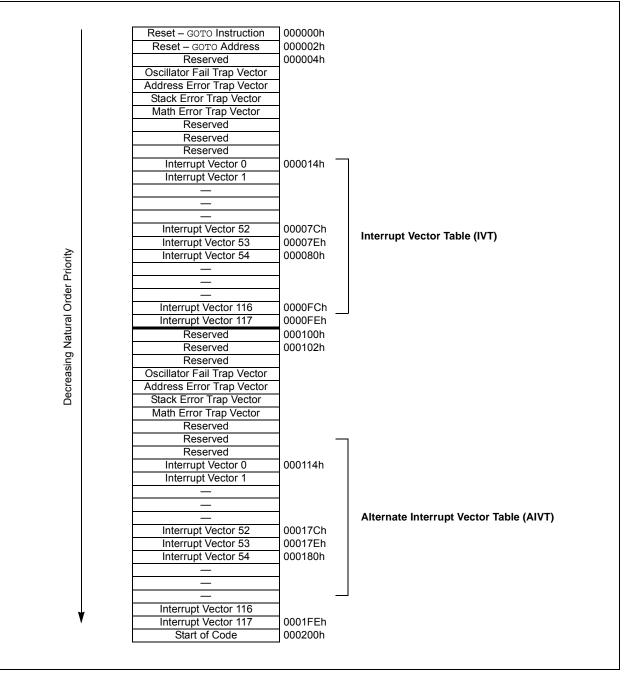

FIGURE 8-1: PIC24F INTERRUPT VECTOR TABLE

## REGISTER 16-1: RCFGCAL: RTCC CALIBRATION AND CONFIGURATION REGISTER<sup>(1)</sup> (CONTINUED)

- **Note 1:** The RCFGCAL register is only affected by a POR.

- 2: A write to the RTCEN bit is only allowed when RTCWREN = 1.

- 3: This bit is read-only; it is cleared to '0' on a write to the lower half of the MINSEC register.

### 16.2.5 RTCVAL REGISTER MAPPINGS

### REGISTER 16-4: YEAR: YEAR VALUE REGISTER<sup>(1)</sup>

| - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - | U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|-----|-----|-----|-----|-----|-------|

| bit 15 bit 8                                                                                                                                                                                                          | _      | —   | _   | —   | —   | —   | —   | —     |

|                                                                                                                                                                                                                       | bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-x  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| YRTEN3 | YRTEN2 | YRTEN1 | YRTEN0 | YRONE3 | YRONE2 | YRONE1 | YRONE0 |

| bit 7  | •      |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'

- bit 7-4 **YRTEN<3:0>:** Binary Coded Decimal Value of Year's Tens Digit bits Contains a value from 0 to 9.

- bit 3-0 **YRONE<3:0>:** Binary Coded Decimal Value of Year's Ones Digit bits Contains a value from 0 to 9.

**Note 1:** A write to the YEAR register is only allowed when RTCWREN = 1.

## **REGISTER 16-5:** MTHDY: MONTH AND DAY VALUE REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   |

|--------|-----|-----|---------|---------|---------|---------|---------|

| —      | —   | —   | MTHTEN0 | MTHONE3 | MTHONE2 | MTHONE1 | MTHONE0 |

| bit 15 |     |     |         |         |         |         | bit 8   |

| U-0   | U-0 | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   | DAYTEN1 | DAYTEN0 | DAYONE3 | DAYONE2 | DAYONE1 | DAYONE0 |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-13 Unimplemented: Read as '0'

- bit 12 MTHTEN0: Binary Coded Decimal Value of Month's Tens Digit bit Contains a value of '0' or '1'.

- bit 11-8 MTHONE<3:0>: Binary Coded Decimal Value of Month's Ones Digit bits Contains a value from 0 to 9.

- bit 7-6 Unimplemented: Read as '0'

- bit 5-4 **DAYTEN<1:0>:** Binary Coded Decimal Value of Day's Tens Digit bits Contains a value from 0 to 3.

- bit 3-0 **DAYONE<3:0>:** Binary Coded Decimal Value of Day's Ones Digit bits Contains a value from 0 to 9.

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

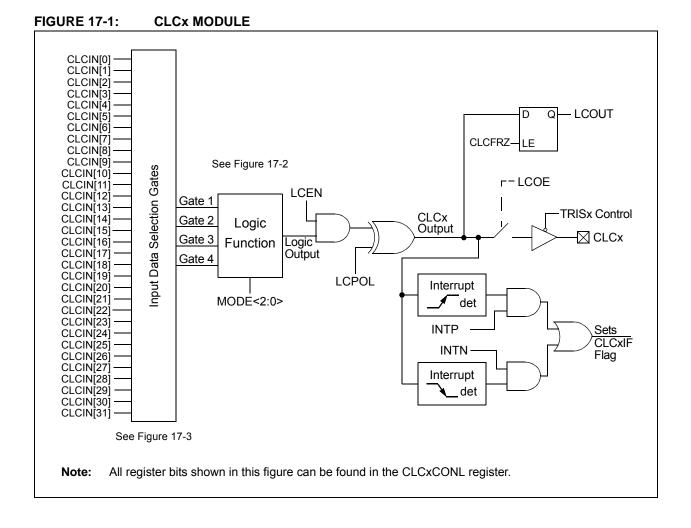

## 17.0 CONFIGURABLE LOGIC CELL (CLC)

The Configurable Logic Cell (CLC) module allows the user to specify combinations of signals as inputs to a logic function and to use the logic output to control other peripherals or I/O pins. This provides greater flex-ibility and potential in embedded designs since the CLC

module can operate outside the limitations of software execution and supports a vast amount of output designs.

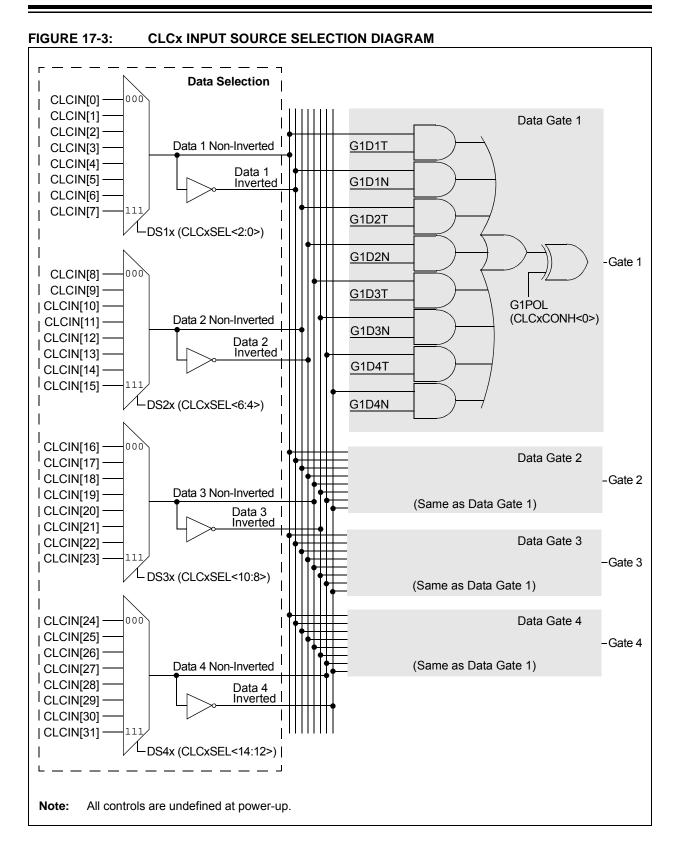

There are four input gates to the selected logic function. These four input gates select from a pool of up to 32 signals that are selected using four data source selection multiplexers. Figure 17-1 shows an overview of the module. Figure 17-3 shows the details of the data source multiplexers and logic input gate connections.

REGISTER 18-1:

#### U-0 R/W-0 R/W-0 U-0 U-0 U-0 U-0 U-0 HLVDEN HLSIDL \_\_\_\_\_ \_\_\_\_ \_\_\_\_\_ \_\_\_\_\_ bit 15 bit 8 R/W-0 R/W-0 R/W-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0 VDIR BGVST **IRVST** HLVDL3 HLVDL2 HLVDL1 HLVDL0 bit 7 bit 0 Legend: R = Readable bit U = Unimplemented bit, read as '0' W = Writable bit -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15 HLVDEN: High/Low-Voltage Detect Power Enable bit 1 = HLVD is enabled 0 = HLVD is disabled bit 14 Unimplemented: Read as '0' bit 13 HLSIDL: HLVD Stop in Idle Mode bit 1 = Discontinues module operation when device enters Idle mode 0 = Continues module operation in Idle mode bit 12-8 Unimplemented: Read as '0' bit 7 VDIR: Voltage Change Direction Select bit 1 = Event occurs when voltage equals or exceeds trip point (HLVDL<3:0>) 0 = Event occurs when voltage equals or falls below trip point (HLVDL<3:0>) bit 6 BGVST: Band Gap Voltage Stable Flag bit 1 = Indicates that the band gap voltage is stable 0 = Indicates that the band gap voltage is unstable bit 5 **IRVST:** Internal Reference Voltage Stable Flag bit 1 = Indicates that the internal reference voltage is stable and the High-Voltage Detect logic generates the interrupt flag at the specified voltage range 0 = Indicates that the internal reference voltage is unstable and the High-Voltage Detect logic will not generate the interrupt flag at the specified voltage range, and the HLVD interrupt should not be enabled bit 4 Unimplemented: Read as '0' bit 3-0 HLVDL<3:0>: High/Low-Voltage Detection Limit bits 1111 = External analog input is used (input comes from the HLVDIN pin) 1110 = Trip Point 1<sup>(1)</sup> 1101 = Trip Point 2<sup>(1)</sup> 1100 = Trip Point 3<sup>(1)</sup> 0000 = Trip Point 15<sup>(1)</sup>

HLVDCON: HIGH/LOW-VOLTAGE DETECT CONTROL REGISTER

| R/W-0         | U-0                                                                                                                     | R/W-0                                | R/W-0          | U-0               | U-0              | U-0             | U-0     |  |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------------|-------------------|------------------|-----------------|---------|--|--|

| AMPEN         |                                                                                                                         | AMPSIDL                              | AMPSLP         |                   |                  |                 |         |  |  |

| bit 15        |                                                                                                                         |                                      | •              |                   |                  |                 | bit 8   |  |  |

|               |                                                                                                                         |                                      |                |                   |                  |                 |         |  |  |

| R/W-0         | U-0                                                                                                                     | R/W-0                                | R/W-0          | R/W-0             | R/W-0            | R/W-0           | R/W-0   |  |  |

| SPDSEL        | —                                                                                                                       | NINSEL2                              | NINSEL1        | NINSEL0           | PINSEL2          | PINSEL1         | PINSEL0 |  |  |

| bit 7         |                                                                                                                         |                                      |                |                   |                  |                 | bit 0   |  |  |

| Legend:       |                                                                                                                         |                                      |                |                   |                  |                 |         |  |  |

| R = Readabl   | e bit                                                                                                                   | W = Writable                         | bit            | U = Unimplen      | nented bit, read | 1 as '0'        |         |  |  |

| -n = Value at | POR                                                                                                                     | '1' = Bit is set                     |                | '0' = Bit is clea |                  | x = Bit is unkr | nown    |  |  |

|               |                                                                                                                         |                                      |                |                   |                  |                 | -       |  |  |

| bit 15        | AMPEN: Op                                                                                                               | Amp x Control                        | Module Enable  | e bit             |                  |                 |         |  |  |

|               | 1 = Module                                                                                                              |                                      |                |                   |                  |                 |         |  |  |

|               | 0 = Module                                                                                                              |                                      |                |                   |                  |                 |         |  |  |

| bit 14        | -                                                                                                                       | nted: Read as '                      |                |                   |                  |                 |         |  |  |

| bit 13        |                                                                                                                         | Dp Amp x Periph                      |                |                   |                  |                 |         |  |  |

|               |                                                                                                                         | nues module op<br>es module opera    |                |                   | le mode          |                 |         |  |  |

| bit 12        |                                                                                                                         | p Amp x Periph                       |                |                   | it               |                 |         |  |  |

|               |                                                                                                                         | es module opera                      |                | -                 |                  |                 |         |  |  |

|               |                                                                                                                         | nues module op                       |                |                   | pinouo           |                 |         |  |  |

| bit 11-8      | Unimpleme                                                                                                               | nted: Read as '                      | כי             |                   |                  |                 |         |  |  |

| bit 7         | SPDSEL: Op                                                                                                              | p Amp x Power/                       | Speed Select b | bit               |                  |                 |         |  |  |

|               | • •                                                                                                                     | ower and band                        | •              | • •               |                  |                 |         |  |  |

| bit 6         | -                                                                                                                       | ower and bandw                       | -              | sponse (me)       |                  |                 |         |  |  |

|               | -                                                                                                                       | nted: Read as '                      |                | oot hito          |                  |                 |         |  |  |

| bit 5-3       |                                                                                                                         | I>: Negative Op<br>rved; do not use  |                | ect bits          |                  |                 |         |  |  |

|               |                                                                                                                         | rved; do not use                     |                |                   |                  |                 |         |  |  |

|               |                                                                                                                         | np negative inpu                     |                | to the op amp     | output (voltage  | e follower)     |         |  |  |

|               |                                                                                                                         | rved; do not use                     |                |                   |                  |                 |         |  |  |

|               |                                                                                                                         | rved; do not use<br>np negative inpu |                | to the OAVING     | nin              |                 |         |  |  |

|               |                                                                                                                         | np negative inpl                     |                |                   |                  |                 |         |  |  |

|               |                                                                                                                         | np negative inpu                     |                |                   |                  |                 |         |  |  |

| bit 2-0       | PINSEL<2:0                                                                                                              | >: Positive Op /                     | Amp Input Sele | ect bits          |                  |                 |         |  |  |

|               | -                                                                                                                       | np positive inpu                     |                | to the output of  | the A/D input i  | multiplexer     |         |  |  |

|               | 110 = Reserved; do not use<br>101 = Op amp positive input is connected to the DAC1 output for OA1 (DAC2 output for OA2) |                                      |                |                   |                  |                 |         |  |  |

|               |                                                                                                                         | rved; do not use                     |                |                   |                  |                 | i (JAZ) |  |  |

|               |                                                                                                                         | rved; do not use                     |                |                   |                  |                 |         |  |  |

|               |                                                                                                                         | np positive inpu                     |                |                   |                  |                 |         |  |  |

|               | •                                                                                                                       | np positive inpu                     |                |                   | pin              |                 |         |  |  |

|               | 000 = Op an                                                                                                             | np positive inpu                     | i is connected | IU AVSS           |                  |                 |         |  |  |

| Note 1: The   | nis register is a                                                                                                       | vailable only on                     | PIC24F(V)16    | KM2XX devices     |                  |                 |         |  |  |

|               |                                                                                                                         |                                      |                |                   |                  |                 |         |  |  |

## REGISTER 21-1: AMPxCON: OP AMP x CONTROL REGISTER<sup>(1)</sup>

## REGISTER 23-1: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER

| U-0           | U-0                                                                                                                                                                    | U-0                                                                                                                                                  | U-0            | U-0               | U-0             | U-0             | U-0   |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------------|-----------------|-----------------|-------|--|

| _             | _                                                                                                                                                                      |                                                                                                                                                      | —              | _                 | —               | _               | _     |  |

| bit 15        |                                                                                                                                                                        |                                                                                                                                                      |                |                   |                 |                 | bit 8 |  |

|               |                                                                                                                                                                        |                                                                                                                                                      |                |                   |                 |                 |       |  |

| R/W-0         | R/W-0                                                                                                                                                                  | R/W-0                                                                                                                                                | R/W-0          | R/W-0             | R/W-0           | R/W-0           | R/W-0 |  |

| CVREN         | CVROE                                                                                                                                                                  | CVRSS                                                                                                                                                | CVR4           | CVR3              | CVR2            | CVR1            | CVR0  |  |

| bit 7         |                                                                                                                                                                        |                                                                                                                                                      |                |                   |                 |                 | bit ( |  |

| Legend:       |                                                                                                                                                                        |                                                                                                                                                      |                |                   |                 |                 |       |  |

| R = Readab    | le bit                                                                                                                                                                 | W = Writable                                                                                                                                         | bit            | U = Unimplem      | nented bit, rea | d as '0'        |       |  |

| -n = Value at | t POR                                                                                                                                                                  | '1' = Bit is set                                                                                                                                     |                | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |  |

| bit 7         | 1 = CVREF ci<br>0 = CVREF ci                                                                                                                                           | Unimplemented: Read as '0'<br>CVREN: Comparator Voltage Reference Enable bit<br>1 = CVREF circuit is powered on<br>0 = CVREF circuit is powered down |                |                   |                 |                 |       |  |

| bit 6         | 1 = CVREF VC                                                                                                                                                           | nparator VREF (<br>bltage level is o<br>bltage level is d                                                                                            | utput on the C |                   | oin             |                 |       |  |

| bit 5         | <b>CVRSS:</b> Comparator VREF Source Selection bit<br>1 = Comparator reference source, CVRSRC = VREF+ – VREF-<br>0 = Comparator reference source, CVRSRC = AVDD – AVSS |                                                                                                                                                      |                |                   |                 |                 |       |  |

| bit 4-0       | <u>When CVRSS</u><br>CVREF = (VRE<br><u>When CVRSS</u>                                                                                                                 | <u>S = 1:</u><br>:F-) + (CVR<4:(                                                                                                                     | )>/32) • (VREF | ,                 | :0> ≤ 31 bits   |                 |       |  |

## 27.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of the PIC24FV16KM204 family electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the PIC24FV16KM204 family are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these, or any other conditions above the parameters indicated in the operation listings of this specification, is not implied.

## Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias                                     | 40°C to +125°C       |

|--------------------------------------------------------------------|----------------------|

| Storage temperature                                                | 65°C to +150°C       |

| Voltage on VDD with respect to Vss (PIC24FXXKMXXX)                 | -0.3V to +4.5V       |

| Voltage on VDD with respect to Vss (PIC24FVXXKMXXX)                | -0.3V to +6.5V       |

| Voltage on any combined analog and digital pin with respect to Vss | 0.3V to (VDD + 0.3V) |

| Voltage on any digital only pin with respect to Vss                | 0.3V to (VDD + 0.3V) |

| Voltage on MCLR/VPP pin with respect to Vss                        | -0.3V to +9.0V       |

| Maximum current out of Vss pin                                     |                      |

| Maximum current into Vod pin <sup>(1)</sup>                        |                      |

| Maximum output current sunk by any I/O pin                         |                      |

| Maximum output current sourced by any I/O pin                      |                      |

| Maximum current sunk by all ports                                  |                      |

| Maximum current sourced by all ports <sup>(1)</sup>                | 200 mA               |

Note 1: Maximum allowable current is a function of device maximum power dissipation (see Table 27-1).

**†** Notice: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

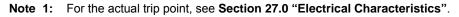

## TABLE 27-32: EXAMPLE SPI SLAVE MODE REQUIREMENTS (CKE = 1)

| Param<br>No. | Symbol                | Characteristic                                                                   | Min                      | Max           | Units | Conditions |          |

|--------------|-----------------------|----------------------------------------------------------------------------------|--------------------------|---------------|-------|------------|----------|

| 70           | TssL2scH,<br>TssL2scL | $\overline{\text{SSx}} \downarrow$ to SCKx $\downarrow$ or SCKx $\uparrow$ Input | 3 Тсү                    |               | ns    |            |          |

| 70A          | TssL2WB               | SSx to Write to SSPxBUF                                                          |                          | 3 TCY         | _     | ns         |          |

| 71           | TscH                  | SCKx Input High Time                                                             | Continuous               | 1.25 Tcy + 30 |       | ns         |          |

| 71A          |                       | (Slave mode)                                                                     | Single Byte              | 40            | _     | ns         | (Note 1) |

| 72           | TscL                  | SCKx Input Low Time                                                              | Continuous               | 1.25 Tcy + 30 | —     | ns         |          |

| 72A          |                       | (Slave mode)                                                                     | (Slave mode) Single Byte |               | _     | ns         | (Note 1) |

| 73A          | Тв2в                  | Last Clock Edge of Byte 1 to the First                                           | 1.5 Tcy + 40             | —             | ns    | (Note 2)   |          |

| 74           | TscH2DIL,<br>TscL2DIL | Hold Time of SDIx Data Input to SCKx Edge                                        |                          | 40            | _     | ns         |          |

| 75           | TDOR                  | SDOx Data Output Rise Time                                                       |                          |               | 25    | ns         |          |

| 76           | TDOF                  | SDOx Data Output Fall Time                                                       |                          |               | 25    | ns         |          |

| 77           | TssH2doZ              | SSx ↑ to SDOx Output High-Impeda                                                 | ance                     | 10            | 50    | ns         |          |

| 80           | TscH2doV,<br>TscL2doV | SDOx Data Output Valid After SCKx Edge                                           |                          | —             | 50    | ns         |          |

| 82           | TssL2DoV              | SDOx Data Output Valid After SSx                                                 | _                        | 50            | ns    |            |          |

| 83           | TscH2ssH,<br>TscL2ssH | SSx ↑ After SCKx Edge                                                            |                          | 1.5 Tcy + 40  | _     | ns         |          |

|              | Fsck                  | SCKx Frequency                                                                   |                          | —             | 10    | MHz        |          |

**Note 1:** Requires the use of Parameter 73A.

2: Only if Parameters 71A and 72A are used.

| AC CHARACTERISTICS |     |                                       | Standard Operating Conditions:<br>Operating temperature |                         |           | : 1.8V to 3.6V (PIC24F16KM204)<br>2.0V to 5.5V (PIC24FV16KM204)<br>$-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                                         |  |

|--------------------|-----|---------------------------------------|---------------------------------------------------------|-------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--|

| Param<br>No.       | Sym | Characteristic                        | Min.                                                    | Тур                     | Max.      | Units                                                                                                                                                                            | Comments                                |  |

|                    |     | Resolution                            | 8                                                       |                         | _         | bits                                                                                                                                                                             |                                         |  |

|                    |     | DACREF<1:0> Input Voltage<br>Range    | AVss + 1.8                                              | —                       | AVDD      | V                                                                                                                                                                                |                                         |  |

|                    |     | Differential Linearity Error<br>(DNL) | —                                                       | —                       | ±0.5      | LSb                                                                                                                                                                              |                                         |  |

|                    |     | Integral Linearity Error (INL)        | —                                                       | —                       | ±1.5      | LSb                                                                                                                                                                              |                                         |  |

|                    |     | Offset Error                          | —                                                       | —                       | ±0.5      | LSb                                                                                                                                                                              |                                         |  |

|                    |     | Gain Error                            | _                                                       | —                       | ±3.0      | LSb                                                                                                                                                                              |                                         |  |

|                    |     | Monotonicity                          | _                                                       | _                       | —         | _                                                                                                                                                                                | (Note 1)                                |  |

|                    |     | Output Voltage Range                  | AVss + 50                                               | AVss + 5 to<br>AVpp – 5 | AVDD - 50 | mV                                                                                                                                                                               | 0.5V input overdrive, no output loading |  |

|                    |     | Slew Rate                             | _                                                       | 5                       |           | V/µs                                                                                                                                                                             |                                         |  |

|                    |     | Settling Time                         | —                                                       | 10                      | —         | μs                                                                                                                                                                               |                                         |  |

## TABLE 27-39: 8-BIT DIGITAL-TO-ANALOG CONVERTER SPECIFICATIONS

Note 1: DAC output voltage never decreases with an increase in the data code.

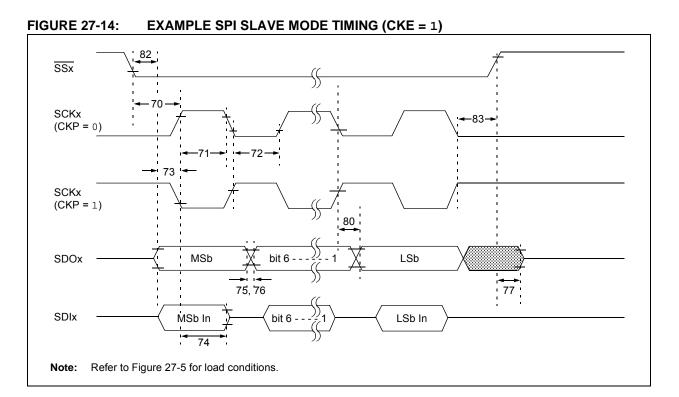

24FV16KM

204/MV® 1342M7W

XXXXXXXX

XXXXXXXX YYWWNNN

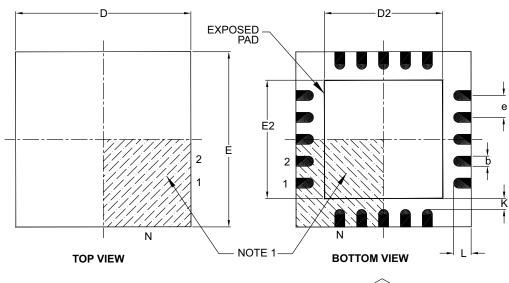

## 20-Lead Plastic Quad Flat, No Lead Package (ML) – 4x4x0.9 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units            |                | MILLIMETERS |      |  |

|------------------------|------------------|----------------|-------------|------|--|

| Dimensi                | Dimension Limits |                | NOM         | MAX  |  |

| Number of Pins         | Ν                |                | 20          |      |  |

| Pitch                  | е                |                | 0.50 BSC    |      |  |

| Overall Height         | Α                | 0.80           | 0.90        | 1.00 |  |

| Standoff               | A1               | 0.00 0.02 0.05 |             |      |  |

| Contact Thickness      | A3               | 0.20 REF       |             |      |  |

| Overall Width          | E                | 4.00 BSC       |             |      |  |

| Exposed Pad Width      | E2               | 2.60 2.70 2.80 |             |      |  |

| Overall Length         | D                | 4.00 BSC       |             |      |  |

| Exposed Pad Length     | D2               | 2.60 2.70 2.80 |             |      |  |

| Contact Width          | b                | 0.18 0.25 0.30 |             |      |  |

| Contact Length         | L                | 0.30 0.40 0.50 |             |      |  |

| Contact-to-Exposed Pad | К                | 0.20 – –       |             |      |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-126B

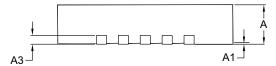

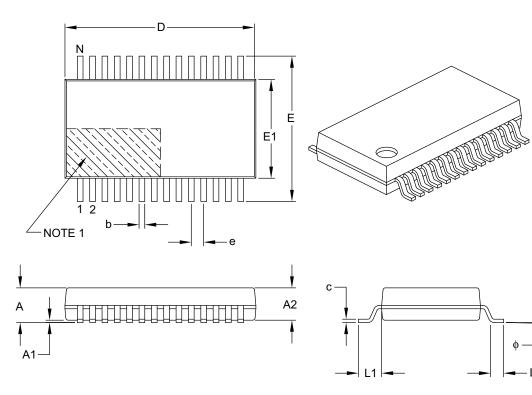

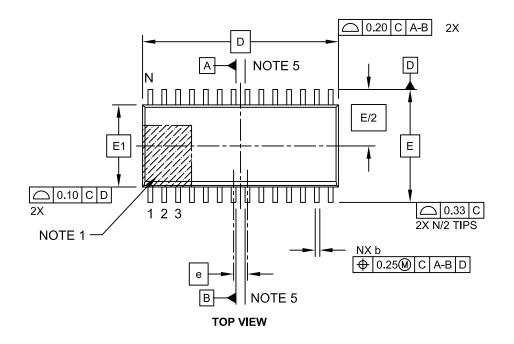

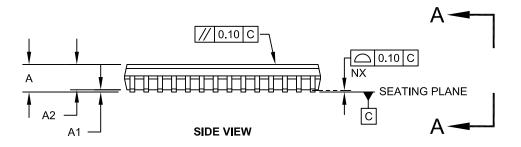

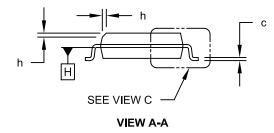

## 28-Lead Plastic Shrink Small Outline (SS) – 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            |             |          | 6     |

|--------------------------|------------------|-------------|----------|-------|

| Dimensi                  | Dimension Limits |             |          | MAX   |

| Number of Pins           | Ν                |             | 28       |       |

| Pitch                    | е                |             | 0.65 BSC |       |

| Overall Height           | Α                | -           | -        | 2.00  |

| Molded Package Thickness | A2               | 1.65        | 1.75     | 1.85  |

| Standoff                 | A1               | 0.05        | -        | _     |

| Overall Width            | E                | 7.40        | 7.80     | 8.20  |

| Molded Package Width     | E1               | 5.00        | 5.30     | 5.60  |

| Overall Length           | D                | 9.90        | 10.20    | 10.50 |

| Foot Length              | L                | 0.55        | 0.75     | 0.95  |

| Footprint                | L1               | _1 1.25 REF |          |       |

| Lead Thickness           | С                | 0.09        | -        | 0.25  |

| Foot Angle               | φ                | 0°          | 4°       | 8°    |

| Lead Width               | b                | 0.22        | _        | 0.38  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-073B

## 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-052C Sheet 1 of 2

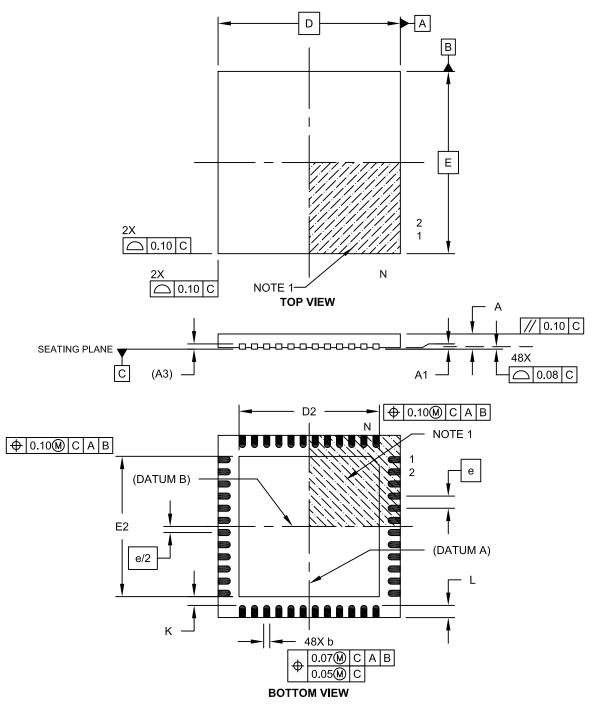

## 48-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) – 6x6x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-153A Sheet 1 of 2

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

## QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MTP, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

Analog-for-the-Digital Age, Application Maestro, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, SQI, Serial Quad I/O, Total Endurance, TSHARC, UniWinDriver, WiperLock, ZENA and Z-Scale are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

GestIC and ULPP are registered trademarks of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

$\ensuremath{\textcircled{\sc 0}}$  2013, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

ISBN: 978-1-62077-358-1

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELoQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mulfacture of development systems is ISO 9001:2000 certified.