Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 37                                                                            |

| Program Memory Size        | 8KB (2.75K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5V                                                                       |

| Data Converters            | A/D 22x10b/12b; D/A 2x8b                                                      |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 44-VQFN Exposed Pad                                                           |

| Supplier Device Package    | 44-QFN (8x8)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fv08km204-i-ml |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 1.0   | Device Overview                                             |       |

|-------|-------------------------------------------------------------|-------|

| 2.0   | Guidelines for Getting Started with 16-Bit Microcontrollers | 29    |

| 3.0   | CPU                                                         | 35    |

| 4.0   | Memory Organization                                         | 41    |

| 5.0   | Flash Program Memory                                        | 67    |

| 6.0   | Data EEPROM Memory                                          | 73    |

| 7.0   | Resets                                                      | 79    |

| 8.0   | Interrupt Controller                                        | 85    |

| 9.0   | Oscillator Configuration                                    | . 121 |

| 10.0  | Power-Saving Features                                       | . 131 |

| 11.0  | I/O Ports                                                   | . 137 |

| 12.0  | Timer1                                                      |       |

| 13.0  | Capture/Compare/PWM/Timer Modules (MCCP and SCCP)           | . 143 |

| 14.0  | Master Synchronous Serial Port (MSSP)                       |       |

| 15.0  | Universal Asynchronous Receiver Transmitter (UART)          | . 173 |

| 16.0  | Real-Time Clock and Calendar (RTCC)                         | . 181 |

| 17.0  | Configurable Logic Cell (CLC)                               | . 195 |

| 18.0  | High/Low-Voltage Detect (HLVD)                              | . 207 |

|       | 12-Bit A/D Converter with Threshold Detect                  |       |

| 20.0  | 8-Bit Digital-to-Analog Converter (DAC)                     | . 229 |

| 21.0  | Dual Operational Amplifier Module                           | . 233 |

| 22.0  | Comparator Module                                           |       |

| 23.0  | Comparator Voltage Reference                                | . 239 |

| 24.0  | Charge Time Measurement Unit (CTMU)                         | . 241 |

| 25.0  | Special Features                                            | . 249 |

| 26.0  | Development Support                                         | . 261 |

| 27.0  | Electrical Characteristics                                  | . 265 |

| 28.0  | Packaging Information                                       | . 297 |

| Appe  | ndix A: Revision History                                    | . 325 |

| Index | · · · · · · · · · · · · · · · · · · ·                       | 327   |

|       | /icrochip Web Site                                          |       |

| Custo | omer Change Notification Service                            | . 333 |

| Custo | omer Support                                                | . 333 |

| Produ | uct Identification System                                   | . 335 |

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

## Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

Microchip's Worldwide Web site; http://www.microchip.com

Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

#### TABLE 4-9: MCCP2 REGISTER MAP

| File Name | Addr. | Bit 15  | Bit 14                            | Bit 13               | Bit 12               | Bit 11               | Bit 10               | Bit 9                | Bit 8                | Bit 7        | Bit 6        | Bit 5   | Bit 4                 | Bit 3   | Bit 2   | Bit 1                  | Bit 0      | All<br>Resets |

|-----------|-------|---------|-----------------------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|--------------|--------------|---------|-----------------------|---------|---------|------------------------|------------|---------------|

| CCP2CON1L | 164h  | CCPON   | _                                 | CCPSIDL              | r                    | TMRSYNC              | CLKSEL2              | CLKSEL1              | CLKSEL0              | TMRPS1       | TMRPS0       | T32     | CCSEL                 | MOD3    | MOD2    | MOD1                   | MOD0       | 0000          |

| CCP2CON1H | 166h  | OPSSRC  | RTRGEN                            | _                    | _                    | IOPS3                | IOPS2                | IOPS1                | IOPS0                | TRIGEN       | ONESHOT      | ALTSYNC | SYNC4                 | SYNC3   | SYNC2   | SYNC1                  | SYNC0      | 0000          |

| CCP2CON2L | 168h  | PWMRSEN | ASDGM                             |                      | SSDG                 |                      |                      | _                    | _                    | ASDG7        | ASDG6        | ASDG5   | ASDG4                 | ASDG3   | ASDG2   | ASDG1                  | ASDG0      | 0000          |

| CCP2CON2H | 16Ah  | OENSYNC | -                                 | OCFEN <sup>(1)</sup> | OCEEN <sup>(1)</sup> | OCDEN <sup>(1)</sup> | OCCEN <sup>(1)</sup> | OCBEN <sup>(1)</sup> | OCAEN                | ICGSM1       | ICGSM0       | _       | AUXOUT1               | AUXOUT0 | ICSEL2  | ICSEL1                 | ICSEL0     | 0100          |

| CCP2CON3L | 16Ch  | _       | _                                 | _                    | _                    | _                    | _                    | _                    | _                    | _            |              | DT5     | DT4                   | DT3     | DT2     | DT1                    | DT0        | 0000          |

| CCP2CON3H | 16Eh  | OETRIG  | OSCNT2                            | OSCNT1               | OSCNT0               | _                    | OUTM2 <sup>(1)</sup> | OUTM1 <sup>(1)</sup> | OUTM0 <sup>(1)</sup> | _            | _            | POLACE  | POLBDF <sup>(1)</sup> | PSSACE1 | PSSACE0 | PSSBDF1 <sup>(1)</sup> | PSSBDF0(1) | 0000          |

| CCP2STATL | 170h  | _       | -                                 |                      | _                    |                      |                      | _                    | _                    | CCPTRIG      | TRSET        | TRCLR   | ASEVT                 | SCEVT   | ICDIS   | ICOV                   | ICBNE      | 0000          |

| CCP2TMRL  | 174h  |         |                                   |                      |                      |                      |                      | MCC                  | P2 Time Ba           | ase Register | r Low Word   |         |                       |         |         |                        |            | 0000          |

| CCP2TMRH  | 176h  |         |                                   |                      |                      |                      |                      | MCC                  | P2 Time Ba           | se Register  | High Word    |         |                       |         |         |                        |            | 0000          |

| CCP2PRL   | 178h  |         |                                   |                      |                      |                      |                      | MCCP2                | Time Base            | Period Regi  | ister Low Wo | rd      |                       |         |         |                        |            | FFFF          |

| CCP2PRH   | 17Ah  |         |                                   |                      |                      |                      |                      | MCCP2                | Time Base I          | Period Regi  | ster High Wo | rd      |                       |         |         |                        |            | FFFF          |

| CCP2RAL   | 17Ch  |         |                                   |                      |                      |                      |                      | 0                    | utput Comp           | oare 2 Data  | Word A       |         |                       |         |         |                        |            | 0000          |

| CCP2RBL   | 180h  |         | Output Compare 2 Data Word B 0000 |                      |                      |                      |                      |                      |                      |              |              | 0000    |                       |         |         |                        |            |               |

| CCP2BUFL  | 184h  |         |                                   |                      |                      |                      |                      | Input                | Capture 2            | Data Buffer  | Low Word     |         |                       |         |         |                        |            | 0000          |

| CCP2BUFH  | 186h  |         |                                   |                      |                      |                      |                      | Input                | Capture 2            | Data Buffer  | High Word    |         |                       |         |         |                        |            | 0000          |

PIC24FV16KM204 FAMILY

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

Note 1: These bits are available only on PIC24F(V)16KM2XX devices.

**REGISTER 7-1:**

RCON: RESET CONTROL REGISTER<sup>(1)</sup>

| R/W-0, H   | S R/W-0, HS                      | R/W-0                 | R/W-0                | U-0                  | U-0                                 | R/W-0             | R/W-0          |

|------------|----------------------------------|-----------------------|----------------------|----------------------|-------------------------------------|-------------------|----------------|

| TRAPR      |                                  | SBOREN                | RETEN <sup>(3)</sup> | _                    | _                                   | СМ                | PMSLP          |

| bit 15     |                                  |                       |                      |                      |                                     |                   | bit 8          |

|            |                                  |                       |                      |                      |                                     |                   |                |

| R/W-0, H   | S R/W-0, HS                      | R/W-0, HS             | R/W-0, HS            | R/W-0, HS            | R/W-0, HS                           | R/W-1, HS         | R/W-1, HS      |

| EXTR       | SWR                              | SWDTEN <sup>(2)</sup> | WDTO                 | SLEEP                | IDLE                                | BOR               | POR            |

| bit 7      |                                  |                       |                      |                      |                                     |                   | bit C          |

|            |                                  |                       |                      |                      |                                     |                   |                |

| Legend:    |                                  | HS = Hardwar          | e Settable bit       |                      |                                     |                   |                |

| R = Read   | able bit                         | W = Writable t        | pit                  | U = Unimplen         | nented bit, read                    | as '0'            |                |

| -n = Value | e at POR                         | '1' = Bit is set      |                      | '0' = Bit is cle     | ared                                | x = Bit is unkn   | own            |

|            |                                  |                       |                      |                      |                                     |                   |                |

| bit 15     | -                                | Reset Flag bit        |                      |                      |                                     |                   |                |

|            | •                                | onflict Reset has     |                      |                      |                                     |                   |                |

| 1.11.4.4   |                                  | onflict Reset has     |                      |                      | <b>E</b> 1                          |                   |                |

| bit 14     |                                  | gal Opcode or l       |                      |                      | r Flag bit<br>or Uninitialized V    | / register used   | aa an Addraaa  |

|            |                                  | aused a Reset         | on, an illegal a     |                      |                                     | v register used   | as an Address  |

|            |                                  | opcode or Unir        | nitialized W Re      | set has not oc       | curred                              |                   |                |

| bit 13     | SBOREN: So                       | oftware Enable/D      | Disable of BOF       | R bit                |                                     |                   |                |

|            | 1 = BOR is turned on in software |                       |                      |                      |                                     |                   |                |

|            |                                  | rned off in softw     |                      |                      |                                     |                   |                |

| bit 12     |                                  | ention Sleep Mo       |                      |                      |                                     |                   |                |

|            |                                  |                       |                      |                      | Regulator (RETR<br>ge Regulator (VF |                   |                |

| bit 11-10  | -                                | ted: Read as '0       |                      |                      |                                     |                   |                |

| bit 9      | -                                | ation Word Misr       |                      | lag bit              |                                     |                   |                |

|            | -                                | ration Word Mis       |                      | -                    |                                     |                   |                |

|            | 0 = A Configu                    | ration Word Mis       | match Reset          | has not occurre      | ed                                  |                   |                |

| bit 8      | PMSLP: Prog                      | gram Memory Po        | ower During S        | leep bit             |                                     |                   |                |

|            |                                  | memory bias vo        |                      |                      |                                     |                   |                |

|            | 0 = Program<br>Standby           |                       | oltage is pow        | vered down du        | iring Sleep and                     | the voltage re    | gulator enters |

| bit 7      | •                                | nal Reset (MCLF       | R) Pin hit           |                      |                                     |                   |                |

| bit i      |                                  | Clear (pin) Rese      |                      | d                    |                                     |                   |                |

|            |                                  | Clear (pin) Rese      |                      |                      |                                     |                   |                |

| bit 6      | SWR: Softwa                      | re reset (Instru      | uction) Flag bit     | t                    |                                     |                   |                |

|            |                                  | instruction has t     |                      |                      |                                     |                   |                |

|            |                                  | instruction has r     |                      |                      |                                     |                   |                |

| bit 5      |                                  | oftware Enable/[      | Disable of WD        | l bit <sup>(2)</sup> |                                     |                   |                |

|            | 1 = WDT is ei<br>0 = WDT is di   |                       |                      |                      |                                     |                   |                |

|            |                                  |                       |                      |                      | <b>-</b>                            |                   |                |

| Note 1:    | All of the Reset                 | •                     | be set or clear      | ed in software.      | Setting one of the                  | nese bits in soft | ware does not  |

| 2:         | If the FWDTEN                    |                       | tion bits are '1     | 1' (upprogram        | med) the WDT i                      | is alwavs enabl   | ed renardless  |

| <b>_</b> . | of the SWDTEN                    |                       |                      |                      |                                     | ie amayo chabi    |                |

| -          |                                  |                       |                      |                      |                                     |                   |                |

## 3: This is implemented on PIC24FV16KMXXX parts only; not used on PIC24F16KMXXX devices.

## REGISTER 8-10: IFS5: INTERRUPT FLAG STATUS REGISTER 5

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | _   | —   | _   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0, HS |

|-------|-----|-----|-----|-----|-----|-----|-----------|

| —     | —   | —   | _   | —   | _   | —   | ULPWUIF   |

| bit 7 |     |     |     |     |     |     | bit 0     |

| Legend:           | HS = Hardware Settable bit |                             |                    |

|-------------------|----------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-1 Unimplemented: Read as '0'

bit 0 ULPWUIF: Ultra Low-Power Wake-up Interrupt Flag Status bit

1 = Interrupt request has occurred

0 = Interrupt request has not occurred

### REGISTER 8-11: IFS6: INTERRUPT FLAG STATUS REGISTER 6

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0, HS | R/W-0, HS |

|-------|-----|-----|-----|-----|-----|-----------|-----------|

| —     | —   | —   | —   | —   | —   | CLC2IF    | CLC1IF    |

| bit 7 |     |     |     |     |     |           | bit 0     |

| Legend:           | HS = Hardware Settable bit |                             |                    |

|-------------------|----------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-2 Unimplemented: Read as '0'

bit 1 CLC2IF: Configurable Logic Cell 2 Interrupt Flag Status bit 1 = Interrupt request has occurred 0 = Interrupt request has not occurred

bit 0 CLC1IF: Configurable Logic Cell 1 Interrupt Flag Status bit

1 = Interrupt request has occurred

0 = Interrupt request has not occurred

| U-0                          | U-0                                      | U-0                                                                                                                                     | U-0                             | U-0              | R/W-1            | R/W-0           | R/W-0   |

|------------------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|------------------|------------------|-----------------|---------|

| _                            |                                          |                                                                                                                                         |                                 |                  | U2ERIP2          | U2ERIP1         | U2ERIP0 |

| oit 15                       |                                          |                                                                                                                                         | •                               |                  |                  | •               | bit 8   |

|                              |                                          |                                                                                                                                         |                                 |                  |                  |                 |         |

| U-0                          | R/W-1                                    | R/W-0                                                                                                                                   | R/W-0                           | U-0              | U-0              | U-0             | U-0     |

| —                            | U1ERIP2                                  | U1ERIP1                                                                                                                                 | U1ERIP0                         | —                | —                | —               | —       |

| bit 7                        |                                          |                                                                                                                                         |                                 |                  |                  |                 | bit 0   |

|                              |                                          |                                                                                                                                         |                                 |                  |                  |                 |         |

| Legend:                      |                                          |                                                                                                                                         |                                 |                  |                  |                 |         |

| R = Readab                   | ole bit                                  | W = Writable                                                                                                                            | bit                             | U = Unimpler     | mented bit, read | d as '0'        |         |

| -n = Value a                 | at POR                                   | '1' = Bit is set                                                                                                                        |                                 | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |

| bit 10-8<br>bit 7<br>bit 6-4 | <pre>111 = Interru </pre>                | >: UART2 Error<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>nted: Read as '<br>>: UART1 Error<br>pt is Priority 7 ( | highest priority<br>abled<br>o' | interrupt)       |                  |                 |         |

| bit 3-0                      | •<br>•<br>001 = Interru<br>000 = Interru | pt is Priority 1<br>pt is Priority 1<br>pt source is dis<br>nted: Read as '                                                             | abled                           | interrupt)       |                  |                 |         |

### REGISTER 8-30: IPC16: INTERRUPT PRIORITY CONTROL REGISTER 16

## 10.2.2 IDLE MODE

Idle mode includes these features:

- · The CPU will stop executing instructions.

- · The WDT is automatically cleared.

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 10.6 "Selective Peripheral Module Control").

- If the WDT or FSCM is enabled, the LPRC will also remain active.

The device will wake from Idle mode on any of these events:

- · Any interrupt that is individually enabled

- Any device Reset

- A WDT time-out

On wake-up from Idle, the clock is reapplied to the CPU and instruction execution begins immediately, starting with the instruction following the PWRSAV instruction or the first instruction in the ISR.

#### 10.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction will be held off until entry into Sleep or Idle mode has completed. The device will then wake-up from Sleep or Idle mode.

#### 10.2.3.1 Power-on Resets (PORs)

VDD voltage is monitored to produce PORs. When a true POR occurs, the entire device is reset.

## 10.3 Ultra Low-Power Wake-up

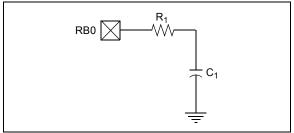

The Ultra Low-Power Wake-up (ULPWU) on pin, RB0, allows a slow falling voltage to generate an interrupt without excess current consumption.

To use this feature:

- 1. Charge the capacitor on RB0 by configuring the RB0 pin to an output and setting it to '1'.

- 2. Stop charging the capacitor by configuring RB0 as an input.

- 3. Discharge the capacitor by setting the ULPEN and ULPSINK bits in the ULPWCON register.

- 4. Configure Sleep mode.

- 5. Enter Sleep mode.

When the voltage on RB0 drops below VIL, the device wakes up and executes the next instruction.

This feature provides a low-power technique for periodically waking up the device from Sleep mode.

The time-out is dependent on the discharge time of the RC circuit on RB0.

When the ULPWU module wakes the device from Sleep mode, the ULPWUIF bit (IFS5<0>) is set. Software can check this bit upon wake-up to determine the wake-up source.

See Example 10-2 for initializing the ULPWU module.

### EXAMPLE 10-2: ULTRA LOW-POWER WAKE-UP INITIALIZATION

```

//*********

// 1. Charge the capacitor on RBO

TRISBbits.TRISB0 = 0;

LATBbits.LATB0 = 1;

for(i = 0; i < 10000; i++) Nop();</pre>

//2. Stop Charging the capacitor

on RBO

11

//*******************************

TRISBbits.TRISB0 = 1;

//3. Enable ULPWU Interrupt

IFS5bits.ULPWUIF = 0;

IEC5bits.ULPWUIE = 1;

IPC21bits.ULPWUIP = 0x7;

//*********************************

//4. Enable the Ultra Low Power

11

Wakeup module and allow

11

capacitor discharge

ULPWCONbits.ULPEN = 1;

ULPWCONbit.ULPSINK = 1;

//5. Enter Sleep Mode

11

Sleep();

//for sleep, execution will

//resume here

```

A series resistor, between RB0 and the external capacitor provides overcurrent protection for the AN2/ULPWU/RB0 pin and enables software calibration of the time-out (see Figure 10-1).

#### FIGURE 10-1: SERIES RESISTOR

A timer can be used to measure the charge time and discharge time of the capacitor. The charge time can then be adjusted to provide the desired delay in Sleep. This technique compensates for the affects of temperature, voltage and component accuracy. The peripheral can also be configured as a simple, programmable Low-Voltage Detect (LVD) or temperature sensor.

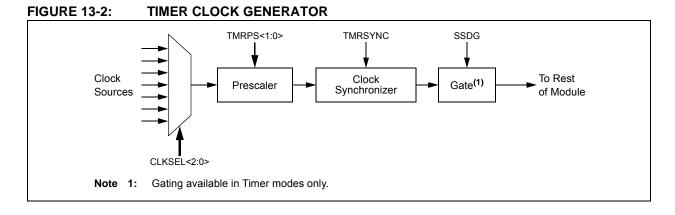

## 13.1 Time Base Generator

The Timer Clock Generator (TCG) generates a clock for the module's internal time base, using one of the clock signals already available on the microcontroller. This is used as the time reference for the module in its three major modes. The internal time base is shown in Figure 13-2.

There are eight inputs available to the clock generator, which are selected using the CLKSEL<2:0> bits (CCPxCON1L<10:8>). Available sources include the FRC and LPRC, the Secondary Oscillator, and the TCLKI External Clock inputs. The system clock is the default source (CLKSEL<2:0> = 000). On PIC24FV16KM204 family devices, clock sources to the MCCPx module must be synchronized with the system clock; as a result, when clock sources are selected, clock input timing restrictions or module operating restrictions may exist. Table 13-1 describes which time base sources are valid for the various operating modes.

#### TABLE 13-1: VALID TIMER OPTIONS FOR MCCPx/SCCPx MODES

| CLKSEL               | Tir                 | ner                  | Input   | Output  |

|----------------------|---------------------|----------------------|---------|---------|

| <2:0> <sup>(1)</sup> | Sync <sup>(2)</sup> | Async <sup>(3)</sup> | Capture | Compare |

| 111                  | Х                   | _                    | _       | _       |

| 110                  | Х                   |                      |         | —       |

| 101                  | Х                   | _                    | -       | —       |

| 011                  | Х                   | _                    | -       | —       |

| 010                  | Х                   |                      |         | —       |

| 001                  | Х                   | _                    | —       | _       |

| 000 <b>(4)</b>       | —                   | Х                    | Х       | Х       |

**Note 1:** See Register 13-1 for the description of the time base sources.

- 2: Synchronous Operation: TMRSYNC (CCPxCON1L<11>) = 1 and TRIGEN (CCPxCON1H<7>) = 0.

- Asynchronous Operation: (TMRSYNC = 0) or Triggered mode (TRIGEN = 1).

- 4: When CLKSEL<2:0> = 000, the TMRSYNC bit must be cleared.

DS30003030B-page 144

## 14.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on MSSP, refer to the "PIC24F Family Reference Manual".

The Master Synchronous Serial Port (MSSP) module is an 8-bit serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, Shift registers, display drivers, A/D Converters, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>)

- Full Master mode

- Slave mode (with general address call)

The SPI interface supports these modes in hardware:

- Master mode

- Slave mode

- · Daisy-Chaining Operation in Slave mode

- Synchronized Slave Operation

The I<sup>2</sup>C interface supports the following modes in hardware:

- Master mode

- · Multi-Master mode

- Slave mode with 10-Bit and 7-Bit Addressing and Address Masking

- Byte NACKing

- Selectable Address and Data Hold, and Interrupt Masking

## 14.1 I/O Pin Configuration for SPI

In SPI Master mode, the MSSP module will assert control over any pins associated with the SDOx and SCKx outputs. This does not automatically disable other digital functions associated with the pin and may result in the module driving the digital I/O port inputs. To prevent this, the MSSP module outputs must be disconnected from their output pins while the module is in SPI Master mode. While disabling the module temporarily may be an option, it may not be a practical solution in all applications.

The SDOx and SCKx outputs for the module can be selectively disabled by using the SDOxDIS and SCKxDIS bits in the PADCFG1 register (Register 14-10). Setting the bit disconnects the corresponding output for a particular module from its assigned pin.

## 15.2 Transmitting in 8-Bit Data Mode

- 1. Set up the UARTx:

- a) Write the appropriate values for data, parity and Stop bits.

- b) Write the appropriate baud rate value to the UxBRG register.

- c) Set up transmit and receive interrupt enable and priority bits.

- 2. Enable the UARTx.

- 3. Set the UTXEN bit (causes a transmit interrupt, two cycles after being set).

- 4. Write the data byte to the lower byte of the UxTXREG word. The value will be immediately transferred to the Transmit Shift Register (TSR) and the serial bit stream will start shifting out with the next rising edge of the baud clock.

- Alternately, the data byte may be transferred while UTXEN = 0, and then, the user may set UTXEN. This will cause the serial bit stream to begin immediately, because the baud clock will start from a cleared state.

- 6. A transmit interrupt will be generated as per interrupt control bit, UTXISELx.

## 15.3 Transmitting in 9-Bit Data Mode

- 1. Set up the UARTx (as described in **Section 15.2** "**Transmitting in 8-Bit Data Mode**").

- 2. Enable the UARTx.

- 3. Set the UTXEN bit (causes a transmit interrupt, two cycles after being set).

- 4. Write UxTXREG as a 16-bit value only.

- 5. A word write to UxTXREG triggers the transfer of the 9-bit data to the TSR. The serial bit stream will start shifting out with the first rising edge of the baud clock.

- 6. A transmit interrupt will be generated as per the setting of control bit, UTXISELx.

## 15.4 Break and Sync Transmit Sequence

The following sequence will send a message frame header, made up of a Break, followed by an Auto-Baud Sync byte.

- 1. Configure the UARTx for the desired mode.

- 2. Set UTXEN and UTXBRK this sets up the Break character.

- 3. Load the UxTXREG with a dummy character to initiate transmission (value is ignored).

- 4. Write '55h' to UxTXREG loads the Sync character into the transmit FIFO.

- 5. After the Break has been sent, the UTXBRK bit is reset by hardware. The Sync character now transmits.

## 15.5 Receiving in 8-Bit or 9-Bit Data Mode

- 1. Set up the UARTx (as described in Section 15.2 "Transmitting in 8-Bit Data Mode").

- 2. Enable the UARTx.

- 3. A receive interrupt will be generated when one or more data characters have been received, as per interrupt control bit, URXISELx.

- 4. Read the OERR bit to determine if an overrun error has occurred. The OERR bit must be reset in software.

- 5. Read UxRXREG.

The act of reading the UxRXREG character will move the next character to the top of the receive FIFO, including a new set of PERR and FERR values.

## 15.6 Operation of UxCTS and UxRTS Control Pins

UARTx Clear-To-Send (UxCTS) and Request-To-Send (UxRTS) are the two hardware controlled pins that are associated with the UARTx module. These two pins allow the UARTx to operate in Simplex and Flow Control modes. They are implemented to control the transmission and reception between the Data Terminal Equipment (DTE). The UEN<1:0> bits in the UxMODE register configure these pins.

## 15.7 Infrared Support

The UARTx module provides two types of infrared UARTx support: one is the IrDA clock output to support an external IrDA encoder and decoder device (legacy module support), and the other is the full implementation of the IrDA encoder and decoder.

As the IrDA modes require a 16x baud clock, they will only work when the BRGH bit (UxMODE<3>) is '0'.

#### 15.7.1 EXTERNAL IrDA SUPPORT – IrDA CLOCK OUTPUT

To support external IrDA encoder and decoder devices, the UxBCLK pin (same as the UxRTS pin) can be configured to generate the 16x baud clock. When UEN<1:0> = 11, the UxBCLK pin will output the 16x baud clock if the UARTx module is enabled; it can be used to support the IrDA codec chip.

## 15.7.2 BUILT-IN IrDA ENCODER AND DECODER

The UARTx has full implementation of the IrDA encoder and decoder as part of the UARTx module. The built-in IrDA encoder and decoder functionality is enabled using the IREN bit (UxMODE<12>). When enabled (IREN = 1), the receive pin (UxRX) acts as the input from the infrared receiver. The transmit pin (UxTX) acts as the output to the infrared transmitter.

## REGISTER 19-10: AD1CTMENH: CTMU ENABLE REGISTER (HIGH WORD)<sup>(1)</sup>

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0   | R/W-0   | R/W-0   | R/W-0                  | R/W-0                  | R/W-0   | R/W-0   | R/W-0   |

|---------|---------|---------|------------------------|------------------------|---------|---------|---------|

| CTMEN23 | CTMEN22 | CTMEN21 | CTMEN20 <sup>(2)</sup> | CTMEN19 <sup>(2)</sup> | CTMEN18 | CTMEN17 | CTMEN16 |

| bit 7   |         |         |                        |                        |         |         | bit 0   |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'.

bit 7-0 CTMEN<23:16>: CTMU Enabled During Conversion bits<sup>(2)</sup> 1 = CTMU is enabled and connected to the selected channel during conversion 0 = CTMU is not connected to this channel

- **Note 1:** Unimplemented channels are read as '0'.

- **2:** The CTMEN<20:19> bits are not implemented in 20-pin devices.

## REGISTER 19-11: AD1CTMENL: CTMU ENABLE REGISTER (LOW WORD)<sup>(1)</sup>

| R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0                   |

|---------|---------|---------|---------|---------|---------|--------|-------------------------|

| CTMEN15 | CTMEN14 | CTMEN13 | CTMEN12 | CTMEN11 | CTMEN10 | CTMEN9 | CTMEN8 <sup>(2,3)</sup> |

| bit 15  |         |         |         |         |         |        | bit 8                   |

| R/W-0                   | R/W-0                   | R/W-0                 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------------------------|-------------------------|-----------------------|--------|--------|--------|--------|--------|

| CTMEN7 <sup>(2,3)</sup> | CTMEN6 <sup>(2,3)</sup> | CTMEN5 <sup>(2)</sup> | CTMEN4 | CTMEN3 | CTMEN2 | CTMEN1 | CTMEN0 |

| bit 7                   |                         |                       |        |        |        |        | bit 0  |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-0 CTMEN<15:0>: CTMU Enabled During Conversion bits<sup>(2,3)</sup>

1 = CTMU is enabled and connected to the selected channel during conversion

0 = CTMU is not connected to this channel

- Note 1: Unimplemented channels are read as '0'.

- 2: The CTMEN<8:5> bits are not implemented in 20-pin devices.

- **3:** The CTMEN<8:6> bits are not implemented in 28-pin devices.

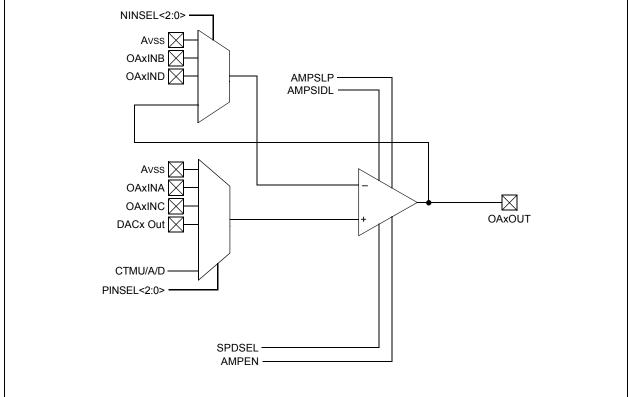

## 21.0 DUAL OPERATIONAL AMPLIFIER MODULE

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the *"PIC24F Family Reference Manual"*, *"Operational Amplifier (Op Amp)"* (DS30505). Device-specific information in this data sheet supersedes the information in the *"PIC24F Family Reference Manual"*.

PIC24FV16KM204 family devices include two operational amplifiers to complement the microcontroller's other analog features. They may be used to provide analog signal conditioning, either as stand-alone devices or in addition to other analog peripherals. The two op amps are functionally identical; the block diagram for a single amplifier is shown in Figure 21-1. Each op amp has these features:

- · Internal unity-gain buffer option

- Multiple input options each on the inverting and non-inverting amplifier inputs

- · Rail-to-rail input and output capabilities

- User-selectable option for regular or low-power operation

- User-selectable operation in Idle and Sleep modes

When using the op amps, it is recommended to set the ANSx and TRISx bits of both the input and output pins to configure them as analog pins. See **Section 11.2 "Configuring Analog Port Pins"** for more information.

### REGISTER 24-1: CTMUCON1L: CTMU CONTROL 1 LOW REGISTER (CONTINUED)

- bit 1-0 IRNG<1:0>: Current Source Range Select bits

- 11 = 100 × Base Current

- 10 = 10 × Base Current

- 01 = Base Current Level (0.55 μA nominal)

- 00 = 1000 × Base Current

## 27.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of the PIC24FV16KM204 family electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the PIC24FV16KM204 family are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these, or any other conditions above the parameters indicated in the operation listings of this specification, is not implied.

## Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias                                     | 40°C to +125°C       |

|--------------------------------------------------------------------|----------------------|

| Storage temperature                                                | 65°C to +150°C       |

| Voltage on VDD with respect to Vss (PIC24FXXKMXXX)                 | -0.3V to +4.5V       |

| Voltage on VDD with respect to Vss (PIC24FVXXKMXXX)                | -0.3V to +6.5V       |

| Voltage on any combined analog and digital pin with respect to Vss | 0.3V to (VDD + 0.3V) |

| Voltage on any digital only pin with respect to Vss                | 0.3V to (VDD + 0.3V) |

| Voltage on MCLR/VPP pin with respect to Vss                        | -0.3V to +9.0V       |

| Maximum current out of Vss pin                                     |                      |

| Maximum current into Vod pin <sup>(1)</sup>                        | 250 mA               |

| Maximum output current sunk by any I/O pin                         |                      |

| Maximum output current sourced by any I/O pin                      |                      |

| Maximum current sunk by all ports                                  |                      |

| Maximum current sourced by all ports <sup>(1)</sup>                | 200 mA               |

Note 1: Maximum allowable current is a function of device maximum power dissipation (see Table 27-1).

**†** Notice: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

## TABLE 27-4: HIGH/LOW-VOLTAGE DETECT CHARACTERISTICS

|              | Standard Operating Conditions: 1.8V to 3.6V (PIC24F16KM204)<br>2.0V to 5.5V (PIC24FV16KM204)<br>-40°C $\leq$ TA $\leq$ +85°C for Industrial<br>-40°C $\leq$ TA $\leq$ +125°C for Extended |                 |                                  |      |     |      |       |            |  |  |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------------------------|------|-----|------|-------|------------|--|--|

| Param<br>No. | Symbol                                                                                                                                                                                    | Chara           | octeristic                       | Min  | Тур | Max  | Units | Conditions |  |  |

| DC18         | Vhlvd                                                                                                                                                                                     | HLVD Voltage on | HLVDL<3:0> = 0000 <sup>(2)</sup> | _    | _   | 1.90 | V     |            |  |  |

|              |                                                                                                                                                                                           | VDD Transition  | HLVDL<3:0> = 0001                | 1.88 | —   | 2.13 | V     |            |  |  |

|              |                                                                                                                                                                                           |                 | HLVDL<3:0> = 0010                | 2.09 | —   | 2.35 | V     |            |  |  |

|              |                                                                                                                                                                                           |                 | HLVDL<3:0> = 0011                | 2.25 | —   | 2.53 | V     |            |  |  |

|              |                                                                                                                                                                                           |                 | HLVDL<3:0> = 0100                | 2.35 | —   | 2.62 | V     |            |  |  |

|              |                                                                                                                                                                                           |                 | HLVDL<3:0> = 0101                | 2.55 | —   | 2.84 | V     |            |  |  |

|              |                                                                                                                                                                                           |                 | HLVDL<3:0> = 0110                | 2.80 | —   | 3.10 | V     |            |  |  |

|              |                                                                                                                                                                                           |                 | HLVDL<3:0> = 0111                | 2.95 | _   | 3.25 | V     |            |  |  |

|              |                                                                                                                                                                                           |                 | HLVDL<3:0> = 1000                | 3.09 | —   | 3.41 | V     |            |  |  |

|              |                                                                                                                                                                                           |                 | HLVDL<3:0> = 1001                | 3.27 | —   | 3.59 | V     |            |  |  |

|              |                                                                                                                                                                                           |                 | HLVDL<3:0> = 1010 <sup>(1)</sup> | 3.46 | _   | 3.79 | V     |            |  |  |

|              |                                                                                                                                                                                           |                 | HLVDL<3:0> = 1011 <sup>(1)</sup> | 3.62 | _   | 4.01 | V     |            |  |  |

|              |                                                                                                                                                                                           |                 | HLVDL<3:0> = 1100 <sup>(1)</sup> | 3.91 | —   | 4.26 | V     |            |  |  |

|              |                                                                                                                                                                                           |                 | HLVDL<3:0> = 1101 <sup>(1)</sup> | 4.18 |     | 4.55 | V     |            |  |  |

|              |                                                                                                                                                                                           |                 | HLVDL<3:0> = 1110 <sup>(1)</sup> | 4.49 |     | 4.87 | V     |            |  |  |

Note 1: These trip points should not be used on PIC24FXXKMXXX devices.

2: This trip point should not be used on PIC24FVXXKMXXX devices.

## TABLE 27-5:BOR TRIP POINTS

| Standard Operating Conditions: 1.8V to 3.6V (PIC24F16KM204)2.0V to 5.5V (PIC24FV16KM204)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                |                    |                |      |      |      |       |                          |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------------|----------------|------|------|------|-------|--------------------------|--|--|

| Param<br>No.                                                                                                                                                                                                             | Sym            | Characte           | eristic        | Min  | Тур  | Max  | Units | Conditions               |  |  |

| DC15                                                                                                                                                                                                                     |                | BOR Hysteresis     |                | _    | 5    | _    | mV    |                          |  |  |

| DC19                                                                                                                                                                                                                     |                | BOR Voltage on VDD | BORV<1:0> = 00 | —    | _    | _    | —     | Valid for LPBOR (Note 1) |  |  |

|                                                                                                                                                                                                                          |                | Transition         | BORV<1:0> = 01 | 2.90 | 3    | 3.38 | V     |                          |  |  |

|                                                                                                                                                                                                                          |                |                    | BORV<1:0> = 10 | 2.53 | 2.7  | 3.07 | V     |                          |  |  |

|                                                                                                                                                                                                                          |                | BORV<1:0> = 11     |                | 1.75 | 1.85 | 2.05 | V     | (Note 2)                 |  |  |

|                                                                                                                                                                                                                          | BORV<1:0> = 11 |                    |                | 1.95 | 2.05 | 2.16 | V     | (Note 3)                 |  |  |

Note 1: LPBOR re-arms the POR circuit but does not cause a BOR.

2: This is valid for PIC24F (3.3V) devices.

3: This is valid for PIC24FV (5V) devices.

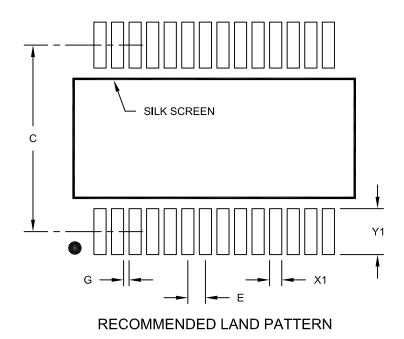

28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            |            |      |      |  |  |

|--------------------------|------------------|------------|------|------|--|--|

| Dimensio                 | Dimension Limits |            |      | MAX  |  |  |

| Contact Pitch            | E                | E 0.65 BSC |      |      |  |  |

| Contact Pad Spacing      | С                |            | 7.20 |      |  |  |

| Contact Pad Width (X28)  | X1               |            |      | 0.45 |  |  |

| Contact Pad Length (X28) | Y1               |            |      | 1.75 |  |  |

| Distance Between Pads    | G                | 0.20       |      |      |  |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2073A

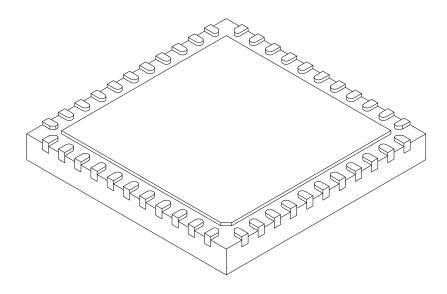

## 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | Units |          |          |      |  |

|-------------------------|-------|----------|----------|------|--|

| Dimension               | MIN   | NOM      | MAX      |      |  |

| Number of Pins          | Ν     |          | 44       |      |  |

| Pitch                   | е     |          | 0.65 BSC |      |  |

| Overall Height          | А     | 0.80     | 0.90     | 1.00 |  |

| Standoff                | A1    | 0.00     | 0.02     | 0.05 |  |

| Terminal Thickness      | A3    | 0.20 REF |          |      |  |

| Overall Width           | Е     |          | 8.00 BSC |      |  |

| Exposed Pad Width       | E2    | 6.25     | 6.45     | 6.60 |  |

| Overall Length          | D     |          | 8.00 BSC |      |  |

| Exposed Pad Length      | D2    | 6.25     | 6.45     | 6.60 |  |

| Terminal Width          | b     | 0.20     | 0.30     | 0.35 |  |

| Terminal Length         | L     | 0.30     | 0.40     | 0.50 |  |

| Terminal-to-Exposed-Pad | K     | 0.20     | -        | -    |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated

- 3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension. usually without tolerance. for information purposes only.

Microchip Technology Drawing C04-103C Sheet 2 of 2

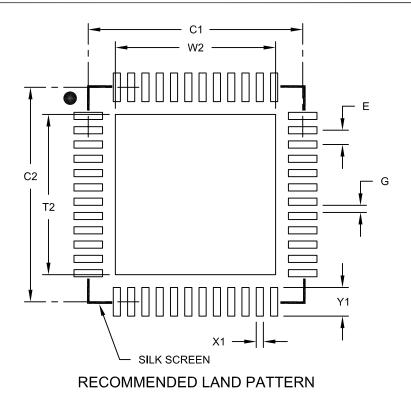

48-Lead Ultra Thin Plastic Quad Flat, No Lead Package (MV) - 6x6 mm Body [UQFN] With 0.40 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units    |          |      |      |  |

|----------------------------|----------|----------|------|------|--|

| Dimensior                  | n Limits | MIN      | NOM  | MAX  |  |

| Contact Pitch              | E        | 0.40 BSC |      |      |  |

| Optional Center Pad Width  | W2       |          |      | 4.45 |  |

| Optional Center Pad Length | T2       |          |      | 4.45 |  |

| Contact Pad Spacing        | C1       |          | 6.00 |      |  |

| Contact Pad Spacing        | C2       |          | 6.00 |      |  |

| Contact Pad Width (X28)    | X1       |          |      | 0.20 |  |

| Contact Pad Length (X28)   |          |          | 0.80 |      |  |

| Distance Between Pads      | 0.20     |          |      |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2153A

NOTES:

## **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| Product Group<br>Pin Count<br>Tape and Reel Fl |                                                                                                                                    | <ul> <li>Examples:</li> <li>a) PIC24FV16KM204-I/ML: Wide Voltage Range,<br/>General Purpose, 16-Kbyte Program Memory,<br/>44-Pin, Industrial Temp., QFN Package</li> <li>b) PIC24F08KM102-I/SS: Standard Voltage Range,<br/>General Purpose with Reduced Feature Set,<br/>8-Kbyte Program Memory, 28-Pin, Industrial<br/>Temp., SSOP Package</li> </ul> |

|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Architecture                                   | 24 = 16-bit modified Harvard without DSP                                                                                           |                                                                                                                                                                                                                                                                                                                                                         |

| Flash Memory Family                            | <ul><li>F = Standard voltage range Flash program memory</li><li>FV = Wide voltage range Flash program memory</li></ul>             |                                                                                                                                                                                                                                                                                                                                                         |

| Product Group                                  | KM2 = General Purpose PIC24F Lite Microcontroller<br>KM1 = General Purpose PIC24F Lite Microcontroller with<br>Reduced Feature Set |                                                                                                                                                                                                                                                                                                                                                         |

| Pin Count                                      | 01 = 20-pin<br>02 = 28-pin<br>04 = 44-pin                                                                                          |                                                                                                                                                                                                                                                                                                                                                         |

| Temperature Range                              | I = $-40^{\circ}$ C to $+85^{\circ}$ C (Industrial)<br>E = $-40^{\circ}$ C to $+125^{\circ}$ C (Extended)                          |                                                                                                                                                                                                                                                                                                                                                         |

| Package                                        | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                               |                                                                                                                                                                                                                                                                                                                                                         |

| Pattern                                        | Three-digit QTP, SQTP, Code or Special Requirements<br>(blank otherwise)<br>ES = Engineering Sample                                |                                                                                                                                                                                                                                                                                                                                                         |