Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                      |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 37                                                                            |

| Program Memory Size        | 8KB (2.75K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5V                                                                       |

| Data Converters            | A/D 22x10b/12b; D/A 2x8b                                                      |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 48-UFQFN Exposed Pad                                                          |

| Supplier Device Package    | 48-UQFN (6x6)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fv08km204-i-mv |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Pin Diagrams (Continued)**

|          | 28-Pin QFN <sup>(1)</sup>                                                            | 22<br>21 RB13<br>20 RB12                         |

|----------|--------------------------------------------------------------------------------------|--------------------------------------------------|

|          | RB3 4<br>Vss 5<br>RA2 6<br>RA3 7<br><u>8 9 10 11 12 <b>13</b> 1</u>                  | 18 RB10<br>17 RA6 or VDDcore<br>16 RA7<br>15 RB9 |

|          | R 85<br>R 85<br>R 85<br>R 82<br>R 82<br>R 82<br>R 82<br>R 82<br>R 82<br>R 82<br>R 82 | 5<br>0<br>2<br>2                                 |

| Pin      | Pin Features                                                                         | Pin Features                                     |

|          | PIC24FXXKMX02                                                                        | PIC24FVXXKMX02                                   |

| 1        | PGED1/AN2/CTCMP/ULPWU/C1IND/ / / /CN4/I                                              | RB0                                              |

| 2        | PGEC1/ / /AN3/C1INC/ / /CTED12/CN                                                    | I5/RB1                                           |

| 3        | / /AN4/C1INB/ / /U1RX/TCKIB/CTED1                                                    | 13/CN6/RB2                                       |

| 4        | /AN5/C1INA/ / /CN7/RB3                                                               |                                                  |

| 5        | Vss                                                                                  |                                                  |

| 6        | OSCI/CLKI/AN13/CN30/RA2                                                              |                                                  |

| 7        | OSCO/CLKO/AN14/CN29/RA3                                                              |                                                  |

| 8        | SOSCI/AN15/ / /CN1/RB4                                                               |                                                  |

| 9        | SOSCO/SCLKI/AN16/PWRLCLK/ /CN0/RA4                                                   |                                                  |

| 10       |                                                                                      |                                                  |

| 11       | PGED3/AN17/ASDA1/ / /OC1E/CLCINA/CN27/RB5                                            |                                                  |

| 12       | PGEC3/AN18/ASCL1/ / /OC1F/CLCINB/CN24/RB6<br>AN19/U1TX/INT0/CN23/RB7                 | AN19/U1TX/ /OC1A/INT0/CN23/RB7                   |

| 13<br>14 | AN19/0112/IN10/CN23/RB7<br>AN20/SCL1/U1CTS/C3OUT/OC1B/CTED10/CN22/RB8                | AN 19/011X/ /OCTA/IN10/CN23/RB7                  |

| 14       | AN21/SDA1/T1CK/U1RTS/U1BCLK/IC2/ /CLC10/CTED4/CN                                     | 121/PB0                                          |

| 16       | /IC1/ / /CTED3/CN9/RA7                                                               | vz //KD9                                         |

| 17       | /OC1A/CTED1/INT2/CN8/RA6                                                             | VDDCORE/VCAP                                     |

| 18       | PGED2/SDI1/ /OC1C/CTED11/CN16/RB10                                                   |                                                  |

| 19       | PGEC2/SCK1/OC2A/CTED9/CN15/RB11                                                      | <u></u>                                          |

| 20       | /AN12/HLVDIN/ / / /CTED2/CN14/RB12                                                   | /AN12/HLVDIN/SS2/ / /CTED2/INT2/CN14/RB12        |

| 21       | / /AN11/SDO1/OCFB/OC3B/OC1D/CTPLS/CN13                                               | 3/RB13                                           |

| 22       | /CVREF/ / /AN10/ / /C1OUT                                                            | OCFA/CTED5/INT1/CN12/RB14                        |

| 23       | / /AN9/ /REFO/SS1/TCKIA/CTED6/CN                                                     | I11/RB15                                         |

| 24       | Vss                                                                                  |                                                  |

| 25       | Vdd                                                                                  |                                                  |

| 26       | MCLR/Vpp/RA5                                                                         |                                                  |

|          | CVREF+/VREF+/ /AN0/ /CN2/RA0                                                         | CVREF+/VREF+/ /AN0/ /CTED1/CN2/RA0               |

| 27       |                                                                                      |                                                  |

Legend:Values inindicate pin function differences between PIC24F(V)XXKM202 and PIC24F(V)XXKM102 devices.Note 1:Exposed pad on underside of device is connected to Vss.

| TABLE 1-1: | DEVICE FEATURES FOR THE PIC24F16KM204 FAMILY |

|------------|----------------------------------------------|

|------------|----------------------------------------------|

| TABLE 1-1: DEVICE FEATURES FO                    | R THE PIC24F16                                                                                                                                 |                    | •                      |                       |  |  |

|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------------------------|-----------------------|--|--|

| Features                                         | PIC24F16KM204                                                                                                                                  | PIC24F08KM204      | PIC24F16KM202          | PIC24F08KM202         |  |  |

| Operating Frequency                              |                                                                                                                                                | DC-3               | 2 MHz                  |                       |  |  |

| Program Memory (bytes)                           | 16K                                                                                                                                            | 8K                 | 16K                    | 8K                    |  |  |

| Program Memory (instructions)                    | 5632                                                                                                                                           | 2816               | 5632                   | 2816                  |  |  |

| Data Memory (bytes)                              |                                                                                                                                                | 20                 | )48                    |                       |  |  |

| Data EEPROM Memory (bytes)                       |                                                                                                                                                | 5                  | 12                     |                       |  |  |

| Interrupt Sources (soft vectors/NMI traps)       |                                                                                                                                                | 40 (               | 36/4)                  |                       |  |  |

| Voltage Range                                    |                                                                                                                                                | 1.8-               | 3.6V                   |                       |  |  |

| I/O Ports                                        | PORTA<<br>PORTB<<br>PORTC                                                                                                                      | :15:0>             | -                      | RTA<7:0><br>RTB<15:0> |  |  |

| Total I/O Pins                                   | 38                                                                                                                                             |                    |                        | 24                    |  |  |

| Timers                                           | (One 16-bit timer, f                                                                                                                           |                    | I1<br>Ps with up to tv | vo 16/32 timers each) |  |  |

| Capture/Compare/PWM modules<br>MCCP<br>SCCP      |                                                                                                                                                |                    | 3<br>2                 |                       |  |  |

| Serial Communications<br>MSSP<br>UART            |                                                                                                                                                |                    | 2<br>2                 |                       |  |  |

| Input Change Notification Interrupt              | 37 23                                                                                                                                          |                    |                        |                       |  |  |

| 12-Bit Analog-to-Digital Module (input channels) | 22                                                                                                                                             | 22                 | 19                     | 19                    |  |  |

| Analog Comparators                               | 3                                                                                                                                              |                    |                        |                       |  |  |

| 8-Bit Digital-to-Analog Converters               |                                                                                                                                                |                    | 2                      |                       |  |  |

| Operational Amplifiers                           | 2                                                                                                                                              |                    |                        |                       |  |  |

| Charge Time Measurement Unit (CTMU)              | Yes                                                                                                                                            |                    |                        |                       |  |  |

| Real-Time Clock and Calendar (RTCC)              | Yes                                                                                                                                            |                    |                        |                       |  |  |

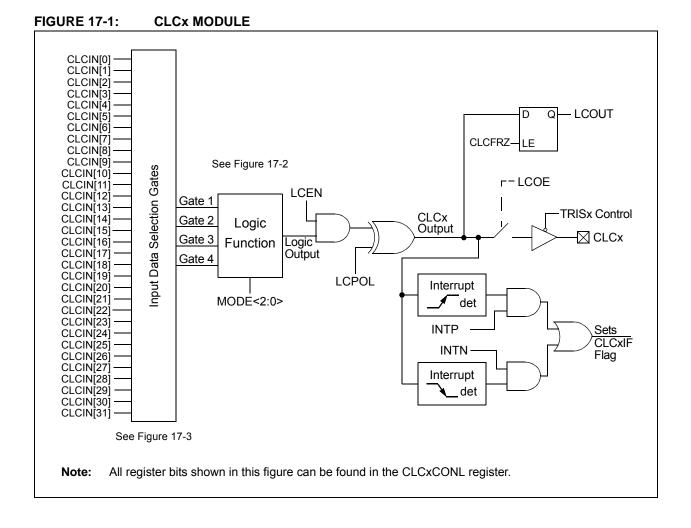

| Configurable Logic Cell (CLC)                    |                                                                                                                                                |                    | 2                      |                       |  |  |

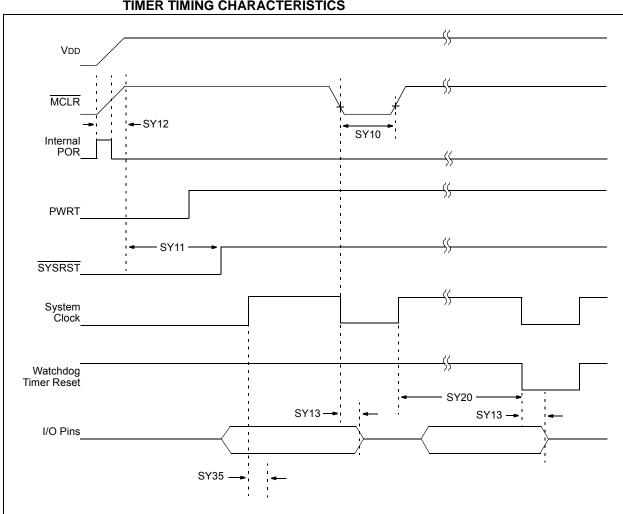

| Resets (and delays)                              | POR, BOR, RESET Instruction, MCLR, WDT, Illegal Opcode<br>REPEAT Instruction, Hardware Traps, Configuration Word Mism<br>(PWRT, OST, PLL Lock) |                    |                        |                       |  |  |

| Instruction Set                                  | 76 Base Inst                                                                                                                                   | ructions, Multiple | e Addressing N         | lode Variations       |  |  |

| Packages                                         | 44-Pin QFN/TQFP,         28-Pin           48-Pin UQFN         SPDIP/SSOP/SOIC/QFN                                                              |                    |                        |                       |  |  |

#### TABLE 1-5: PIC24FV16KM204 FAMILY PINOUT DESCRIPTION (CONTINUED)

|          |                                  |                                  | F             |                        |                |                                  |                                  | FV            |                        |                |     |        |                                                |

|----------|----------------------------------|----------------------------------|---------------|------------------------|----------------|----------------------------------|----------------------------------|---------------|------------------------|----------------|-----|--------|------------------------------------------------|

|          |                                  | Pin Number                       |               |                        |                |                                  | I                                | Pin Numb      | er                     |                |     |        |                                                |

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | I/O | Buffer | Description                                    |

| MCLR     | 1                                | 1                                | 26            | 18                     | 19             | 1                                | 1                                | 26            | 18                     | 19             | Ι   | ST     | Master Clear (Device Reset) Input (active-low) |

| OA1INA   | _                                | 5                                | 2             | 22                     | 24             |                                  | 5                                | 2             | 22                     | 24             | Ι   | ANA    | Op Amp 1 Input A                               |

| OA1INB   | _                                | 6                                | 3             | 23                     | 25             | _                                | 6                                | 3             | 23                     | 25             | I   | ANA    | Op Amp 1 Input B                               |

| OA1INC   | _                                | 24                               | 21            | 11                     | 12             | _                                | 24                               | 21            | 11                     | 12             | I   | ANA    | Op Amp 1 Input C                               |

| OA1IND   | _                                | 25                               | 22            | 14                     | 15             | _                                | 25                               | 22            | 14                     | 15             | I   | ANA    | Op Amp 1 Input D                               |

| OA1OUT   | _                                | 7                                | 4             | 24                     | 26             | _                                | 7                                | 4             | 24                     | 26             | 0   | ANA    | Op Amp 1 Analog Output                         |

| OA2INA   | _                                | 5                                | 2             | 22                     | 24             | _                                | 5                                | 2             | 22                     | 24             | I   | ANA    | Op Amp 2 Input A                               |

| OA2INB   | _                                | 6                                | 3             | 23                     | 25             | _                                | 6                                | 3             | 23                     | 25             | I   | ANA    | Op Amp 2 Input B                               |

| OA2INC   | _                                | 24                               | 21            | 11                     | 12             | _                                | 24                               | 21            | 11                     | 12             | I   | ANA    | Op Amp 2 Input C                               |

| OA2IND   | _                                | 25                               | 22            | 14                     | 15             | _                                | 25                               | 22            | 14                     | 15             | I   | ANA    | Op Amp 2 Input D                               |

| OA2OUT   | _                                | 26                               | 23            | 15                     | 16             | _                                | 26                               | 23            | 15                     | 16             | 0   | ANA    | Op Amp 2 Analog Output                         |

| OC1A     | 14                               | 20                               | 17            | 7                      | 7              | 11                               | 16                               | 13            | 43                     | 47             | 0   | _      | MCCP1 Output Compare A                         |

| OC1B     | 12                               | 17                               | 14            | 44                     | 48             | 12                               | 17                               | 14            | 44                     | 48             | 0   | _      | MCCP1 Output Compare B                         |

| OC1C     | 15                               | 21                               | 18            | 8                      | 9              | 15                               | 21                               | 18            | 8                      | 9              | 0   | _      | MCCP1 Output Compare C                         |

| OC1D     | 16                               | 24                               | 21            | 11                     | 12             | 16                               | 24                               | 21            | 11                     | 12             | 0   |        | MCCP1 Output Compare D                         |

| OC1E     | _                                | 14                               | 11            | 41                     | 45             | _                                | 14                               | 11            | 41                     | 45             | 0   | _      | MCCP1 Output Compare E                         |

| OC1F     | _                                | 15                               | 12            | 42                     | 46             | _                                | 15                               | 12            | 42                     | 46             | 0   | _      | MCCP1 Output Compare F                         |

| OC2A     | 4                                | 22                               | 19            | 9                      | 10             | 4                                | 22                               | 19            | 9                      | 10             | 0   |        | MCCP2 Output Compare A                         |

| OC2B     | _                                | 23                               | 20            | 10                     | 11             |                                  | 23                               | 20            | 10                     | 11             | 0   | _      | MCCP2 Output Compare B                         |

| OC2C     | _                                |                                  | _             | 2                      | 2              |                                  |                                  |               | 2                      | 2              | 0   |        | MCCP2 Output Compare C                         |

| OC2D     | _                                |                                  | _             | 3                      | 3              |                                  |                                  |               | 3                      | 3              | 0   |        | MCCP2 Output Compare D                         |

| OC2E     | _                                |                                  | _             | 4                      | 4              |                                  |                                  |               | 4                      | 4              | 0   |        | MCCP2 Output Compare E                         |

| OC2F     | _                                |                                  | _             | 5                      | 5              |                                  |                                  |               | 5                      | 5              | 0   |        | MCCP2 Output Compare F                         |

| OC3A     | _                                | 21                               | 18            | 12                     | 13             |                                  | 21                               | 18            | 12                     | 13             | 0   | _      | MCCP3 Output Compare A                         |

| OC3B     | _                                | 24                               | 21            | 13                     | 14             | _                                | 24                               | 21            | 13                     | 14             | 0   | _      | MCCP3 Output Compare B                         |

| OC4      | _                                | 18                               | 15            | 1                      | 1              | _                                | 18                               | 15            | 1                      | 1              | 0   | _      | SCCP4 Output Compare                           |

| OC5      | _                                | 19                               | 16            | 6                      | 6              | _                                | 19                               | 16            | 6                      | 6              | 0   | _      | SCCP5 Output Compare                           |

| OCFA     | 17                               | 25                               | 22            | 14                     | 15             | 17                               | 25                               | 22            | 14                     | 15             | Ι   | ST     | MCCP/SCCP Output Compare Fault Input A         |

| OCFB     | 16                               | 24                               | 21            | 32                     | 35             | 16                               | 24                               | 21            | 32                     | 35             | Ι   | ST     | MCCP/SCCP Output Compare Fault Input B         |

Legend: ANA = Analog level input/output, ST = Schmitt Trigger input buffer, I<sup>2</sup>C<sup>™</sup> = I<sup>2</sup>C/SMBus input buffer

# DS30003030B-page 24

NOTES:

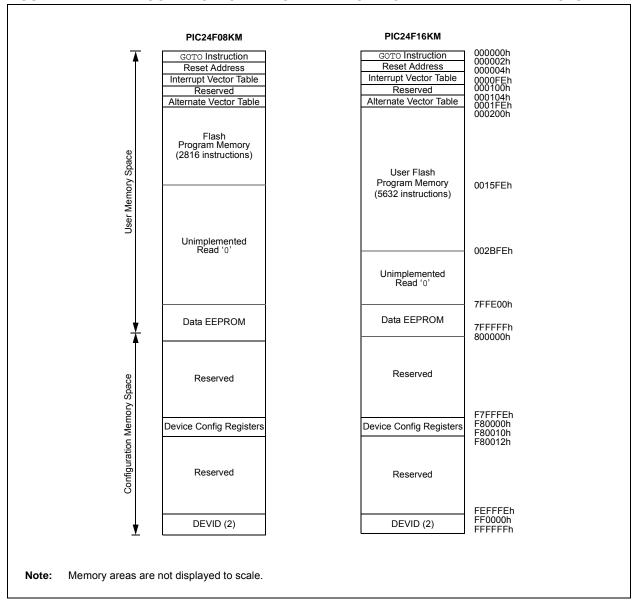

# 4.0 MEMORY ORGANIZATION

As with Harvard architecture devices, the PIC24F microcontrollers feature separate program and data memory space and busing. This architecture also allows the direct access of program memory from the Data Space (DS) during code execution.

# 4.1 **Program Address Space**

The program address memory space of the PIC24F devices is 4M instructions. The space is addressable by a 24-bit value derived from either the 23-bit Program Counter (PC) during program execution, or from a table operation or Data Space remapping, as described in **Section 4.3 "Interfacing Program and Data Memory Spaces"**.

The user access to the program memory space is restricted to the lower half of the address range (000000h to 7FFFFh). The exception is the use of TBLRD/TBLWT operations, which use TBLPAG<7> to permit access to the Configuration bits and Device ID sections of the configuration memory space.

Memory maps for the PIC24FV16KM204 family of devices are displayed in Figure 4-1.

# FIGURE 4-1: PROGRAM SPACE MEMORY MAP FOR PIC24FXXXXX FAMILY DEVICES

# REGISTER 8-7: IFS2: INTERRUPT FLAG STATUS REGISTER 2

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0, HS | U-0   |

|--------|-----|-----|-----|-----|-----|-----------|-------|

| —      | —   | —   | —   | —   | —   | CCT5IF    | —     |

| bit 15 |     |     |     |     |     |           | bit 8 |

|        |     |     |     |     |     |           |       |

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0       | U-0   |

|        |     | _   | _   |     | _   |           | _     |

| bit 7  |     |     |     |     |     |           | bit 0 |

| Legend:           | HS = Hardware Settable bit |                             |                    |

|-------------------|----------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-10 | Unimplemented: Read as '0'                                |

|-----------|-----------------------------------------------------------|

| bit 9     | CCT5IF: Capture/Compare 5 Timer Interrupt Flag Status bit |

|           | 1 = Interrupt request has occurred                        |

|           | 0 = Interrupt request has not occurred                    |

|           |                                                           |

bit 8-0 Unimplemented: Read as '0'

# REGISTER 8-8: IFS3: INTERRUPT FLAG STATUS REGISTER 3

| U-0    | R/W-0, HS | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----------|-----|-----|-----|-----|-----|-------|

| —      | RTCIF     | —   | —   | —   | —   | —   | —     |

| bit 15 |           |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0, HS | R/W-0, HS | U-0   |

|-------|-----|-----|-----|-----|-----------|-----------|-------|

| —     | —   | —   | —   | —   | BCL2IF    | SSP2IF    | —     |

| bit 7 |     |     |     |     |           |           | bit 0 |

| Legend:           | HS = Hardware Settable bit |                             |                    |

|-------------------|----------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15   | Unimplemented: Read as '0'                                                          |

|----------|-------------------------------------------------------------------------------------|

| bit 14   | RTCIF: Real-Time Clock and Calendar Interrupt Flag Status bit                       |

|          | 1 = Interrupt request has occurred                                                  |

|          | 0 = Interrupt request has not occurred                                              |

| bit 13-3 | Unimplemented: Read as '0'                                                          |

| bit 2    | BCL2IF: MSSP2 I <sup>2</sup> C <sup>™</sup> Bus Collision Interrupt Flag Status bit |

|          | 1 = Interrupt request has occurred                                                  |

|          | 0 = Interrupt request has not occurred                                              |

| bit 1    | SSP2IF: MSSP2 SPI/I <sup>2</sup> C Event Interrupt Flag Status bit                  |

|          | 1 = Interrupt request has occurred                                                  |

|          | 0 = Interrupt request has not occurred                                              |

| bit 0    | Unimplemented: Read as '0'                                                          |

|          |                                                                                     |

| RW-0         RW-1         RW-1         RW-0         RW-0         RW-0         RW-0         RW-1           R01         DOZE2         DOZE1         DOZE0         DOZEN <sup>(1)</sup> RCDIV2         RCDIV1         RCDIV0           bit 15             bit 15           U-0         U-0         U-0         U-0         U-0         U-0                   bit 7           U-0         U-0         U-0         U-0           Legend:         Re Readable bit         W = Writable bit         U = Unimplemented bit, read as '0'            -n = Value at POR         '1' = Bit is set         '0' = Bit is cleared         x = Bit is unknown           bit 15         RO: Recover on Interrupt bit         1 = Interrupts lear the DOZEN bit, and reset the CPU and peripheral clock ratio to 1:1         0 = 1:1           10 = 1:12         DOZE-c2:0: CPU and Peripheral Clock Ratio Select bits         111 = 1:2         112 = 1:2           100 = 1:1         12         DOZE-c2:0: CSCCON-14:12> = 111:         111 = 312 SkHz (divide-by-26)         111:           110 = 125 kHz (divide-by-26)         111:         111 = 25 (CSCCON-14:12>) = 111: <td< th=""><th>REGISTER</th><th>9-2: CLKL</th><th>DIV: CLOCK L</th><th></th><th>6151EK</th><th></th><th></th><th></th></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | REGISTER | 9-2: CLKL                                                                                                                                                                                                                                                        | DIV: CLOCK L                                                                                                                                                                                                                                                                                                                   |                                                                                                                  | 6151EK               |                  |                  |        |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|----------------------|------------------|------------------|--------|--|--|--|

| bit 15       bit 1         U-0       U-0       U-0       U-0       U-0       U-0         -       -       -       -       -       -         bit 7       bit 10       U-0       U-0       U-0       U-0         Egend:       R       Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       RO: Recover on Interrupt bit       1 = Interrupts clear the DOZEN bit, and reset the CPU and peripheral clock ratio to 1:1       0 = Interrupts have no effect on the DOZEN bit         bit 14-12       DOZE       DOZE       2:0: CPU and Peripheral Clock Ratio Select bits       111 = 1:28         110 = 1:4       101 = 1:28       100 = 1:16       112       100 = 1:16         011 = 1:1       DOZE       2:0: CPU and peripheral clock ratio are set to 1:1       111 = 13:25 kHz (divide-by-26)         110 = 125 kHz (divide-by-32)       100 = 2:0: CPU and peripheral clock ratio are set to 1:1       111 = 31:25 kHz (divide-by-32)         101 = 250 kHz (divide-by-30)       101 = 250 kHz (divide-by-30)       101 = 250 kHz (divide-by-30)         101 = 250 kHz (divide-by-30)       101 = 250 kHz (divide-by-30)       101 = 250 kHz (divide-by-30)         101 = 156 kHz (d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R/W-0    | R/W-0                                                                                                                                                                                                                                                            | R/W-1                                                                                                                                                                                                                                                                                                                          | R/W-1                                                                                                            |                      | R/W-0            | R/W-0            | R/W-1  |  |  |  |

| U-0         U-0         U-0         U-0         U-0         U-0         U-0           -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ROI      | DOZE2                                                                                                                                                                                                                                                            | DOZE1                                                                                                                                                                                                                                                                                                                          | DOZE0                                                                                                            | DOZEN <sup>(1)</sup> | RCDIV2           | RCDIV1           | RCDIV0 |  |  |  |

| -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | bit 15   |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                |                                                                                                                  |                      |                  |                  | bit 8  |  |  |  |

| -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 11.0     | 11.0                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                |                                                                                                                  |                      |                  |                  | 11.0   |  |  |  |

| Legend:<br>R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'<br>-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown<br>bit 15 ROI: Recover on Interrupt bit<br>1 = Interrupts clear the DOZEN bit, and reset the CPU and peripheral clock ratio to 1:1<br>0 = Interrupts have no effect on the DOZEN bit<br>bit 14-12 DOZE-2:0-: CPU and Peripheral Clock Ratio Select bits<br>111 = 1:128<br>110 = 1:64<br>110 = 1:132<br>100 = 1:16<br>011 = 1:3<br>100 = 1:16<br>011 = 1:2<br>000 = 1:1<br>bit 11 DOZEN: Doze Enable bit <sup>(1)</sup><br>1 = DOZE-2:0-> bits specify the CPU and peripheral clock ratio<br>0 = CPU and peripheral clock ratio are set to 1:1<br>bit 10-8 RCDIV-2:0->: FRC Postscaler Select bits<br>When COSC-2:0-> (OSCCON<14:12>) = 111:<br>111 = 31.25 kHz (divide-by-256)<br>110 = 125 kHz (divide-by-2)<br>100 = 500 kHz (divide-by-2)<br>100 = 2 MHz (divide-by-2) - default<br>001 = 4 MHz (divide-by-2) - default<br>001 = 4 MHz (divide-by-2)<br>100 = 8 MHz (divide-by-2)<br>100 = 15 kHz (divide-by-2)<br>100 = 125 kHz (divide-by   | 0-0      | 0-0                                                                                                                                                                                                                                                              | 0-0                                                                                                                                                                                                                                                                                                                            | 0-0                                                                                                              | 0-0                  | 0-0              | 0-0              | 0-0    |  |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       ROI: Recover on Interrupt bit       1 = Interrupts clear the DOZEN bit, and reset the CPU and peripheral clock ratio to 1:1       0 = Interrupts have no effect on the DOZEN bit         bit 14-12       DOZE-2:0>: CPU and Peripheral Clock Ratio Select bits       111 = 1:128         101 = 1:64       101 = 1:32       100 = 1:16         001 = 1:1       000 = 1:11       DOZEN: Doze Enable bit <sup>(1)</sup> 1 = DOZE<2:0>: Dits specify the CPU and peripheral clock ratio       0 = CPU and peripheral clock ratio are set to 1:1         bit 10       DOZEN: Doze Enable bit <sup>(1)</sup> 1 = DOZE         1 = 1:2       000 = 1:1       111 = 31.25 kHz (divide-by-256)         1 = 250 kHz (divide-by-256)       111 = 31.25 kHz (divide-by-256)         1 = 255 kHz (divide-by-32)       100 = 500 kHz (divide-by-32)         1 = 1 = 255 kHz (divide-by-32)       100 = 2 MHz (divide-by-41)         1 = 1 = 152 kHz (divide-by-32)       100 = 2 MHz (divide-by-32)         1 = 1 = 15 kHz (divide-by-32)       110 = 15.62 kHz (divide-by-256)         1 = 1 = 12 + 12 (divide-by-41)       111 = 1.5 kHz (divide-by-42)         1 = 1 = 1 = 1.5 kHz (divide-by-22) - default       100 = 8 MHz (divide-by-42) = 110: </td <td>bit 7</td> <td colspan="10">7</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | bit 7    | 7                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                |                                                                                                                  |                      |                  |                  |        |  |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       ROI: Recover on Interrupt bit       1 = Interrupts clear the DOZEN bit, and reset the CPU and peripheral clock ratio to 1:1       0 = Interrupts have no effect on the DOZEN bit         bit 14-12       DOZE-2:0>: CPU and Peripheral Clock Ratio Select bits       111 = 1:128         101 = 1:64       101 = 1:32       100 = 1:16         001 = 1:1       000 = 1:11       DOZEN: Doze Enable bit <sup>(1)</sup> 1 = DOZE<2:0>: Dits specify the CPU and peripheral clock ratio       0 = CPU and peripheral clock ratio are set to 1:1         bit 10       DOZEN: Doze Enable bit <sup>(1)</sup> 1 = DOZE         1 = 1:2       000 = 1:1       111 = 31.25 kHz (divide-by-256)         1 = 250 kHz (divide-by-256)       111 = 31.25 kHz (divide-by-256)         1 = 255 kHz (divide-by-32)       100 = 500 kHz (divide-by-32)         1 = 1 = 255 kHz (divide-by-32)       100 = 2 MHz (divide-by-41)         1 = 1 = 152 kHz (divide-by-32)       100 = 2 MHz (divide-by-32)         1 = 1 = 15 kHz (divide-by-32)       110 = 15.62 kHz (divide-by-256)         1 = 1 = 12 + 12 (divide-by-41)       111 = 1.5 kHz (divide-by-42)         1 = 1 = 1 = 1.5 kHz (divide-by-22) - default       100 = 8 MHz (divide-by-42) = 110: </td <td>Logondu</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Logondu  |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                |                                                                                                                  |                      |                  |                  |        |  |  |  |

| <pre>in = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15 ROI: Recover on Interrupt bit 1 = Interrupts clear the DOZEN bit, and reset the CPU and peripheral clock ratio to 1:1 0 = Interrupts have no effect on the DOZEN bit bit 14-12 DOZE-2:0&gt;: CPU and Peripheral Clock Ratio Select bits 111 = 1:128 110 = 1:64 101 = 1:32 100 = 1:1 001 = 1:4 001 = 1:2 000 = 1:1 bit 11 DOZEN: Doze Enable bit<sup>(1)</sup> 1 = DOZE-2:0&gt; bits specify the CPU and peripheral clock ratio 0 = CPU and peripheral clock ratio are set to 1:1 bit 10-8 RCDIVe2:0&gt;: FRC Postscaler Select bits When COSC&lt;2:0&gt; (OSCCON(14:12&gt;) = 111: 111 = 31.25 kHz (divide-by-266) 110 = 125 kHz (divide-by-4) 011 = 150 kHz (divide-by-4) 011 = 150 kHz (divide-by-4) 011 = 15.8 kHz (divide-by-4) 011 = 15.8 kHz (divide-by-4) 101 = 15.62 kHz (divide-by-256) 110 = 7.81 kHz (divide-by-4) 011 = 62.5 kHz (divide-by-4) 011 = 25 kHz (divide-by-4) 011 = 15.62 kHz (divide-by-4) 011 = 25 kHz (divide-by-4) 011 = 25 kHz (divide-by-4) 011 = 15.62 kHz (divide-by-4) 011 = 15.62 kHz (divide-by-4) 011 = 02.5 kHz (divide-by-4) 011 = 15.62 kHz (divide-by-4) 011 = 15.62 kHz (divide-by-2) - default 011 = 02.5 kHz (divide-by-4) 011 = 1.5 kHz (divide-by-4) 011 = 0.5 kH</pre>                                                                                                            | -        | le bit                                                                                                                                                                                                                                                           | W = Writable                                                                                                                                                                                                                                                                                                                   | bit                                                                                                              | U = Unimplem         | nented bit, read | d as '0'         |        |  |  |  |

| bit 15 ROI: Recover on Interrupt bit<br>1 = Interrupts clear the DOZEN bit, and reset the CPU and peripheral clock ratio to 1:1<br>0 = Interrupts have no effect on the DOZEN bit<br>DOZE-2:00: CPU and Peripheral Clock Ratio Select bits<br>111 = 1:128<br>110 = 1:64<br>101 = 1:32<br>100 = 1:16<br>011 = 1:8<br>010 = 1:4<br>001 = 1:2<br>000 = 1:1<br>bit 11 DOZEN: Doze Enable bit <sup>(1)</sup><br>1 = DOZE-2:00: bits specify the CPU and peripheral clock ratio<br>0 = CPU and peripheral clock ratio are set to 1:1<br>bit 10-8 RCDV-2:00: FRC Postscaler Select bits<br>When COSC-2:00: (OSCCON<14:12>) = 111:<br>111 = 31.25 kHz (divide-by-256)<br>110 = 125 kHz (divide-by-256)<br>110 = 125 kHz (divide-by-32)<br>100 = 500 kHz (divide-by-29)<br>011 = 1 MHz (divide-by-2) - default<br>000 = 8 MHz (divide-by-2) - default<br>101 = 25 kHz (divide-by-26)<br>110 = 7.81 kHz (divide-by-32)<br>100 = 7.81 kHz (divide-by-32)<br>100 = 125 kHz (divide-by-2) - default<br>001 = 125 kHz (divide-by-2) - default<br>001 = 125 kHz (divide-by-32)<br>100 = 125 kHz (divide-by-32)<br>100 = 125 kHz (divide-by-32)<br>100 = 125 kHz (divide-by-32)<br>100 = 7.81 kHz (divide-by-32)<br>100 = 125 kHz (divide-by-4)<br>011 = 62.5 kHz (divide-by-4)<br>011 = 50.5 kHz (divide-by-4)<br>011 = 15.5 kHz (divide-by-4)<br>011 = 15.5 kHz (divide-by-4)<br>011 = 62.5 kHz (divide-by-4)<br>011 = 6 |          |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                |                                                                                                                  | -                    |                  |                  | nown   |  |  |  |

| $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          | 1 = Interrupts<br>0 = Interrupts                                                                                                                                                                                                                                 | s clear the DOZ<br>s have no effect                                                                                                                                                                                                                                                                                            | EN bit, and re<br>t on the DOZE                                                                                  | N bit                | d peripheral cl  | ock ratio to 1:1 |        |  |  |  |

| 1 = DOZE<2:0> bits specify the CPU and peripheral clock ratio 0 = CPU and peripheral clock ratio are set to 1:1 bit 10-8 $RCDIV<2:0>: FRC Postscaler Select bits When COSC<2:0> (OSCCON<14:12>) = 111: 111 = 31.25 kHz (divide-by-256) 110 = 125 kHz (divide-by-264) 101 = 250 kHz (divide-by-32) 100 = 500 kHz (divide-by-32) 100 = 500 kHz (divide-by-4) 011 = 1 MHz (divide-by-4) 010 = 2 MHz (divide-by-2) - default 000 = 8 MHz (divide-by-2) 100 = 8 MHz (divide-by-2) = 110: 111 = 1.95 kHz (divide-by-256) 110 = 7.81 kHz (divide-by-256) 110 = 7.81 kHz (divide-by-32) 100 = 31.25 kHz (divide-by-3) 100 = 31.25 kHz (divide-by-4) 011 = 125 kHz (divide-by-4) 010 = 125 kHz (divide-by-4) 010 = 125 kHz (divide-by-2) - default 000 = 500 kHz (divide-by-1)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          | 111 = 1:128<br>110 = 1:64<br>101 = 1:32<br>100 = 1:16<br>011 = 1:8<br>010 = 1:4<br>001 = 1:2                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                |                                                                                                                  |                      |                  |                  |        |  |  |  |

| bit 10-8 <b>RCDIV-2:0&gt;:</b> FRC Postscaler Select bits<br>When COSC<2:0> (OSCCON<14:12>) = 111:<br>111 = 31.25 kHz (divide-by-256)<br>110 = 125 kHz (divide-by-64)<br>101 = 250 kHz (divide-by-32)<br>100 = 500 kHz (divide-by-16)<br>011 = 1 MHz (divide-by-8)<br>010 = 2 MHz (divide-by-8)<br>010 = 2 MHz (divide-by-2) – default<br>000 = 8 MHz (divide-by-2) – default<br>000 = 8 MHz (divide-by-1)<br>When COSC<2:0> (OSCCON<14:12>) = 110:<br>111 = 1.95 kHz (divide-by-26)<br>110 = 7.81 kHz (divide-by-32)<br>100 = 31.25 kHz (divide-by-32)<br>100 = 31.25 kHz (divide-by-8)<br>011 = 62.5 kHz (divide-by-8)<br>010 = 125 kHz (divide-by-4)<br>011 = 250 kHz (divide-by-2) – default<br>000 = 500 kHz (divide-by-1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | bit 11   | 1 = DOZE<2                                                                                                                                                                                                                                                       | :0> bits specify                                                                                                                                                                                                                                                                                                               |                                                                                                                  |                      | ratio            |                  |        |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | bit 10-8 | When COSC<br>111 = 31.25 K<br>110 = 125 K<br>101 = 250 K<br>100 = 500 K<br>011 = 1 MHz<br>010 = 2 MHz<br>001 = 4 MHz<br>000 = 8 MHz<br>When COSC<br>111 = 1.95 K<br>100 = 7.81 K<br>101 = 15.62 K<br>100 = 31.25 K<br>011 = 62.5 K<br>010 = 125 K<br>001 = 250 K | <2:0> (OSCCO<br>kHz (divide-by-2<br>dz (divide-by-2<br>dz (divide-by-32<br>dz (divide-by-32<br>dz (divide-by-32)<br>(divide-by-4)<br>(divide-by-4)<br>(divide-by-2)<br>- (divide-by-2)<br>- (divide-by-2)<br>- (divide-by-2)<br>- (divide-by-2)<br>- (divide-by-3)<br>dz (divide-by-4)<br>dz (divide-by-2)<br>dz (divide-by-2) | <u>N&lt;14:12&gt;) = 1</u><br>256)<br>)<br>)<br>default<br><u>N&lt;14:12&gt;) = 1</u><br>56)<br>4)<br>32)<br>16) | -                    |                  |                  |        |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | bit 7-0  |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                | )'                                                                                                               |                      |                  |                  |        |  |  |  |

### REGISTER 9-2: CLKDIV: CLOCK DIVIDER REGISTER

**Note 1:** This bit is automatically cleared when the ROI bit is set and an interrupt occurs.

The following code sequence for a clock switch is recommended:

- 1. Disable interrupts during the OSCCON register unlock and write sequence.

- 2. Execute the unlock sequence for the OSCCON high byte by writing 78h and 9Ah to OSCCON<15:8>, in two back-to-back instructions.

- 3. Write the new oscillator source to the NOSCx bits in the instruction immediately following the unlock sequence.

- Execute the unlock sequence for the OSCCON 4. low byte by writing 46h and 57h to OSCCON<7:0>, in two back-to-back instructions.

- Set the OSWEN bit in the instruction immediately 5 following the unlock sequence.

- Continue to execute code that is not 6. clock-sensitive (optional).

- Invoke an appropriate amount of software delay 7. (cycle counting) to allow the selected oscillator and/or PLL to start and stabilize.

- 8. Check to see if OSWEN is '0'. If it is, the switch was successful. If OSWEN is still set, then check the LOCK bit to determine the cause of failure.

The core sequence for unlocking the OSCCON register and initiating a clock switch is shown in Example 9-1 and Example 9-2.

#### EXAMPLE 9-1: ASSEMBLY CODE SEQUENCE FOR CLOCK SWITCHING

| ;Place the new oscillator selection in WO |

|-------------------------------------------|

| ;OSCCONH (high byte) Unlock Sequence      |

| MOV #OSCCONH, w1                          |

| MOV #0x78, w2                             |

| MOV #0x9A, w3                             |

| MOV.b w2, [w1]                            |

| MOV.b w3, [w1]                            |

| ;Set new oscillator selection             |

| MOV.b WREG, OSCCONH                       |

| ;OSCCONL (low byte) unlock sequence       |

| MOV #OSCCONL, w1                          |

| MOV #0x46, w2                             |

| MOV #0x57, w3                             |

| MOV.b w2, [w1]                            |

| MOV.b w3, [w1]                            |