Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                     |

| Number of I/O              | 37                                                                             |

| Program Memory Size        | 8KB (2.75K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | 512 x 8                                                                        |

| RAM Size                   | 2K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5V                                                                        |

| Data Converters            | A/D 22x10b/12b; D/A 2x8b                                                       |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 44-QFN (8x8)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fv08km204t-i-ml |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.4.1 CONSIDERATIONS FOR CERAMIC CAPACITORS

In recent years, large value, low-voltage, surface-mount ceramic capacitors have become very cost effective in sizes up to a few tens of microfarad. The low-ESR, small physical size and other properties make ceramic capacitors very attractive in many types of applications.

Ceramic capacitors are suitable for use with the internal voltage regulator of this microcontroller. However, some care is needed in selecting the capacitor to ensure that it maintains sufficient capacitance over the intended operating range of the application.

Typical low-cost, 10  $\mu$ F ceramic capacitors are available in X5R, X7R and Y5V dielectric ratings (other types are also available, but are less common). The initial tolerance specifications for these types of capacitors are often specified as ±10% to ±20% (X5R and X7R), or -20%/+80% (Y5V). However, the effective capacitance that these capacitors provide in an application circuit will also vary based on additional factors, such as the applied DC bias voltage and the temperature. The total in-circuit tolerance is, therefore, much wider than the initial tolerance specification.

The X5R and X7R capacitors typically exhibit satisfactory temperature stability (ex:  $\pm 15\%$  over a wide temperature range, but consult the manufacturer's data sheets for exact specifications). However, Y5V capacitors typically have extreme temperature tolerance specifications of  $\pm 22\%/-82\%$ . Due to the extreme temperature tolerance, a 10 µF nominal rated Y5V type capacitor may not deliver enough total capacitance to meet minimum internal voltage regulator stability and transient response requirements. Therefore, Y5V capacitors are not recommended for use with the internal regulator if the application must operate over a wide temperature range.

In addition to temperature tolerance, the effective capacitance of large value ceramic capacitors can vary substantially, based on the amount of DC voltage applied to the capacitor. This effect can be very significant, but is often overlooked or is not always documented.

A typical DC bias voltage vs. capacitance graph for X7R type capacitors is shown in Figure 2-4.

#### DC BIAS VOLTAGE vs. FIGURE 2-4: CAPACITANCE **CHARACTERISTICS** Capacitance Change (%) 0 -10 16V Capacitor -20 -30 -40 10V Capacitor -50 -60 -70 6.3V Capacitor -80 -9 10 11 12 13 2 8 15 16 DC Bias Voltage (VDC)

When selecting a ceramic capacitor to be used with the internal voltage regulator, it is suggested to select a high-voltage rating, so that the operating voltage is a small percentage of the maximum rated capacitor voltage. For example, choose a ceramic capacitor rated at 16V for the 3.3V or 2.5V core voltage. Suggested capacitors are shown in Table 2-1.

### 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of ohms, not to exceed 100Ω.

Pull-up resistors, series diodes, and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits, and pins, Voltage Input High (VIH) and Voltage Input Low (VIL) requirements.

For device emulation, ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins), programmed into the device, matches the physical connections for the ICSP to the Microchip debugger/emulator tool.

For more information on available Microchip development tools connection requirements, refer to **Section 26.0 "Development Support"**.

#### TABLE 4-6: TIMER1 REGISTER MAP

| File Name | Addr.                | Bit 15 | Bit 14                                                                | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7        | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|----------------------|--------|-----------------------------------------------------------------------|--------|--------|--------|--------|-------|--------|--------------|-------|-------|-------|-------|-------|-------|-------|---------------|

| TMR1      | 100h Timer1 Register |        |                                                                       |        |        |        |        |       |        |              |       |       |       |       | xxxx  |       |       |               |

| PR1       | 102h                 |        |                                                                       |        |        |        |        |       | Timer1 | Period Regis | ster  |       |       |       |       |       |       | FFFF          |

| T1CON     | 104h                 | TON    | N <u>- TSIDL TECS1 TECS0 - TGATE TCKPS1 TCKPS0 - TSYNC TCS -</u> 0000 |        |        |        |        |       |        |              |       |       |       |       |       |       |       |               |

|           |                      |        |                                                                       |        |        |        |        |       |        |              |       |       |       |       |       |       |       |               |

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition, r = reserved.

#### TABLE 4-7: CLC1-2 REGISTER MAP

| File Name               | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| CLC1CONL                | 122h  | LCEN   | —      | _      | —      | INTP   | INTN   | —     | —     | LCOE  | LCOUT | LCPOL | —     | _     | MODE2 | MODE1 | MODE0 | 0000          |

| CLC1CONH                | 124h  | _      | _      |        | _      | _      | _      | _     | _     | _     | _     | _     | _     | G4POL | G3POL | G2POL | G1POL | 0000          |

| CLC1SEL                 | 126h  | _      | DS42   | DS41   | DS40   |        | DS32   | DS31  | DS30  | —     | DS22  | DS21  | DS20  | _     | DS12  | DS11  | DS10  | 0000          |

| CLC1GLSL                | 12Ah  | G2D4T  | G2D4N  | G2D3T  | G2D3N  | G2D2T  | G2D2N  | G2D1T | G2D1N | G1D4T | G1D4N | G1D3T | G1D3N | G1D2T | G1D2N | G1D1T | G1D1N | 0000          |

| CLC1GLSH                | 12Ch  | G4D4T  | G4D4N  | G4D3T  | G4D3N  | G4D2T  | G4D2N  | G4D1T | G4D1N | G3D4T | G3D4N | G3D3T | G3D3N | G3D2T | G3D2N | G3D1T | G3D1N | 0000          |

| CLC2CONL <sup>(1)</sup> | 12Eh  | LCEN   | _      | -      | _      | INTP   | INTN   | _     | _     | LCOE  | LCOUT | LCPOL | _     | _     | MODE2 | MODE1 | MODE0 | 0000          |

| CLC2CONH <sup>(1)</sup> | 130h  | —      | —      | _      | —      | _      | _      | —     | _     | _     | _     | _     | —     | G4POL | G3POL | G2POL | G1POL | 0000          |

| CLC2SEL <sup>(1)</sup>  | 132h  | —      | DS42   | DS41   | DS40   | _      | DS32   | DS31  | DS30  | _     | DS22  | DS21  | DS20  | —     | DS12  | DS11  | DS10  | 0000          |

| CLC2GLSL <sup>(1)</sup> | 136h  | G2D4T  | G2D4N  | G2D3T  | G2D3N  | G2D2T  | G2D2N  | G2D1T | G2D1N | G1D4T | G1D4N | G1D3T | G1D3N | G1D2T | G1D2N | G1D1T | G1D1N | 0000          |

| CLC2GLSH <sup>(1)</sup> | 138h  | G4D4T  | G4D4N  | G4D3T  | G4D3N  | G4D2T  | G4D2N  | G4D1T | G4D1N | G3D4T | G3D4N | G3D3T | G3D3N | G3D2T | G3D2N | G3D1T | G3D1N | 0000          |

**Legend:** x = unknown, u = unchanged, --- = unimplemented, q = value depends on condition, r = reserved.

Note 1: These registers are available only on PIC24F(V)16KM2XX devices.

#### TABLE 4-31: CLOCK CONTROL REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7   | Bit 6 | Bit 5  | Bit 4 | Bit 3  | Bit 2   | Bit 1  | Bit 0  | All<br>Resets |

|-----------|-------|--------|--------|--------|--------|--------|--------|--------|--------|---------|-------|--------|-------|--------|---------|--------|--------|---------------|

| RCON      | 740h  | TRAPR  | IOPUWR | SBOREN | RETEN  |        |        | СМ     | PMSLP  | EXTR    | SWR   | SWDTEN | WDTO  | SLEEP  | IDLE    | BOR    | POR    | (Note 1)      |

| OSCCON    | 742h  | _      | COSC2  | COSC1  | COSC0  | _      | NOSC2  | NOSC1  | NOSC0  | CLKLOCK | _     | LOCK   | _     | CF     | SOSCDRV | SOSCEN | OSWEN  | (Note 2)      |

| CLKDIV    | 744h  | ROI    | DOZE2  | DOZE1  | DOZE0  | DOZEN  | RCDIV2 | RCDIV1 | RCDIV0 | _       | _     | _      | _     | _      | _       | _      | _      | 0100          |

| OSCTUN    | 748h  | _      | _      | _      | _      | _      | _      | _      | _      | _       | _     | TUN5   | TUN4  | TUN3   | TUN2    | TUN1   | TUN0   | 0000          |

| REFOCON   | 74Eh  | ROEN   | —      | ROSSLP | ROSEL  | RODIV3 | RODIV2 | RODIV1 | RODIV0 | _       | _     | _      | —     | —      | —       | _      | _      | 0000          |

| HLVDCON   | 756h  | HLVDEN | —      | HLSIDL | _      | _      | —      | _      | _      | VDIR    | BGVST | IRVST  | _     | HLVDL3 | HLVDL2  | HLVDL1 | HLVDL0 | 0000          |

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

Note 1: RCON register Reset values are dependent on the type of Reset.

2: OSCCON register Reset values are dependent on Configuration fuses and by type of Reset.

#### TABLE 4-32: NVM REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-----------|-------|--------|--------|--------|---------|--------|--------|-------|-------|---------|---------|---------|---------|---------|---------|---------|---------|---------------|

| NVMCON    | 760h  | WR     | WREN   | WRERR  | PGMONLY |        |        | _     |       | _       | ERASE   | NVMOP5  | NVMOP4  | NVMOP3  | NVMOP2  | NVMOP1  | NVMOP0  | 0000          |

| NVMKEY    | 766h  | —      |        |        | _       |        | _      |       |       | NVMKEY7 | NVMKEY6 | NVMKEY5 | NVMKEY4 | NVMKEY3 | NVMKEY2 | NVMKEY1 | NVMKEY0 | 0000          |

Legend: x = unknown, u = unchanged, - = unimplemented, q = value depends on condition, r = reserved.

#### TABLE 4-33: ULTRA LOW-POWER WAKE-UP REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|--------|--------|---------|--------|--------|--------|-------|---------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| ULPWCON   | 768h  | ULPEN  |        | ULPSIDL | _      | _      | _      | —     | ULPSINK | —     |       | —     | _     | _     | _     |       |       | 0000          |

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

#### TABLE 4-34: PMD REGISTER MAP

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8 | Bit 7  | Bit 6                 | Bit 5                 | Bit 4                 | Bit 3                 | Bit 2                 | Bit 1                 | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|-------|--------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|--------|---------------|

| PMD1         | 770h  | _      | _      |        | —      | T1MD   |        | _      | _     | SSP1MD | U2MD <sup>(1)</sup>   | U1MD                  | _                     | _                     | _                     | _                     | ADCMD  | 0000          |

| PMD2         | 772h  |        | _      |        | _      |        | _      | _      | _     | _      | -                     | _                     | CCP5MD <sup>(1)</sup> | CCP4MD <sup>(1)</sup> | CCP3MD <sup>(1)</sup> | CCP2MD                | CCP1MD | 0000          |

| PMD3         | 774h  |        | _      |        | _      |        | CMPMD  | RTCCMD | _     | _      | DAC1MD <sup>(1)</sup> | _                     | _                     | _                     | _                     | SSP2MD <sup>(1)</sup> | _      | 0000          |

| PMD4         | 776h  |        | _      |        | _      |        | _      | _      | _     | _      | ULPWUMD               | _                     | _                     | REFOMD                | CTMUMD                | HLVDMD                | _      | 0000          |

| PMD6         | 77Ah  |        | _      |        | _      |        | _      | _      | _     | _      | -                     | AMP1MD <sup>(1)</sup> | DAC2MD <sup>(1)</sup> | AMP2MD <sup>(1)</sup> | _                     | _                     | _      | 0000          |

| PMD8         | 77Eh  | _      | _      | —      | _      | _      | -      | _      | _     | _      | _                     | _                     | —                     | CLC2MD <sup>(1)</sup> | CLC1MD                | _                     | _      | 0000          |

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition, r = reserved.

Note 1: These bits are available only on PIC24F(V)16KM2XX devices.

#### 4.2.5 SOFTWARE STACK

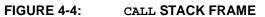

In addition to its use as a working register, the W15 register in PIC24F devices is also used as a Software Stack Pointer. The pointer always points to the first available free word and grows from lower to higher addresses. It pre-decrements for stack pops and post-increments for stack pushes, as depicted in Figure 4-4.

For a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, ensuring that the MSB is always clear.

| Note: | A PC push during exception processing    |

|-------|------------------------------------------|

|       | will concatenate the SRL register to the |

|       | MSB of the PC prior to the push.         |

The Stack Pointer Limit Value (SPLIM) register, associated with the Stack Pointer, sets an upper address boundary for the stack. SPLIM is uninitialized at Reset. As is the case for the Stack Pointer, SPLIM<0> is forced to '0' as all stack operations must be word-aligned. Whenever an EA is generated using W15 as a source or destination pointer, the resulting address is compared with the value in SPLIM. If the contents of the Stack Pointer (W15) and the SPLIM register are equal, and a push operation is performed, a stack error trap will not occur. The stack error trap will occur on a subsequent push operation.

Thus, for example, if it is desirable to cause a stack error trap when the stack grows beyond address, 0DF6 in RAM, initialize the SPLIM with the value, 0DF4.

Similarly, a Stack Pointer underflow (stack error) trap is generated when the Stack Pointer address is found to be less than 0800h. This prevents the stack from interfering with the Special Function Register (SFR) space.

**Note:** A write to the SPLIM register should not be immediately followed by an indirect read operation using W15.

#### 4.3 Interfacing Program and Data Memory Spaces

The PIC24F architecture uses a 24-bit-wide program space and 16-bit-wide Data Space (DS). The architecture is also a modified Harvard scheme, meaning that data can also be present in the program space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Apart from the normal execution, the PIC24F architecture provides two methods by which the program space can be accessed during operation:

- Using table instructions to access individual bytes or words anywhere in the program space

- Remapping a portion of the program space into the Data Space, PSV

Table instructions allow an application to read or write small areas of the program memory. This makes the method ideal for accessing data tables that need to be updated from time to time. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for look ups from a large table of static data. It can only access the least significant word (lsw) of the program word.

#### 4.3.1 ADDRESSING PROGRAM SPACE

Since the address ranges for the data and program spaces are 16 and 24 bits, respectively, a method is needed to create a 23-bit or 24-bit program address from 16-bit data registers. The solution depends on the interface method to be used.

For table operations, the 8-bit Table Memory Page Address register (TBLPAG) is used to define a 32K word region within the program space. This is concatenated with a 16-bit EA to arrive at a full 24-bit program space address. In this format, the Most Significant bit (MSb) of TBLPAG is used to determine if the operation occurs in the user memory (TBLPAG<7> = 0) or the configuration memory (TBLPAG<7> = 1).

For remapping operations, the 8-bit Program Space Visibility Page Address register (PSVPAG) is used to define a 16K word page in the program space. When the MSb of the EA is '1', PSVPAG is concatenated with the lower 15 bits of the EA to form a 23-bit program space address. Unlike the table operations, this limits remapping operations strictly to the user memory area.

See Table 4-35 and Figure 4-5 to know how the program EA is created for table operations and remapping accesses from the data EA. Here, P<23:0> refers to a program space word, whereas D<15:0> refers to a Data Space word.

#### REGISTER 8-7: IFS2: INTERRUPT FLAG STATUS REGISTER 2

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0, HS | U-0   |

|--------|-----|-----|-----|-----|-----|-----------|-------|

| —      | —   | —   | —   | —   | —   | CCT5IF    | —     |

| bit 15 |     |     |     |     |     |           | bit 8 |

|        |     |     |     |     |     |           |       |

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0       | U-0   |

|        |     | _   | _   |     | _   |           | _     |

| bit 7  |     |     |     |     |     |           | bit 0 |

| Legend:           | HS = Hardware Settable bit |                             |                    |

|-------------------|----------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-10 | Unimplemented: Read as '0'                                |

|-----------|-----------------------------------------------------------|

| bit 9     | CCT5IF: Capture/Compare 5 Timer Interrupt Flag Status bit |

|           | 1 = Interrupt request has occurred                        |

|           | 0 = Interrupt request has not occurred                    |

|           |                                                           |

bit 8-0 Unimplemented: Read as '0'

#### REGISTER 8-8: IFS3: INTERRUPT FLAG STATUS REGISTER 3

| U-0    | R/W-0, HS | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----------|-----|-----|-----|-----|-----|-------|

| —      | RTCIF     | —   | —   | —   | —   | —   | —     |

| bit 15 |           |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0, HS | R/W-0, HS | U-0   |

|-------|-----|-----|-----|-----|-----------|-----------|-------|

| —     | —   | —   | —   | —   | BCL2IF    | SSP2IF    | —     |

| bit 7 |     |     |     |     |           |           | bit 0 |

| Legend:           | HS = Hardware Settable bit |                                    |                    |  |  |  |

|-------------------|----------------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

| bit 15   | Unimplemented: Read as '0'                                                          |

|----------|-------------------------------------------------------------------------------------|

| bit 14   | RTCIF: Real-Time Clock and Calendar Interrupt Flag Status bit                       |

|          | 1 = Interrupt request has occurred                                                  |

|          | 0 = Interrupt request has not occurred                                              |

| bit 13-3 | Unimplemented: Read as '0'                                                          |

| bit 2    | BCL2IF: MSSP2 I <sup>2</sup> C <sup>™</sup> Bus Collision Interrupt Flag Status bit |

|          | 1 = Interrupt request has occurred                                                  |

|          | 0 = Interrupt request has not occurred                                              |

| bit 1    | SSP2IF: MSSP2 SPI/I <sup>2</sup> C Event Interrupt Flag Status bit                  |

|          | 1 = Interrupt request has occurred                                                  |

|          | 0 = Interrupt request has not occurred                                              |

| bit 0    | Unimplemented: Read as '0'                                                          |

|          |                                                                                     |

|              |                                                                       |                               | -                          |                   |                  |                 |         |  |  |  |  |  |  |

|--------------|-----------------------------------------------------------------------|-------------------------------|----------------------------|-------------------|------------------|-----------------|---------|--|--|--|--|--|--|

| U-0          | U-0                                                                   | U-0                           | U-0                        | U-0               | R/W-1            | R/W-0           | R/W-0   |  |  |  |  |  |  |

| _            | _                                                                     | _                             | _                          | _                 | BCL2IP2          | BCL2IP1         | BCL2IP0 |  |  |  |  |  |  |

| oit 15       |                                                                       |                               |                            |                   |                  |                 | bit 8   |  |  |  |  |  |  |

|              |                                                                       |                               |                            |                   |                  |                 |         |  |  |  |  |  |  |

| U-0          | R/W-1                                                                 | R/W-0                         | R/W-0                      | U-0               | U-0              | U-0             | U-0     |  |  |  |  |  |  |

| —            | SSP2IP2                                                               | SSP2IP1                       | SSP2IP0                    |                   | —                | —               | —       |  |  |  |  |  |  |

| bit 7        |                                                                       |                               |                            |                   |                  |                 | bit 0   |  |  |  |  |  |  |

|              |                                                                       |                               |                            |                   |                  |                 |         |  |  |  |  |  |  |

| Legend:      |                                                                       |                               |                            |                   |                  |                 |         |  |  |  |  |  |  |

| R = Readab   | ole bit                                                               | W = Writable                  | bit                        | U = Unimplei      | mented bit, read | d as '0'        |         |  |  |  |  |  |  |

| -n = Value a | at POR                                                                | '1' = Bit is set              |                            | '0' = Bit is cle  | eared            | x = Bit is unkr | nown    |  |  |  |  |  |  |

|              |                                                                       |                               |                            |                   |                  |                 |         |  |  |  |  |  |  |

| bit 15-11    | -                                                                     | nted: Read as '               |                            |                   |                  |                 |         |  |  |  |  |  |  |

| bit 10-8     | BCL2IP<2:0                                                            | >: MSSP2 I <sup>2</sup> C™    | Bus Collision              | Interrupt Prior   | rity bits        |                 |         |  |  |  |  |  |  |

|              | <pre>111 = Interrupt is Priority 7 (highest priority interrupt)</pre> |                               |                            |                   |                  |                 |         |  |  |  |  |  |  |

|              |                                                                       |                               |                            |                   |                  |                 |         |  |  |  |  |  |  |

|              | •                                                                     |                               |                            |                   |                  |                 |         |  |  |  |  |  |  |

|              | 001 = Interrupt is Priority 1                                         |                               |                            |                   |                  |                 |         |  |  |  |  |  |  |

|              | 000 = Interru                                                         | pt source is dis              | abled                      |                   |                  |                 |         |  |  |  |  |  |  |

| bit 7        | Unimplemen                                                            | nted: Read as '               | o'                         |                   |                  |                 |         |  |  |  |  |  |  |

| bit 6-4      | SSP2IP<2:0>                                                           | SPI/I SPI/I                   | <sup>2</sup> C Event Inter | rupt Priority bit | ts               |                 |         |  |  |  |  |  |  |

|              | 111 = Interru                                                         | pt is Priority 7 (            | highest priority           | / interrupt)      |                  |                 |         |  |  |  |  |  |  |

|              |                                                                       |                               |                            |                   |                  |                 |         |  |  |  |  |  |  |

|              | •                                                                     |                               |                            |                   |                  |                 |         |  |  |  |  |  |  |

|              | 001 = Interru                                                         | 001 = Interrupt is Priority 1 |                            |                   |                  |                 |         |  |  |  |  |  |  |

|              | 000 = Interru                                                         | pt source is dis              | abled                      |                   |                  |                 |         |  |  |  |  |  |  |

| bit 3-0      | Unimplemen                                                            | ted: Read as '                | כ'                         |                   |                  |                 |         |  |  |  |  |  |  |

|              |                                                                       |                               |                            |                   |                  |                 |         |  |  |  |  |  |  |

#### REGISTER 8-28: IPC12: INTERRUPT PRIORITY CONTROL REGISTER 12

#### 13.2 General Purpose Timer

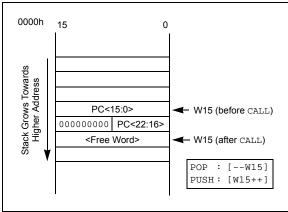

Timer mode is selected when CCSEL = 0 and MOD<3:0> = 0000. The timer can function as a 32-bit timer or a dual 16-bit timer, depending on the setting of the T32 bit (Table 13-2).

| T32<br>(CCPxCON1L<5>) | Operating Mode           |

|-----------------------|--------------------------|

| 0                     | Dual Timer Mode (16-bit) |

| 1                     | Timer Mode (32-bit)      |

TABLE 13-2: TIMER OPERATION MODE

Dual 16-Bit Timer mode provides a simple timer function with two independent 16-bit timer/counters. The primary timer uses CCPxTMRL and CCPxPRL. Only the primary timer can interact with other modules on the device. It generates the MCCPx Sync out signals for use by other MCCP modules. It can also use the SYNC<4:0> bits signal generated by other modules.

The secondary timer uses CCPxTMRH and CCPxPRH. It is intended to be used only as a periodic interrupt source for scheduling CPU events. It does not generate an Output Sync/Trigger signal like the primary time base. In Dual Timer mode, the Secondary Timer Period register, CCPxPRH, generates the MCCP Compare Event (CCPxIF) used by many other modules on the device.

The 32-Bit Timer mode uses the CCPxTMRL and CCPxTMRH registers, together, as a single 32-bit timer. When CCPxTMRL overflows, CCPxTMRH increments by one. This mode provides a simple timer function when it is important to track long time periods. Note that

the T32 bit (CCPxCON1L<5>) should be set before the CCPxTMRL or CCPxPRH registers are written to initialize the 32-bit timer.

#### 13.2.1 SYNC AND TRIGGER OPERATION

In both 16-bit and 32-bit modes, the timer can also function in either Synchronization ("Sync") or Trigger operation. Both use the SYNC<4:0> bits (CCPxCON1H<4:0>) to determine the input signal source. The difference is how that signal affects the timer.

In Sync operation, the timer Reset or clear occurs when the input selected by SYNC<4:0> is asserted. The timer immediately begins to count again from zero unless it is held for some other reason. Sync operation is used whenever the TRIGEN bit (CCPxCON1H<7>) is cleared. SYNC<4:0> can have any value except '11111'.

In Trigger operation, the timer is held in Reset until the input selected by SYNC<4:0> is asserted; when it occurs, the timer starts counting. Trigger operation is used whenever the TRIGEN bit is set. In Trigger mode, the timer will continue running after a Trigger event as long as the CCPTRIG bit (CCPxSTATL< 7>) is set. To clear CCPTRIG, the TRCLR bit (CCPxSTATL<5>) must be set to clear the Trigger event, reset the timer and hold it at zero until another Trigger event occurs. On PIC24FV16KM204 family devices, Trigger operation can only be used when the system clock is the time base source (CLKSEL<2:0> = 000).

#### REGISTER 15-2: UxSTA: UARTx STATUS AND CONTROL REGISTER

| R/W-0        | R/W-0  | R/W-0    | U-0 | R/W-0, HC | R/W-0 | R-0, HSC | R-1, HSC |  |  |  |  |

|--------------|--------|----------|-----|-----------|-------|----------|----------|--|--|--|--|

| UTXISEL1     | UTXINV | UTXISEL0 | —   | UTXBRK    | UTXEN | UTXBF    | TRMT     |  |  |  |  |

| bit 15 bit 8 |        |          |     |           |       |          |          |  |  |  |  |

| R/W-0       | R/W-0    | R/W-0 | R-1, HSC | R-0, HSC | R-0, HSC | R/C-0, HS | R-0, HSC |  |  |  |  |

|-------------|----------|-------|----------|----------|----------|-----------|----------|--|--|--|--|

| URXISEL1    | URXISEL0 | ADDEN | RIDLE    | PERR     | FERR     | OERR      | URXDA    |  |  |  |  |

| bit 7 bit 0 |          |       |          |          |          |           |          |  |  |  |  |

| Legend:                    | HC = Hardware Clearable bit |                                       |                    |  |  |  |

|----------------------------|-----------------------------|---------------------------------------|--------------------|--|--|--|

| HS = Hardware Settable bit | C = Clearable bit           | HSC = Hardware Settable/Clearable bit |                    |  |  |  |

| R = Readable bit           | W = Writable bit            | U = Unimplemented bit, read as '0'    |                    |  |  |  |

| -n = Value at POR          | '1' = Bit is set            | '0' = Bit is cleared                  | x = Bit is unknown |  |  |  |

bit 15,13 UTXISEL<1:0>: UARTx Transmission Interrupt Mode Selection bits

- 11 = Reserved; do not use

- 10 = Interrupt when a character is transferred to the Transmit Shift Register (TSR) and as a result, the transmit buffer becomes empty

- 01 = Interrupt when the last character is shifted out of the Transmit Shift Register; all transmit operations are completed

- 00 = Interrupt when a character is transferred to the Transmit Shift Register (this implies there is at least one character open in the transmit buffer)

- bit 14 UTXINV: IrDA<sup>®</sup> Encoder Transmit Polarity Inversion bit

| bit 14  | UTXINV: IrDA <sup>®</sup> Encoder Transmit Polarity Inversion bit                                                                                                                                                        |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <u>If IREN = 0:</u>                                                                                                                                                                                                      |

|         | 1 = UxTX Idle '0'                                                                                                                                                                                                        |

|         | 0 = UxTX Idle '1'                                                                                                                                                                                                        |

|         | <u>If IREN = 1:</u>                                                                                                                                                                                                      |

|         | 1 = UxTX Idle '1'                                                                                                                                                                                                        |

|         | 0 = UxTX Idle '0'                                                                                                                                                                                                        |

| bit 12  | Unimplemented: Read as '0'                                                                                                                                                                                               |

| bit 11  | UTXBRK: UARTx Transmit Break bit                                                                                                                                                                                         |

|         | <ul> <li>1 = Sends Sync Break on next transmission – Start bit, followed by twelve '0' bits, followed by Stop bit;<br/>cleared by hardware upon completion</li> </ul>                                                    |

|         | 0 = Sync Break transmission is disabled or completed                                                                                                                                                                     |

| bit 10  | UTXEN: UARTx Transmit Enable bit                                                                                                                                                                                         |

|         | <ul> <li>1 = Transmit is enabled; UxTX pin is controlled by UARTx</li> <li>0 = Transmit is disabled; any pending transmission is aborted and the buffer is reset; UxTX pin is controlled by the PORT register</li> </ul> |

| bit 9   | UTXBF: UARTx Transmit Buffer Full Status bit (read-only)                                                                                                                                                                 |

|         | 1 = Transmit buffer is full                                                                                                                                                                                              |

|         | 0 = Transmit buffer is not full, at least one more character can be written                                                                                                                                              |

| bit 8   | TRMT: Transmit Shift Register Empty bit (read-only)                                                                                                                                                                      |

|         | <ul> <li>1 = Transmit Shift Register is empty and the transmit buffer is empty (the last transmission has<br/>completed)</li> </ul>                                                                                      |

|         | 0 = Transmit Shift Register is not empty; a transmission is in progress or queued                                                                                                                                        |

| bit 7-6 | URXISEL<1:0>: UARTx Receive Interrupt Mode Selection bits                                                                                                                                                                |

|         | 11 = Interrupt is set on an RSR transfer, making the receive buffer full (i.e., has 4 data characters)                                                                                                                   |

|         | 10 = Interrupt is set on an RSR transfer, making the receive buffer 3/4 full (i.e., has 3 data characters)                                                                                                               |

|         | 0x = Interrupt is set when any character is received and transferred from the RSR to the receive buffer; receive buffer has one or more characters                                                                       |

|         |                                                                                                                                                                                                                          |

## TABLE 19-2:NUMERICAL EQUIVALENTS OF VARIOUS RESULT CODES:<br/>12-BIT FRACTIONAL FORMATS

| VIN/VREF   | 12-Bit<br>Output Code | 16-Bit Fractional Format<br>Equivalent Decimal Value |       | 16-Bit Signed Fractional Format/<br>Equivalent Decimal Value |        |  |  |  |  |  |  |  |

|------------|-----------------------|------------------------------------------------------|-------|--------------------------------------------------------------|--------|--|--|--|--|--|--|--|

| +4095/4096 | 0 1111 1111 1111      | 1111 1111 1111 0000                                  | 0.999 | 0111 1111 1111 1000                                          | 0.999  |  |  |  |  |  |  |  |

| +4094/4096 | 0 1111 1111 1110      | 1111 1111 1110 0000                                  | 0.998 | 0111 1111 1110 1000                                          | 0.998  |  |  |  |  |  |  |  |

|            | •••                   |                                                      |       |                                                              |        |  |  |  |  |  |  |  |

| +1/4096    | 0 0000 0000 0001      | 0000 0000 0001 0000                                  | 0.001 | 0000 0000 0000 1000                                          | 0.001  |  |  |  |  |  |  |  |

| 0/4096     | 0 0000 0000 0000      | 0000 0000 0000 0000                                  | 0.000 | 0000 0000 0000 0000                                          | 0.000  |  |  |  |  |  |  |  |

| -1/4096    | 1 0111 1111 1111      | 0000 0000 0000 0000                                  | 0.000 | 1111 1111 1111 1000                                          | -0.001 |  |  |  |  |  |  |  |

|            | •••                   |                                                      |       |                                                              |        |  |  |  |  |  |  |  |

| -4095/4096 | 1 0000 0000 0001      | 0000 0000 0000 0000                                  | 0.000 | 1000 0000 0000 1000                                          | -0.999 |  |  |  |  |  |  |  |

| -4096/4096 | 1 0000 0000 0000      | 0000 0000 0000 0000                                  | 0.000 | 1000 0000 0000 0000                                          | -1.000 |  |  |  |  |  |  |  |

### FIGURE 19-5: A/D OUTPUT DATA FORMATS (10-BIT)

| RAM Contents:            |     |     |     |     |     |     | d09 | d08 | d07 | d06 | d05 | d04 | d03 | d02 | d01 | d00 |

|--------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Read to Bus:             |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     | I   |

| Integer                  | 0   | 0   | 0   | 0   | 0   | 0   | d09 | d08 | d07 | d06 | d05 | d04 | d03 | d02 | d01 | d00 |

|                          |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

| Signed Integer           | s0  | s0  | s0  | s0  | s0  | s0  | d09 | d08 | d07 | d06 | d05 | d04 | d03 | d02 | d01 | d00 |

|                          |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

| Fractional (1.15)        | d09 | d08 | d07 | d06 | d05 | d04 | d03 | d02 | d01 | d00 | 0   | 0   | 0   | 0   | 0   | 0   |

|                          |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

| Signed Fractional (1.15) | s0  | d09 | d08 | d07 | d06 | d05 | d04 | d03 | d02 | d01 | d00 | 0   | 0   | 0   | 0   | 0   |

|                          | L   |     |     |     |     |     |     | 1   |     |     |     |     |     |     |     |     |

## TABLE 19-3:NUMERICAL EQUIVALENTS OF VARIOUS RESULT CODES:<br/>10-BIT INTEGER FORMATS

| VIN/VREF   | 10-Bit Differential<br>Output Code<br>(11-bit result) | 16-Bit Integer Format/16-Bit Signed Integer Format/Equivalent Decimal ValueEquivalent Decimal Value |      |                     |       |  |

|------------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------|---------------------|-------|--|

| +1023/1024 | 011 1111 1111                                         | 0000 0011 1111 1111                                                                                 | 1023 | 0000 0001 1111 1111 | 1023  |  |

| +1022/1024 | 011 1111 1110                                         | 0000 0011 1111 1110                                                                                 | 1022 | 0000 0001 1111 1110 | 1022  |  |

|            | •••                                                   |                                                                                                     |      |                     |       |  |

| +1/1024    | 000 0000 0001                                         | 0000 0000 0000 0001                                                                                 | 1    | 0000 0000 0000 0001 | 1     |  |

| 0/1024     | 000 0000 0000                                         | 0000 0000 0000 0000                                                                                 | 0    | 0000 0000 0000 0000 | 0     |  |

| -1/1024    | 101 1111 1111                                         | 0000 0000 0000 0000                                                                                 | 0    | 1111 1111 1111 1111 | -1    |  |

|            | •••                                                   |                                                                                                     |      |                     |       |  |

| -1023/1024 | 100 0000 0001                                         | 0000 0000 0000 0000                                                                                 | 0    | 1111 1110 0000 0001 | -1023 |  |

| -1024/1024 | 100 0000 0000                                         | 0000 0000 0000 0000                                                                                 | 0    | 1111 1110 0000 0000 | -1024 |  |

### 20.0 8-BIT DIGITAL-TO-ANALOG CONVERTER (DAC)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the *"PIC24F Family Reference Manual"*. Device-specific information in this data sheet supersedes the information in the *"PIC24F Family Reference Manual"*.

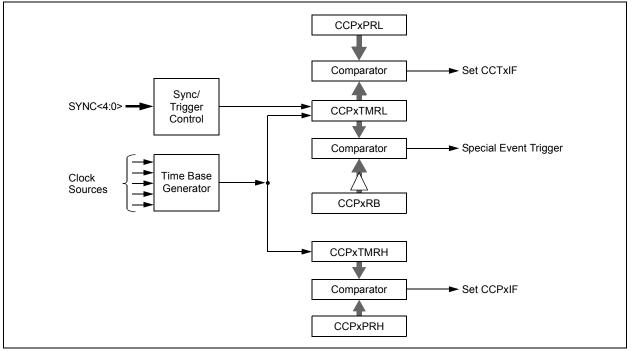

PIC24FV16KM204 family devices include two 8-bit Digital-to-Analog Converters (DACs) for generating analog outputs from digital data. A simplified block diagram for a single DAC is shown in Figure 20-1. Both of the DACs are identical. The DAC generates an analog output voltage based on the digital input code, according to the formula:

$V \text{DAC} = \frac{V \text{DACREF} \times \text{DACxDAT}}{256}$

where *V*DAC is the analog output voltage and *V*DACREF is the reference voltage selected by DACREF<1:0>.

Each DAC includes these features:

- Precision 8-bit resistor ladder for high accuracy

- Fast settling time, supporting 1 Msps effective sampling rates

- · Buffered output voltage

- Three user-selectable voltage reference options

- Multiple conversion Trigger options, plus a manual convert-on-write option

- · Left and right justified input data options

- User-selectable Sleep and Idle mode operation

When using the DAC, it is recommended to set the ANSx and TRISx bits for the DACx output pin to configure it as an analog output. See **Section 11.2** "**Configuring Analog Port Pins**" for more information.

#### FIGURE 20-1: SINGLE DACX SIMPLIFIED BLOCK DIAGRAM

#### REGISTER 20-1: DACxCON: DACx CONTROL REGISTER (CONTINUED)

- bit 6-2 DACTSEL<4:0>: DACx Trigger Source Select bits

- 11101-11111 = Unused 11100 = CTMU 11011 = A/D 11010 = Comparator 3 11001 = Comparator 2 11000 = Comparator 1 10011 to 10111 = Unused 10010 = CLC2 output 10001 = CLC1 output 01100 to 10000 = Unused 01011 = Timer1 Sync output 01010 = External Interrupt 2 01001 = External Interrupt 1 01000 = External Interrupt 0 0011x = Unused 00101 = MCCP5 or SCCP5 Sync output 00100 = MCCP4 or SCCP4 Sync output 00011 = MCCP3 or SCCP3 Sync output 00010 = MCCP2 or SCCP2 Sync output 00001 = MCCP1 or SCCP1 Sync output 00000 = Unused DACREF<1:0>: DACx Reference Source Select bits 11 = Internal Band Gap Buffer 1 (BGBUF1)<sup>(1)</sup>

- 10 = AVDD

bit 1-0

- 01 = DVREF+

- 00 = Reference is not connected (lowest power but no DAC functionality)

- **Note 1:** BGBUF1 voltage is configured by BUFREF<1:0> (BUFCON0<1:0>).

#### REGISTER 25-4: FOSC: OSCILLATOR CONFIGURATION REGISTER

| R/P-1  | R/P-1  | R/P-1   | R/P-1     | R/P-1     | R/P-1    | R/P-1   | R/P-1   |

|--------|--------|---------|-----------|-----------|----------|---------|---------|

| FCKSM1 | FCKSM0 | SOSCSEL | POSCFREQ1 | POSCFREQ0 | OSCIOFNC | POSCMD1 | POSCMD0 |

| bit 7  |        |         |           |           |          |         | bit 0   |

| Legend:           |                      |                            |                    |

|-------------------|----------------------|----------------------------|--------------------|

| R = Readable bit  | P = Programmable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared       | x = Bit is unknown |

| bit 7-6 | <b>FCKSM&lt;1:0&gt;:</b> Clock Switching and Fail-Safe Clock Monitor Selection Configuration bits<br>1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled<br>01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled<br>00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled                                            |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5   | <b>SOSCSEL:</b> Secondary Oscillator Power Selection Configuration bit<br>1 = Secondary Oscillator is configured for high-power operation<br>0 = Secondary Oscillator is configured for low-power operation                                                                                                                                                          |

| bit 4-3 | <b>POSCFREQ&lt;1:0&gt;:</b> Primary Oscillator Frequency Range Configuration bits<br>11 = Primary Oscillator/External Clock input frequency is greater than 8 MHz<br>10 = Primary Oscillator/External Clock input frequency is between 100 kHz and 8 MHz<br>01 = Primary Oscillator/External Clock input frequency is less than 100 kHz<br>00 = Reserved; do not use |

| bit 2   | <ul> <li>OSCIOFNC: CLKO Enable Configuration bit</li> <li>1 = CLKO output signal is active on the OSCO pin; Primary Oscillator must be disabled or configured for the External Clock (EC) mode for the CLKO to be active (POSCMD&lt;1:0&gt; = 11 or 00)</li> <li>0 = CLKO output is disabled</li> </ul>                                                              |

| bit 1-0 | POSCMD<1:0>: Primary Oscillator Configuration bits<br>11 = Primary Oscillator mode is disabled<br>10 = HS Oscillator mode is selected<br>01 = XT Oscillator mode is selected                                                                                                                                                                                         |

00 = External Clock mode is selected

#### 26.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 26.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

#### 26.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

#### 26.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

#### 26.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

#### 26.11 Demonstration/Development Boards, Evaluation Kits and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

### 26.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

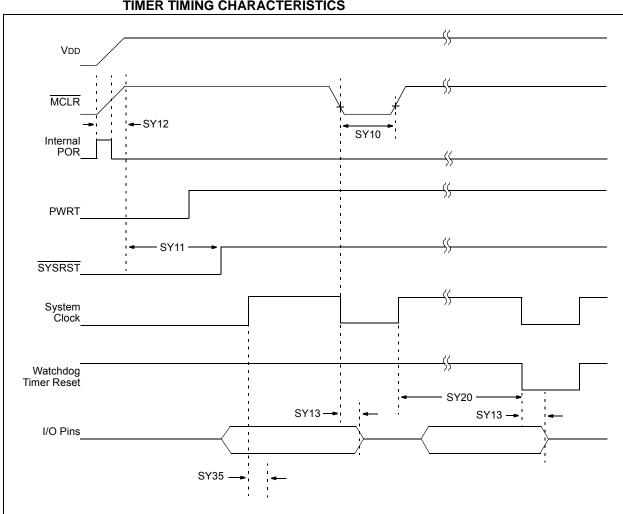

## FIGURE 27-8: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING CHARACTERISTICS

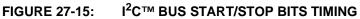

## TABLE 27-33: I<sup>2</sup>C<sup>™</sup> BUS START/STOP BITS REQUIREMENTS (SLAVE MODE)

| Param.<br>No. | Symbol  | Characte        | ristic       | Min  | Max | Units | Conditions                   |    |  |                          |

|---------------|---------|-----------------|--------------|------|-----|-------|------------------------------|----|--|--------------------------|

| 90            | TSU:STA | Start Condition | 100 kHz mode | 4700 |     | ns    | Only relevant for Repeated   |    |  |                          |

|               |         | Setup Time      | 400 kHz mode | 600  | _   |       | Start condition              |    |  |                          |

| 91            | THD:STA | Start Condition | 100 kHz mode | 4000 | —   | ns    | After this period, the first |    |  |                          |

|               |         | Hold Time       | 400 kHz mode | 600  | _   |       |                              |    |  | clock pulse is generated |

| 92            | Tsu:sto | Stop Condition  | 100 kHz mode | 4700 | _   | ns    | ns                           | ns |  |                          |

|               |         | Setup Time      | 400 kHz mode | 600  | —   |       |                              |    |  |                          |

| 93            | THD:STO | Stop Condition  | 100 kHz mode | 4000 | _   | ns    |                              |    |  |                          |

|               |         | Hold Time       | 400 kHz mode | 600  | _   |       |                              |    |  |                          |

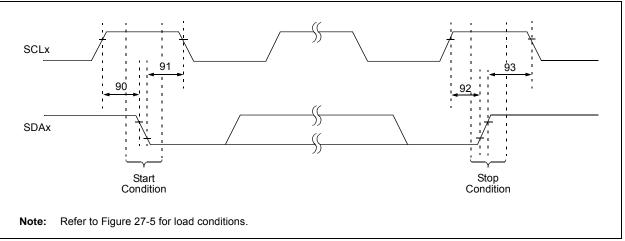

#### FIGURE 27-16: I<sup>2</sup>C<sup>™</sup> BUS DATA TIMING

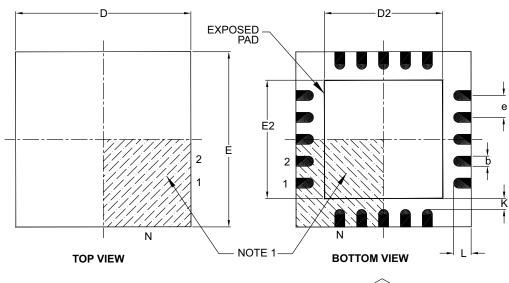

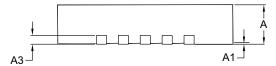

#### 20-Lead Plastic Quad Flat, No Lead Package (ML) – 4x4x0.9 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units     |                | MILLIMETERS | 6    |

|------------------------|-----------|----------------|-------------|------|

| Dimensi                | on Limits | MIN            | NOM         | MAX  |

| Number of Pins         | N         | 20             |             |      |

| Pitch                  | е         |                | 0.50 BSC    |      |

| Overall Height         | Α         | 0.80           | 0.90        | 1.00 |

| Standoff               | A1        | 0.00           | 0.02        | 0.05 |

| Contact Thickness      | A3        | 0.20 REF       |             |      |

| Overall Width          | E         | 4.00 BSC       |             |      |

| Exposed Pad Width      | E2        | 2.60 2.70 2.80 |             |      |

| Overall Length         | D         | 4.00 BSC       |             |      |

| Exposed Pad Length     | D2        | 2.60           | 2.70        | 2.80 |

| Contact Width          | b         | 0.18           | 0.25        | 0.30 |

| Contact Length         | L         | 0.30           | 0.40        | 0.50 |

| Contact-to-Exposed Pad | К         | 0.20           | -           | _    |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-126B

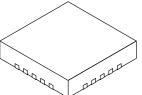

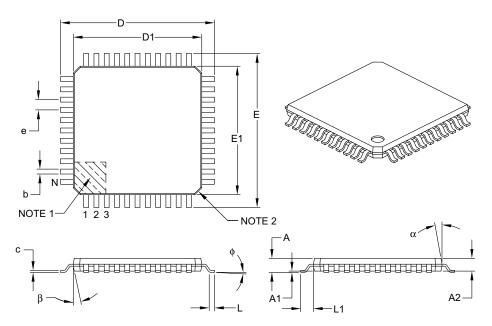

#### 44-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units       |           | MILLIMETERS | 6    |

|--------------------------|-------------|-----------|-------------|------|

| Dimens                   | sion Limits | MIN       | NOM         | MAX  |

| Number of Leads N        |             |           | 44          |      |

| Lead Pitch               | е           | 0.80 BSC  |             |      |

| Overall Height           | А           | -         | -           | 1.20 |

| Molded Package Thickness | A2          | 0.95      | 1.00        | 1.05 |

| Standoff                 | A1          | 0.05      | -           | 0.15 |

| Foot Length              | L           | 0.45      | 0.60        | 0.75 |

| Footprint                | L1          |           | 1.00 REF    |      |

| Foot Angle               | ф           | 0°        | 3.5°        | 7°   |

| Overall Width            | E           | 12.00 BSC |             |      |

| Overall Length           | D           | 12.00 BSC |             |      |

| Molded Package Width     | E1          | 10.00 BSC |             |      |

| Molded Package Length    | D1          | 10.00 BSC |             |      |

| Lead Thickness           | С           | 0.09      | -           | 0.20 |

| Lead Width               | b           | 0.30      | 0.37        | 0.45 |

| Mold Draft Angle Top     | α           | 11°       | 12°         | 13°  |

| Mold Draft Angle Bottom  | β           | 11°       | 12°         | 13°  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-076B

#### INDEX

| 1 | • |

|---|---|

| r | ١ |

| A/D                                               |       |

|---------------------------------------------------|-------|

| Buffer Data Formats                               | . 225 |

| Control Registers                                 | . 212 |

| AD1CHITH/L                                        | . 212 |

| AD1CHS                                            | . 212 |

| AD1CON1                                           | . 212 |

| AD1CON2                                           | . 212 |

| AD1CON3                                           | . 212 |

| AD1CON5                                           | . 212 |

| AD1CSSH/L                                         | . 212 |

| AD1CTMENH/L                                       | . 212 |

| Sampling Requirements                             | . 223 |

| Transfer Function                                 | . 224 |

| AC Characteristics                                |       |

| 8-Bit DAC Specifications                          | . 296 |

| A/D Conversion Requirements                       | . 295 |

| A/D Module Specifications                         | . 294 |

| Capacitive Loading Requirements on                |       |

| Output Pins                                       | . 279 |

| CLKO and I/O Requirements                         | . 282 |

| External Clock Requirements                       | . 280 |

| Internal RC Accuracy                              | . 281 |

| Internal RC Oscillator Specifications             | . 281 |

| Load Conditions and Requirements                  | . 279 |

| PLL Clock Specification                           | . 281 |

| Reset, Watchdog Timer. Oscillator Start-up Timer, |       |

| Power-up Timer, Brown-out Reset                   |       |

| Requirements                                      | . 284 |

| Temperature and Voltage Specifications            | . 279 |

| Assembler                                         |       |

| MPASM Assembler                                   | . 262 |

|                                                   |       |

### В

| Block Diagrams                                   |         |

|--------------------------------------------------|---------|

| 12-Bit A/D Converter                             | 210     |

| 12-Bit A/D Converter Analog Input Model          | 223     |

| 16-Bit Timer1                                    |         |

| 32-Bit Timer Mode                                | 146     |

| Accessing Program Memory with                    |         |

| Table Instructions                               | 65      |

| CALL Stack Frame                                 | 63      |

| CLCx Input Source Selection                      |         |

| CLCx Logic Function Combinatorial Options        | 196     |

| CLCx Module                                      | 195     |

| Comparator Voltage Reference                     | 239     |

| Comparator x Module                              |         |

| Conceptual MCCPx/SCCPx Modules                   | 143     |

| CPU Programmer's Model                           | 37      |

| CTMU Connections, Internal Configuration for     |         |

| Capacitance Measurement                          | 242     |

| CTMU Connections, Internal Configuration for     |         |

| Pulse Delay Generation                           | 243     |

| CTMU Connections, Internal Configuration for     |         |

| Time Measurement                                 |         |

| Data Access from Program Space Address Gen<br>64 | eration |

| Data EEPROM Addressing with TBLPAG and           |         |

| NVM Registers                                    | 75      |

| Dual 16-Bit Timer Mode                           | 145     |

| High/Low-Voltage Detect (HLVD)                   | 207     |

| Individual Comparator Configurations             | 236     |

| Input Capture x Module                           | 148     |

|                                                  |         |

| MCLR Pin Connections Example           | 30  |

|----------------------------------------|-----|

| MSSPx (I <sup>2</sup> C Master Mode)   | 161 |

| MSSPx (I <sup>2</sup> C Mode)          | 161 |

| MSSPx (SPI Mode)                       | 160 |

| On-Chip Voltage Regulator Connections  | 257 |

| Output Compare x Module                | 147 |

| PIC24F CPU Core                        | 36  |

| PIC24FXXXXX Family (General)           | 19  |

| PSV Operation                          |     |

| Recommended Minimum Connections        | 29  |

| Reset System                           | 79  |

| RTCC Module                            |     |

| Series Resistor                        | 132 |

| Shared I/O Port Structure              | 137 |

| Simplified Single DACx Module          | 229 |

| Simplified UARTx                       | 173 |

| Single Operational Amplifier           | 233 |

| SPI Master/Slave Connection            | 160 |

| Suggested Oscillator Circuit Placement | 33  |

| System Clock                           |     |

| Table Register Addressing              | 67  |

| Timer Clock Generator                  | 144 |

| Watchdog Timer (WDT)                   | 258 |

| Brown-out Reset                        |     |

| Trip Points                            |     |

#### С

| C Compilers                                      |

|--------------------------------------------------|

| MPLAB XC Compilers                               |

| Capture/Compare/PWM/Timer                        |

| Auxiliary Output 149                             |

| General Purpose Timer 145                        |

| Input Capture Mode 148                           |

| Output Compare Mode 147                          |

| Synchronization Sources 153                      |

| Time Base Generator 144                          |

| Capture/Compare/PWM/Timer (MCCP, SCCP) 143       |

| Charge Time Measurement Unit. See CTMU.          |

| CLC                                              |

| Control Registers 198                            |

| Code Examples                                    |

| Assembly Code Sequence for Clock Switching 128   |

| C Code Power-Saving Entry 131                    |

| C Code Sequence for Clock Switching 128          |

| Data EEPROM Bulk Erase 77                        |

| Data EEPROM Unlock Sequence                      |

| Erasing a Program Memory Row,                    |

| Assembly Language                                |

| Erasing a Program Memory Row, C Language 70      |

| I/O Port Write/Read 140                          |

| Initiating a Programming Sequence,               |

| Assembly Language72                              |

| Initiating a Programming Sequence, C Language 72 |

| Loading the Write Buffers, Assembly Language 71  |

| Loading the Write Buffers, C Language            |

| Reading Data EEPROM Using                        |

| TBLRD Command78                                  |

| Setting the RTCWREN Bit in 'C' 182               |

| Setting the RTCWREN Bit in Assembly 182          |

| Single-Word Erase                                |

| Single-Word Write to Data EEPROM                 |

| Ultra Low-Power Wake-up Initialization           |

| Code Protection                                  |

| Comparator 235                                   |

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

## QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MTP, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.