Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                      |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 23                                                                            |

| Program Memory Size        | 16KB (5.5K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 1K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5V                                                                       |

| Data Converters            | A/D 19x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                |

| Supplier Device Package    | 28-SOIC                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fv16km102-e-so |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

FIGURE 2-1:

# 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT MICROCONTROLLERS

# 2.1 Basic Connection Requirements

Getting started with the PIC24FV16KM204 family of 16-bit microcontrollers requires attention to a minimal set of device pin connections before proceeding with development.

The following pins must always be connected:

- All VDD and Vss pins (see Section 2.2 "Power Supply Pins")

- All AVDD and AVss pins, regardless of whether or not the analog device features are used (see Section 2.2 "Power Supply Pins")

- MCLR pin (see Section 2.3 "Master Clear (MCLR) Pin")

- VCAP pins (see Section 2.4 "Voltage Regulator Pin (VCAP)")

These pins must also be connected if they are being used in the end application:

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.5 "ICSP Pins**")

- OSCI and OSCO pins when an external oscillator source is used

(see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins are used when external voltage reference for analog modules is implemented

**Note:** The AVDD and AVss pins must always be connected, regardless of whether any of the analog modules are being used.

The minimum mandatory connections are shown in Figure 2-1.

#### **MINIMUM CONNECTIONS** C2<sup>(2)</sup> Vdd Vss ₹R1 VDD R2 MCLR VCAP (1) C1 PIC24FV16KM204 Vdd Vss C6<sup>(2)</sup> C3(2) VDD Vss AVDD AVSS /SS 20/

RECOMMENDED

#### Key (all values are recommendations):

C5<sup>(2)</sup>

C1 through C6: 0.1  $\mu\text{F},$  20V ceramic

C7: 10 µF, 16V tantalum or ceramic

R1: 10 kΩ

R2: 100Ω to 470Ω

- Note 1: See Section 2.4 "Voltage Regulator Pin (VCAP)" for an explanation of VCAP pin connections.

- 2: The example shown is for a PIC24F device with five VDD/Vss and AVDD/AVss pairs. Other devices may have more or less pairs; adjust the number of decoupling capacitors appropriately.

C4(2)

NOTES:

#### TABLE 4-6: TIMER1 REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14               | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9          | Bit 8  | Bit 7        | Bit 6 | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|--------|----------------------|--------|--------|--------|--------|----------------|--------|--------------|-------|--------|--------|-------|-------|-------|-------|---------------|

| TMR1      | 100h  |        | Timer1 Register xxxx |        |        |        |        |                |        |              |       |        |        |       |       |       |       |               |

| PR1       | 102h  |        |                      |        |        |        |        |                | Timer1 | Period Regis | ster  |        |        |       |       |       |       | FFFF          |

| T1CON     | 104h  | TON    | —                    | TSIDL  | _      | _      | _      | TECS1          | TECS0  | _            | TGATE | TCKPS1 | TCKPS0 | _     | TSYNC | TCS   | _     | 0000          |

| Lanandi   |       |        | le ave a a d         |        |        |        |        | and the second |        |              |       |        |        |       |       |       |       |               |

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition, r = reserved.

# TABLE 4-7: CLC1-2 REGISTER MAP

| File Name               | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| CLC1CONL                | 122h  | LCEN   | —      | _      | —      | INTP   | INTN   | —     | —     | LCOE  | LCOUT | LCPOL | —     | _     | MODE2 | MODE1 | MODE0 | 0000          |

| CLC1CONH                | 124h  | _      | _      |        | _      | _      | _      | _     | _     | _     | _     | _     | _     | G4POL | G3POL | G2POL | G1POL | 0000          |

| CLC1SEL                 | 126h  | _      | DS42   | DS41   | DS40   |        | DS32   | DS31  | DS30  | —     | DS22  | DS21  | DS20  | _     | DS12  | DS11  | DS10  | 0000          |

| CLC1GLSL                | 12Ah  | G2D4T  | G2D4N  | G2D3T  | G2D3N  | G2D2T  | G2D2N  | G2D1T | G2D1N | G1D4T | G1D4N | G1D3T | G1D3N | G1D2T | G1D2N | G1D1T | G1D1N | 0000          |

| CLC1GLSH                | 12Ch  | G4D4T  | G4D4N  | G4D3T  | G4D3N  | G4D2T  | G4D2N  | G4D1T | G4D1N | G3D4T | G3D4N | G3D3T | G3D3N | G3D2T | G3D2N | G3D1T | G3D1N | 0000          |

| CLC2CONL <sup>(1)</sup> | 12Eh  | LCEN   | _      | -      | _      | INTP   | INTN   | _     | _     | LCOE  | LCOUT | LCPOL | _     | _     | MODE2 | MODE1 | MODE0 | 0000          |

| CLC2CONH <sup>(1)</sup> | 130h  | —      | —      | _      | —      | _      | _      | —     | _     | _     | _     | _     | —     | G4POL | G3POL | G2POL | G1POL | 0000          |

| CLC2SEL <sup>(1)</sup>  | 132h  | —      | DS42   | DS41   | DS40   | _      | DS32   | DS31  | DS30  | _     | DS22  | DS21  | DS20  | —     | DS12  | DS11  | DS10  | 0000          |

| CLC2GLSL <sup>(1)</sup> | 136h  | G2D4T  | G2D4N  | G2D3T  | G2D3N  | G2D2T  | G2D2N  | G2D1T | G2D1N | G1D4T | G1D4N | G1D3T | G1D3N | G1D2T | G1D2N | G1D1T | G1D1N | 0000          |

| CLC2GLSH <sup>(1)</sup> | 138h  | G4D4T  | G4D4N  | G4D3T  | G4D3N  | G4D2T  | G4D2N  | G4D1T | G4D1N | G3D4T | G3D4N | G3D3T | G3D3N | G3D2T | G3D2N | G3D1T | G3D1N | 0000          |

**Legend:** x = unknown, u = unchanged, --- = unimplemented, q = value depends on condition, r = reserved.

Note 1: These registers are available only on PIC24F(V)16KM2XX devices.

## TABLE 4-8: MCCP1 REGISTER MAP

| File Name | Addr. | Bit 15  | Bit 14                                                                                             | Bit 13  | Bit 12 | Bit 11  | Bit 10  | Bit 9   | Bit 8       | Bit 7        | Bit 6        | Bit 5  | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Rese |

|-----------|-------|---------|----------------------------------------------------------------------------------------------------|---------|--------|---------|---------|---------|-------------|--------------|--------------|--------|---------|---------|---------|---------|---------|-------------|

| CCP1CON1L | 140h  | CCPON   | —                                                                                                  | CCPSIDL | r      | TMRSYNC | CLKSEL2 | CLKSEL1 | CLKSEL0     | TMRPS1       | TMRPS0       | T32    | CCSEL   | MOD3    | MOD2    | MOD1    | MOD0    | 0000        |

| CCP1CON1H | 142h  | OPSSRC  | SRC RTRGEN <u>– –</u> OPS3 OPS2 OPS1 OPS0 TRIGEN ONESHOT ALTSYNC SYNC4 SYNC3 SYNC2 SYNC1 SYNC0 000 |         |        |         |         |         |             |              |              | 0000   |         |         |         |         |         |             |

| CCP1CON2L | 144h  | PWMRSEN | ASDGM                                                                                              | _       | SSDG   | _       | _       | _       | _           | ASDG7        | ASDG6        | ASDG5  | ASDG4   | ASDG3   | ASDG2   | ASDG1   | ASDG0   | 0000        |

| CCP1CON2H | 146h  | OENSYNC | _                                                                                                  | OCFEN   | OCEEN  | OCDEN   | OCCEN   | OCBEN   | OCAEN       | ICGSM1       | ICGSM0       | _      | AUXOUT1 | AUXOUT0 | ICS2    | ICS1    | ICS0    | 0100        |

| CCP1CON3L | 148h  | _       | _                                                                                                  | _       | _      | _       | _       | _       | _           | _            |              | DT5    | DT4     | DT3     | DT2     | DT1     | DT0     | 0000        |

| CCP1CON3H | 14Ah  | OETRIG  | OSCNT2                                                                                             | OSCNT1  | OSCNT0 | _       | OUTM2   | OUTM1   | OUTM0       | _            | _            | POLACE | POLBDF  | PSSACE1 | PSSACE0 | PSSBDF1 | PSSBDF0 | 0000        |

| CCP1STATL | 14Ch  | _       | _                                                                                                  | _       | _      | _       | _       | _       | _           | CCPTRIG      | TRSET        | TRCLR  | ASEVT   | SCEVT   | ICDIS   | ICOV    | ICBNE   | 0000        |

| CCP1TMRL  | 150h  |         |                                                                                                    |         |        |         |         | MCCI    | P1 Time Ba  | se Register  | Low Word     |        |         |         |         |         |         | 0000        |

| CCP1TMRH  | 152h  |         |                                                                                                    |         |        |         |         | MCCF    | P1 Time Ba  | se Register  | High Word    |        |         |         |         |         |         | 0000        |

| CCP1PRL   | 154h  |         |                                                                                                    |         |        |         |         | MCCP1   | Fime Base F | Period Regis | ster Low Wor | ď      |         |         |         |         |         | FFFF        |

| CCP1PRH   | 156h  |         |                                                                                                    |         |        |         |         | MCCP1 T | īme Base F  | Period Regis | ster High Wo | rd     |         |         |         |         |         | FFFF        |

| CCP1RAL   | 158h  |         | Output Compare 1 Data Word A 000                                                                   |         |        |         |         |         |             |              | 0000         |        |         |         |         |         |         |             |

| CCP1RBL   | 15Ch  |         | Output Compare 1 Data Word B 000                                                                   |         |        |         |         |         |             |              | 0000         |        |         |         |         |         |         |             |

| CCP1BUFL  | 160h  |         | Input Capture 1 Data Buffer Low Word                                                               |         |        |         |         |         |             |              | 0000         |        |         |         |         |         |         |             |

| CCP1BUFH  | 162h  |         |                                                                                                    |         |        |         |         | Input   | Capture 1   | Data Buffer  | High Word    |        |         |         |         |         |         | 0000        |

Legend: x = unknown, u = unchanged, --- = unimplemented, q = value depends on condition, r = reserved.

# TABLE 4-12: SCCP5 REGISTER MAP

| File Name                | Addr. | Bit 15  | Bit 14                                | Bit 13  | Bit 12 | Bit 11  | Bit 10  | Bit 9     | Bit 8       | Bit 7        | Bit 6      | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1  | Bit 0  | All<br>Resets |

|--------------------------|-------|---------|---------------------------------------|---------|--------|---------|---------|-----------|-------------|--------------|------------|---------|---------|---------|---------|--------|--------|---------------|

| CCP5CON1L <sup>(1)</sup> | 1D0h  | CCPON   | _                                     | CCPSIDL | r      | TMRSYNC | CLKSEL2 | CLKSEL1   | CLKSEL0     | TMRPS1       | TMRPS0     | T32     | CCSEL   | MOD3    | MOD2    | MOD1   | MOD0   | 0000          |

| CCP5CON1H(1)             | 1D2h  | OPSSRC  | RTRGEN                                | _       | _      | IOPS3   | IOPS2   | IOPS1     | IOPS0       | TRIGEN       | ONESHOT    | ALTSYNC | SYNC4   | SYNC3   | SYNC2   | SYNC1  | SYNC0  | 0000          |

| CCP5CON2L <sup>(1)</sup> | 1D4h  | PWMRSEN | ASDGM                                 | _       | SSDG   | _       | _       | _         | _           | ASDG7        | ASDG6      | ASDG5   | ASDG4   | ASDG3   | ASDG2   | ASDG1  | ASDG0  | 0000          |

| CCP5CON2H(1)             | 1D6h  | OENSYNC | _                                     | _       | _      | _       | _       | _         | OCAEN       | ICGSM1       | ICGSM0     | _       | AUXOUT1 | AUXOUT0 | ICSEL2  | ICSEL1 | ICSEL0 | 0100          |

| CCP5CON3H <sup>(1)</sup> | 1DAh  | OETRIG  | OSCNT2                                | OSCNT1  | OSCNT0 | -       | _       | _         | _           | _            | _          | POLACE  | _       | PSSACE1 | PSSACE0 | _      | _      | 0000          |

| CCP5STATL <sup>(1)</sup> | 1DCh  | -       | _                                     | _       | —      | -       | _       | _         | _           | CCPTRIG      | TRSET      | TRCLR   | ASEVT   | SCEVT   | ICDIS   | ICOV   | ICBNE  | 0000          |

| CCP5TMRL <sup>(1)</sup>  | 1E0h  |         |                                       |         |        |         |         | SCCP5     | i Time Base | Register Lo  | w Word     |         |         |         |         |        |        | 0000          |

| CCP5TMRH <sup>(1)</sup>  | 1E2h  |         |                                       |         |        |         |         | SCCP5     | Time Base   | Register Hig | gh Word    |         |         |         |         |        |        | 0000          |

| CCP5PRL <sup>(1)</sup>   | 1E4h  |         |                                       |         |        |         |         | SCCP5 Tir | ne Base Pe  | iod Register | r Low Word |         |         |         |         |        |        | FFFF          |

| CCP5PRH <sup>(1)</sup>   | 1E6h  |         |                                       |         |        |         |         | SCCP5 Tin | ne Base Per | iod Register | High Word  |         |         |         |         |        |        | FFFF          |

| CCP5RAL <sup>(1)</sup>   | 1E8h  |         |                                       |         |        |         |         | Out       | put Compar  | e 5 Data Wo  | rd A       |         |         |         |         |        |        | 0000          |

| CCP5RBL <sup>(1)</sup>   | 1ECh  |         | Output Compare 5 Data Word B 000      |         |        |         |         |           |             |              |            | 0000    |         |         |         |        |        |               |

| CCP5BUFL <sup>(1)</sup>  | 1F0h  |         | Input Capture 5 Data Buffer Low Word  |         |        |         |         |           |             |              |            | 0000    |         |         |         |        |        |               |

| CCP5BUFH <sup>(1)</sup>  | 1F2h  |         | Input Capture 5 Data Buffer High Word |         |        |         |         |           |             |              |            | 0000    |         |         |         |        |        |               |

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

Note 1: These registers are available only on PIC24F(V)16KM2XX devices.

#### REGISTER 8-33: IPC20: INTERRUPT PRIORITY CONTROL REGISTER 20

| U-0           | U-0        | U-0              | U-0          | U-0                                     | U-0              | U-0      | U-0      |  |  |  |  |

|---------------|------------|------------------|--------------|-----------------------------------------|------------------|----------|----------|--|--|--|--|

| —             | —          | —                | —            | —                                       | —                | —        | —        |  |  |  |  |

| bit 15        |            |                  |              |                                         |                  |          | bit 8    |  |  |  |  |

|               |            |                  |              |                                         |                  |          |          |  |  |  |  |

| U-0           | U-0        | U-0              | U-0          | U-0                                     | R/W-1            | R/W-0    | R/W-0    |  |  |  |  |

| _             | _          | _                | _            | —                                       | ULPWUIP2         | ULPWUIP1 | ULPWUIP0 |  |  |  |  |

| bit 7         |            |                  |              |                                         |                  |          | bit 0    |  |  |  |  |

| Legend:       |            |                  |              |                                         |                  |          |          |  |  |  |  |

| R = Readable  | e bit      | W = Writable     | bit          | U = Unimplem                            | nented bit, read | l as '0' |          |  |  |  |  |

| -n = Value at | POR        | '1' = Bit is set |              | '0' = Bit is cleared x = Bit is unknown |                  |          |          |  |  |  |  |

|               |            |                  |              |                                         |                  |          |          |  |  |  |  |

| bit 15-3      | Unimplemer | ted: Read as '0  | )'           |                                         |                  |          |          |  |  |  |  |

| bit 2-0       | ULPWUIP<2  | :0>: Ultra Low-F | Power Wake-u | p Interrupt Prior                       | rity bits        |          |          |  |  |  |  |

111 = Interrupt is Priority 7 (highest priority interrupt)

- •

- 001 = Interrupt is Priority 1

000 = Interrupt source is disabled

# REGISTER 8-34: IPC24: INTERRUPT PRIORITY CONTROL REGISTER 24

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | R/W-1   | R/W-0   | R/W-0   | U-0 | R/W-1   | R/W-0   | R/W-0   |

|-------|---------|---------|---------|-----|---------|---------|---------|

| —     | CLC2IP2 | CLC2IP1 | CLC2IP0 | —   | CLC1IP2 | CLC1IP1 | CLC1IP0 |

| bit 7 |         |         |         |     |         |         | bit 0   |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 15-7 | Unimplemented: Read as '0'                                 |

|----------|------------------------------------------------------------|

| bit 6-4  | CLC2IP<2:0>: CLC2 Interrupt Priority bits                  |

|          | 111 = Interrupt is Priority 7 (highest priority interrupt) |

|          | •                                                          |

|          | •                                                          |

|          | •                                                          |

|          | 001 = Interrupt is Priority 1                              |

|          | 000 = Interrupt source is disabled                         |

| bit 3    | Unimplemented: Read as '0'                                 |

| bit 2-0  | CLC1IP<2:0>: CLC1 Interrupt Priority bits                  |

|          | 111 = Interrupt is Priority 7 (highest priority interrupt) |

|          | •                                                          |

|          | •                                                          |

|          | •                                                          |

|          | 001 = Interrupt is Priority 1                              |

|          | 000 = Interrupt source is disabled                         |

|          |                                                            |

## REGISTER 10-1: ULPWCON: ULPWU CONTROL REGISTER

| R/W-0         | U-0                                         | R/W-0            | U-0             | U-0               | U-0             | U-0             | R/W-0          |  |  |

|---------------|---------------------------------------------|------------------|-----------------|-------------------|-----------------|-----------------|----------------|--|--|

| ULPEN         |                                             | ULPSIDL          | _               | —                 | _               | _               | ULPSINK        |  |  |

| bit 15        |                                             |                  |                 |                   |                 |                 | bit 8          |  |  |

|               |                                             |                  |                 |                   |                 |                 |                |  |  |

| U-0           | U-0                                         | U-0              | U-0             | U-0               | U-0             | U-0             | U-0            |  |  |

| _             | _                                           | —                |                 | —                 | _               | _               | —              |  |  |

| bit 7         | ·                                           | · · ·            |                 |                   |                 |                 | bit 0          |  |  |

|               |                                             |                  |                 |                   |                 |                 |                |  |  |

| Legend:       |                                             |                  |                 |                   |                 |                 |                |  |  |

| R = Readabl   | le bit                                      | W = Writable b   | it              | U = Unimplen      | nented bit, rea | d as '0'        |                |  |  |

| -n = Value at | POR                                         | '1' = Bit is set |                 | '0' = Bit is clea | ared            | x = Bit is unkr | Bit is unknown |  |  |

|               |                                             |                  |                 |                   |                 |                 |                |  |  |

| bit 15        | ULPEN: ULF                                  | PWU Module En    | able bit        |                   |                 |                 |                |  |  |

|               | 1 = Module i                                |                  |                 |                   |                 |                 |                |  |  |

|               | 0 = Module i                                | s disabled       |                 |                   |                 |                 |                |  |  |

| bit 14        | Unimpleme                                   | nted: Read as '0 | ,               |                   |                 |                 |                |  |  |

| bit 13        | ULPSIDL: U                                  | LPWU Stop in Ic  | lle Select bit  |                   |                 |                 |                |  |  |

|               |                                             | nues module ope  |                 |                   | Idle mode       |                 |                |  |  |

|               | 0 = Continues module operation in Idle mode |                  |                 |                   |                 |                 |                |  |  |

| bit 12-9      | Unimplemented: Read as '0'                  |                  |                 |                   |                 |                 |                |  |  |

| bit 8         | ULPSINK: U                                  | ILPWU Current S  | Sink Enable bit |                   |                 |                 |                |  |  |

|               | 1 = Current s                               | sink is enabled  |                 |                   |                 |                 |                |  |  |

|               | 0 = Current s                               | sink is disabled |                 |                   |                 |                 |                |  |  |

| bit 7-0       | Unimpleme                                   | nted: Read as '0 | 3               |                   |                 |                 |                |  |  |

# 11.2.2 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation, and a read operation of the same port. Typically, this instruction would be a NOP.

# 11.3 Input Change Notification (ICN)

The Input Change Notification function of the I/O ports allows the PIC24FXXXXX family of devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature is capable of detecting input Change-of-States, even in Sleep mode, when the clocks are disabled. Depending on the device pin count, there are up to 37 external signals (CN0 through CN36) that may be selected (enabled) for generating an interrupt request on a Change-of-State.

There are six control registers associated with the CN module. The CNEN1 and CNEN3 registers contain the interrupt enable control bits for each of the CNx input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each CNx pin also has a weak pull-up/pull-down connected to it. The pull-ups act as a current source that is connected to the pin. The pull-downs act as a current sink to eliminate the need for external resistors when push button or keypad devices are connected.

On any pin, only the pull-up resistor or the pull-down resistor should be enabled, but not both of them. If the push button or the keypad is connected to VDD, enable the pull-down, or if they are connected to VSS, enable the pull-up resistors. The pull-ups are enabled separately using the CNPU1 and CNPU3 registers, which contain the control bits for each of the CNx pins.

Setting any of the control bits enables the weak pull-ups for the corresponding pins. The pull-downs are enabled separately using the CNPD1 and CNPD3 registers, which contain the control bits for each of the CNx pins. Setting any of the control bits enables the weak pull-downs for the corresponding pins.

When the internal pull-up is selected, the pin uses VDD as the pull-up source voltage. When the internal pull-down is selected, the pins are pulled down to Vss by an internal resistor. Make sure that there is no external pull-up source/pull-down sink when the internal pull-ups/pull-downs are enabled.

Note: Pull-ups and pull-downs on Change Notification (CN) pins should always be disabled whenever the port pin is configured as a digital output.

# EXAMPLE 11-1: PORT WRITE/READ EXAMPLE

| MOV 0xFF00, W0;<br>MOV W0, TRISB;                                                 | //Configure PORTB<15:8> as inputs and PORTB<7:0> as outputs                                                                         |

|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| NOP ;                                                                             | //Delay 1 cycle                                                                                                                     |

| BTSS PORTB, #13;                                                                  | //Next Instruction                                                                                                                  |

| <pre>Equivalent `C' Code TRISB = 0xFF00; NOP(); if(PORTBbits.RB13 == 1) { }</pre> | //Configure PORTB<15:8> as inputs and PORTB<7:0> as outputs<br>//Delay 1 cycle<br>// execute following code if PORTB pin 13 is set. |

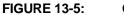

# 13.3 Output Compare Mode

Output Compare mode compares the Timer register value with the value of one or two Compare registers, depending on its mode of operation. The Output Compare x module on compare match events has the ability to generate a single output transition or a train of output

pulses. Like most PIC<sup>®</sup> MCU peripherals, the Output Compare x module can also generate interrupts on a compare match event.

Table 13-3 shows the various modes available in Output Compare modes.

| TABLE 13-3: | OUTPUT COMPARE/PWM MODES |

|-------------|--------------------------|

|-------------|--------------------------|

| MOD<3:0><br>(CCPxCON1L<3:0>) | T32<br>(CCPxCON1L<5>) | Operating Mode                         |                  |  |  |

|------------------------------|-----------------------|----------------------------------------|------------------|--|--|

| 0001                         | 0                     | Output High on Compare (16-bit)        |                  |  |  |

| 0001                         | 1                     | Output High on Compare (32-bit)        |                  |  |  |

| 0010                         | 0                     | Output Low on Compare (16-bit)         | Single Edge Mede |  |  |

| 0010                         | 1                     | Output Low on Compare (32-bit)         | Single Edge Mode |  |  |

| 0011                         | 0                     | Output Toggle on Compare (16-bit)      |                  |  |  |

| 0011                         | 1                     | Output Toggle on Compare (32-bit)      |                  |  |  |

| 0100                         | 0                     | Dual Edge Compare (16-bit)             | Dual Edge Mode   |  |  |

| 0101                         | 0                     | Dual Edge Compare (16-bit buffered)    | PWM Mode         |  |  |

| 0110                         | 0                     | Center-Aligned Pulse (16-bit buffered) | Center PWM       |  |  |

| 0111                         | 0                     | Variable Frequency Pulse (16-bit)      |                  |  |  |

| 0111                         | 1                     | Variable Frequency Pulse (32-bit)      |                  |  |  |

#### OUTPUT COMPARE x BLOCK DIAGRAM

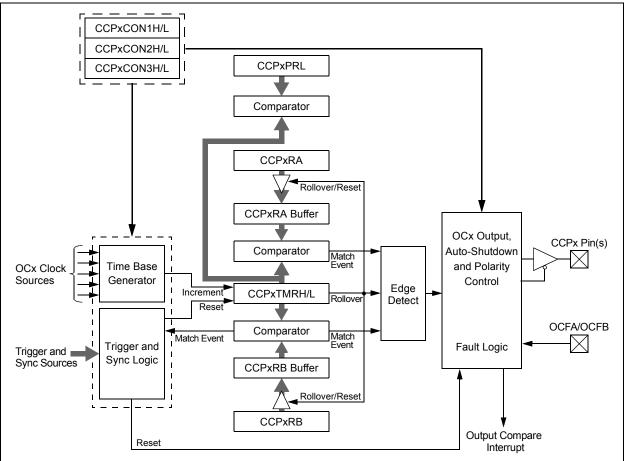

# 13.4 Input Capture Mode

Input Capture mode is used to capture a timer value from an independent timer base upon an event on an input pin or other internal Trigger source. The input capture features are useful in applications requiring frequency (time period) and pulse measurement. Figure 13-6 depicts a simplified block diagram of Input Capture mode. Input Capture mode uses a dedicated 16/32-bit, synchronous, up counting timer for the capture function. The timer value is written to the FIFO when a capture event occurs. The internal value may be read (with a synchronization delay) using the CCPxTMRH/L register.

To use Input Capture mode, the CCSEL bit (CCPxCON1L<4>) must be set. The T32 and the MOD<3:0> bits are used to select the proper Capture mode, as shown in Table 13-4.

| MOD<3:0><br>(CCPxCON1L<3:0>) | T32<br>(CCPxCON1L<5>) | Operating Mode                     |

|------------------------------|-----------------------|------------------------------------|

| 0000                         | 0                     | Edge Detect (16-bit capture)       |

| 0000                         | 1                     | Edge Detect (32-bit capture)       |

| 0001                         | 0                     | Every Rising (16-bit capture)      |

| 0001                         | 1                     | Every Rising (32-bit capture)      |

| 0010                         | 0                     | Every Falling (16-bit capture)     |

| 0010                         | 1                     | Every Falling (32-bit capture)     |

| 0011                         | 0                     | Every Rise/Fall (16-bit capture)   |

| 0011                         | 1                     | Every Rise/Fall (32-bit capture)   |

| 0100                         | 0                     | Every 4th Rising (16-bit capture)  |

| 0100                         | 1                     | Every 4th Rising (32-bit capture)  |

| 0101                         | 0                     | Every 16th Rising (16-bit capture) |

| 0101                         | 1                     | Every 16th Rising (32-bit capture) |

## TABLE 13-4: INPUT CAPTURE MODES

### REGISTER 17-5: CLCxGLSH: CLCx GATE LOGIC INPUT SELECT HIGH REGISTER (CONTINUED)

| bit 3 | G3D2T: Gate 3 Data Source 2 True Enable bit                  |

|-------|--------------------------------------------------------------|

|       | 1 = The Data Source 2 inverted signal is enabled for Gate 3  |

|       | 0 = The Data Source 2 inverted signal is disabled for Gate 3 |

| bit 2 | G3D2N: Gate 3 Data Source 2 Negated Enable bit               |

|       | 1 = The Data Source 2 inverted signal is enabled for Gate 3  |

|       | 0 = The Data Source 2 inverted signal is disabled for Gate 3 |

| bit 1 | G3D1T: Gate 3 Data Source 1 True Enable bit                  |

|       | 1 = The Data Source 1 inverted signal is enabled for Gate 3  |

|       | 0 = The Data Source 1 inverted signal is disabled for Gate 3 |

| bit 0 | G3D1N: Gate 3 Data Source 1 Negated Enable bit               |

|       | 1 = The Data Source 1 inverted signal is enabled for Gate 3  |

|       | 0 = The Data Source 1 inverted signal is disabled for Gate 3 |

# TABLE 19-2:NUMERICAL EQUIVALENTS OF VARIOUS RESULT CODES:<br/>12-BIT FRACTIONAL FORMATS

| VIN/VREF   | 12-Bit<br>Output Code |                     |       |                     |        |  |  |  |  |

|------------|-----------------------|---------------------|-------|---------------------|--------|--|--|--|--|

| +4095/4096 | 0 1111 1111 1111      | 1111 1111 1111 0000 | 0.999 | 0111 1111 1111 1000 | 0.999  |  |  |  |  |

| +4094/4096 | 0 1111 1111 1110      | 1111 1111 1110 0000 | 0.998 | 0111 1111 1110 1000 | 0.998  |  |  |  |  |

|            |                       | • • •               |       |                     |        |  |  |  |  |

| +1/4096    | 0 0000 0000 0001      | 0000 0000 0001 0000 | 0.001 | 0000 0000 0000 1000 | 0.001  |  |  |  |  |

| 0/4096     | 0 0000 0000 0000      | 0000 0000 0000 0000 | 0.000 | 0000 0000 0000 0000 | 0.000  |  |  |  |  |

| -1/4096    | 1 0111 1111 1111      | 0000 0000 0000 0000 | 0.000 | 1111 1111 1111 1000 | -0.001 |  |  |  |  |

|            | •••                   |                     |       |                     |        |  |  |  |  |

| -4095/4096 | 1 0000 0000 0001      | 0000 0000 0000 0000 | 0.000 | 1000 0000 0000 1000 | -0.999 |  |  |  |  |

| -4096/4096 | 1 0000 0000 0000      | 0000 0000 0000 0000 | 0.000 | 1000 0000 0000 0000 | -1.000 |  |  |  |  |

# FIGURE 19-5: A/D OUTPUT DATA FORMATS (10-BIT)

| RAM Contents:            |     |     |     |     |     |     | d09 | d08 | d07 | d06 | d05 | d04 | d03 | d02 | d01 | d00 |

|--------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Read to Bus:             |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     | I   |

| Integer                  | 0   | 0   | 0   | 0   | 0   | 0   | d09 | d08 | d07 | d06 | d05 | d04 | d03 | d02 | d01 | d00 |

|                          |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

| Signed Integer           | s0  | s0  | s0  | s0  | s0  | s0  | d09 | d08 | d07 | d06 | d05 | d04 | d03 | d02 | d01 | d00 |

|                          |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

| Fractional (1.15)        | d09 | d08 | d07 | d06 | d05 | d04 | d03 | d02 | d01 | d00 | 0   | 0   | 0   | 0   | 0   | 0   |

|                          |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

| Signed Fractional (1.15) | s0  | d09 | d08 | d07 | d06 | d05 | d04 | d03 | d02 | d01 | d00 | 0   | 0   | 0   | 0   | 0   |

|                          | L   |     |     |     |     |     |     | 1   |     |     |     |     |     |     |     |     |

# TABLE 19-3:NUMERICAL EQUIVALENTS OF VARIOUS RESULT CODES:<br/>10-BIT INTEGER FORMATS

| VIN/VREF   | 10-Bit Differential<br>Output Code<br>(11-bit result) | 16-Bit Integer Format/<br>Equivalent Decimal Value |      | 16-Bit Signed Integer Forn<br>Equivalent Decimal Valu |       |

|------------|-------------------------------------------------------|----------------------------------------------------|------|-------------------------------------------------------|-------|

| +1023/1024 | 011 1111 1111                                         | 0000 0011 1111 1111                                | 1023 | 0000 0001 1111 1111                                   | 1023  |

| +1022/1024 | 011 1111 1110                                         | 0000 0011 1111 1110                                | 1022 | 0000 0001 1111 1110                                   | 1022  |

|            |                                                       | •••                                                |      |                                                       |       |

| +1/1024    | 000 0000 0001                                         | 0000 0000 0000 0001                                | 1    | 0000 0000 0000 0001                                   | 1     |

| 0/1024     | 000 0000 0000                                         | 0000 0000 0000 0000                                | 0    | 0000 0000 0000 0000                                   | 0     |

| -1/1024    | 101 1111 1111                                         | 0000 0000 0000 0000                                | 0    | 1111 1111 1111 1111                                   | -1    |

|            |                                                       | •••                                                |      |                                                       |       |

| -1023/1024 | 100 0000 0001                                         | 0000 0000 0000 0000                                | 0    | 1111 1110 0000 0001                                   | -1023 |

| -1024/1024 | 100 0000 0000                                         | 0000 0000 0000 0000                                | 0    | 1111 1110 0000 0000                                   | -1024 |

# REGISTER 22-1: CMxCON: COMPARATOR x CONTROL REGISTERS (CONTINUED)

- bit 2 Unimplemented: Read as '0'

- bit 1-0 **CCH<1:0>:** Comparator x Channel Select bits

- 11 = Inverting input of the comparator connects to BGBUF1<sup>(1)</sup>

- 10 = Inverting input of the comparator connects to the CxIND pin

- 01 = Inverting input of the comparator connects to the CxINC pin

- 00 = Inverting input of the comparator connects to the CxINB pin

- **Note 1:** BGBUF1 voltage is configured by BUFREF1<1:0> (BUFCON0<1:0>).

- 2: If the EVPOL<1:0> bits are set to a value other than '00', the first interrupt generated will occur on any transition of COUT. Subsequent interrupts will occur based on the EVPOLx bits setting.

## REGISTER 22-2: CMSTAT: COMPARATOR MODULE STATUS REGISTER

| R/W-0  | U-0 | U-0 | U-0 | U-0 | R-0, HSC             | R-0, HSC             | R-0, HSC |

|--------|-----|-----|-----|-----|----------------------|----------------------|----------|

| CMIDL  | —   | —   | —   | —   | C3EVT <sup>(1)</sup> | C2EVT <sup>(1)</sup> | C1EVT    |

| bit 15 |     |     |     |     |                      |                      | bit 8    |

|        |     |     |     |     |                      |                      |          |

| U-0   | U-0 | U-0 | U-0 | U-0 | R-0, HSC             | R-0, HSC             | R-0, HSC |

|-------|-----|-----|-----|-----|----------------------|----------------------|----------|

| —     | —   | —   | —   | —   | C3OUT <sup>(1)</sup> | C2OUT <sup>(1)</sup> | C1OUT    |

| bit 7 |     |     |     |     |                      |                      | bit 0    |

| Legend:           | HSC = Hardware Settable/Clearable bit |                                    |                    |  |  |  |

|-------------------|---------------------------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit                      | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set                      | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

| bit 15    | CMIDL: Comparator x Stop in Idle Mode bit                                                                                                                                                |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | <ul> <li>1 = Comparator interrupts are disabled in Idle mode; enabled comparators remain operational</li> <li>0 = Continues operation of all enabled comparators in Idle mode</li> </ul> |

| bit 14-11 | Unimplemented: Read as '0'                                                                                                                                                               |

| bit 10    | C3EVT: Comparator 3 Event Status bit (read-only) <sup>(1)</sup>                                                                                                                          |

|           | Shows the current event status of Comparator 3 (CM3CON<9>).                                                                                                                              |

| bit 9     | C2EVT: Comparator 2 Event Status bit (read-only) <sup>(1)</sup>                                                                                                                          |

|           | Shows the current event status of Comparator 2 (CM2CON<9>).                                                                                                                              |

| bit 8     | C1EVT: Comparator 1 Event Status bit (read-only)                                                                                                                                         |

|           | Shows the current event status of Comparator 1 (CM1CON<9>).                                                                                                                              |

| bit 7-3   | Unimplemented: Read as '0'                                                                                                                                                               |

| bit 2     | C3OUT: Comparator 3 Output Status bit (read-only) <sup>(1)</sup>                                                                                                                         |

|           | Shows the current output of Comparator 3 (CM3CON<8>).                                                                                                                                    |

| bit 1     | C2OUT: Comparator 2 Output Status bit (read-only) <sup>(1)</sup>                                                                                                                         |

|           | Shows the current output of Comparator 2 (CM2CON<8>).                                                                                                                                    |

| bit 0     | C1OUT: Comparator 1 Output Status bit (read-only)                                                                                                                                        |

|           | Shows the current output of Comparator 1 (CM1CON<8>).                                                                                                                                    |

| Note 1:   | Comparator 2 and Comparator 3 are only available on PIC24F(V)16KM2XX devices.                                                                                                            |

# 24.0 CHARGE TIME MEASUREMENT UNIT (CTMU)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the Charge Time Measurement Unit, refer to the "PIC24F Family Reference Manual", "Charge Time Measurement Unit (CTMU) with Threshold Detect" (DS39743).

The Charge Time Measurement Unit (CTMU) is a flexible analog module that provides charge measurement, accurate differential time measurement between pulse sources and asynchronous pulse generation. Its key features include:

- Thirteen external edge input Trigger sources

- · Polarity control for each edge source

- · Control of edge sequence

- Control of response to edge levels or edge transitions

- · Time measurement resolution of one nanosecond

- Accurate current source suitable for capacitive measurement

Together with other on-chip analog modules, the CTMU can be used to precisely measure time, measure capacitance, measure relative changes in capacitance or generate output pulses that are independent of the system clock. The CTMU module is ideal for interfacing with capacitive-based touch sensors.

The CTMU is controlled through three registers: CTMUCON1, CTMUCON2 and CTMUICON. CTMUCON1 enables the module and controls the mode of operation of the CTMU, as well as controlling edge sequencing. CTMUCON2 controls edge source selection and edge source polarity selection. The CTMUICON register selects the current range of current source and trims the current.

# 24.1 Measuring Capacitance

The CTMU module measures capacitance by generating an output pulse, with a width equal to the time between edge events, on two separate input channels. The pulse edge events to both input channels can be selected from several internal peripheral modules (OC1, Timer1, any input capture or comparator module) and up to 13 external pins (CTED1 through CTED13). This pulse is used with the module's precision current source to calculate capacitance according to the relationship:

### EQUATION 24-1:

$$I = C \cdot \frac{dV}{dT}$$

For capacitance measurements, the A/D Converter samples an External Capacitor (CAPP) on one of its input channels after the CTMU output's pulse. A Precision Resistor (RPR) provides current source calibration on a second A/D channel. After the pulse ends, the converter determines the voltage on the capacitor. The actual calculation of capacitance is performed in software by the application.

Figure 24-1 illustrates the external connections used for capacitance measurements, and how the CTMU and A/D modules are related in this application. This example also shows the edge events coming from Timer1, but other configurations using external edge sources are possible. A detailed discussion on measuring capacitance and time with the CTMU module is provided in the "*PIC24F Family Reference Manual*".

### REGISTER 24-1: CTMUCON1L: CTMU CONTROL 1 LOW REGISTER (CONTINUED)

- bit 1-0 IRNG<1:0>: Current Source Range Select bits

- 11 = 100 × Base Current

- 10 = 10 × Base Current

- 01 = Base Current Level (0.55 μA nominal)

- 00 = 1000 × Base Current

# REGISTER 25-7: FICD: IN-CIRCUIT DEBUGGER CONFIGURATION REGISTER

| R/P-1                       | U-0                                                                                                                                                                                 | U-0                                                                                                                     | U-0                                                                     | U-0                              | U-0              | R/P-1           | R/P-1              |  |  |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|----------------------------------|------------------|-----------------|--------------------|--|--|

| DEBUG                       | _                                                                                                                                                                                   | _                                                                                                                       | —                                                                       | —                                | —                | FICD1           | FICD0              |  |  |

| bit 7                       |                                                                                                                                                                                     |                                                                                                                         |                                                                         | •                                |                  | •               | bit 0              |  |  |

|                             |                                                                                                                                                                                     |                                                                                                                         |                                                                         |                                  |                  |                 |                    |  |  |

| Legend:                     |                                                                                                                                                                                     |                                                                                                                         |                                                                         |                                  |                  |                 |                    |  |  |

| R = Readab                  | le bit                                                                                                                                                                              | P = Programn                                                                                                            | nable bit                                                               | U = Unimplem                     | nented bit, read | l as '0'        |                    |  |  |

| -n = Value a                | t POR                                                                                                                                                                               | '1' = Bit is set                                                                                                        |                                                                         | '0' = Bit is clea                | ared             | x = Bit is unkr | x = Bit is unknown |  |  |

| bit 7<br>bit 6-2<br>bit 1-0 | <b>DEBUG:</b> Background<br>1 = Background<br>0 = Background<br><b>Unimplemente</b><br><b>FICD&lt;1:0:&gt;:</b> IC<br>11 = PGEC1/P<br>10 = PGEC2/P<br>01 = PGEC3/P<br>00 = Reserved | d debugger is o<br>d debugger fun<br>ed: Read as '0'<br>CD Pin Select b<br>GED1 are use<br>GED2 are use<br>GED3 are use | disabled<br>Inctions are ena<br>its<br>d for programm<br>d for programm | ning and debug<br>ning and debug | ging the device  | Э               |                    |  |  |

# REGISTER 25-8: DEVID: DEVICE ID REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0    |

|--------|-----|-----|-----|-----|-----|-----|--------|

| —      | —   | —   | —   | —   | —   | —   | —      |

| bit 23 |     |     |     |     |     |     | bit 16 |

| R      | R      | R      | R      | R      | R      | R      | R      |

|--------|--------|--------|--------|--------|--------|--------|--------|

| FAMID7 | FAMID6 | FAMID5 | FAMID4 | FAMID3 | FAMID2 | FAMID1 | FAMID0 |

| bit 15 |        |        |        |        |        |        | bit 8  |

| R     | R    | R    | R    | R    | R    | R    | R     |

|-------|------|------|------|------|------|------|-------|

| DEV7  | DEV6 | DEV5 | DEV4 | DEV3 | DEV2 | DEV1 | DEV0  |

| bit 7 |      |      |      |      |      |      | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 23-16 | Unimplemented: Read as '0'                  |

|-----------|---------------------------------------------|

| bit 15-8  | FAMID<7:0>: Device Family Identifier bits   |

|           | 01000101 = PIC24FV16KM204 family            |

| bit 7-0   | DEV<7:0>: Individual Device Identifier bits |

|           | 00011111 = PIC24FV16KM204                   |

|           | 00011011 = PIC24FV16KM202                   |

|           | 00010111 = PIC24FV08KM204                   |

|           | 00010011 = PIC24FV08KM202                   |

|           | 00001111 = PIC24FV16KM104                   |

|           | 00001011 = PIC24FV16KM102                   |

|           | 00000011 = PIC24FV08KM102                   |

|           | 00000001 = PIC24FV08KM101                   |

|           | 00011110 = PIC24F16KM204                    |

|           | 00011010 = PIC24F16KM202                    |

|           | 00010110 = PIC24F08KM204                    |

|           | 00010010 = PIC24F08KM202                    |

|           | 00001110 = PIC24F16KM104                    |

|           | 00001010 = PIC24F16KM102                    |

|           | 00000010 = PIC24F08KM102                    |

|           | 0000000 = PIC24F08KM101                     |

# TABLE 27-1: THERMAL OPERATING CONDITIONS

| Rating                                                                                                                                                                                                                                                                                                                        | Symbol | Min | Тур         | Max  | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|-------------|------|------|

| Operating Junction Temperature Range                                                                                                                                                                                                                                                                                          | TJ     | -40 | _           | +140 | °C   |

| Operating Ambient Temperature Range                                                                                                                                                                                                                                                                                           | TA     | -40 | _           | +125 | °C   |

| $\begin{array}{l} \mbox{Power Dissipation} \\ \mbox{Internal Chip Power Dissipation:} \\ \mbox{PINT} = \mbox{VDD } x \ (\mbox{IDD} - \Sigma \ \mbox{IOH}) \\ \mbox{I/O Pin Power Dissipation:} \\ \mbox{PI/O} = \Sigma \ (\{\mbox{VDD} - \mbox{VOH} \} \ x \ \mbox{IOH}) + \Sigma \ (\mbox{VOL } x \ \mbox{IOL}) \end{array}$ | PD     |     | Pint + Pi/c | )    | W    |

| Maximum Allowed Power Dissipation                                                                                                                                                                                                                                                                                             | PDMAX  | (   | TJ — TA)/θJ | IA   | W    |

# TABLE 27-2: THERMAL PACKAGING CHARACTERISTICS

| Characteristic                           | Symbol | Тур  | Max | Unit | Notes |

|------------------------------------------|--------|------|-----|------|-------|

| Package Thermal Resistance, 20-Pin PDIP  | θJA    | 62.4 | _   | °C/W | 1     |

| Package Thermal Resistance, 28-Pin SPDIP | θJA    | 60   |     | °C/W | 1     |

| Package Thermal Resistance, 20-Pin SSOP  | θJA    | 108  | -   | °C/W | 1     |

| Package Thermal Resistance, 28-Pin SSOP  | θJA    | 71   | _   | °C/W | 1     |

| Package Thermal Resistance, 20-Pin SOIC  | θJA    | 75   | _   | °C/W | 1     |

| Package Thermal Resistance, 28-Pin SOIC  | θJA    | 80.2 | _   | °C/W | 1     |

| Package Thermal Resistance, 20-Pin QFN   | θJA    | 43   | _   | °C/W | 1     |

| Package Thermal Resistance, 28-Pin QFN   | θJA    | 32   | _   | °C/W | 1     |

| Package Thermal Resistance, 44-Pin QFN   | θJA    | 29   | _   | °C/W | 1     |

| Package Thermal Resistance, 44-Pin TQFP  | θJA    | 40   | _   | °C/W | 1     |

| Package Thermal Resistance, 48-Pin UQFN  | θJA    | 41   | _   | °C/W | 1     |

**Note 1:** Junction to ambient thermal resistance, Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.

## TABLE 27-3: DC CHARACTERISTICS: TEMPERATURE AND VOLTAGE SPECIFICATIONS

| DC CHA       |        | STICS                                                            | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                                  |     |      |                                   |

|--------------|--------|------------------------------------------------------------------|-------------------------------------------------------|----------------------------------|-----|------|-----------------------------------|

| Param<br>No. | Symbol | Characteristic                                                   | Min                                                   | Min Typ <sup>(1)</sup> Max Units |     |      | Conditions                        |

| DC10         | Vdd    | Supply Voltage                                                   | 1.8                                                   | —                                | 3.6 | V    | For PIC24F devices                |

|              |        |                                                                  | 2.0                                                   |                                  | 5.5 | V    | For PIC24FV devices               |

| DC12         | Vdr    | RAM Data Retention                                               | 1.6                                                   |                                  | —   | V    | For PIC24F devices                |

|              |        | Voltage <sup>(2)</sup>                                           | 1.8                                                   |                                  | —   | V    | For PIC24FV devices               |

| DC16         | VPOR   | VDD Start Voltage<br>to Ensure Internal<br>Power-on Reset Signal | Vss                                                   | —                                | 0.7 | V    |                                   |

| DC17         | SVDD   | VDD Rise Rate<br>to Ensure Internal<br>Power-on Reset Signal     | 0.05                                                  | _                                | —   | V/ms | 0-3.3V in 0.1s<br>0-2.5V in 60 ms |

**Note 1:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**2:** This is the limit to which VDD can be lowered without losing RAM data.

| AC CHARACTERISTICS |       |                                  |     | Operating<br>temperatu |     | $\begin{array}{l} \textbf{s: 1.8V to 3.6V (PIC24F16KM204)} \\ \textbf{2.0V to 5.5V (PIC24FV16KM204)} \\ \textbf{-40^{\circ}C} \leq \text{TA} \leq +85^{\circ}\text{C} \text{ for Industrial} \\ \textbf{-40^{\circ}C} \leq \text{TA} \leq +125^{\circ}\text{C} \text{ for Extended} \end{array}$ |                                                     |  |  |

|--------------------|-------|----------------------------------|-----|------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--|--|

| Param<br>No.       | Sym   | Characteristic <sup>(1)</sup>    | Min | Тур <sup>(2)</sup>     | Max | Units                                                                                                                                                                                                                                                                                            | Conditions                                          |  |  |

| OS50               | Fplli | PLL Input Frequency<br>Range     | 4   | —                      | 8   | MHz                                                                                                                                                                                                                                                                                              | ECPLL, HSPLL modes,<br>-40°C $\leq$ TA $\leq$ +85°C |  |  |

| OS51               | Fsys  | PLL Output Frequency<br>Range    | 16  | —                      | 32  | MHz                                                                                                                                                                                                                                                                                              | $-40^{\circ}C \le TA \le +85^{\circ}C$              |  |  |

| OS52               | TLOCK | PLL Start-up Time<br>(Lock Time) | -   | 1                      | 2   | ms                                                                                                                                                                                                                                                                                               |                                                     |  |  |

| OS53               | DCLK  | CLKO Stability (Jitter)          | -2  | 1                      | 2   | %                                                                                                                                                                                                                                                                                                | Measured over 100 ms period                         |  |  |

### TABLE 27-21: PLL CLOCK TIMING SPECIFICATIONS

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

### TABLE 27-22: INTERNAL RC OSCILLATOR ACCURACY

| AC CHARACTERISTICS Standard Operating Conditions: 1.8V to 3.6V (PIC24F16KM204)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                              |     |   |     |           | /16KM204)<br>or Industrial                                                                                                                                                        |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-----|---|-----|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Param<br>No.CharacteristicMinTypMaxUnitsCondition                                                                                                                                                                     |                              |     |   |     | onditions |                                                                                                                                                                                   |  |  |  |

| F20                                                                                                                                                                                                                   | FRC @ 8 MHz <sup>(1)</sup>   | -2  |   | +2  | %         | +25°C $3.0V \le VDD \le 3.6V, F dt 3.2V \le VDD \le 5.5V, FV$                                                                                                                     |  |  |  |

|                                                                                                                                                                                                                       |                              | -5  | _ | +5  | %         | $\label{eq:constraint} \begin{array}{c} -40^\circ C \leq T_A \leq +125^\circ C \\ 2.0V \leq V DD \leq 3.6V, \ F \ devic \\ 2.0V \leq V DD \leq 5.5V, \ FV \ devic \\ \end{array}$ |  |  |  |

| F21                                                                                                                                                                                                                   | LPRC @ 31 kHz <sup>(2)</sup> | -15 |   | +15 | %         | $\label{eq:constraint} \begin{array}{l} -40^{\circ}C \leq TA \leq +125^{\circ}C \\ 2.0V \leq VDD \leq 3.6V, \ F \ device \\ 2.0V \leq VDD \leq 5.5V, \ FV \ device \end{array}$   |  |  |  |

**Note 1:** The frequency is calibrated at +25°C and 3.3V. The OSCTUN bits can be used to compensate for temperature drift.

2: The change of LPRC frequency as VDD changes.

### TABLE 27-23: INTERNAL RC OSCILLATOR SPECIFICATIONS

| АС СНА       | AC CHARACTERISTICS |                    | $\begin{tabular}{ c c c c c c c c c c c c c c c c c c c$ |     |     |       |            |  |  |

|--------------|--------------------|--------------------|----------------------------------------------------------|-----|-----|-------|------------|--|--|

| Param<br>No. | Sym                | Characteristic     | Min                                                      | Тур | Мах | Units | Conditions |  |  |

|              | TFRC               | FRC Start-up Time  | —                                                        | 5   | _   | μS    |            |  |  |

|              | TLPRC              | LPRC Start-up Time | —                                                        | 70  | —   | μS    |            |  |  |

| Param<br>No. | Symbol | Characteristic                                         | Min | Тур | Max | Units | Comments |

|--------------|--------|--------------------------------------------------------|-----|-----|-----|-------|----------|

| 300          | TRESP  | Response Time <sup>*(1)</sup>                          | _   | 150 | 400 | ns    |          |

| 301          | Тмс2о∨ | Comparator Mode Change to<br>Output Valid <sup>*</sup> | —   | —   | 10  | μs    |          |

## TABLE 27-26: COMPARATOR TIMING REQUIREMENTS

Parameters are characterized but not tested.

\*

**Note 1:** Response time is measured with one comparator input at (VDD – 1.5)/2, while the other input transitions from Vss to VDD.

#### TABLE 27-27: COMPARATOR VOLTAGE REFERENCE SETTLING TIME SPECIFICATIONS

| Param<br>No. | Symbol | Characteristic               | Min | Тур | Max | Units | Comments |

|--------------|--------|------------------------------|-----|-----|-----|-------|----------|

| VR310        | TSET   | Settling Time <sup>(1)</sup> |     |     | 10  | μS    |          |

Note 1: Settling time is measured while CVRSS = 1 and the CVR<3:0> bits transition from '0000' to '1111'.

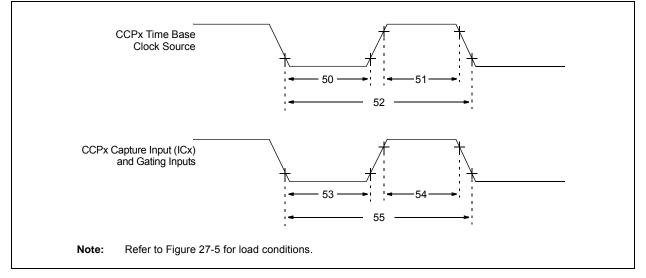

# FIGURE 27-10: CAPTURE/COMPARE/PWM TIMINGS (MCCPx, SCCPx MODULES)

## TABLE 27-28: CAPTURE/COMPARE/PWM REQUIREMENTS (MCCPx, SCCPx MODULES)

| Param<br>No. | Symbol | Characteristic                         | Min        | Max | Units | Conditions                         |

|--------------|--------|----------------------------------------|------------|-----|-------|------------------------------------|

| 50           | TCLKL  | CCPx Time Base Clock Source Low Time   | TCY/2      | _   | ns    |                                    |

| 51           | ТсікН  | CCPx Time Base Clock Source High Time  | Tcy/2      | _   | ns    |                                    |

| 52           | TCLK   | CCPx Time Base Clock Source Period     | Тсү        | -   | ns    |                                    |

| 53           | TccL   | CCPx Capture or Gating Input Low Time  | TCLK       | —   | ns    |                                    |

| 54           | ТссН   | CCPx Capture or Gating Input High Time | TCLK       | _   | ns    |                                    |

| 55           | TCCP   | CCPx Capture or Gating Input Period    | 2 * Tclk/N | —   | ns    | N = Prescale<br>Value (1, 4 or 16) |