# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 23                                                                            |

| Program Memory Size        | 16KB (5.5K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 1K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5V                                                                       |

| Data Converters            | A/D 19x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Through Hole                                                                  |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                       |

| Supplier Device Package    | 28-SPDIP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fv16km102-e-sp |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 4-8: MCCP1 REGISTER MAP

| File Name | Addr. | Bit 15                                | Bit 14                                              | Bit 13  | Bit 12 | Bit 11  | Bit 10  | Bit 9   | Bit 8       | Bit 7        | Bit 6        | Bit 5   | Bit 4   | Bit 3   | Bit 2 | Bit 1 | Bit 0 | All<br>Rese |

|-----------|-------|---------------------------------------|-----------------------------------------------------|---------|--------|---------|---------|---------|-------------|--------------|--------------|---------|---------|---------|-------|-------|-------|-------------|

| CCP1CON1L | 140h  | CCPON                                 | —                                                   | CCPSIDL | r      | TMRSYNC | CLKSEL2 | CLKSEL1 | CLKSEL0     | TMRPS1       | TMRPS0       | T32     | CCSEL   | MOD3    | MOD2  | MOD1  | MOD0  | 0000        |

| CCP1CON1H | 142h  | OPSSRC                                | RTRGEN                                              | _       | _      | OPS3    | OPS2    | OPS1    | OPS0        | TRIGEN       | ONESHOT      | ALTSYNC | SYNC4   | SYNC3   | SYNC2 | SYNC1 | SYNC0 | 0000        |

| CCP1CON2L | 144h  | PWMRSEN                               | ASDGM                                               | _       | SSDG   | _       | _       | _       | _           | ASDG7        | ASDG6        | ASDG5   | ASDG4   | ASDG3   | ASDG2 | ASDG1 | ASDG0 | 0000        |

| CCP1CON2H | 146h  | OENSYNC                               | _                                                   | OCFEN   | OCEEN  | OCDEN   | OCCEN   | OCBEN   | OCAEN       | ICGSM1       | ICGSM0       | _       | AUXOUT1 | AUXOUT0 | ICS2  | ICS1  | ICS0  | 0100        |

| CCP1CON3L | 148h  | _                                     | _                                                   | _       | _      | _       | _       | _       | _           | _            |              | DT5     | DT4     | DT3     | DT2   | DT1   | DT0   | 0000        |

| CCP1CON3H | 14Ah  | OETRIG                                | OSCNT2                                              |         |        |         |         |         |             |              |              |         |         |         |       | 0000  |       |             |

| CCP1STATL | 14Ch  | _                                     | CCPTRIG TRSET TRCLR ASEVT SCEVT ICDIS ICOV ICBNE OC |         |        |         |         |         |             |              |              |         |         |         | 0000  |       |       |             |

| CCP1TMRL  | 150h  |                                       |                                                     |         |        |         |         | MCCI    | P1 Time Ba  | se Register  | Low Word     |         |         |         |       |       |       | 0000        |

| CCP1TMRH  | 152h  |                                       |                                                     |         |        |         |         | MCCF    | P1 Time Ba  | se Register  | High Word    |         |         |         |       |       |       | 0000        |

| CCP1PRL   | 154h  |                                       |                                                     |         |        |         |         | MCCP1   | Fime Base F | Period Regis | ster Low Wor | ď       |         |         |       |       |       | FFFF        |

| CCP1PRH   | 156h  |                                       |                                                     |         |        |         |         | MCCP1 T | īme Base F  | Period Regis | ster High Wo | rd      |         |         |       |       |       | FFFF        |

| CCP1RAL   | 158h  |                                       |                                                     |         |        |         |         | O       | utput Comp  | are 1 Data \ | Nord A       |         |         |         |       |       |       | 0000        |

| CCP1RBL   | 15Ch  |                                       | Output Compare 1 Data Word B 0000                   |         |        |         |         |         |             |              |              |         | 0000    |         |       |       |       |             |

| CCP1BUFL  | 160h  |                                       |                                                     |         |        |         |         | Input   | Capture 1 I | Data Buffer  | Low Word     |         |         |         |       |       |       | 0000        |

| CCP1BUFH  | 162h  | Input Capture 1 Data Buffer High Word |                                                     |         |        |         |         |         |             |              |              | 0000    |         |         |       |       |       |             |

Legend: x = unknown, u = unchanged, --- = unimplemented, q = value depends on condition, r = reserved.

#### TABLE 4-9: MCCP2 REGISTER MAP

| File Name | Addr. | Bit 15  | Bit 14                                               | Bit 13               | Bit 12               | Bit 11               | Bit 10               | Bit 9                | Bit 8       | Bit 7        | Bit 6        | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|-------|---------|------------------------------------------------------|----------------------|----------------------|----------------------|----------------------|----------------------|-------------|--------------|--------------|---------|---------|---------|--------|--------|--------|---------------|

| CCP2CON1L | 164h  | CCPON   | _                                                    | CCPSIDL              | r                    | TMRSYNC              | CLKSEL2              | CLKSEL1              | CLKSEL0     | TMRPS1       | TMRPS0       | T32     | CCSEL   | MOD3    | MOD2   | MOD1   | MOD0   | 0000          |

| CCP2CON1H | 166h  | OPSSRC  | RTRGEN                                               | _                    | _                    | IOPS3                | IOPS2                | IOPS1                | IOPS0       | TRIGEN       | ONESHOT      | ALTSYNC | SYNC4   | SYNC3   | SYNC2  | SYNC1  | SYNC0  | 0000          |

| CCP2CON2L | 168h  | PWMRSEN | ASDGM                                                |                      | SSDG                 |                      |                      | _                    | _           | ASDG7        | ASDG6        | ASDG5   | ASDG4   | ASDG3   | ASDG2  | ASDG1  | ASDG0  | 0000          |

| CCP2CON2H | 16Ah  | OENSYNC | -                                                    | OCFEN <sup>(1)</sup> | OCEEN <sup>(1)</sup> | OCDEN <sup>(1)</sup> | OCCEN <sup>(1)</sup> | OCBEN <sup>(1)</sup> | OCAEN       | ICGSM1       | ICGSM0       | _       | AUXOUT1 | AUXOUT0 | ICSEL2 | ICSEL1 | ICSEL0 | 0100          |

| CCP2CON3L | 16Ch  | _       | _                                                    | _                    | _                    | _                    | _                    | _                    | _           | _            |              | DT5     | DT4     | DT3     | DT2    | DT1    | DT0    | 0000          |

| CCP2CON3H | 16Eh  | OETRIG  |                                                      |                      |                      |                      |                      |                      |             |              |              |         |         |         |        | 0000   |        |               |

| CCP2STATL | 170h  | _       | CCPTRIG TRSET TRCLR ASEVT SCEVT ICDIS ICOV ICBNE 000 |                      |                      |                      |                      |                      |             |              |              |         |         |         |        | 0000   |        |               |

| CCP2TMRL  | 174h  |         |                                                      |                      |                      |                      |                      | MCC                  | P2 Time Ba  | ase Register | r Low Word   |         |         |         |        |        |        | 0000          |

| CCP2TMRH  | 176h  |         |                                                      |                      |                      |                      |                      | MCC                  | P2 Time Ba  | se Register  | High Word    |         |         |         |        |        |        | 0000          |

| CCP2PRL   | 178h  |         |                                                      |                      |                      |                      |                      | MCCP2                | Time Base   | Period Regi  | ister Low Wo | rd      |         |         |        |        |        | FFFF          |

| CCP2PRH   | 17Ah  |         |                                                      |                      |                      |                      |                      | MCCP2                | Time Base I | Period Regi  | ster High Wo | rd      |         |         |        |        |        | FFFF          |

| CCP2RAL   | 17Ch  |         | Output Compare 2 Data Word A 0000                    |                      |                      |                      |                      |                      |             |              |              |         | 0000    |         |        |        |        |               |

| CCP2RBL   | 180h  |         | Output Compare 2 Data Word B 0000                    |                      |                      |                      |                      |                      |             |              |              |         | 0000    |         |        |        |        |               |

| CCP2BUFL  | 184h  |         |                                                      |                      |                      |                      |                      | Input                | Capture 2   | Data Buffer  | Low Word     |         |         |         |        |        |        | 0000          |

| CCP2BUFH  | 186h  |         |                                                      |                      |                      |                      |                      | Input                | Capture 2   | Data Buffer  | High Word    |         |         |         |        |        |        | 0000          |

PIC24FV16KM204 FAMILY

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

Note 1: These bits are available only on PIC24F(V)16KM2XX devices.

#### TABLE 4-21: PORTA REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 <sup>(4,5)</sup> | Bit 10 <sup>(4,5)</sup> | Bit 9 <sup>(4,5)</sup> | Bit 8 <sup>(4,5)</sup> | Bit 7 <sup>(4)</sup> | Bit 6 <sup>(3)</sup> | Bit 5 <sup>(2)</sup> | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets       |

|-----------|-------|--------|--------|--------|--------|-------------------------|-------------------------|------------------------|------------------------|----------------------|----------------------|----------------------|--------|--------|--------|--------|--------|---------------------|

| TRISA     | 2C0h  |        | _      | _      | _      | TRISA11                 | TRISA10                 | TRISA9                 | TRISA8                 | TRISA7               | TRISA6               | _                    | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 0FDF <sup>(1)</sup> |

| PORTA     | 2C2h  | _      | —      | —      |        | RA11                    | RA10                    | RA9                    | RA8                    | RA7                  | RA6                  | RA5                  | RA4    | RA3    | RA2    | RA1    | RA0    | xxxx                |

| LATA      | 2C4h  | _      | —      | —      |        | LATA11                  | LATA10                  | LATA9                  | LATA8                  | LATA7                | LATA6                | _                    | LATA4  | LATA3  | LATA2  | LATA1  | LATA0  | xxxx                |

| ODCA      | 2C6h  | _      | —      | _      | _      | ODA11                   | ODA10                   | ODA9                   | ODA8                   | ODA7                 | ODA6                 | _                    | ODA4   | ODA3   | ODA2   | ODA1   | ODA0   | 0000                |

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition, r = reserved.

Note 1: Reset value depends on the device type; the PIC24F16KM204 value is shown.

2: These bits are only available when MCLRE (FPOR<7>) = 0.

3: These bits are not implemented in FV devices.

4: These bits are not implemented in 20-pin devices.

5: These bits are not implemented in 28-pin devices.

#### TABLE 4-22: PORTB REGISTER MAP

| File Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11 <sup>(2)</sup> | Bit 10 <sup>(2)</sup> | Bit 9  | Bit 8  | Bit 7  | Bit 6 <sup>(2)</sup> | Bit 5 <sup>(2)</sup> | Bit 4  | Bit 3 <sup>(2)</sup> | Bit 2  | Bit 1  | Bit 0  | All<br>Resets       |

|-----------|-------|---------|---------|---------|---------|-----------------------|-----------------------|--------|--------|--------|----------------------|----------------------|--------|----------------------|--------|--------|--------|---------------------|

| TRISB     | 2C8h  | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11               | TRISB10               | TRISB9 | TRISB8 | TRISB7 | TRISB6               | TRISB5               | TRISB4 | TRISB3               | TRISB2 | TRISB1 | TRISB0 | <sub>FFFF</sub> (1) |

| PORTB     | 2CAh  | RB15    | RB14    | RB13    | RB12    | RB11                  | RB10                  | RB9    | RB8    | RB7    | RB6                  | RB5                  | RB4    | RB3                  | RB2    | RB1    | RB0    | xxxx                |

| LATB      | 2CCh  | LATB15  | LATB14  | LATB13  | LATB12  | LATB11                | LATB10                | LATB9  | LATB8  | LATB7  | LATB6                | LATB5                | LATB4  | LATB3                | LATB2  | LATB1  | LATB0  | xxxx                |

| ODCB      | 2CEh  | ODB15   | ODB14   | ODB13   | ODB12   | ODB11                 | ODB10                 | ODB9   | ODB8   | ODB7   | ODB6                 | ODB5                 | ODB4   | ODB3                 | ODB2   | ODB1   | ODB0   | 0000                |

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition, r = reserved.

Note 1: Reset value depends on the device type; the PIC24F16KM204 value is shown.

2: These bits are not implemented in 20-pin devices.

#### TABLE 4-23: PORTC REGISTER MAP

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 <sup>(2,3)</sup> | Bit 8 <sup>(2,3)</sup> | Bit 7 <sup>(2,3)</sup> | Bit 6 <sup>(2,3)</sup> | Bit 5 <sup>(2,3)</sup> | Bit 4 <sup>(2,3)</sup> | Bit 3 <sup>(2,3)</sup> | Bit 2 <sup>(2,3)</sup> | Bit 1 <sup>(2,3)</sup> | Bit 0 <sup>(2,3)</sup> | All<br>Resets       |

|--------------|-------|--------|--------|--------|--------|--------|--------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|---------------------|

| TRISC        | 2D0h  | _      | _      |        | _      | —      | _      | TRISC9                 | TRISC8                 | TRISC7                 | TRISC6                 | TRISC5                 | TRISC4                 | TRISC3                 | TRISC2                 | TRISC1                 | TRISC0                 | 03FF <sup>(1)</sup> |

| PORTC        | 2D2h  | —      | _      | _      | -      | —      | _      | RC9                    | RC8                    | RC7                    | RC6                    | RC5                    | RC4                    | RC3                    | RC2                    | RC1                    | RC0                    | xxxx                |

| LATTC        | 2D4h  | —      | _      | _      | -      | —      | _      | LATC9                  | LATC8                  | LATC7                  | LATC6                  | LATC5                  | LATC4                  | LATC3                  | LATC2                  | LATC1                  | LATC0                  | xxxx                |

| ODCC         | 2D6h  | _      | _      | —      | -      | —      | _      | ODC9                   | ODC8                   | ODC7                   | ODC6                   | ODC5                   | ODC4                   | ODC3                   | ODC2                   | ODC1                   | ODC0                   | 0000                |

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

Note 1: Reset value depends on the device type; the PIC24F16KM204 value is shown.

**2:** These bits are not implemented in 20-pin devices.

3: These bits are not implemented in 28-pin devices.

### 5.2 RTSP Operation

The PIC24F Flash program memory array is organized into rows of 32 instructions or 96 bytes. RTSP allows the user to erase blocks of 1 row, 2 rows and 4 rows (32, 64 and 128 instructions) at a time, and to program one row at a time. It is also possible to program single words.

The 1-row (96 bytes), 2-row (192 bytes) and 4-row (384 bytes) erase blocks, and single row write block (96 bytes) are edge-aligned, from the beginning of program memory.

When data is written to program memory using TBLWT instructions, the data is not written directly to memory. Instead, data written using Table Writes is stored in holding latches until the programming sequence is executed.

Any number of TBLWT instructions can be executed and a write will be successfully performed. However, 32 TBLWT instructions are required to write the full row of memory.

The basic sequence for RTSP programming is to set up a Table Pointer, then do a series of TBLWT instructions to load the buffers. Programming is performed by setting the control bits in the NVMCON register.

Data can be loaded in any order and the holding registers can be written to multiple times before performing a write operation. Subsequent writes, however, will wipe out any previous writes.

| Note: | Writing | to   | а    | location     | multiple | times, |

|-------|---------|------|------|--------------|----------|--------|

|       | without | eras | sing | it, is not i | ecommer  | nded.  |

All of the Table Write operations are single-word writes (two instruction cycles), because only the buffers are written. A programming cycle is required for programming each row.

### 5.3 Enhanced In-Circuit Serial Programming

Enhanced ICSP uses an on-board bootloader, known as the Program Executive (PE), to manage the programming process. Using an SPI data frame format, the Program Executive can erase, program and verify program memory. For more information on Enhanced ICSP, see the device programming specification.

### 5.4 Control Registers

There are two SFRs used to read and write the program Flash memory: NVMCON and NVMKEY.

The NVMCON register (Register 5-1) controls the blocks that need to be erased, which memory type is to be programmed and when the programming cycle starts.

NVMKEY is a write-only register that is used for write protection. To start a programming or erase sequence, the user must consecutively write 55h and AAh to the NVMKEY register. Refer to **Section 5.5 "Programming Operations"** for further details.

### 5.5 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. During a programming or erase operation, the processor stalls (waits) until the operation is finished. Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

### REGISTER 8-27: IPC10: INTERRUPT PRIORITY CONTROL REGISTER 10

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   |     | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

|        |     |     |     |     |     |     |       |

| U-0   | R/W-1   | R/W-0   | R/W-0   | U-0 | U-0 | U-0 | U-0   |

|-------|---------|---------|---------|-----|-----|-----|-------|

| —     | CCT5IP2 | CCT5IP1 | CCT5IP0 |     | _   | —   | —     |

| bit 7 |         |         |         |     |     |     | bit 0 |

| Legend:    |            |                                 |                              |                    |

|------------|------------|---------------------------------|------------------------------|--------------------|

| R = Reada  | ble bit    | W = Writable bit                | U = Unimplemented bit        | , read as '0'      |

| -n = Value | at POR     | '1' = Bit is set                | '0' = Bit is cleared         | x = Bit is unknown |

|            |            |                                 |                              |                    |

| bit 15-7   | Unimpler   | mented: Read as '0'             |                              |                    |

| bit 6-4    | CCT5IP<    | 2:0>: Capture/Compare 5 Ti      | imer Interrupt Priority bits |                    |

|            | 111 = Inte | errupt is Priority 7 (highest p | riority interrupt)           |                    |

|            | •          |                                 |                              |                    |

|            | •          |                                 |                              |                    |

|            | •          |                                 |                              |                    |

|            | 001 = Inte | errupt is Priority 1            |                              |                    |

- 000 = Interrupt source is disabled

- bit 3-0 Unimplemented: Read as '0'

| U-0                          | U-0                                      | U-0                                                                                                                                     | U-0                             | U-0              | R/W-1            | R/W-0           | R/W-0   |

|------------------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|------------------|------------------|-----------------|---------|

| _                            |                                          |                                                                                                                                         |                                 | _                | U2ERIP2          | U2ERIP1         | U2ERIP0 |

| oit 15                       |                                          |                                                                                                                                         | •                               |                  |                  | •               | bit 8   |

|                              |                                          |                                                                                                                                         |                                 |                  |                  |                 |         |

| U-0                          | R/W-1                                    | R/W-0                                                                                                                                   | R/W-0                           | U-0              | U-0              | U-0             | U-0     |

| —                            | U1ERIP2                                  | U1ERIP1                                                                                                                                 | U1ERIP0                         | —                | —                | —               | —       |

| bit 7                        |                                          |                                                                                                                                         |                                 |                  |                  |                 | bit 0   |

|                              |                                          |                                                                                                                                         |                                 |                  |                  |                 |         |

| Legend:                      |                                          |                                                                                                                                         |                                 |                  |                  |                 |         |

| R = Readab                   | ole bit                                  | W = Writable                                                                                                                            | bit                             | U = Unimpler     | mented bit, read | d as '0'        |         |

| -n = Value a                 | at POR                                   | '1' = Bit is set                                                                                                                        |                                 | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |

| bit 10-8<br>bit 7<br>bit 6-4 | <pre>111 = Interru </pre>                | >: UART2 Error<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>nted: Read as '<br>>: UART1 Error<br>pt is Priority 7 ( | highest priority<br>abled<br>o' | interrupt)       |                  |                 |         |

| bit 3-0                      | •<br>•<br>001 = Interru<br>000 = Interru | pt is Priority 1<br>pt is Priority 1<br>pt source is dis<br>nted: Read as '                                                             | abled                           | interrupt)       |                  |                 |         |

#### REGISTER 8-30: IPC16: INTERRUPT PRIORITY CONTROL REGISTER 16

NOTES:

| R/W-0         | U-0                                                              | R/W-0                                  | r-0            | R/W-0                                | R/W-0                  | R/W-0                  | R/W-0                  |

|---------------|------------------------------------------------------------------|----------------------------------------|----------------|--------------------------------------|------------------------|------------------------|------------------------|

| CCPON         |                                                                  | CCPSIDL                                | r              | TMRSYNC                              | CLKSEL2 <sup>(1)</sup> | CLKSEL1 <sup>(1)</sup> | CLKSEL0 <sup>(1)</sup> |

| bit 15        |                                                                  |                                        |                |                                      | •                      | •                      | bit 8                  |

|               |                                                                  |                                        |                |                                      |                        |                        |                        |

| R/W-0         | R/W-0                                                            | R/W-0                                  | R/W-0          | R/W-0                                | R/W-0                  | R/W-0                  | R/W-0                  |

| TMRPS1        | TMRPS0                                                           | T32                                    | CCSEL          | MOD3                                 | MOD2                   | MOD1                   | MOD0                   |

| bit 7         |                                                                  |                                        |                |                                      |                        |                        | bit (                  |

|               |                                                                  |                                        |                |                                      |                        |                        |                        |

| Legend:       |                                                                  | r = Reserved I                         |                |                                      |                        |                        |                        |

| R = Readable  |                                                                  | W = Writable I                         | oit            |                                      | nented bit, read       |                        |                        |

| -n = Value at | POR                                                              | '1' = Bit is set                       |                | '0' = Bit is clea                    | ared                   | x = Bit is unkn        | own                    |

| bit 15        | CCPON: CCF                                                       | x Module Enat                          | ole bit        |                                      |                        |                        |                        |

|               | 1 = Module is<br>0 = Module is                                   |                                        | an operating r | node specified b                     | by the MOD<3:          | 0> control bits        |                        |

| bit 14        | Unimplemen                                                       | ted: Read as 'd                        | )'             |                                      |                        |                        |                        |

| bit 13        | CCPSIDL: CO                                                      | CPx Stop in Idle                       | Mode Bit       |                                      |                        |                        |                        |

|               |                                                                  | ues module op<br>s module opera        |                | device enters lo<br>ode              | lle mode               |                        |                        |

| bit 12        | Reserved: Ma                                                     | -                                      |                |                                      |                        |                        |                        |

| bit 11        | TMRSYNC: T                                                       | ime Base Cloc                          | k Synchroniza  | ation bit                            |                        |                        |                        |

|               | (CLKSEL<br>0 = Synchron                                          | <b>&lt;2:0&gt;</b> ≠ 000)              |                | k is selected and<br>lock is selecte | -                      |                        | -                      |

| bit 10-8      |                                                                  | >: CCPx Time                           | Base Clock S   | elect bits <sup>(1)</sup>            |                        |                        |                        |

|               | 110 = Externa<br>101 = CLC1<br>100 = Reserv<br>011 = LPRC (      | 31 kHz source<br>dary Oscillator<br>ed | t              |                                      |                        |                        |                        |

| bit 7-6       | TMRPS<1:0>                                                       | : Time Base Pr                         | escale Select  | t bits                               |                        |                        |                        |

|               | 11 = 1:64 Pre<br>10 = 1:16 Pre<br>01 = 1:4 Pres<br>00 = 1:1 Pres | scaler<br>caler                        |                |                                      |                        |                        |                        |

| bit 5         | T32: 32-Bit Ti                                                   | me Base Selec                          | t bit          |                                      |                        |                        |                        |

|               |                                                                  |                                        |                | e edge output co<br>e edge output co |                        |                        |                        |

| bit 4         |                                                                  | ure/Compare N                          |                |                                      |                        |                        |                        |

|               | 1 = Input Cap                                                    | -                                      |                |                                      |                        |                        |                        |

### REGISTER 13-1: CCPxCON1L: CCPx CONTROL 1 LOW REGISTERS

| U-0           | U-0                                                                                                                                                                                                                      | U-0              | U-0                            | U-0                          | U-0               | U-0             | U-0           |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------|------------------------------|-------------------|-----------------|---------------|--|--|--|

| _             | —                                                                                                                                                                                                                        | _                | _                              | —                            | —                 | —               | —             |  |  |  |

| bit 15        | •                                                                                                                                                                                                                        |                  |                                | ·                            |                   | ·               | bit           |  |  |  |

| DA            |                                                                                                                                                                                                                          |                  |                                |                              |                   |                 |               |  |  |  |

| R-0<br>ACKTIM | R/W-0<br>PCIE                                                                                                                                                                                                            | R/W-0<br>SCIE    | R/W-0<br>BOEN <sup>(1)</sup>   | R/W-0<br>SDAHT               | R/W-0<br>SBCDE    | R/W-0<br>AHEN   | R/W-0<br>DHEN |  |  |  |

| bit 7         | FUE                                                                                                                                                                                                                      | SUE              | BOEIN',                        | SDATI                        | SECDE             | ALEN            | bit           |  |  |  |

|               |                                                                                                                                                                                                                          |                  |                                |                              |                   |                 | bit           |  |  |  |

| Legend:       |                                                                                                                                                                                                                          |                  |                                |                              |                   |                 |               |  |  |  |

| R = Readabl   | le bit                                                                                                                                                                                                                   | W = Writable     | bit                            | U = Unimplem                 | nented bit, read  | 1 as '0'        |               |  |  |  |

| -n = Value at | t POR                                                                                                                                                                                                                    | '1' = Bit is set |                                | '0' = Bit is clea            | ared              | x = Bit is unkn | own           |  |  |  |

|               |                                                                                                                                                                                                                          |                  |                                |                              |                   |                 |               |  |  |  |

| bit 15-8      | -                                                                                                                                                                                                                        | ted: Read as '   |                                |                              |                   |                 |               |  |  |  |

| bit 7         |                                                                                                                                                                                                                          | •                | e Status bit (I <sup>2</sup> 0 | C™ mode only)                |                   |                 |               |  |  |  |

|               | Unused in SP                                                                                                                                                                                                             |                  |                                | •                            |                   |                 |               |  |  |  |

| bit 6         |                                                                                                                                                                                                                          |                  | ipt Enable bit (I              | <sup>2</sup> C mode only)    |                   |                 |               |  |  |  |

|               | Unused in SP                                                                                                                                                                                                             |                  |                                | •                            |                   |                 |               |  |  |  |

| bit 5         |                                                                                                                                                                                                                          |                  | ipt Enable bit (I              | <sup>2</sup> C mode only)    |                   |                 |               |  |  |  |

|               | Unused in SP                                                                                                                                                                                                             |                  | (1)                            |                              |                   |                 |               |  |  |  |

| bit 4         |                                                                                                                                                                                                                          | r Overwrite Ena  | able bit <sup>(1)</sup>        |                              |                   |                 |               |  |  |  |

|               | In SPI Slave I                                                                                                                                                                                                           |                  | ny time that a p               | ovu data buta ia             | chiffod in igno   | ring the DC hit |               |  |  |  |

|               | <ul> <li>1 = SSPxBUF updates every time that a new data byte is shifted in, ignoring the BF bit</li> <li>0 = If a new byte is received with the BF bit of the SSPxSTAT register already set, the SSPOV bit of</li> </ul> |                  |                                |                              |                   |                 |               |  |  |  |

|               |                                                                                                                                                                                                                          |                  |                                | buffer is not up             |                   | <b>3</b>        |               |  |  |  |

| bit 3         | SDAHT: SDA                                                                                                                                                                                                               | x Hold Time S    | election bit (I <sup>2</sup> C | mode only)                   |                   |                 |               |  |  |  |

|               | Unused in SP                                                                                                                                                                                                             | l mode.          |                                |                              |                   |                 |               |  |  |  |

| bit 2         | SBCDE: Slav                                                                                                                                                                                                              | ve Mode Bus C    | ollision Detect                | Enable bit (I <sup>2</sup> C | Slave mode or     | ıly)            |               |  |  |  |

|               | Unused in SP                                                                                                                                                                                                             | l mode.          |                                |                              |                   |                 |               |  |  |  |

| bit 1         | AHEN: Addre                                                                                                                                                                                                              | ess Hold Enabl   | e bit (I <sup>2</sup> C Slave  | mode only)                   |                   |                 |               |  |  |  |

|               | Unused in SP                                                                                                                                                                                                             | l mode.          |                                |                              |                   |                 |               |  |  |  |

| bit 0         | DHEN: Data                                                                                                                                                                                                               | Hold Enable bi   | t (Slave mode o                | only)                        |                   |                 |               |  |  |  |

|               | Unused in SP                                                                                                                                                                                                             | Pl mode.         |                                |                              |                   |                 |               |  |  |  |

| Note 1: F     | or Daisy-Chaine                                                                                                                                                                                                          | ed SPI Operatio  | on: Allows the u               | iser to ignore al            | I but the last re | ceived byte S   | SDUV is still |  |  |  |

### REGISTER 14-6: SSPxCON3: MSSPx CONTROL REGISTER 3 (SPI MODE)

**Note 1:** For Daisy-Chained SPI Operation: Allows the user to ignore all but the last received byte. SSPOV is still set when a new byte is received and BF = 1, but hardware continues to write the most recent byte to SSPxBUF.

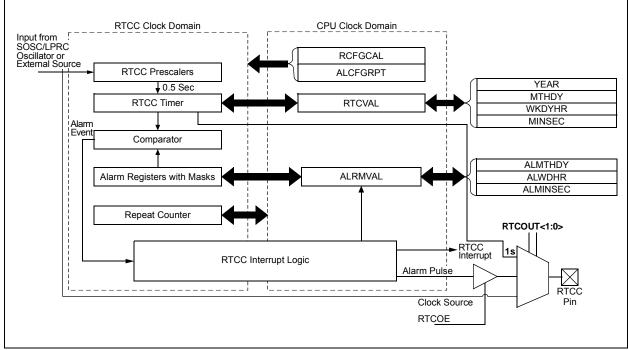

### 16.0 REAL-TIME CLOCK AND CALENDAR (RTCC)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the Real-Time Clock and Calendar, refer to the "PIC24F Family Reference Manual", "Real-Time Clock and Calendar (RTCC)" (DS39696).

The RTCC provides the user with a Real-Time Clock and Calendar (RTCC) function that can be calibrated.

Key features of the RTCC module are:

- · Operates in Sleep and Retention Sleep modes

- · Selectable clock source

- Provides hours, minutes and seconds using 24-hour format

- · Visibility of one half second period

- Provides calendar weekday, date, month and year

- Alarm-configurable for half a second, one second, 10 seconds, one minute, 10 minutes, one hour, one day, one week, one month or one year

- · Alarm repeat with decrementing counter

- · Alarm with indefinite repeat chime

- Year 2000 to 2099 leap year correction

- · BCD format for smaller software overhead

- Optimized for long term battery operation

- User calibration of the 32.768 kHz clock crystal/32K INTRC frequency with periodic auto-adjust

- · Optimized for long term battery operation

- · Fractional second synchronization

- Calibration to within ±2.64 seconds error per month

- · Calibrates up to 260 ppm of crystal error

- Ability to periodically wake-up external devices without CPU intervention (external power control)

- · Power control output for external circuit control

- · Calibration takes effect every 15 seconds

- · Runs from any one of the following:

- External Real-Time Clock of 32.768 kHz

- Internal 31.25 kHz LPRC Clock

- 50 Hz or 60 Hz External Input

### 16.1 RTCC Source Clock

The user can select between the SOSC crystal oscillator, LPRC internal oscillator or an external 50 Hz/60 Hz power line input as the clock reference for the RTCC module. This gives the user an option to trade off system cost, accuracy and power consumption, based on the overall system needs.

### FIGURE 16-1: RTCC BLOCK DIAGRAM

| R/W-0              | R-0                                    | r-0                                             | R/W-0                                      | R/W-0             | R/W-0 | R/W-0           | R/W-0 |  |  |  |  |

|--------------------|----------------------------------------|-------------------------------------------------|--------------------------------------------|-------------------|-------|-----------------|-------|--|--|--|--|

| ADRC               | EXTSAM                                 | r                                               | SAMC4                                      | SAMC3             | SAMC2 | SAMC1           | SAMC0 |  |  |  |  |

| bit 15             |                                        |                                                 |                                            |                   |       |                 | bit   |  |  |  |  |

| R/W-0              | R/W-0                                  | R/W-0                                           | R/W-0                                      | R/W-0             | R/W-0 | R/W-0           | R/W-0 |  |  |  |  |

| ADCS7              | ADCS6                                  | ADCS5                                           | ADCS4                                      | ADCS3             | ADCS2 | ADCS1           | ADCS0 |  |  |  |  |

| bit 7              |                                        |                                                 | 1                                          |                   |       |                 | bit   |  |  |  |  |

| Legend:            |                                        | r = Reserved                                    | bit                                        |                   |       |                 |       |  |  |  |  |

| R = Readab         | le bit                                 | W = Writable                                    | ble bit U = Unimplemented bit, read as '0' |                   |       |                 |       |  |  |  |  |

| -n = Value a       | t POR                                  | '1' = Bit is set                                |                                            | '0' = Bit is clea | ared  | x = Bit is unkr | nown  |  |  |  |  |

| bit 13<br>bit 12-8 | 0 = A/D is fir<br><b>Reserved:</b> M   | Auto-Sample                                     | ]                                          | S                 |       |                 |       |  |  |  |  |

|                    | •<br>•<br>00001 = 1 T.<br>00000 = 0 T. |                                                 |                                            |                   |       |                 |       |  |  |  |  |

| bit 7-0            | 11111111-0                             | A/D Conversio<br>1000000 = Re<br>64 * TCY = TAC | served                                     | : bits            |       |                 |       |  |  |  |  |

|                    | •<br>00000001 =<br>00000000 =          | 2 * TCY = TAD                                   |                                            |                   |       |                 |       |  |  |  |  |

### REGISTER 19-3: AD1CON3: A/D CONTROL REGISTER 3

#### REGISTER 19-5: AD1CHS: A/D SAMPLE SELECT REGISTER (CONTINUED)

- bit 7-5 **CH0NA<2:0>:** Sample A Channel 0 Negative Input Select bits The same definitions as for CHONB<2:0>.

- bit 4-0 **CH0SA<4:0>:** Sample A Channel 0 Positive Input Select bits The same definitions as for CHONA<4:0>.

- Note 1: This is implemented on 44-pin devices only.

- 2: This is implemented on 28-pin and 44-pin devices only.

- 3: The band gap value used for this input is 2x or 4x the internal VBG, which is selected when PVCFG<1:0> = 1x.

### REGISTER 19-6: AD1CHITH: A/D SCAN COMPARE HIT REGISTER (HIGH WORD)<sup>(1)</sup>

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | R/W-0                | R/W-0                | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|----------------------|----------------------|-------|-------|-------|

| CHH23 | CHH22 | CHH21 | CHH20 <sup>(2)</sup> | CHH19 <sup>(2)</sup> | CHH18 | CHH17 | CHH16 |

| bit 7 |       |       |                      |                      |       |       | bit 0 |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 15-8 Unimplemented: Read as '0'.

bit 7-0 CHH<23:16>: A/D Compare Hit bits<sup>(2)</sup>

If CM<1:0> = 11:

1 = A/D Result Buffer x has been written with data or a match has occurred

0 = A/D Result Buffer x has not been written with data

For All Other Values of CM<1:0>:

- 1 = A match has occurred on A/D Result Channel x

- 0 = No match has occurred on A/D Result Channel x

Note 1: Unimplemented channels are read as '0'.

2: The CHH<20:19> bits are not implemented in 20-pin devices.

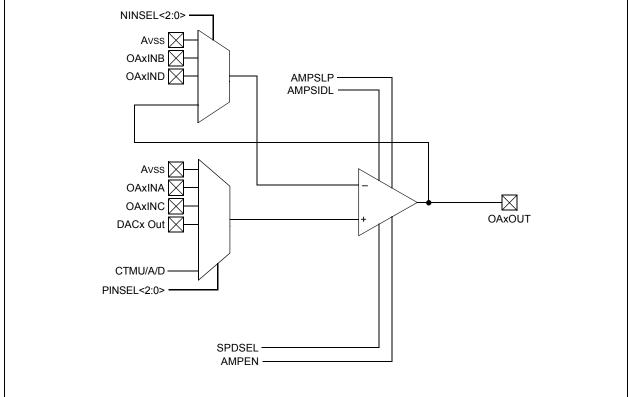

### 21.0 DUAL OPERATIONAL AMPLIFIER MODULE

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the *"PIC24F Family Reference Manual"*, *"Operational Amplifier (Op Amp)"* (DS30505). Device-specific information in this data sheet supersedes the information in the *"PIC24F Family Reference Manual"*.

PIC24FV16KM204 family devices include two operational amplifiers to complement the microcontroller's other analog features. They may be used to provide analog signal conditioning, either as stand-alone devices or in addition to other analog peripherals. The two op amps are functionally identical; the block diagram for a single amplifier is shown in Figure 21-1. Each op amp has these features:

- · Internal unity-gain buffer option

- Multiple input options each on the inverting and non-inverting amplifier inputs

- · Rail-to-rail input and output capabilities

- User-selectable option for regular or low-power operation

- User-selectable operation in Idle and Sleep modes

When using the op amps, it is recommended to set the ANSx and TRISx bits of both the input and output pins to configure them as analog pins. See **Section 11.2 "Configuring Analog Port Pins"** for more information.

NOTES:

| Param<br>No. | Symbol | Characteristic                                         | Min | Тур | Max | Units | Comments |

|--------------|--------|--------------------------------------------------------|-----|-----|-----|-------|----------|

| 300          | TRESP  | Response Time <sup>*(1)</sup>                          | _   | 150 | 400 | ns    |          |

| 301          | Тмс2о∨ | Comparator Mode Change to<br>Output Valid <sup>*</sup> | —   | _   | 10  | μs    |          |

### TABLE 27-26: COMPARATOR TIMING REQUIREMENTS

Parameters are characterized but not tested.

\*

**Note 1:** Response time is measured with one comparator input at (VDD – 1.5)/2, while the other input transitions from Vss to VDD.

#### TABLE 27-27: COMPARATOR VOLTAGE REFERENCE SETTLING TIME SPECIFICATIONS

| Param<br>No. | Symbol | Characteristic               | Min | Тур | Max | Units | Comments |

|--------------|--------|------------------------------|-----|-----|-----|-------|----------|

| VR310        | TSET   | Settling Time <sup>(1)</sup> |     |     | 10  | μS    |          |

Note 1: Settling time is measured while CVRSS = 1 and the CVR<3:0> bits transition from '0000' to '1111'.

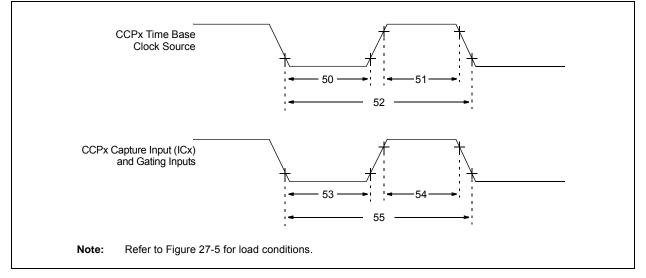

### FIGURE 27-10: CAPTURE/COMPARE/PWM TIMINGS (MCCPx, SCCPx MODULES)

### TABLE 27-28: CAPTURE/COMPARE/PWM REQUIREMENTS (MCCPx, SCCPx MODULES)

| Param<br>No. | Symbol | Characteristic                         | Min        | Max | Units | Conditions                         |

|--------------|--------|----------------------------------------|------------|-----|-------|------------------------------------|

| 50           | TCLKL  | CCPx Time Base Clock Source Low Time   | TCY/2      | _   | ns    |                                    |

| 51           | ТсікН  | CCPx Time Base Clock Source High Time  | Tcy/2      | _   | ns    |                                    |

| 52           | TCLK   | CCPx Time Base Clock Source Period     | Тсү        | -   | ns    |                                    |

| 53           | TccL   | CCPx Capture or Gating Input Low Time  | TCLK       | —   | ns    |                                    |

| 54           | ТссН   | CCPx Capture or Gating Input High Time | TCLK       | _   | ns    |                                    |

| 55           | TCCP   | CCPx Capture or Gating Input Period    | 2 * Tclk/N | —   | ns    | N = Prescale<br>Value (1, 4 or 16) |

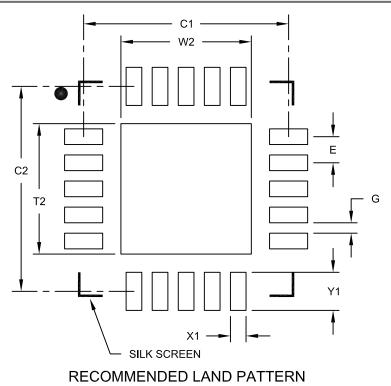

### 20-Lead Plastic Quad Flat, No Lead Package (ML) - 4x4 mm Body [QFN] With 0.40 mm Contact Length

|                            | MILLIMETERS |          |      |      |  |

|----------------------------|-------------|----------|------|------|--|

| Dimensio                   | n Limits    | MIN      | NOM  | MAX  |  |

| Contact Pitch              | E           | 0.50 BSC |      |      |  |

| Optional Center Pad Width  | W2          |          |      | 2.50 |  |

| Optional Center Pad Length | T2          |          |      | 2.50 |  |

| Contact Pad Spacing        | C1          |          | 3.93 |      |  |

| Contact Pad Spacing        | C2          |          | 3.93 |      |  |

| Contact Pad Width          | X1          |          |      | 0.30 |  |

| Contact Pad Length         | Y1          |          |      | 0.73 |  |

| Distance Between Pads      | G           | 0.20     |      |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2126A

### 48-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) – 6x6x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units  |           |          |      |

|------------------------|--------|-----------|----------|------|

| Dimension              | Limits | MIN       | NOM      | MAX  |

| Number of Pins         | Ν      |           | 48       |      |

| Pitch                  | е      |           | 0.40 BSC |      |

| Overall Height         | А      | 0.45      | 0.50     | 0.55 |

| Standoff               | A1     | 0.00      | 0.02     | 0.05 |

| Contact Thickness      | A3     | 0.127 REF |          |      |

| Overall Width          | Е      |           | 6.00 BSC |      |

| Exposed Pad Width      | E2     | 4.45      | 4.60     | 4.75 |

| Overall Length         | D      |           | 6.00 BSC |      |

| Exposed Pad Length     | D2     | 4.45      | 4.60     | 4.75 |

| Contact Width          | b      | 0.15      | 0.20     | 0.25 |

| Contact Length         | L      | 0.30      | 0.40     | 0.50 |

| Contact-to-Exposed Pad | K      | 0.20      | -        | -    |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-153A Sheet 2 of 2

NOTES:

NOTES: