# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 23                                                                            |

| Program Memory Size        | 16KB (5.5K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 1K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5V                                                                       |

| Data Converters            | A/D 19x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Through Hole                                                                  |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                       |

| Supplier Device Package    | 28-SPDIP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fv16km102-i-sp |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

## TABLE 1-5: PIC24FV16KM204 FAMILY PINOUT DESCRIPTION (CONTINUED)

|          |                                  |                                  | F             |                        |                |                                  |                                  | FV            |                        |                |     |        |                                                |

|----------|----------------------------------|----------------------------------|---------------|------------------------|----------------|----------------------------------|----------------------------------|---------------|------------------------|----------------|-----|--------|------------------------------------------------|

|          |                                  | I                                | Pin Numb      | ber                    |                |                                  | I                                | Pin Numb      | er                     |                |     |        |                                                |

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | I/O | Buffer | Description                                    |

| SCL1     | 12                               | 17                               | 14            | 44                     | 48             | 12                               | 17                               | 14            | 44                     | 48             | I/O | I2C    | MSSP1 I <sup>2</sup> C Clock                   |

| SDA1     | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | I/O | I2C    | MSSP1 I <sup>2</sup> C Data                    |

| SCL2     | _                                | 7                                | 4             | 24                     | 26             | _                                | 7                                | 4             | 24                     | 26             | I/O | I2C    | MSSP2 I <sup>2</sup> C Clock                   |

| SDA2     | _                                | 6                                | 3             | 23                     | 25             | _                                | 6                                | 3             | 23                     | 25             | I/O | I2C    | MSSP2 I <sup>2</sup> C Data                    |

| SCLKI    | 10                               | 12                               | 9             | 34                     | 37             | 10                               | 12                               | 9             | 34                     | 37             | Ι   | ST     | Secondary Clock Digital Input                  |

| SOSCI    | 9                                | 11                               | 8             | 33                     | 36             | 9                                | 11                               | 8             | 33                     | 36             | Ι   | ANA    | Secondary Oscillator Input                     |

| SOSCO    | 10                               | 12                               | 9             | 34                     | 37             | 10                               | 12                               | 9             | 34                     | 37             | Ι   | ANA    | Secondary Oscillator Output                    |

| T1CK     | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | Ι   | ST     | Timer1 Digital Input Cock                      |

| TCKIA    | 18                               | 26                               | 23            | 15                     | 16             | 18                               | 26                               | 23            | 15                     | 16             | Ι   | ST     | MCCP/SCCP Time Base Clock Input A              |

| TCKIB    | 6                                | 6                                | 3             | 23                     | 25             | 6                                | 6                                | 3             | 23                     | 25             | Ι   | ST     | MCCP/SCCP Time Base Clock Input B              |

| U1CTS    | 12                               | 17                               | 14            | 44                     | 48             | 12                               | 17                               | 14            | 44                     | 48             | Ι   | ST     | UART1 Clear-To-Send Input                      |

| U1RTS    | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | 0   | _      | UART1 Request-To-Send Output                   |

| U1BCLK   | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | 0   | —      | UART1 16x Baud Rate Clock Output               |

| U1RX     | 6                                | 6                                | 3             | 2                      | 2              | 6                                | 6                                | 3             | 2                      | 2              | Ι   | ST     | UART1 Receive                                  |

| U1TX     | 11                               | 16                               | 13            | 3                      | 3              | 11                               | 16                               | 13            | 3                      | 3              | 0   | _      | UART1 Transmit                                 |

| U2CTS    | _                                | 12                               | 9             | 34                     | 37             | _                                | 12                               | 9             | 34                     | 37             | I   | ST     | UART2 Clear-To-Send Input                      |

| U2RTS    | _                                | 11                               | 8             | 33                     | 36             | _                                | 11                               | 8             | 33                     | 36             | 0   | _      | UART2 Request-To-Send Output                   |

| U2BCLK   | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | 0   | —      | UART2 16x Baud Rate Clock Output               |

| U2RX     | _                                | 5                                | 2             | 22                     | 24             | —                                | 5                                | 2             | 22                     | 24             | Ι   | ST     | UART2 Receive                                  |

| U2TX     | _                                | 4                                | 1             | 21                     | 23             | —                                | 4                                | 1             | 21                     | 23             | 0   | _      | UART2 Transmit                                 |

| ULPWU    | 4                                | 4                                | 1             | 21                     | 23             | 4                                | 4                                | 1             | 21                     | 23             | Ι   | ANA    | Ultra Low-Power Wake-up Input                  |

| VCAP     | _                                | _                                |               | —                      | _              | 14                               | 20                               | 17            | 7                      | 7              | Р   | —      | Regulator External Filter Capacitor Connection |

| Vdd      | 20                               | 28                               | 25            | 17,28,28               | 18,30,30       | 20                               | 28                               | 25            | 17,28,28               | 18,30,30       | Р   | —      | Device Positive Supply Voltage                 |

| VDDCORE  | _                                | _                                | _             | —                      | _              | 14                               | 20                               | 17            | 7                      | 7              | Р   | —      | Microcontroller Core Supply Voltage            |

| Vpp      | 1                                | 1                                | 26            | 18                     | 19             | 1                                | 1                                | 26            | 18                     | 19             | Р   | —      | High-Voltage Programming Pin                   |

| VREF+    | 2                                | 2                                | 27            | 19                     | 21             | 2                                | 2                                | 27            | 19                     | 21             | I   | ANA    | A/D Reference Voltage Positive Input           |

| VREF-    | 3                                | 3                                | 28            | 20                     | 22             | 3                                | 3                                | 28            | 20                     | 22             | Ι   | ANA    | A/D Reference Voltage Negative Input           |

| Vss      | 19                               | 27                               | 24            | 16,29,29               | 17,31,31       | 19                               | 27                               | 24            | 16,29,29               | 17,31,31       | Р   | —      | Device Ground Return Voltage                   |

Legend: ANA = Analog level input/output, ST = Schmitt Trigger input buffer, I<sup>2</sup>C<sup>™</sup> = I<sup>2</sup>C/SMBus input buffer

## TABLE 4-10: MCCP3 REGISTER MAP

| File Name                | Addr. | Bit 15  | Bit 14                                                                                           | Bit 13  | Bit 12 | Bit 11  | Bit 10  | Bit 9   | Bit 8       | Bit 7        | Bit 6        | Bit 5   | Bit 4   | Bit 3   | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------------------|-------|---------|--------------------------------------------------------------------------------------------------|---------|--------|---------|---------|---------|-------------|--------------|--------------|---------|---------|---------|-------|-------|-------|---------------|

| CCP3CON1L <sup>(1)</sup> | 188h  | CCPON   | _                                                                                                | CCPSIDL | r      | TMRSYNC | CLKSEL2 | CLKSEL1 | CLKSEL0     | TMRPS1       | TMRPS0       | T32     | CCSEL   | MOD3    | MOD2  | MOD1  | MOD0  | 0000          |

| CCP3CON1H <sup>(1)</sup> | 18Ah  | OPSSRC  | RTRGEN                                                                                           | _       | _      | IOPS3   | IOPS2   | IOPS1   | IOPS0       | TRIGEN       | ONESHOT      | ALTSYNC | SYNC4   | SYNC3   | SYNC2 | SYNC1 | SYNC0 | 0000          |

| CCP3CON2L <sup>(1)</sup> | 18Ch  | PWMRSEN | ASDGM                                                                                            | _       | SSDG   | _       | _       | _       | _           | ASDG7        | ASDG6        | ASDG5   | ASDG4   | ASDG3   | ASDG2 | ASDG1 | ASDG0 | 0000          |

| CCP3CON2H <sup>(1)</sup> | 18Eh  | OENSYNC | _                                                                                                | OCFEN   | OCEEN  | OCDEN   | OCCEN   | OCBEN   | OCAEN       | ICGSM1       | ICGSM0       | _       | AUXOUT1 | AUXOUT0 | ICS2  | ICS1  | ICS0  | 0100          |

| CCP3CON3L <sup>(1)</sup> | 190h  | _       | _                                                                                                | _       | _      | _       | _       | _       | _           | _            | _            | DT5     | DT4     | DT3     | DT2   | DT1   | DT0   | 0000          |

| CCP3CON3H <sup>(1)</sup> | 192h  | OETRIG  | IG OSCNT2 OSCNT1 OSCNT0 — OUTM2 OUTM1 OUTM0 — — POLACE POLBDF PSSACE1 PSSACE0 PSSBDF1 PSSBDF0 00 |         |        |         |         |         |             |              |              |         |         | 0000    |       |       |       |               |

| CCP3STAT <sup>(1)</sup>  | 194h  | _       | CCPTRIG TRSET TRCLR ASEVT SCEVT ICDIS ICOV ICBNE 000                                             |         |        |         |         |         |             |              |              |         |         | 0000    |       |       |       |               |

| CCP3TMRL <sup>(1)</sup>  | 198h  |         |                                                                                                  |         |        |         |         | MCCF    | P3 Time Bas | se Register  | Low Word     |         |         |         |       | •     | •     | 0000          |

| CCP3TMRH <sup>(1)</sup>  | 19Ah  |         |                                                                                                  |         |        |         |         | MCCF    | 3 Time Bas  | e Register   | High Word    |         |         |         |       |       |       | 0000          |

| CCP3PRL <sup>(1)</sup>   | 19Ch  |         |                                                                                                  |         |        |         |         | MCCP3 1 | īme Base F  | Period Regis | ster Low Wor | d       |         |         |       |       |       | FFFF          |

| CCP3PRH <sup>(1)</sup>   | 19Eh  |         |                                                                                                  |         |        |         |         | МССРЗ Т | ime Base P  | eriod Regis  | ter High Wor | d       |         |         |       |       |       | FFFF          |

| CCP3RAL <sup>(1)</sup>   | 1A0h  |         |                                                                                                  |         |        |         |         | Οι      | tput Compa  | are 3 Data \ | Word A       |         |         |         |       |       |       | 0000          |

| CCP3RBL <sup>(1)</sup>   | 1A4h  |         | Output Compare 3 Data Word B                                                                     |         |        |         |         |         |             |              |              | 0000    |         |         |       |       |       |               |

| CCP3BUFL <sup>(1)</sup>  | 1A8h  |         |                                                                                                  |         |        |         |         | Input   | Capture 3 [ | Data Buffer  | Low Word     |         |         |         |       |       |       | 0000          |

| CCP3BUFH <sup>(1)</sup>  | 1AAh  |         | Input Capture 3 Data Buffer High Word                                                            |         |        |         |         |         |             |              |              | 0000    |         |         |       |       |       |               |

$\label{eq:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:loge$

Note 1: These registers are available only on PIC24F(V)16KM2XX devices.

#### TABLE 4-26: CTMU REGISTER MAP

| File Name | Addr. | Bit 15  | Bit 14  | Bit 13   | Bit 12   | Bit 11   | Bit 10   | Bit 9    | Bit 8    | Bit 7   | Bit 6   | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1   | Bit 0   | All<br>Resets |

|-----------|-------|---------|---------|----------|----------|----------|----------|----------|----------|---------|---------|----------|----------|----------|----------|---------|---------|---------------|

| CTMUCON1L | 35Ah  | CTMUEN  | _       | CTMUSIDL | TGEN     | EDGEN    | EDGSEQEN | IDISSEN  | CTTRIG   | ITRIM5  | ITRIM4  | ITRIM3   | ITRIM2   | ITRIM1   | ITRIM0   | IRNG1   | IRNG0   | 0000          |

| CTMUCON1H | 35Ch  | EDG1MOD | EDG1POL | EDG1SEL3 | EDG1SEL2 | EDG1SEL1 | EDG1SEL0 | EDG2STAT | EDG1STAT | EDG2MOD | EDG2POL | EDG2SEL3 | EDG2SEL2 | EDG2SEL1 | EDG2SEL0 | _       | _       | 0000          |

| CTMUCON2L | 35Eh  | —       | _       | —        | _        |          |          | —        | -        | -       | -       | _        | IRSTEN   |          | DISCHS2  | DISCHS1 | DISCHS0 | 0000          |

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

#### TABLE 4-27: ANSEL REGISTER MAP

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6    | Bit 5                | Bit 4    | Bit 3                | Bit 2                  | Bit 1                  | Bit 0                  | All<br>Resets       |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|----------|----------------------|----------|----------------------|------------------------|------------------------|------------------------|---------------------|

| ANSA         | 4E0h  | —      | _      | —      | —      | —      | —      | —     | _     | _     | —        | —                    | ANSA4(2) | ANSA3                | ANSA2                  | ANSA1                  | ANSA0                  | 001F <sup>(1)</sup> |

| ANSB         | 4E2h  | ANSB15 | ANSB14 | ANSB13 | ANSB12 | _      | _      | ANSB9 | ANSB8 | ANSB7 | ANSB6(2) | ANSB5 <sup>(2)</sup> | ANSB4    | ANSB3 <sup>(2)</sup> | ANSB2                  | ANSB1                  | ANSB0                  | <sub>F3FF</sub> (1) |

| ANSC         | 4E4h  | _      |        | —      | _      | —      | —      | _     |       |       | _        |                      | _        | _                    | ANSC2 <sup>(2,3)</sup> | ANSC1 <sup>(2,3)</sup> | ANSC0 <sup>(2,3)</sup> | 0007 <b>(1)</b>     |

**Legend:** x = unknown, u = unchanged, --- = unimplemented, q = value depends on condition, r = reserved.

**Note 1:** Reset value depends on the device type; the PIC24F16KM204 value is shown.

2: These bits are not implemented in 20-pin devices.

3: These bits are not implemented in 28-pin devices.

## TABLE 4-28: REAL-TIME CLOCK AND CALENDAR REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13  | Bit 12  | Bit 11  | Bit 10        | Bit 9          | Bit 8          | Bit 7   | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets       |

|-----------|-------|--------|--------|---------|---------|---------|---------------|----------------|----------------|---------|--------|-------|-------|-------|-------|-------|-------|---------------------|

| ALRMVAL   | 620h  |        |        |         |         |         | Alarm Value I | High Register  | Window Based   | on APTR | <1:0>  |       |       |       |       |       |       | XXXX                |

| ALCFGRPT  | 622h  | ALRMEN | CHIME  | AMASK3  | AMASK2  | AMASK1  | AMASK0        | ALRMPTR1       | ALRMPTR0       | ARPT7   | ARPT6  | ARPT5 | ARPT4 | ARPT3 | ARPT2 | ARPT1 | ARPT0 | <sub>0000</sub> (1) |

| RTCVAL    | 624h  |        |        |         |         | R       | TCC Value H   | igh Register W | /indow Based o | n RTCPT | R<1:0> |       |       |       |       |       |       | xxxx                |

| RCFGCAL   | 626h  | RTCEN  | _      | RTCWREN | RTCSYNC | HALFSEC | RTCOE         | RTCPTR1        | RTCPTR0        | CAL7    | CAL6   | CAL5  | CAL4  | CAL3  | CAL2  | CAL1  | CAL0  | 0000 <b>(1)</b>     |

| RTCPWC    | 628h  | PWCEN  | PWCPOL | PWCCPRE | PWCSPRE | RTCCLK1 | RTCCLK0       | RTCOUT1        | RTCOUT0        | _       | _      | _     | _     | _     | -     | _     | _     | <sub>0000</sub> (1) |

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition, r = reserved.

**Note 1:** Values are reset only on a VDD POR event.

| U-0          | U-0           | U-0                  | U-0              | U-0               | R/W-1            | R/W-0           | R/W-0   |

|--------------|---------------|----------------------|------------------|-------------------|------------------|-----------------|---------|

| —            | —             | —                    | _                | —                 | CCP5IP2          | CCP5IP1         | CCP5IP0 |

| bit 15       |               |                      |                  |                   |                  | -<br>-          | bit 8   |

|              |               |                      |                  |                   |                  |                 |         |

| U-0          | U-0           | U-0                  | U-0              | U-0               | R/W-1            | R/W-0           | R/W-0   |

| _            | —             | —                    |                  | —                 | INT1IP2          | INT1IP1         | INT1IP0 |

| bit 7        |               |                      |                  |                   |                  |                 | bit 0   |

| Legend:      |               |                      |                  |                   |                  |                 |         |

| R = Readat   | ole hit       | W = Writable b       | hit              | II = Unimpler     | nented bit, read | 1 as '0'        |         |

| -n = Value a |               | '1' = Bit is set     |                  | '0' = Bit is cle  |                  | x = Bit is unkr | own     |

|              |               |                      |                  |                   |                  |                 |         |

| bit 15-11    | Unimplemer    | nted: Read as '0     | '                |                   |                  |                 |         |

| bit 10-8     | CCP5IP<2:0    | >: Capture/Com       | pare 5 Event     | Interrupt Priorit | y bits           |                 |         |

|              | 111 = Interru | ipt is Priority 7 (ł | nighest priority | y interrupt)      |                  |                 |         |

|              | •             |                      |                  |                   |                  |                 |         |

|              | •             |                      |                  |                   |                  |                 |         |

|              |               | pt is Priority 1     |                  |                   |                  |                 |         |

|              |               | pt source is disa    |                  |                   |                  |                 |         |

| bit 7-3      | Unimplemer    | nted: Read as '0     | '                |                   |                  |                 |         |

| bit 2-0      |               | : External Interru   |                  |                   |                  |                 |         |

|              | 111 = Interru | ipt is Priority 7 (h | nighest priority | y interrupt)      |                  |                 |         |

|              | •             |                      |                  |                   |                  |                 |         |

|              | •             |                      |                  |                   |                  |                 |         |

|              |               | pt is Priority 1     | - la la al       |                   |                  |                 |         |

|              | 000 = interru | pt source is disa    | adied            |                   |                  |                 |         |

#### REGISTER 8-24: IPC5: INTERRUPT PRIORITY CONTROL REGISTER 5

NOTES:

| R/W-0         | U-0                                                              | R/W-0                                  | r-0            | R/W-0                                | R/W-0                  | R/W-0                  | R/W-0                  |

|---------------|------------------------------------------------------------------|----------------------------------------|----------------|--------------------------------------|------------------------|------------------------|------------------------|

| CCPON         |                                                                  | CCPSIDL                                | r              | TMRSYNC                              | CLKSEL2 <sup>(1)</sup> | CLKSEL1 <sup>(1)</sup> | CLKSEL0 <sup>(1)</sup> |

| bit 15        |                                                                  |                                        |                |                                      | •                      | •                      | bit 8                  |

|               |                                                                  |                                        |                |                                      |                        |                        |                        |

| R/W-0         | R/W-0                                                            | R/W-0                                  | R/W-0          | R/W-0                                | R/W-0                  | R/W-0                  | R/W-0                  |

| TMRPS1        | TMRPS0                                                           | T32                                    | CCSEL          | MOD3                                 | MOD2                   | MOD1                   | MOD0                   |

| bit 7         |                                                                  |                                        |                |                                      |                        |                        | bit (                  |

|               |                                                                  |                                        |                |                                      |                        |                        |                        |

| Legend:       |                                                                  | r = Reserved I                         |                |                                      |                        |                        |                        |

| R = Readable  |                                                                  | W = Writable I                         | oit            |                                      | nented bit, read       |                        |                        |

| -n = Value at | POR                                                              | '1' = Bit is set                       |                | '0' = Bit is clea                    | ared                   | x = Bit is unkn        | own                    |

| bit 15        | CCPON: CCF                                                       | x Module Enat                          | ole bit        |                                      |                        |                        |                        |

|               | 1 = Module is<br>0 = Module is                                   |                                        | an operating r | node specified b                     | by the MOD<3:          | 0> control bits        |                        |

| bit 14        | Unimplemen                                                       | ted: Read as 'd                        | )'             |                                      |                        |                        |                        |

| bit 13        | CCPSIDL: CO                                                      | CPx Stop in Idle                       | Mode Bit       |                                      |                        |                        |                        |

|               |                                                                  | ues module op<br>s module opera        |                | device enters lo<br>ode              | lle mode               |                        |                        |

| bit 12        | Reserved: Ma                                                     | -                                      |                |                                      |                        |                        |                        |

| bit 11        | TMRSYNC: T                                                       | ime Base Cloc                          | k Synchroniza  | ation bit                            |                        |                        |                        |

|               | (CLKSEL<br>0 = Synchron                                          | <b>&lt;2:0&gt;</b> ≠ 000)              |                | k is selected and<br>lock is selecte | -                      |                        | -                      |

| bit 10-8      |                                                                  | >: CCPx Time                           | Base Clock S   | elect bits <sup>(1)</sup>            |                        |                        |                        |

|               | 110 = Externa<br>101 = CLC1<br>100 = Reserv<br>011 = LPRC (      | 31 kHz source<br>dary Oscillator<br>ed | t              |                                      |                        |                        |                        |

| bit 7-6       | TMRPS<1:0>                                                       | : Time Base Pr                         | escale Select  | t bits                               |                        |                        |                        |

|               | 11 = 1:64 Pre<br>10 = 1:16 Pre<br>01 = 1:4 Pres<br>00 = 1:1 Pres | scaler<br>caler                        |                |                                      |                        |                        |                        |

| bit 5         | T32: 32-Bit Ti                                                   | me Base Selec                          | t bit          |                                      |                        |                        |                        |

|               |                                                                  |                                        |                | e edge output co<br>e edge output co |                        |                        |                        |

| bit 4         |                                                                  | ure/Compare N                          |                |                                      |                        |                        |                        |

|               | 1 = Input Cap                                                    | -                                      |                |                                      |                        |                        |                        |

## REGISTER 13-1: CCPxCON1L: CCPx CONTROL 1 LOW REGISTERS

## 14.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on MSSP, refer to the "PIC24F Family Reference Manual".

The Master Synchronous Serial Port (MSSP) module is an 8-bit serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, Shift registers, display drivers, A/D Converters, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>)

- Full Master mode

- Slave mode (with general address call)

The SPI interface supports these modes in hardware:

- Master mode

- Slave mode

- · Daisy-Chaining Operation in Slave mode

- Synchronized Slave Operation

The I<sup>2</sup>C interface supports the following modes in hardware:

- Master mode

- · Multi-Master mode

- Slave mode with 10-Bit and 7-Bit Addressing and Address Masking

- Byte NACKing

- Selectable Address and Data Hold, and Interrupt Masking

## 14.1 I/O Pin Configuration for SPI

In SPI Master mode, the MSSP module will assert control over any pins associated with the SDOx and SCKx outputs. This does not automatically disable other digital functions associated with the pin and may result in the module driving the digital I/O port inputs. To prevent this, the MSSP module outputs must be disconnected from their output pins while the module is in SPI Master mode. While disabling the module temporarily may be an option, it may not be a practical solution in all applications.

The SDOx and SCKx outputs for the module can be selectively disabled by using the SDOxDIS and SCKxDIS bits in the PADCFG1 register (Register 14-10). Setting the bit disconnects the corresponding output for a particular module from its assigned pin.

'1' = Bit is set

### REGISTER 14-8: SSPxADD: MSSPx SLAVE ADDRESS/BAUD RATE GENERATOR REGISTER

| U-0          | U-0   | U-0          | U-0   | U-0          | U-0              | U-0      | U-0   |

|--------------|-------|--------------|-------|--------------|------------------|----------|-------|

| —            | —     | —            |       | —            | _                | —        | _     |

| bit 15       |       |              |       |              |                  |          | bit 8 |

|              |       |              |       |              |                  |          |       |

| R/W-0        | R/W-0 | R/W-0        | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

| ADD7         | ADD6  | ADD5         | ADD4  | ADD3         | ADD2             | ADD1     | ADD0  |

| bit 7        |       |              |       |              |                  |          | bit 0 |

|              |       |              |       |              |                  |          |       |

| Legend:      |       |              |       |              |                  |          |       |

| R = Readable | e bit | W = Writable | bit   | U = Unimplen | nented bit, read | l as '0' |       |

'0' = Bit is cleared

x = Bit is unknown

bit 15-8 **Unimplemented:** Read as '0'

-n = Value at POR

bit 7-0

ADD<7:0>: Slave Address/Baud Rate Generator Value bits

SPI Master and I<sup>2</sup>C™ Master modes:

Reload value for the Baud Rate Generator. Clock period is (([SPxADD] + 1) \* 2)/Fosc.

I<sup>2</sup>C Slave modes:

Represents 7 or 8 bits of the slave address, depending on the addressing mode used:

7-Bit mode:

Address is ADD<7:1>; ADD<0> is ignored.

10-Bit LSb mode:

ADD<7:0> are the Least Significant bits of the address.

10-Bit MSb mode:

ADD<2:1> are the two Most Significant bits of the address; ADD<7:3> are always '11110' as a specification requirement; ADD<0> is ignored.

## REGISTER 14-9: SSPxMSK: I<sup>2</sup>C<sup>™</sup> SLAVE ADDRESS MASK REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-1               |

|-------|-------|-------|-------|-------|-------|-------|---------------------|

| MSK7  | MSK6  | MSK5  | MSK4  | MSK3  | MSK2  | MSK1  | MSK0 <sup>(1)</sup> |

| bit 7 |       |       |       |       |       |       | bit 0               |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-8 | Unimplemented: Read as '0'                              |

|----------|---------------------------------------------------------|

| bit 7-0  | MSK<7:0>: Slave Address Mask Select bits <sup>(1)</sup> |

|          | 1 = Masking of corresponding bit of SSPxADD is enabled  |

|          | 0 = Masking of corresponding bit of SSPxADD is disabled |

Note 1: MSK0 is not used as a mask bit in 7-bit addressing.

#### 16.2.6 ALRMVAL REGISTER MAPPINGS

## REGISTER 16-8: ALMTHDY: ALARM MONTH AND DAY VALUE REGISTER<sup>(1)</sup>

| U-0      | U-0 | U-0     | R/W-x   | R/W-x            | R/W-x            | R/W-x   | R/W-x            |

|----------|-----|---------|---------|------------------|------------------|---------|------------------|

| —        | —   | —       | MTHTEN0 | MTHONE3 MTHONE2  |                  | MTHONE1 | MTHONE0          |

| bit 15   |     |         |         |                  |                  |         | bit 8            |

|          |     |         |         |                  |                  |         |                  |

| 11.0     |     | D/1/    |         | D/14/            |                  |         |                  |

| U-0      | U-0 | R/W-x   | R/W-x   | R/W-x            | R/W-x            | R/W-x   | R/W-x            |

| <u> </u> |     | DAYTEN1 | DAYTEN0 | R/W-X<br>DAYONE3 | R/W-X<br>DAYONE2 | DAYONE1 | R/W-x<br>DAYONE0 |

### Legend:

| Legena:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-13<br>bit 12 | <b>Unimplemented:</b> Read as '0'<br><b>MTHTEN0:</b> Binary Coded Decimal Value of Month's Tens Digit bit<br>Contains a value of '0' or '1'. |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| bit 11-8            | MTHONE<3:0>: Binary Coded Decimal Value of Month's Ones Digit bits<br>Contains a value from 0 to 9.                                          |

| bit 7-6             | Unimplemented: Read as '0'                                                                                                                   |

| bit 5-4             | <b>DAYTEN&lt;1:0&gt;:</b> Binary Coded Decimal Value of Day's Tens Digit bits<br>Contains a value from 0 to 3.                               |

| bit 3-0             | <b>DAYONE&lt;3:0&gt;:</b> Binary Coded Decimal Value of Day's Ones Digit bits<br>Contains a value from 0 to 9.                               |

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

## REGISTER 16-9: ALWDHR: ALARM WEEKDAY AND HOURS VALUE REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0    | U-0    | U-0    | R/W-x  | R/W-x  | R/W-x  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | —      | —      | —      | WDAY2  | WDAY1  | WDAY0  |

| bit 15 |     |        |        |        |        |        | bit 8  |

|        |     |        |        |        |        |        |        |

| U-0    | U-0 | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  |

| —      | —   | HRTEN1 | HRTEN0 | HRONE3 | HRONE2 | HRONE1 | HRONE0 |

| bit 7  |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-11 | Unimplemented: Read as '0'                                                                   |

|-----------|----------------------------------------------------------------------------------------------|

| bit 10-8  | WDAY<2:0>: Binary Coded Decimal Value of Weekday Digit bits<br>Contains a value from 0 to 6. |

|           |                                                                                              |

| bit 7-6   | Unimplemented: Read as '0'                                                                   |

| bit 5-4   | HRTEN<1:0>: Binary Coded Decimal Value of Hour's Tens Digit bits                             |

|           | Contains a value from 0 to 2.                                                                |

| bit 3-0   | HRONE<3:0>: Binary Coded Decimal Value of Hour's Ones Digit bits                             |

|           | Contains a value from 0 to 9.                                                                |

|           |                                                                                              |

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

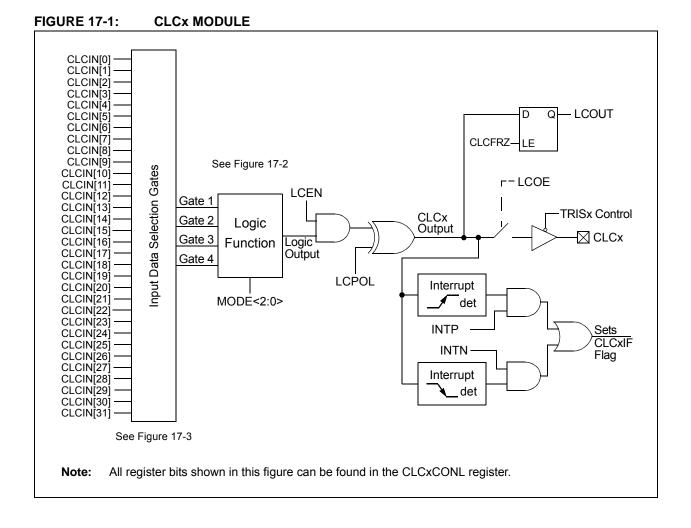

## 17.0 CONFIGURABLE LOGIC CELL (CLC)

The Configurable Logic Cell (CLC) module allows the user to specify combinations of signals as inputs to a logic function and to use the logic output to control other peripherals or I/O pins. This provides greater flex-ibility and potential in embedded designs since the CLC

module can operate outside the limitations of software execution and supports a vast amount of output designs.

There are four input gates to the selected logic function. These four input gates select from a pool of up to 32 signals that are selected using four data source selection multiplexers. Figure 17-1 shows an overview of the module. Figure 17-3 shows the details of the data source multiplexers and logic input gate connections.

### REGISTER 17-3: CLCxSEL: CLCx INPUT MUX SELECT REGISTER (CONTINUED)

- bit 6-4 DS2<2:0>: Data Selection MUX 2 Signal Selection bits

- 111 = MCCP2 Compare Event Flag (CCP2IF)

- 110 = MCCP1 Compare Event Flag (CCP1IF)

- 101 = Digital logic low

- 100 = A/D end of conversion event

- For CLC1:

- 011 = UART1 TX

- 010 = Comparator 1 output

- 001 = CLC2 output

- 000 = CLCINB I/O pin

- For CLC2:

- 011 = UART2 TX

- 010 = Comparator 1 output

- 001 = CLC1 output

- 000 = CLCINB I/O pin

- bit 3 Unimplemented: Read as '0'

- bit 2-0 DS1<2:0>: Data Selection MUX 1 Signal Selection bits

- 111 = SCCP5 Compare Event Flag (CCP5IF)

- 110 = SCCP4 Compare Event Flag (CCP4IF)

- 101 = Digital logic low

- 100 = 8 MHz FRC clock source

- 011 = LPRC clock source

- 010 = SOSC clock source

- 001 = System clock (TCY)

- 000 = CLCINA I/O pin

### REGISTER 17-5: CLCxGLSH: CLCx GATE LOGIC INPUT SELECT HIGH REGISTER (CONTINUED)

| bit 3 | G3D2T: Gate 3 Data Source 2 True Enable bit                  |

|-------|--------------------------------------------------------------|

|       | 1 = The Data Source 2 inverted signal is enabled for Gate 3  |

|       | 0 = The Data Source 2 inverted signal is disabled for Gate 3 |

| bit 2 | G3D2N: Gate 3 Data Source 2 Negated Enable bit               |

|       | 1 = The Data Source 2 inverted signal is enabled for Gate 3  |

|       | 0 = The Data Source 2 inverted signal is disabled for Gate 3 |

| bit 1 | G3D1T: Gate 3 Data Source 1 True Enable bit                  |

|       | 1 = The Data Source 1 inverted signal is enabled for Gate 3  |

|       | 0 = The Data Source 1 inverted signal is disabled for Gate 3 |

| bit 0 | G3D1N: Gate 3 Data Source 1 Negated Enable bit               |

|       | 1 = The Data Source 1 inverted signal is enabled for Gate 3  |

|       | 0 = The Data Source 1 inverted signal is disabled for Gate 3 |

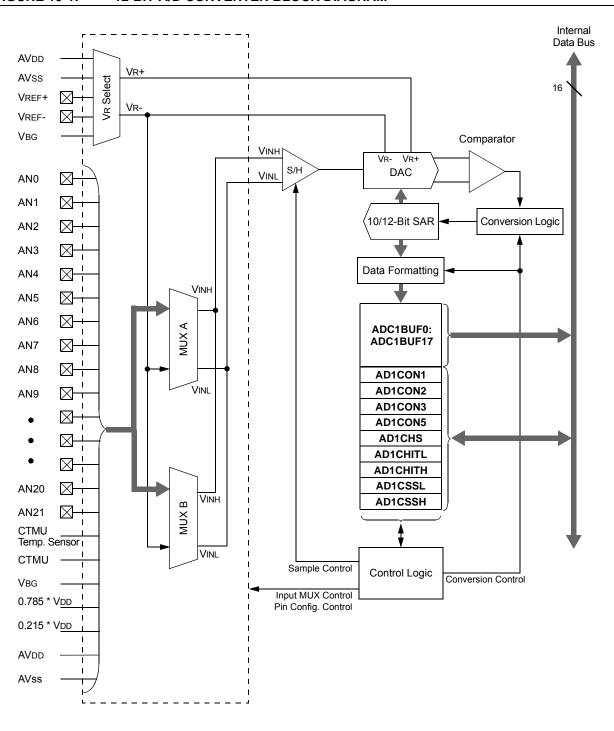

## FIGURE 19-1: 12-BIT A/D CONVERTER BLOCK DIAGRAM

| R/W-0              | R-0                                    | r-0                                              | R/W-0  | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|--------------------|----------------------------------------|--------------------------------------------------|--------|-------------------|------------------|-----------------|-------|

| ADRC               | EXTSAM                                 | r                                                | SAMC4  | SAMC3             | SAMC2            | SAMC1           | SAMC0 |

| bit 15             |                                        |                                                  |        |                   |                  |                 | bit 8 |

| R/W-0              | R/W-0                                  | R/W-0                                            | R/W-0  | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

| ADCS7              | ADCS6                                  | ADCS5                                            | ADCS4  | ADCS3             | ADCS2            | ADCS1           | ADCS0 |

| bit 7              | I                                      |                                                  | •      |                   | •                |                 | bit   |

| Legend:            |                                        | r = Reserved                                     | bit    |                   |                  |                 |       |

| R = Readab         | le bit                                 | W = Writable                                     | bit    | U = Unimplen      | nented bit, read | d as '0'        |       |

| -n = Value a       | t POR                                  | '1' = Bit is set                                 |        | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

| bit 13<br>bit 12-8 | 0 = A/D is fir<br><b>Reserved:</b> M   | Auto-Sample                                      | ]      | S                 |                  |                 |       |

|                    | •<br>•<br>00001 = 1 T.<br>00000 = 0 T. |                                                  |        |                   |                  |                 |       |

| bit 7-0            | 11111111-0                             | A/D Conversio<br>1000000 = Re:<br>64 * Tcy = Tad | served | t bits            |                  |                 |       |

|                    | •<br>00000001 =<br>00000000 =          | 2 * TCY = TAD                                    |        |                   |                  |                 |       |

## REGISTER 19-3: AD1CON3: A/D CONTROL REGISTER 3

| R/W-0        | U-0           | R/W-0                                   | R/W-0          | R/W-0                            | U-0              | R/W-0           | R/W-0        |

|--------------|---------------|-----------------------------------------|----------------|----------------------------------|------------------|-----------------|--------------|

| DACEN        |               | DACSIDL                                 | DACSLP         | DACFM                            |                  | SRDIS           | DACTRIG      |

| bit 15       |               |                                         | 27.002         |                                  |                  | 0.12.0          | bit 8        |

| R/W-0        | R/W-0         | R/W-0                                   | R/W-0          | R/W-0                            | R/W-0            | R/W-0           | R/W-0        |

| DACOE        | DACTSEL4      | DACTSEL3                                | DACTSEL2       | DACTSEL1                         | DACTSEL0         | DACREF1         | DACREF0      |

| bit 7        |               |                                         |                |                                  |                  |                 | bit 0        |

| Legend:      |               |                                         |                |                                  |                  |                 |              |

| R = Readab   | le bit        | W = Writable                            | bit            | U = Unimplen                     | nented bit, read | l as '0'        |              |

| -n = Value a | t POR         | '1' = Bit is set                        |                | '0' = Bit is clea                |                  | x = Bit is unkr | nown         |

|              |               |                                         |                |                                  |                  |                 | -            |

| bit 15       | DACEN: DAC    | x Enable bit                            |                |                                  |                  |                 |              |

|              | 1 = Module is | s enabled                               |                |                                  |                  |                 |              |

|              | 0 = Module is | s disabled                              |                |                                  |                  |                 |              |

| bit 14       | Unimplement   | ted: Read as 'd                         | )'             |                                  |                  |                 |              |

| bit 13       | DACSIDL: DA   | ACx Stop in Idle                        | e Mode bit     |                                  |                  |                 |              |

|              |               | ues module op<br>s module opera         |                | device enters lo<br>ode          | lle mode         |                 |              |

| bit 12       | DACSLP: DA    | Cx Enable Per                           | ipheral During | Sleep bit                        |                  |                 |              |

|              |               |                                         |                | ent value of DA<br>; DACxOUT pi  |                  |                 | nd LATx bits |

| bit 11       | DACFM: DAC    | x Data Format                           | Select bit     |                                  |                  |                 |              |

|              |               | ft justified (data<br>ht justified (dat |                |                                  |                  |                 |              |

| bit 10       | Unimplement   | ted: Read as '0                         | )'             |                                  |                  |                 |              |

| bit 9        | SRDIS: Soft F | Reset Disable b                         | oit            |                                  |                  |                 |              |

|              |               |                                         |                | only on a POR<br>on any type of  |                  | :               |              |

| bit 8        |               | ACx Trigger Inp                         |                |                                  |                  |                 |              |

|              |               |                                         |                | selected (by D<br>as DACxDAT is  |                  |                 | ed)          |

| bit 7        | DACOE: DAC    | Cx Output Enab                          | le bit         |                                  |                  |                 |              |

|              | 1 = DACx out  | put pin is enabl                        | led and driven | on the DACxO<br>put is available |                  | her peripherals | only         |

| Note 1.      |               | in configuration                        |                |                                  | -1.0~)           |                 | -            |

## REGISTER 20-1: DACxCON: DACx CONTROL REGISTER

**Note 1:** BGBUF1 voltage is configured by BUFREF<1:0> (BUFCON0<1:0>).

| R/P-1        | R/P-1                                                                                                        | R/P-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R/P-1           | R/P-1             | R/P-1            | R/P-1           | R/P-1          |  |  |

|--------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------|------------------|-----------------|----------------|--|--|

| FWDTEN1      | WINDIS                                                                                                       | FWDTEN0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | FWPSA           | WDTPS3            | WDTPS2           | WDTPS1          | WDTPS0         |  |  |

| bit 7        |                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                 |                   |                  |                 | bit (          |  |  |

| Legend:      |                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                 |                   |                  |                 |                |  |  |

| R = Readab   | ole bit                                                                                                      | P = Programn                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | nable bit       | U = Unimplen      | nented bit, read | d as '0'        |                |  |  |

| -n = Value a | at POR                                                                                                       | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                 | '0' = Bit is clea | ared             | x = Bit is unkr | nown           |  |  |

| bit 7,5      | FWDTEN<1:0                                                                                                   | >: Watchdog Ti                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | mer Enable bi   | ts                |                  |                 |                |  |  |

|              |                                                                                                              | enabled in hardw                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                 |                   |                  |                 |                |  |  |

|              |                                                                                                              | controlled with the<br>enabled only white the second se |                 | Ų                 | s disabled in Sl | leen: SWDTEN    | hit is disable |  |  |