#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-><F

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I²C, IrDA, LINbus, SPI, UART/USART                                            |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 23                                                                            |

| Program Memory Size        | 16KB (5.5K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 1K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5V                                                                       |

| Data Converters            | A/D 19x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                |

| Supplier Device Package    | 28-SSOP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fv16km102-i-ss |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Pin Diagrams (Continued)

|     | 20-Pin QFN<br>$\begin{array}{c ccccccccccccccccccccccccccccccccccc$              |  |  |  |  |  |  |  |  |

|-----|----------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Dia | Pin Features                                                                     |  |  |  |  |  |  |  |  |

| Pin | PIC24F08KM101 PIC24FV08KM101                                                     |  |  |  |  |  |  |  |  |

| 1   | PGED1/AN2/CTCMP/ULPWU/C1IND/OC2A/CN4/RB0                                         |  |  |  |  |  |  |  |  |

| 2   | PGEC1/AN3/C1INC/CTED12/CN5/RB1                                                   |  |  |  |  |  |  |  |  |

| 3   | AN4/U1RX/TCKIB/CTED13/CN6/RB2                                                    |  |  |  |  |  |  |  |  |

| 4   | OSCI/CLKI/AN13/C1INB/CN30/RA2                                                    |  |  |  |  |  |  |  |  |

| 5   | OSCO/CLKO/AN14/C1INA/CN29/RA3                                                    |  |  |  |  |  |  |  |  |

| 6   | PGED3/SOSCI/AN15/CLCINA/CN1/RB4                                                  |  |  |  |  |  |  |  |  |

| 7   | PGEC3/SOSCO/SCLKI/AN16/PWRLCLK/CLCINB/CN0/RA4                                    |  |  |  |  |  |  |  |  |

| 8   | AN19/U1TX/CTED1/INT0/CN23/RB7 AN19/U1TX/IC1/OC1A/CTED1/INT0/CN23/RB7             |  |  |  |  |  |  |  |  |

| 9   | AN20/SCL1/UICTS/OC1B/CTED10/CN22/RB8                                             |  |  |  |  |  |  |  |  |

| 10  | AN21/SDA1/T1CK/U1RTS/U1BCLK/IC2/CLC10/CTED4/CN21/RB9                             |  |  |  |  |  |  |  |  |

| 11  | IC1/OC1A/INT2/CN8/RA6 VCAP OR VDDCORE                                            |  |  |  |  |  |  |  |  |

| 12  | AN12/HLVDIN/SCK1/OC1C/CTED2/CN14/RB12 AN12/HLVDIN/SCK1/OC1C/CTED2/INT2/CN14/RB12 |  |  |  |  |  |  |  |  |

| 13  | AN11/SDO1/OCFB/OC1D/CTPLS/CN13/RB13                                              |  |  |  |  |  |  |  |  |

| 14  | CVREF/AN10/SDI1/C1OUT/OCFA/CTED5/INT1/CN12/RB14                                  |  |  |  |  |  |  |  |  |

| 15  | AN9/REFO/SS1/TCKIA/CTED6/CN11/RB15                                               |  |  |  |  |  |  |  |  |

| 16  | Vss/AVss                                                                         |  |  |  |  |  |  |  |  |

| 17  | Vdd/AVdd                                                                         |  |  |  |  |  |  |  |  |

| 18  | MCLR/Vpp/RA5                                                                     |  |  |  |  |  |  |  |  |

| 19  | PGEC2/CVREF+ /VREF+/AN0/CN2/RA0                                                  |  |  |  |  |  |  |  |  |

| 20  | PGED2/CVREF-/VREF-/AN1/CN3/RA1                                                   |  |  |  |  |  |  |  |  |

### TABLE 1-2: DEVICE FEATURES FOR THE PIC24F16KM104 FAMILY

|                                                     |                                                                                                                                                     |                    |                       | 1                                        |  |  |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------|------------------------------------------|--|--|

| Features                                            | PIC24F16KM104                                                                                                                                       | PIC24F16KM102      | PIC24F08KM102         | PIC24F08KM101                            |  |  |

| Operating Frequency                                 |                                                                                                                                                     | DC-3               | 2 MHz                 |                                          |  |  |

| Program Memory (bytes)                              | 16K                                                                                                                                                 | 16K                | 8K                    | 8K                                       |  |  |

| Program Memory (instructions)                       | 5632                                                                                                                                                | 5632               | 2816                  | 2816                                     |  |  |

| Data Memory (bytes)                                 |                                                                                                                                                     | 10                 | 24                    |                                          |  |  |

| Data EEPROM Memory (bytes)                          |                                                                                                                                                     | 5                  | 12                    |                                          |  |  |

| Interrupt Sources (soft vectors/NMI traps)          |                                                                                                                                                     | 25 (2              | 21/4)                 |                                          |  |  |

| Voltage Range                                       |                                                                                                                                                     | 1.8-               | 3.6V                  |                                          |  |  |

| I/O Ports                                           | PORTA<11:0><br>PORTB<15:0><br>PORTC<9:0>                                                                                                            | PORTA<br>PORTB     |                       | PORTA<6:0><br>PORTB<15:12,9:7,<br>4,2:0> |  |  |

| Total I/O Pins                                      | 38                                                                                                                                                  | 24                 | ŀ                     | 18                                       |  |  |

| Timers                                              | (One 16-bit timer, t                                                                                                                                |                    | 5<br>Ps with up to tv | vo 16/32 timers each)                    |  |  |

| Capture/Compare/PWM modules<br>MCCP<br>SCCP         |                                                                                                                                                     |                    | 1                     |                                          |  |  |

| Serial Communications<br>MSSP<br>UART               |                                                                                                                                                     |                    | 1                     |                                          |  |  |

| Input Change Notification Interrupt                 | 37                                                                                                                                                  | 23                 | }                     | 17                                       |  |  |

| 12-Bit Analog-to-Digital Module<br>(input channels) | 22                                                                                                                                                  | 19                 | )                     | 16                                       |  |  |

| Analog Comparators                                  |                                                                                                                                                     |                    | 1                     |                                          |  |  |

| 8-Bit Digital-to-Analog Converters                  |                                                                                                                                                     | _                  | _                     |                                          |  |  |

| Operational Amplifiers                              |                                                                                                                                                     | -                  | _                     |                                          |  |  |

| Charge Time Measurement Unit (CTMU)                 |                                                                                                                                                     | Y                  | es                    |                                          |  |  |

| Real-Time Clock and Calendar (RTCC)                 |                                                                                                                                                     | -                  | _                     |                                          |  |  |

| Configurable Logic Cell (CLC)                       |                                                                                                                                                     |                    | 1                     |                                          |  |  |

| Resets (and delays)                                 | POR, BOR, RESET Instruction, MCLR, WDT, Illegal Opcode,<br>REPEAT Instruction, Hardware Traps, Configuration Word Mismatch<br>(PWRT, OST, PLL Lock) |                    |                       |                                          |  |  |

| Instruction Set                                     | 76 Base Inst                                                                                                                                        | ructions, Multiple | e Addressing N        | Iode Variations                          |  |  |

| Packages                                            | 44-Pin<br>QFN/TQFP,<br>48-Pin UQFN                                                                                                                  | 28-F<br>SPDIP/SSOP |                       | 20-Pin<br>SOIC/SSOP/PDIP                 |  |  |

### 2.2 Power Supply Pins

### 2.2.1 DECOUPLING CAPACITORS

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS, is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A 0.1  $\mu$ F (100 nF), 10-20V capacitor is recommended. The capacitor should be a low-ESR device, with a resonance frequency in the range of 200 MHz and higher. Ceramic capacitors are recommended.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is no greater than 0.25 inch (6 mm).

- Handling high-frequency noise: If the board is experiencing high-frequency noise (upward of tens of MHz), add a second ceramic type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of  $0.01 \ \mu\text{F}$  to  $0.001 \ \mu\text{F}$ . Place this second capacitor next to each primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible (e.g.,  $0.1 \ \mu\text{F}$  in parallel with  $0.001 \ \mu\text{F}$ ).

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB trace inductance.

### 2.2.2 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits, including microcontrollers, to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device, and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu F$  to 47  $\mu F$ .

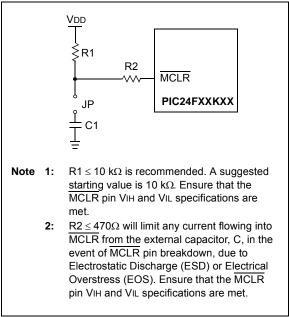

### 2.3 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions: device Reset, and device programming and debugging. If programming and debugging are not required in the end application, a direct connection to VDD may be all that is required. The addition of other components, to help increase the application's resistance to spurious Resets from voltage sags, may be beneficial. A typical configuration is shown in Figure 2-1. Other circuit designs may be implemented, depending on the application's requirements.

During programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the  $\overline{\text{MCLR}}$  pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R1 and C1 will need to be adjusted based on the application and PCB requirements. For example, it is recommended that the capacitor, C1, be isolated from the  $\overline{\text{MCLR}}$  pin during programming and debugging operations by using a jumper (Figure 2-2). The jumper is replaced for normal run-time operations.

Any components associated with the  $\overline{\text{MCLR}}$  pin should be placed within 0.25 inch (6 mm) of the pin.

### FIGURE 2-2: EXAMPLE OF MCLR PIN CONNECTIONS

### 2.4.1 CONSIDERATIONS FOR CERAMIC CAPACITORS

In recent years, large value, low-voltage, surface-mount ceramic capacitors have become very cost effective in sizes up to a few tens of microfarad. The low-ESR, small physical size and other properties make ceramic capacitors very attractive in many types of applications.

Ceramic capacitors are suitable for use with the internal voltage regulator of this microcontroller. However, some care is needed in selecting the capacitor to ensure that it maintains sufficient capacitance over the intended operating range of the application.

Typical low-cost, 10  $\mu$ F ceramic capacitors are available in X5R, X7R and Y5V dielectric ratings (other types are also available, but are less common). The initial tolerance specifications for these types of capacitors are often specified as ±10% to ±20% (X5R and X7R), or -20%/+80% (Y5V). However, the effective capacitance that these capacitors provide in an application circuit will also vary based on additional factors, such as the applied DC bias voltage and the temperature. The total in-circuit tolerance is, therefore, much wider than the initial tolerance specification.

The X5R and X7R capacitors typically exhibit satisfactory temperature stability (ex:  $\pm 15\%$  over a wide temperature range, but consult the manufacturer's data sheets for exact specifications). However, Y5V capacitors typically have extreme temperature tolerance specifications of  $\pm 22\%/-82\%$ . Due to the extreme temperature tolerance, a 10 µF nominal rated Y5V type capacitor may not deliver enough total capacitance to meet minimum internal voltage regulator stability and transient response requirements. Therefore, Y5V capacitors are not recommended for use with the internal regulator if the application must operate over a wide temperature range.

In addition to temperature tolerance, the effective capacitance of large value ceramic capacitors can vary substantially, based on the amount of DC voltage applied to the capacitor. This effect can be very significant, but is often overlooked or is not always documented.

A typical DC bias voltage vs. capacitance graph for X7R type capacitors is shown in Figure 2-4.

#### DC BIAS VOLTAGE vs. FIGURE 2-4: CAPACITANCE **CHARACTERISTICS** Capacitance Change (%) 0 -10 16V Capacitor -20 -30 -40 10V Capacitor -50 -60 -70 6.3V Capacitor -80 -9 10 11 12 13 2 8 15 16 DC Bias Voltage (VDC)

When selecting a ceramic capacitor to be used with the internal voltage regulator, it is suggested to select a high-voltage rating, so that the operating voltage is a small percentage of the maximum rated capacitor voltage. For example, choose a ceramic capacitor rated at 16V for the 3.3V or 2.5V core voltage. Suggested capacitors are shown in Table 2-1.

### 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of ohms, not to exceed 100Ω.

Pull-up resistors, series diodes, and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits, and pins, Voltage Input High (VIH) and Voltage Input Low (VIL) requirements.

For device emulation, ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins), programmed into the device, matches the physical connections for the ICSP to the Microchip debugger/emulator tool.

For more information on available Microchip development tools connection requirements, refer to **Section 26.0 "Development Support"**.

### TABLE 4-15: UART1 REGISTER MAP

| File Name | Addr.                                    | Bit 15   | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8                  | Bit 7    | Bit 6    | Bit 5     | Bit 4       | Bit 3 | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|-----------|------------------------------------------|----------|--------|----------|--------|--------|--------|-------|------------------------|----------|----------|-----------|-------------|-------|--------|--------|-------|---------------|

| U1MODE    | 220h                                     | UARTEN   | —      | USIDL    | IREN   | RTSMD  | -      | UEN1  | UEN0                   | WAKE     | LPBACK   | ABAUD     | URXINV      | BRGH  | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U1STA     | 222h                                     | UTXISEL1 | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT                   | URXISEL1 | URXISEL0 | ADDEN     | RIDLE       | PERR  | FERR   | OERR   | URXDA | 0110          |

| U1TXREG   | 224h                                     | _        | _      | _        | _      | _      | _      | _     |                        |          |          | UART1 Tra | ansmit Regi | ster  |        |        |       | xxxx          |

| U1RXREG   | 226h                                     | —        | _      | _        |        | _      | _      | —     | UART1 Receive Register |          |          |           |             |       | 0000   |        |       |               |

| U1BRG     | U1BRG 228h Baud Rate Generator Prescaler |          |        |          |        |        |        |       |                        |          |          | 0000      |             |       |        |        |       |               |

|           |                                          |          |        |          |        |        |        |       |                        |          |          |           |             |       |        |        |       |               |

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition, r = reserved.

### TABLE 4-16: UART2 REGISTER MAP

| File Name              | Addr. | Bit 15   | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8                  | Bit 7         | Bit 6    | Bit 5     | Bit 4       | Bit 3 | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|------------------------|-------|----------|--------|----------|--------|--------|--------|-------|------------------------|---------------|----------|-----------|-------------|-------|--------|--------|-------|---------------|

| U2MODE <sup>(1)</sup>  | 230h  | UARTEN   | —      | USIDL    | IREN   | RTSMD  | —      | UEN1  | UEN0                   | WAKE          | LPBACK   | ABAUD     | URXINV      | BRGH  | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U2STA <sup>(1)</sup>   | 232h  | UTXISEL1 | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT                   | URXISEL1      | URXISEL0 | ADDEN     | RIDLE       | PERR  | FERR   | OERR   | URXDA | 0110          |

| U2TXREG <sup>(1)</sup> | 234h  | _        | _      | _        | —      | _      | _      | _     |                        |               |          | UART2 Tra | nsmit Regis | ster  |        |        |       | xxxx          |

| U2RXREG <sup>(1)</sup> | 236h  | _        | _      | _        | —      | _      | _      | _     | UART2 Receive Register |               |          |           |             |       | 0000   |        |       |               |

| U2BRG <sup>(1)</sup>   | 238h  |          |        |          |        |        |        | E     | Baud Rate G            | enerator Pres | caler    |           |             |       |        |        |       | 0000          |

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition, r = reserved.

Note 1: These registers are available only on PIC24F(V)16KM2XX devices.

### 5.5.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

The user can program one row of Flash program memory at a time by erasing the programmable row. The general process is:

- 1. Read a row of program memory (32 instructions) and store in data RAM.

- 2. Update the program data in RAM with the desired new data.

- 3. Erase a row (see Example 5-1):

- a) Set the NVMOPx bits (NVMCON<5:0>) to '011000' to configure for row erase. Set the ERASE (NVMCON<6>) and WREN (NVMCON<14>) bits.

- b) Write the starting address of the block to be erased into the TBLPAG and W registers.

- c) Write 55h to NVMKEY.

- d) Write AAh to NVMKEY.

- e) Set the WR bit (NVMCON<15>). The erase cycle begins and the CPU stalls for the duration of the erase cycle. When the erase is done, the WR bit is cleared automatically.

- 4. Write the first 32 instructions from data RAM into the program memory buffers (see Example 5-1).

- 5. Write the program block to Flash memory:

- a) Set the NVMOPx bits to '000100' to configure for row programming. Clear the ERASE bit and set the WREN bit.

- b) Write 55h to NVMKEY.

- c) Write AAh to NVMKEY.

- d) Set the WR bit. The programming cycle begins and the CPU stalls for the duration of the write cycle. When the write to Flash memory is done, the WR bit is cleared automatically.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS, as displayed in Example 5-5.

| EXAMPLE 5-1: | ERASING A PROGRAM MEMORY ROW – ASSEMBLY LANGUAGE CODE |

|--------------|-------------------------------------------------------|

|              |                                                       |

| ; Set up NVMCON fo | or row erase operation               |                                     |

|--------------------|--------------------------------------|-------------------------------------|

| MOV #0x            | x4058, WO ;                          |                                     |

| MOV W0,            | , NVMCON ;                           | Initialize NVMCON                   |

| ; Init pointer to  | row to be ERASED                     |                                     |

| MOV #tk            | <pre>blpage(PROG_ADDR), W0 ;</pre>   |                                     |

| MOV W0,            | , TBLPAG ;                           | Initialize PM Page Boundary SFR     |

| MOV #tk            | <pre>bloffset(PROG_ADDR), W0 ;</pre> | Initialize in-page EA[15:0] pointer |

| TBLWTL W0,         | , [WO] ;                             | Set base address of erase block     |

| DISI #5            | ;                                    | Block all interrupts                |

|                    |                                      | for next 5 instructions             |

| MOV #0×            | x55, WO                              |                                     |

| MOV W0,            | , NVMKEY ;                           | Write the 55 key                    |

| MOV #0×            | xAA, W1 ;                            |                                     |

| MOV W1,            | , NVMKEY ;                           | Write the AA key                    |

| BSET NVM           | MCON, #WR ;                          | Start the erase sequence            |

| NOP                | ;                                    | Insert two NOPs after the erase     |

| NOP                | ;                                    | command is asserted                 |

|                    |                                      |                                     |

### EXAMPLE 5-2: ERASING A PROGRAM MEMORY ROW – 'C' LANGUAGE CODE

```

// C example using MPLAB C30

// Variable located in Pgm Memory, declared as a

int __attribute__ ((space(auto_psv))) progAddr = 0x1234;

// global variable

unsigned int offset;

//Set up pointer to the first memory location to be written

TBLPAG = __builtin_tblpage(&progAddr);

// Initialize PM Page Boundary SFR

offset = __builtin_tbloffset(&progAddr);

// Initialize lower word of address

__builtin_tblwtl(offset, 0x0000);

// Set base address of erase block

// with dummy latch write

NVMCON = 0 \times 4058;

// Initialize NVMCON

asm("DISI #5");

// Block all interrupts for next 5 instructions

_builtin_write_NVM();

\ensuremath{{//}} C30 function to perform unlock

// sequence and set WR

```

### 6.0 DATA EEPROM MEMORY

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on data EEPROM, refer to the *"PIC24F Family Reference Manual"*, **"Data EEPROM"** (DS39720).

The data EEPROM memory is a Nonvolatile Memory (NVM), separate from the program and volatile data RAM. Data EEPROM memory is based on the same Flash technology as program memory, and is optimized for both long retention and a higher number of erase/write cycles.

The data EEPROM is mapped to the top of the user program memory space, with the top address at program memory address, 7FFE00h to 7FFFFh. The size of the data EEPROM is 256 words in PIC24FXXXXX devices.

The data EEPROM is organized as 16-bit-wide memory. Each word is directly addressable, and is readable and writable during normal operation over the entire VDD range.

Unlike the Flash program memory, normal program execution is not stopped during a data EEPROM program or erase operation.

The data EEPROM programming operations are controlled using the three NVM Control registers:

- NVMCON: Nonvolatile Memory Control Register

- NVMKEY: Nonvolatile Memory Key Register

- NVMADR: Nonvolatile Memory Address Register

### 6.1 NVMCON Register

The NVMCON register (Register 6-1) is also the primary control register for data EEPROM program/erase operations. The upper byte contains the control bits used to start the program or erase cycle and the flag bit to indicate if the operation was successfully performed. The lower byte of NVMCOM configures the type of NVM operation that will be performed.

### 6.2 NVMKEY Register

The NVMKEY is a write-only register that is used to prevent accidental writes or erasures of data EEPROM locations.

To start any programming or erase sequence, the following instructions must be executed first, in the exact order provided:

- 1. Write 55h to NVMKEY.

- 2. Write AAh to NVMKEY.

After this sequence, a write will be allowed to the NVMCON register for one instruction cycle. In most cases, the user will simply need to set the WR bit in the NVMCON register to start the program or erase cycle. Interrupts should be disabled during the unlock sequence.

The MPLAB® C30 C compiler provides a defined library procedure (builtin\_write\_NVM) to perform the unlock sequence. Example 6-1 illustrates how the unlock sequence can be performed with in-line assembly.

### EXAMPLE 6-1: DATA EEPROM UNLOCK SEQUENCE

|                | rrupts For 5 instruc | ctions |

|----------------|----------------------|--------|

| asm volatile   | ("disi #5");         |        |

| //Issue Unlock | Sequence             |        |

| asm volatile   | ("mov #0x55, W0      | \n"    |

|                | "mov W0, NVMKEY      | \n"    |

|                | "mov #0xAA, W1       | \n"    |

|                | "mov W1, NVMKEY      | \n");  |

| // Perform Wri | te/Erase operations  |        |

| asm volatile   | ("bset NVMCON, #WR   | \n"    |

|                | "nop                 | \n"    |

|                | "nop                 | \n");  |

|                |                      |        |

### REGISTER 8-3: INTCON1: INTERRUPT CONTROL REGISTER 1

| R/W-0  | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| NSTDIS | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | R/W-0, HS | R/W-0, HS | R/W-0, HS | R/W-0, HS | U-0   |

|-------|-----|-----|-----------|-----------|-----------|-----------|-------|

| —     | —   | —   | MATHERR   | ADDRERR   | STKERR    | OSCFAIL   | —     |

| bit 7 |     |     |           |           |           |           | bit 0 |

| Legend:       |                              | HS = Hardware Settable bi                                                                                | t                      |                    |

|---------------|------------------------------|----------------------------------------------------------------------------------------------------------|------------------------|--------------------|

| R = Readabl   | e bit                        | W = Writable bit                                                                                         | U = Unimplemented bit, | read as '0'        |

| -n = Value at | POR                          | '1' = Bit is set                                                                                         | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15        | 1 = Interru                  | Interrupt Nesting Disable bit<br>Ipt nesting is disabled                                                 |                        |                    |

| bit 14-5      |                              | ipt nesting is enabled<br>nented: Read as '0'                                                            |                        |                    |

| bit 4         | <b>MATHERI</b><br>1 = Overfl | R: Arithmetic Error Trap Status t<br>ow trap has occurred<br>ow trap has not occurred                    | bit                    |                    |

| bit 3         | 1 = Addre                    | R: Address Error Trap Status bit<br>ss error trap has occurred<br>ss error trap has not occurred         |                        |                    |

| bit 2         | 1 = Stack                    | Stack Error Trap Status bit<br>error trap has occurred<br>error trap has not occurred                    |                        |                    |

| bit 1         | 1 = Oscilla                  | Oscillator Failure Trap Status t<br>ator failure trap has occurred<br>ator failure trap has not occurred |                        |                    |

| bit 0         | Unimplen                     | nented: Read as '0'                                                                                      |                        |                    |

| U-0          | U-0           | U-0                                                        | U-0          | U-0               | R/W-1            | R/W-0              | R/W-0   |  |  |  |  |  |

|--------------|---------------|------------------------------------------------------------|--------------|-------------------|------------------|--------------------|---------|--|--|--|--|--|

| —            | —             | —                                                          | _            | —                 | CCP5IP2          | CCP5IP1            | CCP5IP0 |  |  |  |  |  |

| bit 15       |               |                                                            |              |                   |                  | -<br>-             | bit 8   |  |  |  |  |  |

|              |               |                                                            |              |                   |                  |                    |         |  |  |  |  |  |

| U-0          | U-0           | U-0                                                        | U-0          | U-0               | R/W-1            | R/W-0              | R/W-0   |  |  |  |  |  |

| _            | —             | —                                                          |              | —                 | INT1IP2          | INT1IP1            | INT1IP0 |  |  |  |  |  |

| bit 7        |               |                                                            |              |                   |                  |                    | bit 0   |  |  |  |  |  |

| Legend:      |               |                                                            |              |                   |                  |                    |         |  |  |  |  |  |

| R = Readat   | ole hit       | W = Writable b                                             | hit          | II = Unimpler     | nented bit, read | 1 as '0'           |         |  |  |  |  |  |

| -n = Value a |               | '1' = Bit is set                                           |              | '0' = Bit is cle  |                  | x = Bit is unknown |         |  |  |  |  |  |

|              |               |                                                            |              |                   |                  |                    |         |  |  |  |  |  |

| bit 15-11    | Unimplemer    | nted: Read as '0                                           | '            |                   |                  |                    |         |  |  |  |  |  |

| bit 10-8     | CCP5IP<2:0    | >: Capture/Com                                             | pare 5 Event | Interrupt Priorit | y bits           |                    |         |  |  |  |  |  |

|              | 111 = Interru | 111 = Interrupt is Priority 7 (highest priority interrupt) |              |                   |                  |                    |         |  |  |  |  |  |

|              | •             | •                                                          |              |                   |                  |                    |         |  |  |  |  |  |

|              | •             | •                                                          |              |                   |                  |                    |         |  |  |  |  |  |

|              |               | pt is Priority 1                                           |              |                   |                  |                    |         |  |  |  |  |  |

|              |               | pt source is disa                                          |              |                   |                  |                    |         |  |  |  |  |  |

| bit 7-3      | Unimplemer    | nted: Read as '0                                           | '            |                   |                  |                    |         |  |  |  |  |  |

| bit 2-0      |               | : External Interru                                         |              |                   |                  |                    |         |  |  |  |  |  |

|              | 111 = Interru | 111 = Interrupt is Priority 7 (highest priority interrupt) |              |                   |                  |                    |         |  |  |  |  |  |

|              | •             |                                                            |              |                   |                  |                    |         |  |  |  |  |  |

|              | •             |                                                            |              |                   |                  |                    |         |  |  |  |  |  |

|              |               | pt is Priority 1                                           | - la la al   |                   |                  |                    |         |  |  |  |  |  |

|              | 000 = interru | pt source is disa                                          | adied        |                   |                  |                    |         |  |  |  |  |  |

### REGISTER 8-24: IPC5: INTERRUPT PRIORITY CONTROL REGISTER 5

### REGISTER 8-27: IPC10: INTERRUPT PRIORITY CONTROL REGISTER 10

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   |     | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

|        |     |     |     |     |     |     |       |

| U-0   | R/W-1   | R/W-0   | R/W-0   | U-0 | U-0 | U-0 | U-0   |

|-------|---------|---------|---------|-----|-----|-----|-------|

| —     | CCT5IP2 | CCT5IP1 | CCT5IP0 |     | _   |     | —     |

| bit 7 |         |         |         |     |     |     | bit 0 |

| Legend:                               |                                |                                 |                              |                    |  |  |  |  |

|---------------------------------------|--------------------------------|---------------------------------|------------------------------|--------------------|--|--|--|--|

| R = Readable bit<br>-n = Value at POR |                                | W = Writable bit                | U = Unimplemented bit        | , read as '0'      |  |  |  |  |

|                                       |                                | '1' = Bit is set                | '0' = Bit is cleared         | x = Bit is unknown |  |  |  |  |

|                                       |                                |                                 |                              |                    |  |  |  |  |

| bit 15-7                              | 5-7 Unimplemented: Read as '0' |                                 |                              |                    |  |  |  |  |

| bit 6-4                               | CCT5IP<                        | 2:0>: Capture/Compare 5 Ti      | imer Interrupt Priority bits |                    |  |  |  |  |

|                                       | 111 = Inte                     | errupt is Priority 7 (highest p | riority interrupt)           |                    |  |  |  |  |

|                                       | •                              |                                 |                              |                    |  |  |  |  |

| •                                     |                                |                                 |                              |                    |  |  |  |  |

|                                       |                                |                                 |                              |                    |  |  |  |  |

|                                       | 001 = Inte                     | errupt is Priority 1            |                              |                    |  |  |  |  |

- 000 = Interrupt source is disabled

- bit 3-0 Unimplemented: Read as '0'

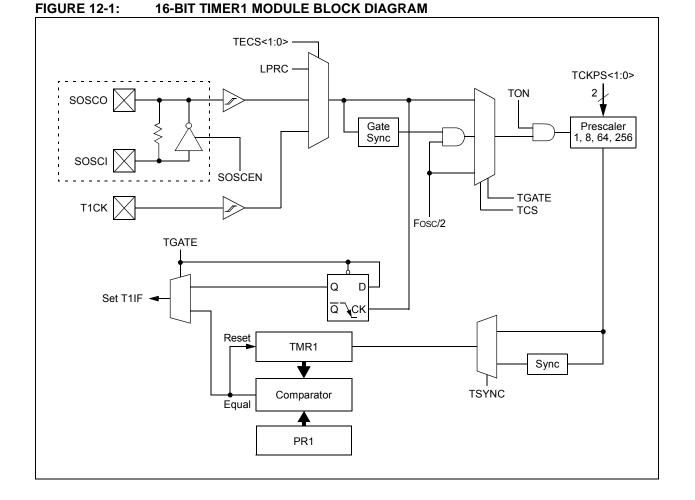

### 12.0 TIMER1

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on timers, refer to the "PIC24F Family Reference Manual", "Timers" (DS39704).

The Timer1 module is a 16-bit timer which can serve as the time counter for the Real-Time Clock (RTC) or operate as a free-running, interval timer/counter. Timer1 can operate in three modes:

- 16-Bit Timer

- 16-Bit Synchronous Counter

- 16-Bit Asynchronous Counter

Timer1 also supports these features:

- Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation During CPU Idle and Sleep modes

- Interrupt on 16-Bit Period Register Match or Falling Edge of External Gate Signal

Figure 12-1 illustrates a block diagram of the 16-bit Timer1 module.

To configure Timer1 for operation:

- 1. Set the TON bit (= 1).

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits.

- 4. Set or clear the TSYNC bit to configure synchronous or asynchronous operation.

- 5. Load the timer period value into the PR1 register.

- 6. If interrupts are required, set the Timer1 Interrupt Enable bit, T1IE. Use the Timer1 Interrupt Priority bits, T1IP<2:0>, to set the interrupt priority.

### REGISTER 13-7: CCPxSTATL: CCPx STATUS REGISTER

| U-0           | U-0                                                                                                           | U-0                                    | U-0            | U-0               | U-0              | U-0             | U-0           |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------|----------------|-------------------|------------------|-----------------|---------------|--|--|--|

|               | —                                                                                                             | —                                      | _              | —                 | _                | —               |               |  |  |  |

| bit 15        | ·                                                                                                             |                                        |                |                   |                  |                 | bit 8         |  |  |  |

|               |                                                                                                               |                                        | 5/2.2          | 5/2.2             | 5/2.2            | 5/2.2           | 5/2.2         |  |  |  |

| R-0           | W1-0                                                                                                          | W1-0                                   | R/C-0          | R/C-0             | R/C-0            | R/C-0           | R/C-0         |  |  |  |

| CCPTRIG       | IRSEI                                                                                                         | TRSET TRCLR ASEVT SCEVT ICDIS ICOV ICE |                |                   |                  |                 |               |  |  |  |

| bit 7         |                                                                                                               |                                        |                |                   |                  |                 | bit 0         |  |  |  |

| Legend:       |                                                                                                               | C = Clearable                          | bit            |                   |                  |                 |               |  |  |  |

| R = Readable  | e bit                                                                                                         | W1 = Write '1'                         | only           | U = Unimplem      | ented bit, read  | l as '0'        |               |  |  |  |

| -n = Value at | POR                                                                                                           | '1' = Bit is set                       |                | '0' = Bit is clea | ared             | x = Bit is unkr | nown          |  |  |  |

|               |                                                                                                               |                                        |                |                   |                  |                 |               |  |  |  |

| bit 15-8      | Unimplemen                                                                                                    | ted: Read as '0                        | )              |                   |                  |                 |               |  |  |  |

| bit 7         |                                                                                                               | CPx Trigger Sta                        |                |                   |                  |                 |               |  |  |  |

|               |                                                                                                               | s been triggered<br>s not been trigg   |                |                   |                  |                 |               |  |  |  |

| bit 6         |                                                                                                               | x Trigger Set Re                       |                |                   |                  |                 |               |  |  |  |

| bit o         |                                                                                                               | is location to trig                    | •              | when TRIGEN       | = 1 (location al | ways reads as   | ; 'O').       |  |  |  |

| bit 5         |                                                                                                               | x Trigger Clear                        |                |                   | ,                |                 |               |  |  |  |

|               | Write '1' to th                                                                                               | is location to ca                      | ncel the timer | Trigger when T    | RIGEN = 1 (lo    | cation always r | eads as '0'). |  |  |  |

| bit 4         | ASEVT: CCP                                                                                                    | x Auto-Shutdow                         | n Event Statu  | s/Control bit     |                  |                 |               |  |  |  |

|               |                                                                                                               | wn event is in p                       |                | x outputs are in  | the shutdown     | state           |               |  |  |  |

| L:1 0         |                                                                                                               | Itputs operate n                       | •              | - h:t             |                  |                 |               |  |  |  |

| bit 3         | •                                                                                                             | le Edge Compa<br>edge compare e        |                |                   |                  |                 |               |  |  |  |

|               |                                                                                                               | edge compare e                         |                |                   |                  |                 |               |  |  |  |

| bit 2         | ICDIS: Input                                                                                                  | Capture x Disab                        | ole bit        |                   |                  |                 |               |  |  |  |

|               |                                                                                                               | Input Capture                          |                |                   |                  | nt              |               |  |  |  |

|               |                                                                                                               | Input Capture >                        |                | -                 | event            |                 |               |  |  |  |

| bit 1         | <b>ICOV:</b> Input Capture x Buffer Overflow Status bit<br>1 = The Input Capture x FIFO buffer has overflowed |                                        |                |                   |                  |                 |               |  |  |  |

|               |                                                                                                               | t Capture x FIF                        |                |                   |                  |                 |               |  |  |  |

| bit 0         | -                                                                                                             | Capture x Buffe                        |                |                   |                  |                 |               |  |  |  |

|               | •                                                                                                             | apture x buffer h                      |                | able              |                  |                 |               |  |  |  |

|               | 0 = Input Ca                                                                                                  | apture x buffer i                      | s empty        |                   |                  |                 |               |  |  |  |

|               |                                                                                                               |                                        |                |                   |                  |                 |               |  |  |  |

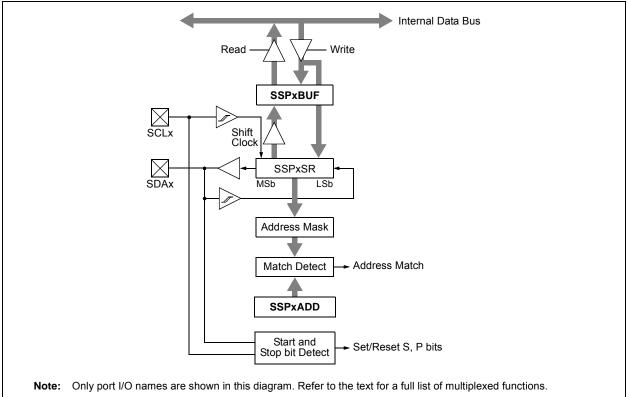

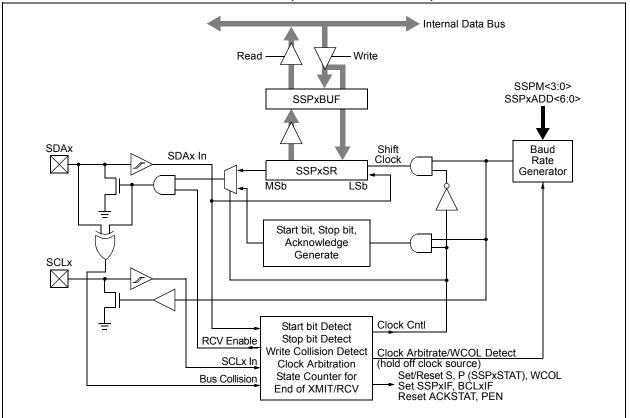

### 14.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on MSSP, refer to the "PIC24F Family Reference Manual".

The Master Synchronous Serial Port (MSSP) module is an 8-bit serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, Shift registers, display drivers, A/D Converters, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>)

- Full Master mode

- Slave mode (with general address call)

The SPI interface supports these modes in hardware:

- Master mode

- Slave mode

- · Daisy-Chaining Operation in Slave mode

- Synchronized Slave Operation

The  $I^2C$  interface supports the following modes in hardware:

- Master mode

- · Multi-Master mode

- Slave mode with 10-Bit and 7-Bit Addressing and Address Masking

- Byte NACKing

- Selectable Address and Data Hold, and Interrupt Masking

### 14.1 I/O Pin Configuration for SPI

In SPI Master mode, the MSSP module will assert control over any pins associated with the SDOx and SCKx outputs. This does not automatically disable other digital functions associated with the pin and may result in the module driving the digital I/O port inputs. To prevent this, the MSSP module outputs must be disconnected from their output pins while the module is in SPI Master mode. While disabling the module temporarily may be an option, it may not be a practical solution in all applications.

The SDOx and SCKx outputs for the module can be selectively disabled by using the SDOxDIS and SCKxDIS bits in the PADCFG1 register (Register 14-10). Setting the bit disconnects the corresponding output for a particular module from its assigned pin.

### FIGURE 14-4: MSSPx BLOCK DIAGRAM (I<sup>2</sup>C<sup>™</sup> MASTER MODE)

### 15.2 Transmitting in 8-Bit Data Mode

- 1. Set up the UARTx:

- a) Write the appropriate values for data, parity and Stop bits.

- b) Write the appropriate baud rate value to the UxBRG register.

- c) Set up transmit and receive interrupt enable and priority bits.

- 2. Enable the UARTx.

- 3. Set the UTXEN bit (causes a transmit interrupt, two cycles after being set).

- 4. Write the data byte to the lower byte of the UxTXREG word. The value will be immediately transferred to the Transmit Shift Register (TSR) and the serial bit stream will start shifting out with the next rising edge of the baud clock.

- Alternately, the data byte may be transferred while UTXEN = 0, and then, the user may set UTXEN. This will cause the serial bit stream to begin immediately, because the baud clock will start from a cleared state.

- 6. A transmit interrupt will be generated as per interrupt control bit, UTXISELx.

### 15.3 Transmitting in 9-Bit Data Mode

- 1. Set up the UARTx (as described in **Section 15.2** "**Transmitting in 8-Bit Data Mode**").

- 2. Enable the UARTx.

- 3. Set the UTXEN bit (causes a transmit interrupt, two cycles after being set).

- 4. Write UxTXREG as a 16-bit value only.

- 5. A word write to UxTXREG triggers the transfer of the 9-bit data to the TSR. The serial bit stream will start shifting out with the first rising edge of the baud clock.

- 6. A transmit interrupt will be generated as per the setting of control bit, UTXISELx.

### 15.4 Break and Sync Transmit Sequence

The following sequence will send a message frame header, made up of a Break, followed by an Auto-Baud Sync byte.

- 1. Configure the UARTx for the desired mode.

- 2. Set UTXEN and UTXBRK this sets up the Break character.

- 3. Load the UxTXREG with a dummy character to initiate transmission (value is ignored).

- 4. Write '55h' to UxTXREG loads the Sync character into the transmit FIFO.

- 5. After the Break has been sent, the UTXBRK bit is reset by hardware. The Sync character now transmits.

### 15.5 Receiving in 8-Bit or 9-Bit Data Mode

- 1. Set up the UARTx (as described in Section 15.2 "Transmitting in 8-Bit Data Mode").

- 2. Enable the UARTx.

- 3. A receive interrupt will be generated when one or more data characters have been received, as per interrupt control bit, URXISELx.

- 4. Read the OERR bit to determine if an overrun error has occurred. The OERR bit must be reset in software.

- 5. Read UxRXREG.

The act of reading the UxRXREG character will move the next character to the top of the receive FIFO, including a new set of PERR and FERR values.

### 15.6 Operation of UxCTS and UxRTS Control Pins

UARTx Clear-To-Send (UxCTS) and Request-To-Send (UxRTS) are the two hardware controlled pins that are associated with the UARTx module. These two pins allow the UARTx to operate in Simplex and Flow Control modes. They are implemented to control the transmission and reception between the Data Terminal Equipment (DTE). The UEN<1:0> bits in the UxMODE register configure these pins.

### 15.7 Infrared Support

The UARTx module provides two types of infrared UARTx support: one is the IrDA clock output to support an external IrDA encoder and decoder device (legacy module support), and the other is the full implementation of the IrDA encoder and decoder.

As the IrDA modes require a 16x baud clock, they will only work when the BRGH bit (UxMODE<3>) is '0'.

### 15.7.1 EXTERNAL IrDA SUPPORT – IrDA CLOCK OUTPUT

To support external IrDA encoder and decoder devices, the UxBCLK pin (same as the UxRTS pin) can be configured to generate the 16x baud clock. When UEN<1:0> = 11, the UxBCLK pin will output the 16x baud clock if the UARTx module is enabled; it can be used to support the IrDA codec chip.

### 15.7.2 BUILT-IN IrDA ENCODER AND DECODER

The UARTx has full implementation of the IrDA encoder and decoder as part of the UARTx module. The built-in IrDA encoder and decoder functionality is enabled using the IREN bit (UxMODE<12>). When enabled (IREN = 1), the receive pin (UxRX) acts as the input from the infrared receiver. The transmit pin (UxTX) acts as the output to the infrared transmitter.

| REGISTER 16-2: | RTCPWC: RTCC CONFIGURATION REGISTER 2 <sup>(1)</sup> |

|----------------|------------------------------------------------------|

|                |                                                      |

| R/W-0      | R/W-0                                          | R/W-0                                                                      | R/W-0                        | R/W-0                                                          | R/W-0                  | R/W-0           | R/W-0   |  |  |  |  |

|------------|------------------------------------------------|----------------------------------------------------------------------------|------------------------------|----------------------------------------------------------------|------------------------|-----------------|---------|--|--|--|--|

| PWCEN      | PWCPOL                                         | PWCCPRE                                                                    | PWCSPRE                      | RTCCLK1 <sup>(2)</sup>                                         | RTCCLK0 <sup>(2)</sup> | RTCOUT1         | RTCOUT0 |  |  |  |  |

| bit 15     |                                                |                                                                            |                              |                                                                |                        |                 | bit 8   |  |  |  |  |

|            |                                                |                                                                            |                              |                                                                |                        |                 |         |  |  |  |  |

| U-0        | U-0                                            | U-0                                                                        | U-0                          | U-0                                                            | U-0                    | U-0             | U-0     |  |  |  |  |

| _          | —                                              | —                                                                          |                              | —                                                              | —                      | —               | —       |  |  |  |  |

| bit 7      |                                                |                                                                            |                              |                                                                |                        |                 | bit C   |  |  |  |  |

| Legend:    |                                                |                                                                            |                              |                                                                |                        |                 |         |  |  |  |  |

| R = Reada  | hle hit                                        | W = Writable                                                               | hit                          | II = I Inimpleme                                               | nted bit, read as      | ʻ <b>∩</b> '    |         |  |  |  |  |

| -n = Value |                                                | '1' = Bit is set                                                           |                              | '0' = Bit is cleare                                            |                        | x = Bit is unkr | own     |  |  |  |  |

|            |                                                |                                                                            |                              |                                                                | 50                     |                 |         |  |  |  |  |

| bit 15     | PWCEN: Po                                      | wer Control Er                                                             | able bit                     |                                                                |                        |                 |         |  |  |  |  |

|            |                                                | ontrol is enable                                                           |                              |                                                                |                        |                 |         |  |  |  |  |

|            | 0 = Power co                                   | ontrol is disable                                                          | ed                           |                                                                |                        |                 |         |  |  |  |  |

| bit 14     | PWCPOL: P                                      | ower Control F                                                             | Polarity bit                 |                                                                |                        |                 |         |  |  |  |  |

|            |                                                | ontrol output is                                                           |                              |                                                                |                        |                 |         |  |  |  |  |

|            |                                                | ontrol output is                                                           |                              |                                                                |                        |                 |         |  |  |  |  |

| bit 13     |                                                | Power Control                                                              | 2                            |                                                                |                        |                 |         |  |  |  |  |

|            |                                                |                                                                            |                              | by-2 of source R <sup>-</sup><br>by-1 of source R <sup>-</sup> |                        |                 |         |  |  |  |  |

| bit 12     |                                                | Power Control                                                              |                              | 2                                                              |                        |                 |         |  |  |  |  |

|            |                                                |                                                                            | •                            | by-2 of source R                                               | CC clock               |                 |         |  |  |  |  |

|            |                                                |                                                                            |                              | by-1 of source R                                               |                        |                 |         |  |  |  |  |

| bit 11-10  | RTCCLK<1:                                      | 0>: RTCC Clo                                                               | ck Select bits <sup>(2</sup> | 2)                                                             |                        |                 |         |  |  |  |  |

|            |                                                |                                                                            |                              | CC clock, which i                                              | s used for all RT      | CC timer opera  | itions. |  |  |  |  |

|            |                                                | 00 = External Secondary Oscillator (SOSC)<br>01 = Internal LPRC Oscillator |                              |                                                                |                        |                 |         |  |  |  |  |

|            | 10 = External power line source – 50 Hz        |                                                                            |                              |                                                                |                        |                 |         |  |  |  |  |

|            |                                                | al power line so                                                           |                              |                                                                |                        |                 |         |  |  |  |  |

| bit 9-8    | RTCOUT<1:                                      | 0>: RTCC Out                                                               | put Select bits              | 5                                                              |                        |                 |         |  |  |  |  |

|            |                                                | Determines the source of the RTCC pin output.                              |                              |                                                                |                        |                 |         |  |  |  |  |

|            |                                                | 00 = RTCC alarm pulse<br>01 = RTCC seconds clock                           |                              |                                                                |                        |                 |         |  |  |  |  |

|            | 10 = RTCC (                                    |                                                                            |                              |                                                                |                        |                 |         |  |  |  |  |

|            | 11 = Power (                                   | control                                                                    |                              |                                                                |                        |                 |         |  |  |  |  |

| bit 7-0    | Unimpleme                                      | nted: Read as                                                              | <b>'</b> 0 <b>'</b>          |                                                                |                        |                 |         |  |  |  |  |

| Note 1:    | The RTCPWC                                     | register is only                                                           | affected by a                | POR                                                            |                        |                 |         |  |  |  |  |

|            | The RTCPWC register is only affected by a POR. |                                                                            |                              |                                                                |                        |                 |         |  |  |  |  |

2: When a new value is written to these register bits, the Seconds Value register should also be written to properly reset the clock prescalers in the RTCC.

| R/W-0               | R/W-0                                                                                                                  | R/W-0                                                                                                                                                             | R/W-0           | r-0                | U-0                | R/W-0             | R/W-0           |  |  |  |  |

|---------------------|------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------|--------------------|-------------------|-----------------|--|--|--|--|

| ASEN <sup>(1)</sup> | LPEN                                                                                                                   | CTMREQ                                                                                                                                                            | BGREQ           | r                  | —                  | ASINT1            | ASINT0          |  |  |  |  |

| bit 15              |                                                                                                                        |                                                                                                                                                                   |                 |                    |                    |                   | bit 8           |  |  |  |  |

| U-0                 | U-0                                                                                                                    | U-0                                                                                                                                                               | U-0             | R/W-0              | R/W-0              | R/W-0             | R/W-0           |  |  |  |  |

|                     | _                                                                                                                      | _                                                                                                                                                                 | _               | WM1                | WM0                | CM1               | CM0             |  |  |  |  |

| bit 7               |                                                                                                                        |                                                                                                                                                                   |                 |                    |                    |                   | bit 0           |  |  |  |  |

| Legend:             |                                                                                                                        | r = Reserved b                                                                                                                                                    | bit             |                    |                    |                   |                 |  |  |  |  |

| R = Reada           | able bit                                                                                                               | W = Writable b                                                                                                                                                    | oit             | U = Unimplem       | nented bit, read   | as '0'            |                 |  |  |  |  |

| -n = Value          | at POR                                                                                                                 | '1' = Bit is set                                                                                                                                                  |                 | '0' = Bit is clea  | ared               | x = Bit is unkn   | iown            |  |  |  |  |

| bit 15              | ASEN. A/D A                                                                                                            | Auto-Scan Enable                                                                                                                                                  | <u> hit(1)</u>  |                    |                    |                   |                 |  |  |  |  |

|                     | 1 = Auto-sca                                                                                                           |                                                                                                                                                                   |                 |                    |                    |                   |                 |  |  |  |  |

|                     | 0 = Auto-sca                                                                                                           | in is disabled                                                                                                                                                    |                 |                    |                    |                   |                 |  |  |  |  |