#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                     |

| Number of I/O              | 23                                                                             |

| Program Memory Size        | 16KB (5.5K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | 512 x 8                                                                        |

| RAM Size                   | 1K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5V                                                                        |

| Data Converters            | A/D 19x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                 |

| Supplier Device Package    | 28-SOIC                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fv16km102t-i-so |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Pin Diagrams (Continued)**

|          | 28-Pin QFN <sup>(1)</sup>                                                            | 22<br>21 RB13<br>20 RB12                         |

|----------|--------------------------------------------------------------------------------------|--------------------------------------------------|

|          | RB3 4<br>Vss 5<br>RA2 6<br>RA3 7<br><u>8 9 10 11 12 <b>13</b> 1</u>                  | 18 RB10<br>17 RA6 or VDDcore<br>16 RA7<br>15 RB9 |

|          | R 85<br>R 85<br>R 85<br>R 82<br>R 82<br>R 82<br>R 82<br>R 82<br>R 82<br>R 82<br>R 82 | 5<br>0<br>2<br>2                                 |

| Pin      | Pin Features                                                                         | Pin Features                                     |

|          | PIC24FXXKMX02                                                                        | PIC24FVXXKMX02                                   |

| 1        | PGED1/AN2/CTCMP/ULPWU/C1IND/ / / /CN4/I                                              | RB0                                              |

| 2        | PGEC1/ / /AN3/C1INC/ / /CTED12/CN                                                    | I5/RB1                                           |

| 3        | / /AN4/C1INB/ / /U1RX/TCKIB/CTED1                                                    | 13/CN6/RB2                                       |

| 4        | /AN5/C1INA/ / /CN7/RB3                                                               |                                                  |

| 5        | Vss                                                                                  |                                                  |

| 6        | OSCI/CLKI/AN13/CN30/RA2                                                              |                                                  |

| 7        | OSCO/CLKO/AN14/CN29/RA3                                                              |                                                  |

| 8        | SOSCI/AN15/ / /CN1/RB4                                                               |                                                  |

| 9        | SOSCO/SCLKI/AN16/PWRLCLK/ /CN0/RA4                                                   |                                                  |

| 10       |                                                                                      |                                                  |

| 11       | PGED3/AN17/ASDA1/ / /OC1E/CLCINA/CN27/RB5                                            |                                                  |

| 12       | PGEC3/AN18/ASCL1/ / /OC1F/CLCINB/CN24/RB6<br>AN19/U1TX/INT0/CN23/RB7                 | AN19/U1TX/ /OC1A/INT0/CN23/RB7                   |

| 13<br>14 | AN19/0112/IN10/CN23/RB7<br>AN20/SCL1/U1CTS/C3OUT/OC1B/CTED10/CN22/RB8                | AN 19/011X/ /OCTA/IN10/CN23/RB7                  |

| 14       | AN21/SDA1/T1CK/U1RTS/U1BCLK/IC2/ /CLC10/CTED4/CN                                     | 121/PB0                                          |

| 16       | /IC1/ / /CTED3/CN9/RA7                                                               | vz //KD9                                         |

| 17       | /OC1A/CTED1/INT2/CN8/RA6                                                             | VDDCORE/VCAP                                     |

| 18       | PGED2/SDI1/ /OC1C/CTED11/CN16/RB10                                                   |                                                  |

| 19       | PGEC2/SCK1/OC2A/CTED9/CN15/RB11                                                      | <u></u>                                          |

| 20       | /AN12/HLVDIN/ / / /CTED2/CN14/RB12                                                   | /AN12/HLVDIN/SS2/ / /CTED2/INT2/CN14/RB12        |

| 21       | / /AN11/SDO1/OCFB/OC3B/OC1D/CTPLS/CN13                                               | 3/RB13                                           |

| 22       | /CVREF/ / /AN10/ / /C1OUT                                                            | OCFA/CTED5/INT1/CN12/RB14                        |

| 23       | / /AN9/ /REFO/SS1/TCKIA/CTED6/CN                                                     | I11/RB15                                         |

| 24       | Vss                                                                                  |                                                  |

| 25       | Vdd                                                                                  |                                                  |

| 26       | MCLR/Vpp/RA5                                                                         |                                                  |

|          | CVREF+/VREF+/ /AN0/ /CN2/RA0                                                         | CVREF+/VREF+/ /AN0/ /CTED1/CN2/RA0               |

| 27       |                                                                                      |                                                  |

Legend:Values inindicate pin function differences between PIC24F(V)XXKM202 and PIC24F(V)XXKM102 devices.Note 1:Exposed pad on underside of device is connected to Vss.

#### REGISTER 8-2: CORCON: CPU CONTROL REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

|        | —   | —   | —   | —   |     |     | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | R/C-0, HSC          | R/W-0              | U-0 | U-0   |

|-------|-----|-----|-----|---------------------|--------------------|-----|-------|

| —     | —   | —   | —   | IPL3 <sup>(2)</sup> | PSV <sup>(1)</sup> | —   | —     |

| bit 7 |     |     |     |                     |                    |     | bit 0 |

| Legend:           | C = Clearable bit | HSC = Hardware Settal  | ble/Clearable bit  |

|-------------------|-------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-4 Unimplemented: Read as '0'

bit 3 IPL3: CPU Interrupt Priority Level Status bit<sup>(2)</sup> 1 = CPU Interrupt Priority Level is greater than 7 0 = CPU Interrupt Priority Level is 7 or less

bit 1-0 Unimplemented: Read as '0'

**Note 1:** See Register 3-2 for the description of this bit, which is not dedicated to interrupt control functions.

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

Note: Bit 2 is described in Section 3.0 "CPU".

#### REGISTER 8-7: IFS2: INTERRUPT FLAG STATUS REGISTER 2

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0, HS | U-0   |

|--------|-----|-----|-----|-----|-----|-----------|-------|

| —      | —   | —   | —   | —   | —   | CCT5IF    | —     |

| bit 15 |     |     |     |     |     |           | bit 8 |

|        |     |     |     |     |     |           |       |

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0       | U-0   |

|        |     | _   | _   |     | _   |           | _     |

| bit 7  |     |     |     |     |     |           | bit 0 |

| Legend:           | HS = Hardware Settable bit |                             |                    |

|-------------------|----------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-10 | Unimplemented: Read as '0'                                |

|-----------|-----------------------------------------------------------|

| bit 9     | CCT5IF: Capture/Compare 5 Timer Interrupt Flag Status bit |

|           | 1 = Interrupt request has occurred                        |

|           | 0 = Interrupt request has not occurred                    |

|           |                                                           |

bit 8-0 Unimplemented: Read as '0'

#### REGISTER 8-8: IFS3: INTERRUPT FLAG STATUS REGISTER 3

| U-0    | R/W-0, HS | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----------|-----|-----|-----|-----|-----|-------|

| —      | RTCIF     | —   | —   | —   | —   | —   | —     |

| bit 15 |           |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0, HS | R/W-0, HS | U-0   |

|-------|-----|-----|-----|-----|-----------|-----------|-------|

| —     | —   | —   | —   | —   | BCL2IF    | SSP2IF    | —     |

| bit 7 |     |     |     |     |           |           | bit 0 |

| Legend:           | HS = Hardware Settable bit |                             |                    |

|-------------------|----------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15   | Unimplemented: Read as '0'                                                          |

|----------|-------------------------------------------------------------------------------------|

| bit 14   | RTCIF: Real-Time Clock and Calendar Interrupt Flag Status bit                       |

|          | 1 = Interrupt request has occurred                                                  |

|          | 0 = Interrupt request has not occurred                                              |

| bit 13-3 | Unimplemented: Read as '0'                                                          |

| bit 2    | BCL2IF: MSSP2 I <sup>2</sup> C <sup>™</sup> Bus Collision Interrupt Flag Status bit |

|          | 1 = Interrupt request has occurred                                                  |

|          | 0 = Interrupt request has not occurred                                              |

| bit 1    | SSP2IF: MSSP2 SPI/I <sup>2</sup> C Event Interrupt Flag Status bit                  |

|          | 1 = Interrupt request has occurred                                                  |

|          | 0 = Interrupt request has not occurred                                              |

| bit 0    | Unimplemented: Read as '0'                                                          |

|          |                                                                                     |

| U-0                          | U-0                                      | U-0                                                                                                                                     | U-0                             | U-0                                                        | R/W-1   | R/W-0           | R/W-0   |

|------------------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|------------------------------------------------------------|---------|-----------------|---------|

| _                            |                                          |                                                                                                                                         |                                 |                                                            | U2ERIP2 | U2ERIP1         | U2ERIP0 |

| oit 15                       |                                          |                                                                                                                                         | •                               |                                                            |         | •               | bit 8   |

|                              |                                          |                                                                                                                                         |                                 |                                                            |         |                 |         |

| U-0                          | R/W-1                                    | R/W-0                                                                                                                                   | R/W-0                           | U-0                                                        | U-0     | U-0             | U-0     |

| —                            | U1ERIP2                                  | U1ERIP1                                                                                                                                 | U1ERIP0                         | —                                                          | —       | —               | —       |

| bit 7                        |                                          |                                                                                                                                         |                                 |                                                            |         |                 | bit 0   |

|                              |                                          |                                                                                                                                         |                                 |                                                            |         |                 |         |

| Legend:                      |                                          |                                                                                                                                         |                                 |                                                            |         |                 |         |

| R = Readab                   | ole bit                                  | W = Writable                                                                                                                            | bit                             | U = Unimplemented bit, read as '0'<br>(0) = Rit is cleared |         |                 |         |

| -n = Value a                 | at POR                                   | '1' = Bit is set                                                                                                                        |                                 | '0' = Bit is cle                                           | ared    | x = Bit is unkr | nown    |

| bit 10-8<br>bit 7<br>bit 6-4 | <pre>111 = Interru </pre>                | >: UART2 Error<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>nted: Read as '<br>>: UART1 Error<br>pt is Priority 7 ( | highest priority<br>abled<br>o' | interrupt)                                                 |         |                 |         |

| bit 3-0                      | •<br>•<br>001 = Interru<br>000 = Interru | pt is Priority 1<br>pt is Priority 1<br>pt source is dis<br>nted: Read as '                                                             | abled                           | interrupt)                                                 |         |                 |         |

#### REGISTER 8-30: IPC16: INTERRUPT PRIORITY CONTROL REGISTER 16

NOTES:

### 9.1 CPU Clocking Scheme

The system clock source can be provided by one of four sources:

- Primary Oscillator (POSC) on the OSCI and OSCO pins

- Secondary Oscillator (SOSC) on the SOSCI and SOSCO pins

The PIC24FXXXXX family devices consist of two types of secondary oscillator:

- High-Power Secondary Oscillator

- Low-Power Secondary Oscillator

These can be selected by using the SOSCSEL (FOSC<5>) bit.

- Fast Internal RC (FRC) Oscillator:

- 8 MHz FRC Oscillator

- 500 kHz Lower Power FRC Oscillator

- Low-Power Internal RC (LPRC) Oscillator with two modes:

- High-Power/High-Accuracy mode

- Low-Power/Low-Accuracy mode

The Primary Oscillator and 8 MHz FRC sources have the option of using the internal 4x PLL. The frequency of the FRC clock source can optionally be reduced by the programmable clock divider. The selected clock source generates the processor and peripheral clock sources.

The processor clock source is divided by two to produce the internal instruction cycle clock, Fcy. In this document, the instruction cycle clock is also denoted by Fosc/2. The internal instruction cycle clock, Fosc/2, can be provided on the OSCO I/O pin for some operating modes of the Primary Oscillator.

### 9.2 Initial Configuration on POR

The oscillator source (and operating mode) that is used at a device Power-on Reset (POR) event is selected using Configuration bit settings. The Oscillator Configuration bit settings are located in the Configuration registers in the program memory (for more information, see Section 25.1 "Configuration Bits"). The Primary Oscillator Configuration bits, POSCMD<1:0> (FOSC<1:0>), and the Initial Oscillator Select Configuration bits, FNOSC<2:0> (FOSCSEL<2:0>), select the oscillator source that is used at a POR. The FRC Primary Oscillator with Postscaler (FRCDIV) is the default (unprogrammed) selection. The Secondary Oscillator, or one of the internal oscillators, may be chosen by programming these bit locations. The EC mode Frequency Range Configuration bits, POSCFREQ<1:0> (FOSC<4:3>), optimize power consumption when running in EC mode. The default configuration is "frequency range is greater than 8 MHz".

The Configuration bits allow users to choose between the various clock modes, shown in Table 9-1.

## 9.2.1 CLOCK SWITCHING MODE CONFIGURATION BITS

The FCKSM<1:0> Configuration bits (FOSC<7:6>) are used jointly to configure device clock switching and the FSCM. Clock switching is enabled only when FCKSM1 is programmed ('0'). The FSCM is enabled only when FCKSM<1:0> are both programmed ('00').

| Oscillator Mode                                      | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | Notes |

|------------------------------------------------------|-------------------|-------------|------------|-------|

| 8 MHz FRC Oscillator with Postscaler (FRCDIV)        | Internal          | 11          | 111        | 1, 2  |

| 500 kHz FRC Oscillator with Postscaler<br>(LPFRCDIV) | Internal          | 11          | 110        | 1     |

| Low-Power RC Oscillator (LPRC)                       | Internal          | 11          | 101        | 1     |

| Secondary (Timer1) Oscillator (SOSC)                 | Secondary         | 00          | 100        | 1     |

| Primary Oscillator (HS) with PLL Module (HSPLL)      | Primary           | 10          | 011        |       |

| Primary Oscillator (EC) with PLL Module (ECPLL)      | Primary           | 00          | 011        |       |

| Primary Oscillator (HS)                              | Primary           | 10          | 010        |       |

| Primary Oscillator (XT)                              | Primary           | 01          | 010        |       |

| Primary Oscillator (EC)                              | Primary           | 00          | 010        |       |

| 8 MHz FRC Oscillator with PLL Module (FRCPLL)        | Internal          | 11          | 001        | 1     |

| 8 MHz FRC Oscillator (FRC)                           | Internal          | 11          | 000        | 1     |

#### TABLE 9-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

Note 1: The OSCO pin function is determined by the OSCIOFNC Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

#### REGISTER 15-3: UXTXREG: UARTX TRANSMIT REGISTER

| U-x    | U-x | U-x | U-x | U-x | U-x | U-x | W-x   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | _   | —   | UTX8  |

| bit 15 |     |     |     |     |     |     | bit 8 |

| W-x   | W-x  | W-x  | W-x  | W-x  | W-x  | W-x  | W-x   |

|-------|------|------|------|------|------|------|-------|

| UTX7  | UTX6 | UTX5 | UTX4 | UTX3 | UTX2 | UTX1 | UTX0  |

| bit 7 |      |      |      |      |      |      | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-9 Unimplemented: Read as '0'

bit 8 **UTX8:** Data of the Transmitted Character bit (in 9-bit mode)

bit 7-0 UTX<7:0>: Data of the Transmitted Character bits

### REGISTER 15-4: UxRXREG: UARTx RECEIVE REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R-0, HSC |

|--------|-----|-----|-----|-----|-----|-----|----------|

| —      | —   | —   | —   | —   | —   | _   | URX8     |

| bit 15 |     |     |     |     |     |     | bit 8    |

| R-0, HSC |

|----------|----------|----------|----------|----------|----------|----------|----------|

| URX7     | URX6     | URX5     | URX4     | URX3     | URX2     | URX1     | URX0     |

| bit 7    |          |          |          |          |          |          | bit 0    |

| Legend:           | HSC = Hardware Settable/ | HSC = Hardware Settable/Clearable bit |                    |  |  |  |

|-------------------|--------------------------|---------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit         | U = Unimplemented bit, read as '0'    |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared                  | x = Bit is unknown |  |  |  |

bit 15-9 Unimplemented: Read as '0'

bit 8 URX8: Data of the Received Character bit (in 9-bit mode)

bit 7-0 URX<7:0>: Data of the Received Character bits

#### 16.2.5 RTCVAL REGISTER MAPPINGS

#### REGISTER 16-4: YEAR: YEAR VALUE REGISTER<sup>(1)</sup>

| -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         - | U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|-----|-----|-----|-----|-----|-------|

| bit 15 bit 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _      | —   | _   | —   | —   | —   | —   | —     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-x  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| YRTEN3 | YRTEN2 | YRTEN1 | YRTEN0 | YRONE3 | YRONE2 | YRONE1 | YRONE0 |

| bit 7  | •      |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'

- bit 7-4 **YRTEN<3:0>:** Binary Coded Decimal Value of Year's Tens Digit bits Contains a value from 0 to 9.

- bit 3-0 **YRONE<3:0>:** Binary Coded Decimal Value of Year's Ones Digit bits Contains a value from 0 to 9.

**Note 1:** A write to the YEAR register is only allowed when RTCWREN = 1.

#### **REGISTER 16-5:** MTHDY: MONTH AND DAY VALUE REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   |

|--------|-----|-----|---------|---------|---------|---------|---------|

| —      | —   | —   | MTHTEN0 | MTHONE3 | MTHONE2 | MTHONE1 | MTHONE0 |

| bit 15 |     |     |         |         |         |         | bit 8   |

| U-0   | U-0              | R/W-x | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   |

|-------|------------------|-------|---------|---------|---------|---------|---------|

| —     | — DAYTEN1 DAYTEN |       | DAYTEN0 | DAYONE3 | DAYONE2 | DAYONE1 | DAYONE0 |

| bit 7 |                  |       |         |         |         |         | bit 0   |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-13 Unimplemented: Read as '0'

- bit 12 MTHTEN0: Binary Coded Decimal Value of Month's Tens Digit bit Contains a value of '0' or '1'.

- bit 11-8 MTHONE<3:0>: Binary Coded Decimal Value of Month's Ones Digit bits Contains a value from 0 to 9.

- bit 7-6 Unimplemented: Read as '0'

- bit 5-4 **DAYTEN<1:0>:** Binary Coded Decimal Value of Day's Tens Digit bits Contains a value from 0 to 3.

- bit 3-0 **DAYONE<3:0>:** Binary Coded Decimal Value of Day's Ones Digit bits Contains a value from 0 to 9.

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

### REGISTER 19-7: AD1CHITL: A/D SCAN COMPARE HIT REGISTER (LOW WORD)<sup>(1)</sup>

| R/W-0                 | R/W-0                     | R/W-0               | R/W-0                     | R/W-0            | R/W-0            | R/W-0          | R/W-0                 |

|-----------------------|---------------------------|---------------------|---------------------------|------------------|------------------|----------------|-----------------------|

| CHH15                 | CHH14                     | CHH13               | CHH12                     | CHH11            | CHH10            | CHH9           | CHH8 <sup>(2,3)</sup> |

| bit 15                |                           |                     |                           | •                | •                | •              | bit 8                 |

|                       |                           |                     |                           |                  |                  |                |                       |

| R/W-0                 | R/W-0                     | R/W-0               | R/W-0                     | R/W-0            | R/W-0            | R/W-0          | R/W-0                 |

| CHH7 <sup>(2,3)</sup> | CHH6 <sup>(2,3)</sup>     | CHH5 <sup>(2)</sup> | CHH4                      | CHH3             | CHH2             | CHH1           | CHH0                  |

| bit 7                 |                           |                     |                           |                  | ·                |                | bit 0                 |

|                       |                           |                     |                           |                  |                  |                |                       |

| Legend:               |                           |                     |                           |                  |                  |                |                       |

| R = Readable          | e bit                     | W = Writable b      | oit                       | U = Unimpler     | nented bit, read | l as '0'       |                       |

| -n = Value at         | POR                       | '1' = Bit is set    |                           | '0' = Bit is cle | ared             | x = Bit is unk | nown                  |

|                       |                           |                     |                           |                  |                  |                |                       |

| bit 15-0              | CHH<15:0>:                | A/D Compare H       | lit bits <sup>(2,3)</sup> |                  |                  |                |                       |

|                       | <u>If CM&lt;1:0&gt; =</u> | <u>11:</u>          |                           |                  |                  |                |                       |

|                       | 1 = A/D Res               | ult Buffer x has    | been written              | with data or a m | atch has occur   | red            |                       |

0 = A/D Result Buffer x has not been written with data

For All Other Values of CM<1:0>:

1 = A match has occurred on A/D Result Channel x

0 = No match has occurred on A/D Result Channel x

#### Note 1: Unimplemented channels are read as '0'.

2: The CHH<8:5> bits are not implemented in 20-pin devices.

**3:** The CHH<8:6> bits are not implemented in 28-pin devices.

| U-0    | R/W-0 | R/W-0 | R/W-0                | R/W-0                | R/W-0 | U-0   | U-0   |

|--------|-------|-------|----------------------|----------------------|-------|-------|-------|

| —      | CSS30 | CSS29 | CSS28                | CSS27                | CSS26 | —     | —     |

| bit 15 |       |       |                      |                      |       |       | bit 8 |

|        |       |       |                      |                      |       |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0                | R/W-0                | R/W-0 | R/W-0 | R/W-0 |

| CSS23  | CSS22 | CSS21 | CSS20 <sup>(2)</sup> | CSS19 <sup>(2)</sup> | CSS18 | CSS17 | CSS16 |

| bit 7  |       |       |                      |                      |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

- bit 14-10CSS<30:26>: A/D Input Scan Selection bits1 = Includes the corresponding channel for input scan0 = Skips the channel for input scanbit 9-8Unimplemented: Read as '0'bit 7-0CSS<23:16>: A/D Input Scan Selection bits<sup>(2)</sup>1 = Includes the corresponding channel for input scan0 = Skips the channel for input scan

- **Note 1:** Unimplemented channels are read as '0'. Do not select unimplemented channels for sampling as indeterminate results may be produced.

- 2: The CSS<20:19> bits are not implemented in 20-pin devices.

#### REGISTER 19-9: AD1CSSL: A/D INPUT SCAN SELECT REGISTER (LOW WORD)<sup>(1)</sup>

| R/W-0                 | R/W-0                 | R/W-0               | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0                 |

|-----------------------|-----------------------|---------------------|-------|-------|-------|-------|-----------------------|

| CSS15                 | CSS14                 | CSS13               | CSS12 | CSS11 | CSS10 | CSS9  | CSS8 <sup>(2,3)</sup> |

| bit 15                | •                     |                     | •     | •     |       |       | bit 8                 |

|                       |                       |                     |       |       |       |       |                       |

| R/W-0                 | R/W-0                 | R/W-0               | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0                 |

| CSS7 <sup>(2,3)</sup> | CSS6 <sup>(2,3)</sup> | CSS5 <sup>(2)</sup> | CSS4  | CSS3  | CSS2  | CSS1  | CSS0                  |

| bit 7                 | •                     |                     | •     | •     |       |       | bit 0                 |

|                       |                       |                     |       |       |       |       |                       |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 CSS<15:0>: A/D Input Scan Selection bits<sup>(2,3)</sup>

1 = Includes the corresponding ANx input for scan

- 0 = Skips the channel for input scan

- **Note 1:** Unimplemented channels are read as '0'. Do not select unimplemented channels for sampling as indeterminate results may be produced.

- 2: The CSS<8:5> bits are not implemented in 20-pin devices.

- 3: The CSS<8:6> bits are not implemented in 28-pin devices.

## TABLE 19-2:NUMERICAL EQUIVALENTS OF VARIOUS RESULT CODES:<br/>12-BIT FRACTIONAL FORMATS

| VIN/VREF   | 12-Bit<br>Output Code | 16-Bit Fractional Format<br>Equivalent Decimal Value | 16-Bit Signed Fractional Fo<br>Equivalent Decimal Val |                     |        |  |  |  |  |  |  |

|------------|-----------------------|------------------------------------------------------|-------------------------------------------------------|---------------------|--------|--|--|--|--|--|--|

| +4095/4096 | 0 1111 1111 1111      | 1111 1111 1111 0000                                  | 0.999                                                 | 0111 1111 1111 1000 | 0.999  |  |  |  |  |  |  |

| +4094/4096 | 0 1111 1111 1110      | 1111 1111 1110 0000                                  | 0.998                                                 | 0111 1111 1110 1000 | 0.998  |  |  |  |  |  |  |

|            |                       | • • •                                                |                                                       |                     |        |  |  |  |  |  |  |

| +1/4096    | 0 0000 0000 0001      | 0000 0000 0001 0000                                  | 0.001                                                 | 0000 0000 0000 1000 | 0.001  |  |  |  |  |  |  |

| 0/4096     | 0 0000 0000 0000      | 0000 0000 0000 0000                                  | 0.000                                                 | 0000 0000 0000 0000 | 0.000  |  |  |  |  |  |  |

| -1/4096    | 1 0111 1111 1111      | 0000 0000 0000 0000                                  | 0.000                                                 | 1111 1111 1111 1000 | -0.001 |  |  |  |  |  |  |

|            | •••                   |                                                      |                                                       |                     |        |  |  |  |  |  |  |

| -4095/4096 | 1 0000 0000 0001      | 0000 0000 0000 0000                                  | 0.000                                                 | 1000 0000 0000 1000 | -0.999 |  |  |  |  |  |  |

| -4096/4096 | 1 0000 0000 0000      | 0000 0000 0000 0000                                  | 0.000                                                 | 1000 0000 0000 0000 | -1.000 |  |  |  |  |  |  |

### FIGURE 19-5: A/D OUTPUT DATA FORMATS (10-BIT)

| RAM Contents:            |     |     |     |     |     |     | d09 | d08 | d07 | d06 | d05 | d04 | d03 | d02 | d01 | d00 |

|--------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Read to Bus:             |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     | I   |

| Integer                  | 0   | 0   | 0   | 0   | 0   | 0   | d09 | d08 | d07 | d06 | d05 | d04 | d03 | d02 | d01 | d00 |

|                          |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

| Signed Integer           | s0  | s0  | s0  | s0  | s0  | s0  | d09 | d08 | d07 | d06 | d05 | d04 | d03 | d02 | d01 | d00 |

|                          |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

| Fractional (1.15)        | d09 | d08 | d07 | d06 | d05 | d04 | d03 | d02 | d01 | d00 | 0   | 0   | 0   | 0   | 0   | 0   |

|                          |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

| Signed Fractional (1.15) | s0  | d09 | d08 | d07 | d06 | d05 | d04 | d03 | d02 | d01 | d00 | 0   | 0   | 0   | 0   | 0   |

|                          | L   | I   |     |     |     |     |     | 1   | I   |     |     |     |     |     |     |     |

## TABLE 19-3:NUMERICAL EQUIVALENTS OF VARIOUS RESULT CODES:<br/>10-BIT INTEGER FORMATS

| VIN/VREF   | 10-Bit Differential<br>Output Code<br>(11-bit result) | 16-Bit Integer Format/16-Bit Signed Integer ForEquivalent Decimal ValueEquivalent Decimal Value |      |                     |       |  |  |  |  |  |  |  |

|------------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------|------|---------------------|-------|--|--|--|--|--|--|--|

| +1023/1024 | 011 1111 1111                                         | 0000 0011 1111 1111                                                                             | 1023 | 0000 0001 1111 1111 | 1023  |  |  |  |  |  |  |  |

| +1022/1024 | 011 1111 1110                                         | 0000 0011 1111 1110                                                                             | 1022 | 0000 0001 1111 1110 | 1022  |  |  |  |  |  |  |  |

|            |                                                       | •••                                                                                             |      |                     |       |  |  |  |  |  |  |  |

| +1/1024    | 000 0000 0001                                         | 0000 0000 0000 0001                                                                             | 1    | 0000 0000 0000 0001 | 1     |  |  |  |  |  |  |  |

| 0/1024     | 000 0000 0000                                         | 0000 0000 0000 0000                                                                             | 0    | 0000 0000 0000 0000 | 0     |  |  |  |  |  |  |  |

| -1/1024    | 101 1111 1111                                         | 0000 0000 0000 0000                                                                             | 0    | 1111 1111 1111 1111 | -1    |  |  |  |  |  |  |  |

|            | •••                                                   |                                                                                                 |      |                     |       |  |  |  |  |  |  |  |

| -1023/1024 | 100 0000 0001                                         | 0000 0000 0000 0000                                                                             | 0    | 1111 1110 0000 0001 | -1023 |  |  |  |  |  |  |  |

| -1024/1024 | 100 0000 0000                                         | 0000 0000 0000 0000                                                                             | 0    | 1111 1110 0000 0000 | -1024 |  |  |  |  |  |  |  |

### 22.0 COMPARATOR MODULE

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the Comparator module, refer to the "PIC24F Family Reference Manual", "Scalable Comparator Module" (DS39734).

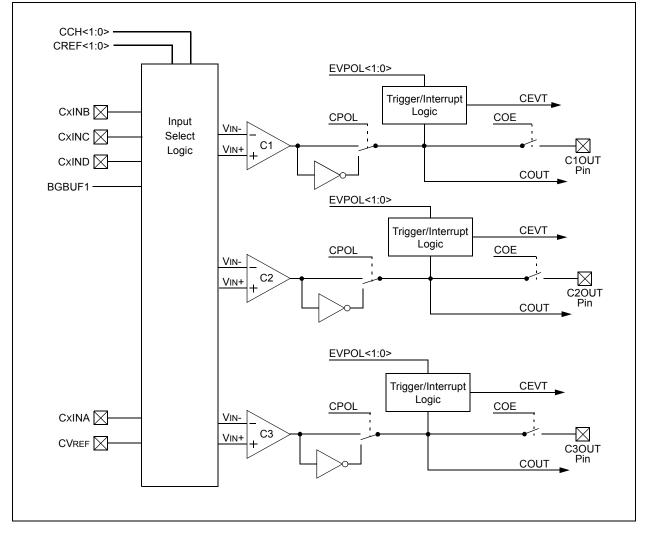

The comparator module provides three dual input comparators. The inputs to the comparator can be configured to use any one of four external analog inputs, as well as a voltage reference input from either the Internal Band Gap Buffer 1 (BGBUF1) or the comparator voltage reference generator. The comparator outputs may be directly connected to the CxOUT pins. When the respective COE bit equals '1', the I/O pad logic makes the unsynchronized output of the comparator available on the pin.

A simplified block diagram of the module is shown in Figure 22-1. Diagrams of the possible individual comparator configurations are shown in Figure 22-2.

Each comparator has its own control register, CMxCON (Register 22-1), for enabling and configuring its operation. The output and event status of all three comparators is provided in the CMSTAT register (Register 22-2).

#### FIGURE 22-1: COMPARATOR x MODULE BLOCK DIAGRAM

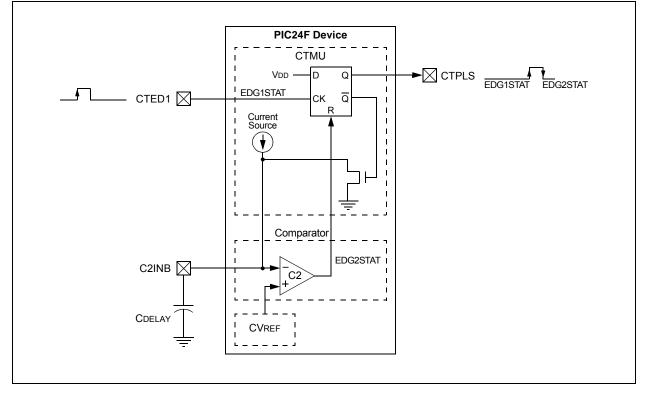

### 24.3 Pulse Generation and Delay

The CTMU module can also generate an output pulse with edges that are not synchronous with the device's system clock. More specifically, it can generate a pulse with a programmable delay from an edge event input to the module.

When the module is configured for pulse generation delay by setting the TGEN bit (CTMUCON1L<12>), the internal current source is connected to the B input of Comparator 2. A Capacitor (CDELAY) is connected to the Comparator 2 pin, C2INB, and the Comparator Voltage Reference, CVREF, is connected to C2INA. CVREF is then configured for a specific trip point. The module begins to charge CDELAY when an edge event is detected. While CVREF is greater than the voltage on CDELAY, the CTPLS pin is high.

When the voltage on CDELAY equals CVREF, CTPLS goes low. With Comparator 2 configured as the second edge, this stops the CTMU from charging. In this state event, the CTMU automatically connects to ground. The IDISSEN bit doesn't need to be set and cleared before the next CTPLS cycle.

Figure 24-3 illustrates the external connections for pulse generation, as well as the relationship of the different analog modules required. While CTED1 is shown as the input pulse source, other options are available. A detailed discussion on pulse generation with the CTMU module is provided in the "*PIC24F Family Reference Manual*".

## FIGURE 24-3: TYPICAL CONNECTIONS AND INTERNAL CONFIGURATION FOR PULSE DELAY GENERATION

| R/P-1                                 | R/P-1                                                                                                                                                                                                                         | R/P-1                                    | R/P-1         | R/P-1                              | R/P-1  | R/P-1              | R/P-1  |  |  |  |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|---------------|------------------------------------|--------|--------------------|--------|--|--|--|

| FWDTEN1                               | WINDIS                                                                                                                                                                                                                        | FWDTEN0                                  | FWPSA         | WDTPS3                             | WDTPS2 | WDTPS1             | WDTPS0 |  |  |  |

| bit 7                                 |                                                                                                                                                                                                                               |                                          |               |                                    |        |                    | bit (  |  |  |  |

| Legend:                               |                                                                                                                                                                                                                               |                                          |               |                                    |        |                    |        |  |  |  |

| R = Readable bit<br>-n = Value at POR |                                                                                                                                                                                                                               | P = Programmable bit<br>'1' = Bit is set |               | U = Unimplemented bit, read as '0' |        |                    |        |  |  |  |

|                                       |                                                                                                                                                                                                                               |                                          |               | '0' = Bit is clea                  | ared   | x = Bit is unknown |        |  |  |  |

| bit 7,5                               | FWDTEN<1:0                                                                                                                                                                                                                    | >: Watchdog Ti                           | mer Enable bi | ts                                 |        |                    |        |  |  |  |

|                                       | 11 = WDT is enabled in hardware                                                                                                                                                                                               |                                          |               |                                    |        |                    |        |  |  |  |

|                                       | <ul> <li>10 = WDT is controlled with the SWDTEN bit setting</li> <li>01 = WDT is enabled only while the device is active, WDT is disabled in Sleep; SWDTEN bit is disabled</li> </ul>                                         |                                          |               |                                    |        |                    |        |  |  |  |

|                                       | 00 = WDT is disabled in hardware; SWDTEN bit is disabled in Sleep; SWDTEN bit is disabled<br>00 = WDT is disabled in hardware; SWDTEN bit is disabled                                                                         |                                          |               |                                    |        |                    |        |  |  |  |

| bit 6                                 | WINDIS: Windowed Watchdog Timer Disable bit                                                                                                                                                                                   |                                          |               |                                    |        |                    |        |  |  |  |

|                                       | 1 = Standard WDT is selected; windowed WDT is disabled                                                                                                                                                                        |                                          |               |                                    |        |                    |        |  |  |  |

|                                       | <ul> <li>0 = Windowed WDT is enabled; note that executing a CLRWDT instruction while the WDT is disabled hardware and software (FWDTEN&lt;1:0&gt; = 00 and SWDTEN (RCON&lt;5&gt;) = 0) will not cause device Reset</li> </ul> |                                          |               |                                    |        |                    |        |  |  |  |

| bit 4                                 | FWPSA: WDT Prescaler bit                                                                                                                                                                                                      |                                          |               |                                    |        |                    |        |  |  |  |

|                                       | 1 = WDT prescaler ratio of 1:128                                                                                                                                                                                              |                                          |               |                                    |        |                    |        |  |  |  |

|                                       | 0 = WDT prescaler ratio of 1:32                                                                                                                                                                                               |                                          |               |                                    |        |                    |        |  |  |  |

| bit 3-0                               | WDTPS<3:0>: Watchdog Timer Postscale Select bits                                                                                                                                                                              |                                          |               |                                    |        |                    |        |  |  |  |

|                                       | 1111 = 1:32,7                                                                                                                                                                                                                 |                                          |               |                                    |        |                    |        |  |  |  |

|                                       | 1110 = 1:16,3                                                                                                                                                                                                                 |                                          |               |                                    |        |                    |        |  |  |  |

|                                       | 1101 = 1:8,19<br>1100 = 1:4,09                                                                                                                                                                                                |                                          |               |                                    |        |                    |        |  |  |  |

|                                       | 1011 = 1:2,04                                                                                                                                                                                                                 |                                          |               |                                    |        |                    |        |  |  |  |

|                                       | 1010 = 1.2,04<br>1010 = 1:1,02                                                                                                                                                                                                |                                          |               |                                    |        |                    |        |  |  |  |

|                                       | 1001 = 1:512                                                                                                                                                                                                                  |                                          |               |                                    |        |                    |        |  |  |  |

|                                       | 1000 <b>= 1:256</b>                                                                                                                                                                                                           |                                          |               |                                    |        |                    |        |  |  |  |

|                                       | 0111 <b>= 1:128</b>                                                                                                                                                                                                           |                                          |               |                                    |        |                    |        |  |  |  |

|                                       | 0110 = 1:64                                                                                                                                                                                                                   |                                          |               |                                    |        |                    |        |  |  |  |

|                                       | 0101 = 1:32<br>0100 = 1:16                                                                                                                                                                                                    |                                          |               |                                    |        |                    |        |  |  |  |

|                                       | 0100 = 1.16<br>0011 = 1:8                                                                                                                                                                                                     |                                          |               |                                    |        |                    |        |  |  |  |

|                                       | 0010 = 1.0<br>0010 = 1.4                                                                                                                                                                                                      |                                          |               |                                    |        |                    |        |  |  |  |

|                                       | 0001 = 1:2                                                                                                                                                                                                                    |                                          |               |                                    |        |                    |        |  |  |  |

|                                       | 0000 = 1:1                                                                                                                                                                                                                    |                                          |               |                                    |        |                    |        |  |  |  |

#### REGISTER 25-5: FWDT: WATCHDOG TIMER CONFIGURATION REGISTER

NOTES:

### 26.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16 and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

### 26.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

#### 26.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

### 26.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- · MPLAB X IDE compatibility

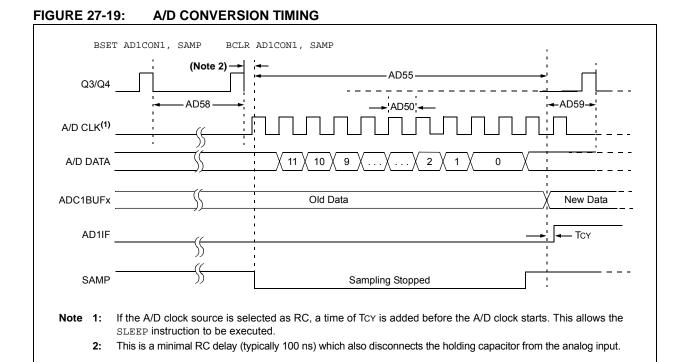

### TABLE 27-38: A/D CONVERSION TIMING REQUIREMENTS<sup>(1)</sup>

| AC CHARACTERISTICS |       |                                                      | Operating temperature |          |          |            | : 1.8V to 3.6V (PIC24F16KM204)<br>2.0V to 5.5V (PIC24FV16KM204)<br>-40°C $\leq$ TA $\leq$ +85°C for Industrial<br>-40°C $\leq$ TA $\leq$ +125°C for Extended |  |  |

|--------------------|-------|------------------------------------------------------|-----------------------|----------|----------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Param<br>No.       | Sym   | Characteristic                                       | Min.                  | Тур      | Max.     | Units      | Conditions                                                                                                                                                   |  |  |

|                    |       |                                                      | Clock P               | aramete  | rs       |            |                                                                                                                                                              |  |  |

| AD50               | Tad   | A/D Clock Period                                     | 600                   | _        | —        | ns         | Tcy = 75 ns, AD1CON3 in default state                                                                                                                        |  |  |

| AD51               | TRC   | A/D Internal RC Oscillator Period                    | —                     | 1.67     | —        | μs         |                                                                                                                                                              |  |  |

|                    |       |                                                      | Conver                | sion Rat | e        |            |                                                                                                                                                              |  |  |

| AD55               | Τςονν | Conversion Time                                      | _                     | 12<br>14 | _        | Tad<br>Tad | 10-bit results<br>12-bit results                                                                                                                             |  |  |

| AD56               | FCNV  | Throughput Rate                                      | _                     | _        | 100      | ksps       |                                                                                                                                                              |  |  |

| AD57               | TSAMP | Sample Time                                          | _                     | 1        | _        | TAD        |                                                                                                                                                              |  |  |

| AD58               | TACQ  | Acquisition Time                                     | 750                   |          | —        | ns         | (Note 2)                                                                                                                                                     |  |  |

| AD59               | Tswc  | Switching Time from Convert to Sample                | —                     | —        | (Note 3) |            |                                                                                                                                                              |  |  |

| AD60               | TDIS  | Discharge Time                                       | 12                    |          | —        | TAD        |                                                                                                                                                              |  |  |

|                    |       | ·                                                    | Clock P               | aramete  | rs       |            | -                                                                                                                                                            |  |  |

| AD61               | TPSS  | Sample Start Delay from<br>Setting Sample bit (SAMP) | 2                     | —        | 3        | Tad        |                                                                                                                                                              |  |  |

**Note 1:** Because the sample caps will eventually lose charge, clock rates below 10 kHz can affect linearity performance, especially at elevated temperatures.

- 2: The time for the holding capacitor to acquire the "New" input voltage when the voltage changes full scale after the conversion (VDD to Vss or Vss to VDD).

- 3: On the following cycle of the device clock.

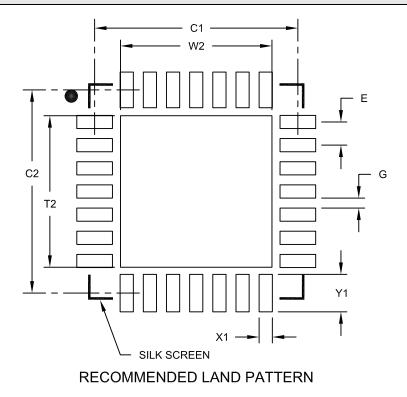

# 28-Lead Plastic Quad Flat, No Lead Package (ML) – 6x6 mm Body [QFN] with 0.55 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | MILLIMETERS |      |          |      |  |  |

|----------------------------|-------------|------|----------|------|--|--|

| Dimensior                  | MIN         | NOM  | MAX      |      |  |  |

| Contact Pitch              | E           |      | 0.65 BSC |      |  |  |

| Optional Center Pad Width  | W2          |      |          | 4.25 |  |  |

| Optional Center Pad Length | T2          |      |          | 4.25 |  |  |

| Contact Pad Spacing        | C1          |      | 5.70     |      |  |  |

| Contact Pad Spacing        | C2          |      | 5.70     |      |  |  |

| Contact Pad Width (X28)    | X1          |      |          | 0.37 |  |  |

| Contact Pad Length (X28)   | Y1          |      |          | 1.00 |  |  |

| Distance Between Pads      | G           | 0.20 |          |      |  |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2105A

NOTES: