Welcome to E-XFL.COM

## What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| 2 0 0 0 0 0                |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                      |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 37                                                                            |

| Program Memory Size        | 16KB (5.5K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 1K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5V                                                                       |

| Data Converters            | A/D 22x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 44-TQFP                                                                       |

| Supplier Device Package    | 44-TQFP (10x10)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fv16km104-e-pt |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 1-5: PIC24FV16KM204 FAMILY PINOUT DESCRIPTION (CONTINUED)

|          |                                  |                                  | F             |                        |                |                                  |                                  | FV            |                        |                |     |        |                                                |  |

|----------|----------------------------------|----------------------------------|---------------|------------------------|----------------|----------------------------------|----------------------------------|---------------|------------------------|----------------|-----|--------|------------------------------------------------|--|

|          |                                  | F                                | Pin Numb      | er                     |                |                                  | I                                | Pin Numb      | er                     |                |     |        |                                                |  |

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | I/O | Buffer | Description                                    |  |

| MCLR     | 1                                | 1                                | 26            | 18                     | 19             | 1                                | 1                                | 26            | 18                     | 19             | Ι   | ST     | Master Clear (Device Reset) Input (active-low) |  |

| OA1INA   | _                                | 5                                | 2             | 22                     | 24             |                                  | 5                                | 2             | 22                     | 24             | Ι   | ANA    | Op Amp 1 Input A                               |  |

| OA1INB   | _                                | 6                                | 3             | 23                     | 25             | _                                | 6                                | 3             | 23                     | 25             | Ι   | ANA    | Op Amp 1 Input B                               |  |

| OA1INC   | _                                | 24                               | 21            | 11                     | 12             | _                                | 24                               | 21            | 11                     | 12             | Ι   | ANA    | Op Amp 1 Input C                               |  |

| OA1IND   | _                                | 25                               | 22            | 14                     | 15             | _                                | 25                               | 22            | 14                     | 15             | Ι   | ANA    | Op Amp 1 Input D                               |  |

| OA1OUT   | _                                | 7                                | 4             | 24                     | 26             | _                                | 7                                | 4             | 24                     | 26             | 0   | ANA    | Op Amp 1 Analog Output                         |  |

| OA2INA   | _                                | 5                                | 2             | 22                     | 24             | _                                | 5                                | 2             | 22                     | 24             | Ι   | ANA    | Op Amp 2 Input A                               |  |

| OA2INB   | _                                | 6                                | 3             | 23                     | 25             | _                                | 6                                | 3             | 23                     | 25             | Ι   | ANA    | Op Amp 2 Input B                               |  |

| OA2INC   | _                                | 24                               | 21            | 11                     | 12             | _                                | 24                               | 21            | 11                     | 12             | Ι   | ANA    | Op Amp 2 Input C                               |  |

| OA2IND   | _                                | 25                               | 22            | 14                     | 15             | _                                | 25                               | 22            | 14                     | 15             | Ι   | ANA    | Op Amp 2 Input D                               |  |

| OA2OUT   | _                                | 26                               | 23            | 15                     | 16             | _                                | 26                               | 23            | 15                     | 16             | 0   | ANA    | Op Amp 2 Analog Output                         |  |

| OC1A     | 14                               | 20                               | 17            | 7                      | 7              | 11                               | 16                               | 13            | 43                     | 47             | 0   | _      | MCCP1 Output Compare A                         |  |

| OC1B     | 12                               | 17                               | 14            | 44                     | 48             | 12                               | 17                               | 14            | 44                     | 48             | 0   | _      | MCCP1 Output Compare B                         |  |

| OC1C     | 15                               | 21                               | 18            | 8                      | 9              | 15                               | 21                               | 18            | 8                      | 9              | 0   | _      | MCCP1 Output Compare C                         |  |

| OC1D     | 16                               | 24                               | 21            | 11                     | 12             | 16                               | 24                               | 21            | 11                     | 12             | 0   |        | MCCP1 Output Compare D                         |  |

| OC1E     | _                                | 14                               | 11            | 41                     | 45             | _                                | 14                               | 11            | 41                     | 45             | 0   | _      | MCCP1 Output Compare E                         |  |

| OC1F     | _                                | 15                               | 12            | 42                     | 46             | _                                | 15                               | 12            | 42                     | 46             | 0   | _      | MCCP1 Output Compare F                         |  |

| OC2A     | 4                                | 22                               | 19            | 9                      | 10             | 4                                | 22                               | 19            | 9                      | 10             | 0   |        | MCCP2 Output Compare A                         |  |

| OC2B     | _                                | 23                               | 20            | 10                     | 11             |                                  | 23                               | 20            | 10                     | 11             | 0   | _      | MCCP2 Output Compare B                         |  |

| OC2C     | _                                |                                  | _             | 2                      | 2              |                                  |                                  |               | 2                      | 2              | 0   |        | MCCP2 Output Compare C                         |  |

| OC2D     | _                                |                                  | _             | 3                      | 3              |                                  |                                  |               | 3                      | 3              | 0   |        | MCCP2 Output Compare D                         |  |

| OC2E     | _                                |                                  | _             | 4                      | 4              |                                  |                                  |               | 4                      | 4              | 0   |        | MCCP2 Output Compare E                         |  |

| OC2F     | _                                |                                  | _             | 5                      | 5              |                                  |                                  |               | 5                      | 5              | 0   |        | MCCP2 Output Compare F                         |  |

| OC3A     | _                                | 21                               | 18            | 12                     | 13             |                                  | 21                               | 18            | 12                     | 13             | 0   | _      | MCCP3 Output Compare A                         |  |

| OC3B     | _                                | 24                               | 21            | 13                     | 14             | _                                | 24                               | 21            | 13                     | 14             | 0   | _      | MCCP3 Output Compare B                         |  |

| OC4      | _                                | 18                               | 15            | 1                      | 1              | _                                | 18                               | 15            | 1                      | 1              | 0   | _      | SCCP4 Output Compare                           |  |

| OC5      | _                                | 19                               | 16            | 6                      | 6              | _                                | 19                               | 16            | 6                      | 6              | 0   | _      | SCCP5 Output Compare                           |  |

| OCFA     | 17                               | 25                               | 22            | 14                     | 15             | 17                               | 25                               | 22            | 14                     | 15             | Ι   | ST     | MCCP/SCCP Output Compare Fault Input A         |  |

| OCFB     | 16                               | 24                               | 21            | 32                     | 35             | 16                               | 24                               | 21            | 32                     | 35             | Ι   | ST     | MCCP/SCCP Output Compare Fault Input B         |  |

Legend: ANA = Analog level input/output, ST = Schmitt Trigger input buffer, I<sup>2</sup>C<sup>™</sup> = I<sup>2</sup>C/SMBus input buffer

# DS30003030B-page 24

# TABLE 1-5: PIC24FV16KM204 FAMILY PINOUT DESCRIPTION (CONTINUED)

|          |                                  |                                  | F             |                        |                |                                  |                                  | FV            |                        |                |     |        |                                                |  |

|----------|----------------------------------|----------------------------------|---------------|------------------------|----------------|----------------------------------|----------------------------------|---------------|------------------------|----------------|-----|--------|------------------------------------------------|--|

|          |                                  | I                                | Pin Numb      | ber                    |                |                                  | I                                | Pin Numb      | er                     |                |     |        |                                                |  |

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | I/O | Buffer | Description                                    |  |

| SCL1     | 12                               | 17                               | 14            | 44                     | 48             | 12                               | 17                               | 14            | 44                     | 48             | I/O | I2C    | MSSP1 I <sup>2</sup> C Clock                   |  |

| SDA1     | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | I/O | I2C    | MSSP1 I <sup>2</sup> C Data                    |  |

| SCL2     | _                                | 7                                | 4             | 24                     | 26             | _                                | 7                                | 4             | 24                     | 26             | I/O | I2C    | MSSP2 I <sup>2</sup> C Clock                   |  |

| SDA2     | _                                | 6                                | 3             | 23                     | 25             | _                                | 6                                | 3             | 23                     | 25             | I/O | I2C    | MSSP2 I <sup>2</sup> C Data                    |  |

| SCLKI    | 10                               | 12                               | 9             | 34                     | 37             | 10                               | 12                               | 9             | 34                     | 37             | Ι   | ST     | Secondary Clock Digital Input                  |  |

| SOSCI    | 9                                | 11                               | 8             | 33                     | 36             | 9                                | 11                               | 8             | 33                     | 36             | Ι   | ANA    | Secondary Oscillator Input                     |  |

| SOSCO    | 10                               | 12                               | 9             | 34                     | 37             | 10                               | 12                               | 9             | 34                     | 37             | Ι   | ANA    | Secondary Oscillator Output                    |  |

| T1CK     | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | Ι   | ST     | Timer1 Digital Input Cock                      |  |

| TCKIA    | 18                               | 26                               | 23            | 15                     | 16             | 18                               | 26                               | 23            | 15                     | 16             | Ι   | ST     | MCCP/SCCP Time Base Clock Input A              |  |

| TCKIB    | 6                                | 6                                | 3             | 23                     | 25             | 6                                | 6                                | 3             | 23                     | 25             | Ι   | ST     | MCCP/SCCP Time Base Clock Input B              |  |

| U1CTS    | 12                               | 17                               | 14            | 44                     | 48             | 12                               | 17                               | 14            | 44                     | 48             | Ι   | ST     | UART1 Clear-To-Send Input                      |  |

| U1RTS    | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | 0   | _      | UART1 Request-To-Send Output                   |  |

| U1BCLK   | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | 0   | —      | UART1 16x Baud Rate Clock Output               |  |

| U1RX     | 6                                | 6                                | 3             | 2                      | 2              | 6                                | 6                                | 3             | 2                      | 2              | Ι   | ST     | UART1 Receive                                  |  |

| U1TX     | 11                               | 16                               | 13            | 3                      | 3              | 11                               | 16                               | 13            | 3                      | 3              | 0   | _      | UART1 Transmit                                 |  |

| U2CTS    | _                                | 12                               | 9             | 34                     | 37             | _                                | 12                               | 9             | 34                     | 37             | I   | ST     | UART2 Clear-To-Send Input                      |  |

| U2RTS    | _                                | 11                               | 8             | 33                     | 36             | _                                | 11                               | 8             | 33                     | 36             | 0   | _      | UART2 Request-To-Send Output                   |  |

| U2BCLK   | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | 0   | —      | UART2 16x Baud Rate Clock Output               |  |

| U2RX     | _                                | 5                                | 2             | 22                     | 24             | —                                | 5                                | 2             | 22                     | 24             | Ι   | ST     | UART2 Receive                                  |  |

| U2TX     | _                                | 4                                | 1             | 21                     | 23             | —                                | 4                                | 1             | 21                     | 23             | 0   | _      | UART2 Transmit                                 |  |

| ULPWU    | 4                                | 4                                | 1             | 21                     | 23             | 4                                | 4                                | 1             | 21                     | 23             | Ι   | ANA    | Ultra Low-Power Wake-up Input                  |  |

| VCAP     | _                                | _                                |               | —                      | _              | 14                               | 20                               | 17            | 7                      | 7              | Р   | —      | Regulator External Filter Capacitor Connection |  |

| Vdd      | 20                               | 28                               | 25            | 17,28,28               | 18,30,30       | 20                               | 28                               | 25            | 17,28,28               | 18,30,30       | Р   | —      | Device Positive Supply Voltage                 |  |

| VDDCORE  | _                                | _                                | _             | —                      | _              | 14                               | 20                               | 17            | 7                      | 7              | Р   | —      | Microcontroller Core Supply Voltage            |  |

| Vpp      | 1                                | 1                                | 26            | 18                     | 19             | 1                                | 1                                | 26            | 18                     | 19             | Р   | —      | High-Voltage Programming Pin                   |  |

| VREF+    | 2                                | 2                                | 27            | 19                     | 21             | 2                                | 2                                | 27            | 19                     | 21             | I   | ANA    | A/D Reference Voltage Positive Input           |  |

| VREF-    | 3                                | 3                                | 28            | 20                     | 22             | 3                                | 3                                | 28            | 20                     | 22             | Ι   | ANA    | A/D Reference Voltage Negative Input           |  |

| Vss      | 19                               | 27                               | 24            | 16,29,29               | 17,31,31       | 19                               | 27                               | 24            | 16,29,29               | 17,31,31       | Р   | —      | Device Ground Return Voltage                   |  |

Legend: ANA = Analog level input/output, ST = Schmitt Trigger input buffer, I<sup>2</sup>C<sup>™</sup> = I<sup>2</sup>C/SMBus input buffer

## TABLE 4-9: MCCP2 REGISTER MAP

| File Name | Addr. | Bit 15  | Bit 14                       | Bit 13               | Bit 12               | Bit 11               | Bit 10               | Bit 9                | Bit 8                | Bit 7        | Bit 6        | Bit 5   | Bit 4                 | Bit 3   | Bit 2   | Bit 1                  | Bit 0      | All<br>Resets |

|-----------|-------|---------|------------------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|--------------|--------------|---------|-----------------------|---------|---------|------------------------|------------|---------------|

| CCP2CON1L | 164h  | CCPON   | _                            | CCPSIDL              | r                    | TMRSYNC              | CLKSEL2              | CLKSEL1              | CLKSEL0              | TMRPS1       | TMRPS0       | T32     | CCSEL                 | MOD3    | MOD2    | MOD1                   | MOD0       | 0000          |

| CCP2CON1H | 166h  | OPSSRC  | RTRGEN                       | _                    | _                    | IOPS3                | IOPS2                | IOPS1                | IOPS0                | TRIGEN       | ONESHOT      | ALTSYNC | SYNC4                 | SYNC3   | SYNC2   | SYNC1                  | SYNC0      | 0000          |

| CCP2CON2L | 168h  | PWMRSEN | ASDGM                        |                      | SSDG                 |                      |                      | _                    | _                    | ASDG7        | ASDG6        | ASDG5   | ASDG4                 | ASDG3   | ASDG2   | ASDG1                  | ASDG0      | 0000          |

| CCP2CON2H | 16Ah  | OENSYNC | -                            | OCFEN <sup>(1)</sup> | OCEEN <sup>(1)</sup> | OCDEN <sup>(1)</sup> | OCCEN <sup>(1)</sup> | OCBEN <sup>(1)</sup> | OCAEN                | ICGSM1       | ICGSM0       | _       | AUXOUT1               | AUXOUT0 | ICSEL2  | ICSEL1                 | ICSEL0     | 0100          |

| CCP2CON3L | 16Ch  | _       | _                            | _                    | _                    | _                    | _                    | _                    | _                    | _            |              | DT5     | DT4                   | DT3     | DT2     | DT1                    | DT0        | 0000          |

| CCP2CON3H | 16Eh  | OETRIG  | OSCNT2                       | OSCNT1               | OSCNT0               | _                    | OUTM2 <sup>(1)</sup> | OUTM1 <sup>(1)</sup> | OUTM0 <sup>(1)</sup> | _            | _            | POLACE  | POLBDF <sup>(1)</sup> | PSSACE1 | PSSACE0 | PSSBDF1 <sup>(1)</sup> | PSSBDF0(1) | 0000          |

| CCP2STATL | 170h  | _       | -                            |                      | _                    |                      |                      | _                    | _                    | CCPTRIG      | TRSET        | TRCLR   | ASEVT                 | SCEVT   | ICDIS   | ICOV                   | ICBNE      | 0000          |

| CCP2TMRL  | 174h  |         |                              |                      |                      |                      |                      | MCC                  | P2 Time Ba           | ase Register | r Low Word   |         |                       |         |         |                        |            | 0000          |

| CCP2TMRH  | 176h  |         |                              |                      |                      |                      |                      | MCC                  | P2 Time Ba           | se Register  | High Word    |         |                       |         |         |                        |            | 0000          |

| CCP2PRL   | 178h  |         |                              |                      |                      |                      |                      | MCCP2                | Time Base            | Period Regi  | ister Low Wo | rd      |                       |         |         |                        |            | FFFF          |

| CCP2PRH   | 17Ah  |         |                              |                      |                      |                      |                      | MCCP2                | Time Base I          | Period Regi  | ster High Wo | rd      |                       |         |         |                        |            | FFFF          |

| CCP2RAL   | 17Ch  |         |                              |                      |                      |                      |                      | 0                    | utput Comp           | oare 2 Data  | Word A       |         |                       |         |         |                        |            | 0000          |

| CCP2RBL   | 180h  |         | Output Compare 2 Data Word B |                      |                      |                      |                      |                      |                      |              |              |         |                       | 0000    |         |                        |            |               |

| CCP2BUFL  | 184h  |         |                              |                      |                      |                      |                      | Input                | Capture 2            | Data Buffer  | Low Word     |         |                       |         |         |                        |            | 0000          |

| CCP2BUFH  | 186h  |         |                              |                      |                      |                      |                      | Input                | Capture 2            | Data Buffer  | High Word    |         |                       |         |         |                        |            | 0000          |

PIC24FV16KM204 FAMILY

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

Note 1: These bits are available only on PIC24F(V)16KM2XX devices.

## EXAMPLE 5-5: INITIATING A PROGRAMMING SEQUENCE – ASSEMBLY LANGUAGE CODE

| DISI | #5          | ; | Block all interrupts<br>for next 5 instructions |

|------|-------------|---|-------------------------------------------------|

| MOV  | #0x55, W0   |   |                                                 |

| MOV  | W0, NVMKEY  | ; | Write the 55 key                                |

| MOV  | #0xAA, W1   | ; |                                                 |

| MOV  | W1, NVMKEY  | ; | Write the AA key                                |

| BSET | NVMCON, #WR | ; | Start the erase sequence                        |

| NOP  |             | ; | 2 NOPs required after setting WR                |

| NOP  |             | ; |                                                 |

| BTSC | NVMCON, #15 | ; | Wait for the sequence to be completed           |

| BRA  | \$-2        | ; |                                                 |

|      |             |   |                                                 |

# EXAMPLE 5-6: INITIATING A PROGRAMMING SEQUENCE – 'C' LANGUAGE CODE

| // C example using MPLAB C30 |                                                 |

|------------------------------|-------------------------------------------------|

| asm("DISI #5");              | // Block all interrupts for next 5 instructions |

| builtin_write_NVM();         | // Perform unlock sequence and set WR           |

# REGISTER 8-7: IFS2: INTERRUPT FLAG STATUS REGISTER 2

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0, HS | U-0   |

|--------|-----|-----|-----|-----|-----|-----------|-------|

| —      | —   | —   | —   | —   | —   | CCT5IF    | —     |

| bit 15 |     |     |     |     |     |           | bit 8 |

|        |     |     |     |     |     |           |       |

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0       | U-0   |

|        |     | _   | _   |     | _   |           | _     |

| bit 7  |     |     |     |     |     |           | bit 0 |

| Legend:           | HS = Hardware Settable bit |                             |                    |

|-------------------|----------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-10 | Unimplemented: Read as '0'                                |

|-----------|-----------------------------------------------------------|

| bit 9     | CCT5IF: Capture/Compare 5 Timer Interrupt Flag Status bit |

|           | 1 = Interrupt request has occurred                        |

|           | 0 = Interrupt request has not occurred                    |

|           |                                                           |

bit 8-0 Unimplemented: Read as '0'

# REGISTER 8-8: IFS3: INTERRUPT FLAG STATUS REGISTER 3

| U-0    | R/W-0, HS | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----------|-----|-----|-----|-----|-----|-------|

| —      | RTCIF     | —   | —   | —   | —   | —   | —     |

| bit 15 |           |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0, HS | R/W-0, HS | U-0   |

|-------|-----|-----|-----|-----|-----------|-----------|-------|

| —     | —   | —   | —   | —   | BCL2IF    | SSP2IF    | —     |

| bit 7 |     |     |     |     |           |           | bit 0 |

| Legend:           | HS = Hardware Settable bit |                             |                    |

|-------------------|----------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15   | Unimplemented: Read as '0'                                                          |

|----------|-------------------------------------------------------------------------------------|

| bit 14   | RTCIF: Real-Time Clock and Calendar Interrupt Flag Status bit                       |

|          | 1 = Interrupt request has occurred                                                  |

|          | 0 = Interrupt request has not occurred                                              |

| bit 13-3 | Unimplemented: Read as '0'                                                          |

| bit 2    | BCL2IF: MSSP2 I <sup>2</sup> C <sup>™</sup> Bus Collision Interrupt Flag Status bit |

|          | 1 = Interrupt request has occurred                                                  |

|          | 0 = Interrupt request has not occurred                                              |

| bit 1    | SSP2IF: MSSP2 SPI/I <sup>2</sup> C Event Interrupt Flag Status bit                  |

|          | 1 = Interrupt request has occurred                                                  |

|          | 0 = Interrupt request has not occurred                                              |

| bit 0    | Unimplemented: Read as '0'                                                          |

|          |                                                                                     |

# 8.4 Interrupt Setup Procedures

# 8.4.1 INITIALIZATION

To configure an interrupt source:

- 1. Set the NSTDIS control bit (INTCON1<15>) if nested interrupts are not desired.

- Select the user-assigned priority level for the interrupt source by writing the control bits in the appropriate IPCx register. The priority level will depend on the specific application and type of interrupt source. If multiple priority levels are not desired, the IPCx register control bits for all enabled interrupt sources may be programmed to the same non-zero value.

**Note:** At a device Reset, the IPCx registers are initialized, such that all user interrupt sources are assigned to Priority Level 4.

- 3. Clear the interrupt flag status bit associated with the peripheral in the associated IFSx register.

- 4. Enable the interrupt source by setting the interrupt enable control bit associated with the source in the appropriate IECx register.

# 8.4.2 INTERRUPT SERVICE ROUTINE

The method that is used to declare an ISR (Interrupt Service Routine) and initialize the IVT with the correct vector address depends on the programming language (i.e., C or assembly), and the language development toolsuite that is used to develop the application. In general, the user must clear the interrupt flag in the appropriate IFSx register for the source of the interrupt that the ISR handles. Otherwise, the ISR will be re-entered immediately after exiting the routine. If the ISR is coded in assembly language, it must be terminated using a RETFIE instruction to unstack the saved PC value, SRL value and old CPU priority level.

# 8.4.3 TRAP SERVICE ROUTINE (TSR)

A Trap Service Routine (TSR) is coded like an ISR, except that the appropriate trap status flag in the INTCON1 register must be cleared to avoid re-entry into the TSR.

## 8.4.4 INTERRUPT DISABLE

All user interrupts can be disabled using the following procedure:

- 1. Push the current SR value onto the software stack using the PUSH instruction.

- 2. Force the CPU to Priority Level 7 by inclusive ORing the value, 0Eh, with SRL.

To enable user interrupts, the POP instruction may be used to restore the previous SR value.

Only user interrupts with a priority level of 7 or less can be disabled. Trap sources (Levels 8-15) cannot be disabled.

The DISI instruction provides a convenient way to disable interrupts of Priority Levels 1-6 for a fixed period. Level 7 interrupt sources are not disabled by the DISI instruction.

# 9.1 CPU Clocking Scheme

The system clock source can be provided by one of four sources:

- Primary Oscillator (POSC) on the OSCI and OSCO pins

- Secondary Oscillator (SOSC) on the SOSCI and SOSCO pins

The PIC24FXXXXX family devices consist of two types of secondary oscillator:

- High-Power Secondary Oscillator

- Low-Power Secondary Oscillator

These can be selected by using the SOSCSEL (FOSC<5>) bit.

- Fast Internal RC (FRC) Oscillator:

- 8 MHz FRC Oscillator

- 500 kHz Lower Power FRC Oscillator

- Low-Power Internal RC (LPRC) Oscillator with two modes:

- High-Power/High-Accuracy mode

- Low-Power/Low-Accuracy mode

The Primary Oscillator and 8 MHz FRC sources have the option of using the internal 4x PLL. The frequency of the FRC clock source can optionally be reduced by the programmable clock divider. The selected clock source generates the processor and peripheral clock sources.

The processor clock source is divided by two to produce the internal instruction cycle clock, Fcy. In this document, the instruction cycle clock is also denoted by Fosc/2. The internal instruction cycle clock, Fosc/2, can be provided on the OSCO I/O pin for some operating modes of the Primary Oscillator.

# 9.2 Initial Configuration on POR

The oscillator source (and operating mode) that is used at a device Power-on Reset (POR) event is selected using Configuration bit settings. The Oscillator Configuration bit settings are located in the Configuration registers in the program memory (for more information, see Section 25.1 "Configuration Bits"). The Primary Oscillator Configuration bits, POSCMD<1:0> (FOSC<1:0>), and the Initial Oscillator Select Configuration bits, FNOSC<2:0> (FOSCSEL<2:0>), select the oscillator source that is used at a POR. The FRC Primary Oscillator with Postscaler (FRCDIV) is the default (unprogrammed) selection. The Secondary Oscillator, or one of the internal oscillators, may be chosen by programming these bit locations. The EC mode Frequency Range Configuration bits, POSCFREQ<1:0> (FOSC<4:3>), optimize power consumption when running in EC mode. The default configuration is "frequency range is greater than 8 MHz".

The Configuration bits allow users to choose between the various clock modes, shown in Table 9-1.

# 9.2.1 CLOCK SWITCHING MODE CONFIGURATION BITS

The FCKSM<1:0> Configuration bits (FOSC<7:6>) are used jointly to configure device clock switching and the FSCM. Clock switching is enabled only when FCKSM1 is programmed ('0'). The FSCM is enabled only when FCKSM<1:0> are both programmed ('00').

| Oscillator Mode                                      | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | Notes |

|------------------------------------------------------|-------------------|-------------|------------|-------|

| 8 MHz FRC Oscillator with Postscaler (FRCDIV)        | Internal          | 11          | 111        | 1, 2  |

| 500 kHz FRC Oscillator with Postscaler<br>(LPFRCDIV) | Internal          | 11          | 110        | 1     |

| Low-Power RC Oscillator (LPRC)                       | Internal          | 11          | 101        | 1     |

| Secondary (Timer1) Oscillator (SOSC)                 | Secondary         | 00          | 100        | 1     |

| Primary Oscillator (HS) with PLL Module (HSPLL)      | Primary           | 10          | 011        |       |

| Primary Oscillator (EC) with PLL Module (ECPLL)      | Primary           | 00          | 011        |       |

| Primary Oscillator (HS)                              | Primary           | 10          | 010        |       |

| Primary Oscillator (XT)                              | Primary           | 01          | 010        |       |

| Primary Oscillator (EC)                              | Primary           | 00          | 010        |       |

| 8 MHz FRC Oscillator with PLL Module (FRCPLL)        | Internal          | 11          | 001        | 1     |

| 8 MHz FRC Oscillator (FRC)                           | Internal          | 11          | 000        | 1     |

# TABLE 9-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

Note 1: The OSCO pin function is determined by the OSCIOFNC Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

| R/W-0         | U-0                                                                                                                  | R/W-0                                                                                                                                                                            | R/W-0                                                                                                 | R/W-0                                    | R/W-0            | R/W-0            | R/W-0     |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|------------------------------------------|------------------|------------------|-----------|--|--|

| ROEN          | _                                                                                                                    | ROSSLP                                                                                                                                                                           | ROSEL                                                                                                 | RODIV3                                   | RODIV2           | RODIV1           | RODIV0    |  |  |

| bit 15        |                                                                                                                      |                                                                                                                                                                                  |                                                                                                       |                                          |                  |                  | bit       |  |  |

| U-0           | U-0                                                                                                                  | U-0                                                                                                                                                                              | U-0                                                                                                   | U-0                                      | U-0              | U-0              | U-0       |  |  |

|               |                                                                                                                      |                                                                                                                                                                                  | _                                                                                                     | _                                        |                  | _                |           |  |  |

| bit 7         |                                                                                                                      |                                                                                                                                                                                  |                                                                                                       |                                          |                  |                  | bit       |  |  |

| Legend:       |                                                                                                                      |                                                                                                                                                                                  |                                                                                                       |                                          |                  |                  |           |  |  |

| R = Readable  | e bit                                                                                                                | W = Writable I                                                                                                                                                                   | oit                                                                                                   | U = Unimplem                             | nented bit, read | 1 as '0'         |           |  |  |

| -n = Value at | POR                                                                                                                  | '1' = Bit is set                                                                                                                                                                 |                                                                                                       | '0' = Bit is clea                        |                  | x = Bit is unkr  | iown      |  |  |

| bit 15        | 1 = Reference                                                                                                        | ence Oscillator<br>e Oscillator is e<br>e Oscillator is d                                                                                                                        | nabled on the                                                                                         |                                          |                  |                  |           |  |  |

| bit 14        | Unimplemen                                                                                                           | ted: Read as 'o                                                                                                                                                                  | )'                                                                                                    |                                          |                  |                  |           |  |  |

| bit 13        | ROSSLP: Reference Oscillator Output Stop in Sleep bit                                                                |                                                                                                                                                                                  |                                                                                                       |                                          |                  |                  |           |  |  |

|               |                                                                                                                      | e Oscillator con<br>e Oscillator is d                                                                                                                                            |                                                                                                       |                                          |                  |                  |           |  |  |

| bit 12        |                                                                                                                      | erence Oscillato                                                                                                                                                                 |                                                                                                       |                                          |                  |                  |           |  |  |

|               | 1 = Primary (<br>0 = System c                                                                                        | Oscillator is use<br>clock is used as                                                                                                                                            | d as the base the base cloc                                                                           | clock <sup>(1)</sup><br>k; base clock re | flects any cloc  | k switching of t | he device |  |  |

| bit 11-8      | 1111 = Base<br>1110 = Base<br>1101 = Base<br>1100 = Base                                                             | Reference Osi<br>clock value divi<br>clock value divi<br>clock value divi<br>clock value divi<br>clock value divi<br>clock value divi                                            | ded by 32,768<br>ded by 16,384<br>ded by 8,192<br>ded by 4,096<br>ded by 2,048                        | 3                                        |                  |                  |           |  |  |

|               | 1001 = Base<br>1000 = Base<br>0111 = Base<br>0110 = Base<br>0101 = Base<br>0100 = Base<br>0011 = Base<br>0010 = Base | clock value divi<br>clock value divi | ded by 512<br>ded by 256<br>ded by 128<br>ded by 64<br>ded by 32<br>ded by 16<br>ded by 8<br>ded by 4 |                                          |                  |                  |           |  |  |

# REGISTER 9-4: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

**Note 1:** The crystal oscillator must be enabled using the FOSC<2:0> bits; the crystal maintains the operation in Sleep mode.

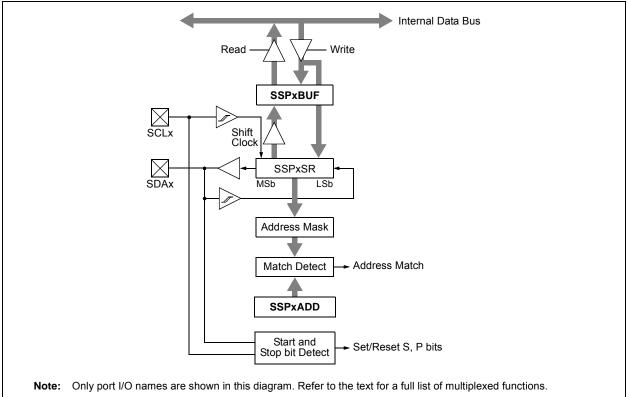

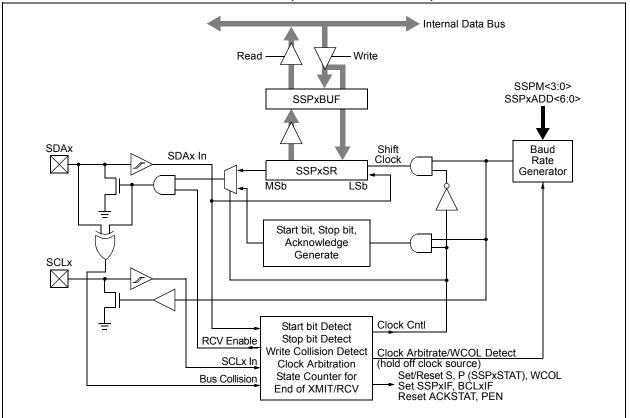

# FIGURE 14-4: MSSPx BLOCK DIAGRAM (I<sup>2</sup>C<sup>™</sup> MASTER MODE)

#### SSPxCON1: MSSPx CONTROL REGISTER 1 (I<sup>2</sup>C<sup>™</sup> MODE) REGISTER 14-4: U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 bit 15 bit 8 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 SSPM0<sup>(2)</sup> SSPOV SSPEN<sup>(1)</sup> CKP SSPM3<sup>(2)</sup> SSPM2(2) SSPM1<sup>(2)</sup> WCOL bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15-8 Unimplemented: Read as '0' bit 7 WCOL: Write Collision Detect bit In Master Transmit mode: 1 = A write to the SSPxBUF register was attempted while the I<sup>2</sup>C conditions were not valid for a transmission to be started (must be cleared in software) 0 = No collisionIn Slave Transmit mode: 1 = The SSPxBUF register is written while it is still transmitting the previous word (must be cleared in software) 0 = No collision In Receive mode (Master or Slave modes): This is a "don't care" bit. bit 6 SSPOV: Master Synchronous Serial Port Receive Overflow Indicator bit In Receive mode: 1 = A byte is received while the SSPxBUF register is still holding the previous byte (must be cleared in software) 0 = No overflow In Transmit mode: This is a "don't care" bit in Transmit mode. SSPEN: Master Synchronous Serial Port Enable bit<sup>(1)</sup> bit 5 1 = Enables the serial port and configures the SDAx and SCLx pins as the serial port pins 0 = Disables the serial port and configures these pins as I/O port pins bit 4 CKP: SCLx Release Control bit In Slave mode: 1 = Releases clock 0 = Holds clock low (clock stretch), used to ensure data setup time In Master mode: Unused in this mode. SSPM<3:0>: Master Synchronous Serial Port Mode Select bits<sup>(2)</sup> bit 3-0 1111 = $I^2C$ Slave mode, 10-bit address with Start and Stop bit interrupts enabled 1110 = $I^2C$ Slave mode, 7-bit address with Start and Stop bit interrupts enabled $1011 = I^2C$ Firmware Controlled Master mode (Slave Idle) 1000 = $I^2C$ Master mode, Clock = Fosc/(2 \* ([SSPxADD] + 1))<sup>(3)</sup> 0111 = $I^2C$ Slave mode, 10-bit address $0110 = I^2C$ Slave mode, 7-bit address Note 1: When enabled, the SDAx and SCLx pins must be configured as inputs.

- 2: Bit combinations not specifically listed here are either reserved or implemented in SPI mode only.

- 3: SSPxADD values of 0, 1 or 2 are not supported when the Baud Rate Generator is used with I<sup>2</sup>C mode.

'1' = Bit is set

# REGISTER 14-8: SSPxADD: MSSPx SLAVE ADDRESS/BAUD RATE GENERATOR REGISTER

| U-0                               | U-0   | U-0   | U-0   | U-0                                | U-0   | U-0   | U-0   |  |

|-----------------------------------|-------|-------|-------|------------------------------------|-------|-------|-------|--|

| —                                 | —     | —     |       | —                                  | _     | —     | _     |  |

| bit 15                            |       |       |       |                                    |       |       | bit 8 |  |

|                                   |       |       |       |                                    |       |       |       |  |

| R/W-0                             | R/W-0 | R/W-0 | R/W-0 | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |

| ADD7                              | ADD6  | ADD5  | ADD4  | ADD3                               | ADD2  | ADD1  | ADD0  |  |

| bit 7                             |       |       |       |                                    |       |       | bit 0 |  |

|                                   |       |       |       |                                    |       |       |       |  |

| Legend:                           |       |       |       |                                    |       |       |       |  |

| R = Readable bit W = Writable bit |       |       | bit   | U = Unimplemented bit, read as '0' |       |       |       |  |

'0' = Bit is cleared

x = Bit is unknown

bit 15-8 **Unimplemented:** Read as '0'

-n = Value at POR

bit 7-0

ADD<7:0>: Slave Address/Baud Rate Generator Value bits

SPI Master and I<sup>2</sup>C™ Master modes:

Reload value for the Baud Rate Generator. Clock period is (([SPxADD] + 1) \* 2)/Fosc.

I<sup>2</sup>C Slave modes:

Represents 7 or 8 bits of the slave address, depending on the addressing mode used:

7-Bit mode:

Address is ADD<7:1>; ADD<0> is ignored.

10-Bit LSb mode:

ADD<7:0> are the Least Significant bits of the address.

10-Bit MSb mode:

ADD<2:1> are the two Most Significant bits of the address; ADD<7:3> are always '11110' as a specification requirement; ADD<0> is ignored.

# REGISTER 14-9: SSPxMSK: I<sup>2</sup>C<sup>™</sup> SLAVE ADDRESS MASK REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-1               |

|-------|-------|-------|-------|-------|-------|-------|---------------------|

| MSK7  | MSK6  | MSK5  | MSK4  | MSK3  | MSK2  | MSK1  | MSK0 <sup>(1)</sup> |

| bit 7 |       |       |       |       |       |       | bit 0               |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 15-8 | Unimplemented: Read as '0'                              |

|----------|---------------------------------------------------------|

| bit 7-0  | MSK<7:0>: Slave Address Mask Select bits <sup>(1)</sup> |

|          | 1 = Masking of corresponding bit of SSPxADD is enabled  |

|          | 0 = Masking of corresponding bit of SSPxADD is disabled |

Note 1: MSK0 is not used as a mask bit in 7-bit addressing.

# 16.3 Calibration

The real-time crystal input can be calibrated using the periodic auto-adjust feature. When properly calibrated, the RTCC can provide an error of less than 3 seconds per month. This is accomplished by finding the number of error clock pulses and storing the value into the lower half of the RCFGCAL register. The 8-bit signed value, loaded into the lower half of RCFGCAL, is multiplied by four and will be either added or subtracted from the RTCC timer, once every minute. Refer to the steps below for RTCC calibration:

- 1. Using another timer resource on the device, the user must find the error of the 32.768 kHz crystal.

- 2. Once the error is known, it must be converted to the number of error clock pulses per minute.

- 3. a) If the oscillator is faster than ideal (negative result from Step 2), the RCFGCAL register value must be negative. This causes the specified number of clock pulses to be subtracted from the timer counter, once every minute.

b) If the oscillator is slower than ideal (positive result from Step 2), the RCFGCAL register value must be positive. This causes the specified number of clock pulses to be subtracted from the timer counter, once every minute.

# EQUATION 16-1:

| (Ideal Frequency <sup>†</sup> – Measured Frequency) * |  |

|-------------------------------------------------------|--|

| 60 = Clocks per Minute                                |  |

| † Ideal Frequency = 32,768 Hz                         |  |

Writes to the lower half of the RCFGCAL register should only occur when the timer is turned off, or immediately after the rising edge of the seconds pulse, except when SECONDS = 00, 15, 30 or 45. This is due to the auto-adjust of the RTCC at 15 second intervals.

**Note:** It is up to the user to include, in the error value, the initial error of the crystal: drift due to temperature and drift due to crystal aging.

# 16.4 Alarm

- Configurable from half second to one year

- Enabled using the ALRMEN bit (ALCFGRPT<15>)

- One-time alarm and repeat alarm options are available

# 16.4.1 CONFIGURING THE ALARM

The alarm feature is enabled using the ALRMEN bit. This bit is cleared when an alarm is issued. Writes to ALRMVAL should only take place when ALRMEN = 0.

As shown in Figure 16-2, the interval selection of the alarm is configured through the AMASKx bits (ALCFGRPT<13:10>). These bits determine which and how many digits of the alarm must match the clock value for the alarm to occur.

The alarm can also be configured to repeat based on a preconfigured interval. The amount of times this occurs, once the alarm is enabled, is stored in the ARPT<7:0> bits (ALCFGRPT<7:0>). When the value of the ARPTx bits equals 00h and the CHIME bit (ALCFGRPT<14>) is cleared, the repeat function is disabled, and only a single alarm will occur. The alarm can be repeated up to 255 times by loading ARPT<7:0> with FFh.

After each alarm is issued, the value of the ARPTx bits is decremented by one. Once the value has reached 00h, the alarm will be issued one last time, after which, the ALRMEN bit will be cleared automatically and the alarm will turn off.

Indefinite repetition of the alarm can occur if the CHIME bit = 1. Instead of the alarm being disabled when the value of the ARPTx bits reaches 00h, it rolls over to FFh and continues counting indefinitely while CHIME is set.

# 16.4.2 ALARM INTERRUPT

At every alarm event, an interrupt is generated. In addition, an alarm pulse output is provided that operates at half the frequency of the alarm. This output is completely synchronous to the RTCC clock and can be used as a Trigger clock to other peripherals.

Note: Changing any of the registers, other than the RCFGCAL and ALCFGRPT registers, and the CHIME bit while the alarm is enabled (ALRMEN = 1), can result in a false alarm event leading to a false alarm interrupt. To avoid a false alarm event, the timer and alarm values should only be changed while the alarm is disabled (ALRMEN = 0). It is recommended that the ALCFGRPT register and CHIME bit be changed when RTCSYNC = 0.

# REGISTER 17-5: CLCxGLSH: CLCx GATE LOGIC INPUT SELECT HIGH REGISTER (CONTINUED)

| bit 3 | G3D2T: Gate 3 Data Source 2 True Enable bit                  |

|-------|--------------------------------------------------------------|

|       | 1 = The Data Source 2 inverted signal is enabled for Gate 3  |

|       | 0 = The Data Source 2 inverted signal is disabled for Gate 3 |

| bit 2 | G3D2N: Gate 3 Data Source 2 Negated Enable bit               |

|       | 1 = The Data Source 2 inverted signal is enabled for Gate 3  |

|       | 0 = The Data Source 2 inverted signal is disabled for Gate 3 |

| bit 1 | G3D1T: Gate 3 Data Source 1 True Enable bit                  |

|       | 1 = The Data Source 1 inverted signal is enabled for Gate 3  |

|       | 0 = The Data Source 1 inverted signal is disabled for Gate 3 |

| bit 0 | G3D1N: Gate 3 Data Source 1 Negated Enable bit               |

|       | 1 = The Data Source 1 inverted signal is enabled for Gate 3  |

|       | 0 = The Data Source 1 inverted signal is disabled for Gate 3 |

# REGISTER 19-7: AD1CHITL: A/D SCAN COMPARE HIT REGISTER (LOW WORD)<sup>(1)</sup>

| R/W-0                 | R/W-0                     | R/W-0               | R/W-0                     | R/W-0                              | R/W-0          | R/W-0              | R/W-0                 |  |

|-----------------------|---------------------------|---------------------|---------------------------|------------------------------------|----------------|--------------------|-----------------------|--|

| CHH15                 | CHH14                     | CHH13               | CHH12                     | CHH11                              | CHH10          | CHH9               | CHH8 <sup>(2,3)</sup> |  |

| bit 15                |                           |                     |                           |                                    |                |                    | bit 8                 |  |

|                       |                           |                     |                           |                                    |                |                    |                       |  |

| R/W-0                 | R/W-0                     | R/W-0               | R/W-0                     | R/W-0                              | R/W-0          | R/W-0              | R/W-0                 |  |

| CHH7 <sup>(2,3)</sup> | CHH6 <sup>(2,3)</sup>     | CHH5 <sup>(2)</sup> | CHH4                      | CHH3                               | CHH2           | CHH1               | CHH0                  |  |

| bit 7                 |                           |                     |                           |                                    |                |                    | bit 0                 |  |

|                       |                           |                     |                           |                                    |                |                    |                       |  |

| Legend:               |                           |                     |                           |                                    |                |                    |                       |  |

| R = Readable          | e bit                     | W = Writable b      | pit                       | U = Unimplemented bit, read as '0' |                |                    |                       |  |

| -n = Value at POR     |                           | '1' = Bit is set    |                           | '0' = Bit is cle                   | ared           | x = Bit is unknown |                       |  |

|                       |                           |                     |                           |                                    |                |                    |                       |  |

| bit 15-0              | CHH<15:0>:                | A/D Compare H       | lit bits <sup>(2,3)</sup> |                                    |                |                    |                       |  |

|                       | <u>If CM&lt;1:0&gt; =</u> | <u>11:</u>          |                           |                                    |                |                    |                       |  |

|                       | 1 = A/D Res               | ult Buffer x has    | been written              | with data or a m                   | atch has occur | red                |                       |  |

0 = A/D Result Buffer x has not been written with data

For All Other Values of CM<1:0>:

1 = A match has occurred on A/D Result Channel x

0 = No match has occurred on A/D Result Channel x

## Note 1: Unimplemented channels are read as '0'.

2: The CHH<8:5> bits are not implemented in 20-pin devices.

**3:** The CHH<8:6> bits are not implemented in 28-pin devices.

## REGISTER 20-1: DACxCON: DACx CONTROL REGISTER (CONTINUED)

- bit 6-2 DACTSEL<4:0>: DACx Trigger Source Select bits

- 11101-11111 = Unused 11100 = CTMU 11011 = A/D 11010 = Comparator 3 11001 = Comparator 2 11000 = Comparator 1 10011 to 10111 = Unused 10010 = CLC2 output 10001 = CLC1 output 01100 to 10000 = Unused 01011 = Timer1 Sync output 01010 = External Interrupt 2 01001 = External Interrupt 1 01000 = External Interrupt 0 0011x = Unused 00101 = MCCP5 or SCCP5 Sync output 00100 = MCCP4 or SCCP4 Sync output 00011 = MCCP3 or SCCP3 Sync output 00010 = MCCP2 or SCCP2 Sync output 00001 = MCCP1 or SCCP1 Sync output 00000 = Unused DACREF<1:0>: DACx Reference Source Select bits 11 = Internal Band Gap Buffer 1 (BGBUF1)<sup>(1)</sup>

- 10 = AVDD

bit 1-0

- 01 = DVREF+

- 00 = Reference is not connected (lowest power but no DAC functionality)

- **Note 1:** BGBUF1 voltage is configured by BUFREF<1:0> (BUFCON0<1:0>).

| DC CHARACTERISTICS |       |                                                                                 | Standard Op        | •                  |            | 1.8V to 3.6V (PIC24F16KM204)<br>2.0V to 5.5V (PIC24FV16KM204)<br>-40°C $\leq$ TA $\leq$ +85°C for Industrial<br>-40°C $\leq$ TA $\leq$ +125°C for Extended |                                                                                                                           |  |

|--------------------|-------|---------------------------------------------------------------------------------|--------------------|--------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--|

| Param<br>No.       | Sym   | Characteristic                                                                  | Min                | Тур <sup>(1)</sup> | Мах        | Units                                                                                                                                                      | Conditions                                                                                                                |  |

|                    | VIL   | Input Low Voltage <sup>(4)</sup>                                                |                    |                    |            |                                                                                                                                                            |                                                                                                                           |  |

| DI10               |       | I/O Pins                                                                        | Vss                | _                  | 0.2 VDD    | V                                                                                                                                                          |                                                                                                                           |  |

| DI15               |       | MCLR                                                                            | Vss                | _                  | 0.2 VDD    | V                                                                                                                                                          |                                                                                                                           |  |

| DI16               |       | OSCI (XT mode)                                                                  | Vss                | —                  | 0.2 VDD    | V                                                                                                                                                          |                                                                                                                           |  |

| DI17               |       | OSCI (HS mode)                                                                  | Vss                | —                  | 0.2 VDD    | V                                                                                                                                                          |                                                                                                                           |  |

| DI18               |       | I/O Pins with I <sup>2</sup> C™ Buffer                                          | Vss                |                    | 0.3 VDD    | V                                                                                                                                                          | SMBus disabled                                                                                                            |  |

| DI19               |       | I/O Pins with SMBus Buffer                                                      | Vss                | —                  | 0.8        | V                                                                                                                                                          | SMBus enabled                                                                                                             |  |

|                    | Vih   | Input High Voltage <sup>(4,5)</sup>                                             |                    |                    |            |                                                                                                                                                            |                                                                                                                           |  |

| DI20               |       | I/O Pins:<br>with Analog Functions<br>Digital Only                              | 0.8 Vdd<br>0.8 Vdd | —                  | Vdd<br>Vdd | V<br>V                                                                                                                                                     |                                                                                                                           |  |

| DI25               |       | MCLR                                                                            | 0.8 Vdd            | _                  | Vdd        | V                                                                                                                                                          |                                                                                                                           |  |

| DI26               |       | OSCI (XT mode)                                                                  | 0.7 Vdd            | —                  | Vdd        | V                                                                                                                                                          |                                                                                                                           |  |

| DI27               |       | OSCI (HS mode)                                                                  | 0.7 Vdd            |                    | Vdd        | V                                                                                                                                                          |                                                                                                                           |  |

| DI28               |       | I/O Pins with I <sup>2</sup> C Buffer:<br>with Analog Functions<br>Digital Only | 0.7 Vdd<br>0.7 Vdd |                    | Vdd<br>Vdd | V<br>V                                                                                                                                                     |                                                                                                                           |  |

| DI29               |       | I/O Pins with SMBus                                                             | 2.1                | —                  | Vdd        | V                                                                                                                                                          | $2.5V \le V\text{PIN} \le V\text{DD}$                                                                                     |  |

| DI30               | ICNPU | CNx Pull-up Current                                                             | 50                 | 250                | 500        | μA                                                                                                                                                         | VDD = 3.3V, VPIN = VSS                                                                                                    |  |

| DI31               | IPU   | Maximum Load Current for                                                        |                    | —                  | 30         | μA                                                                                                                                                         | VDD = 2.0V                                                                                                                |  |

|                    |       | Digital High Detection<br>w/Internal Pull-up                                    | —                  | _                  | 1000       | μA                                                                                                                                                         | VDD = 3.3V                                                                                                                |  |