Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                      |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 37                                                                            |

| Program Memory Size        | 16KB (5.5K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 1K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5V                                                                       |

| Data Converters            | A/D 22x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

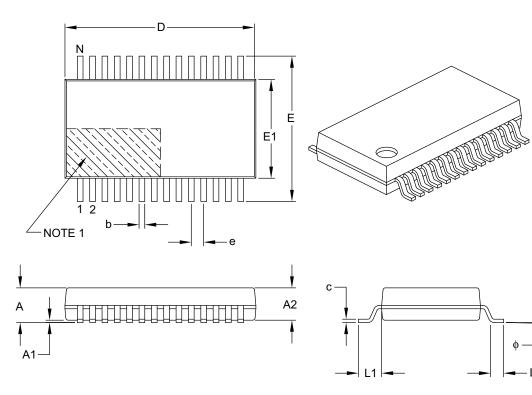

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 48-UFQFN Exposed Pad                                                          |

| Supplier Device Package    | 48-UQFN (6x6)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fv16km104-i-mv |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Pin Diagrams (Continued)

| 20-1     | Pin SPDIP/SSOP/SOIC       MCLR/RA5       1       28       AVDD         RA0       2       27       AVss         RA1       23       26       RB15         RB0       4       C25       RB14         RB1       5       24       RB13         RB2       6       23       RB12         RB3       7       22       RB11         Vss       8       21       RB10         RA3       10       C0       RA6 or Vbbcore         RA3       10       C0       RA7         RB4       111       18       RB9         RA4       112       17       RB8         Vob       13       16       RB7         RB5<       14       15       RB6 |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin      | Pin Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|          | PIC24FXXKMX02 PIC24FVXXKMX02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1        | MCLR/Vpp/RA5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2        | CVREF+/VREF+/ /AN0/ /CN2/RA0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3        | CVREF-/VREF-/AN1/CN3/RA1 CVREF-/VREF-/AN1/RA1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4        | PGED1/AN2/CTCMP/ULPWU/C1IND/ / / /CN4/RB0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5        | PGEC1/ / /AN3/C1INC/ / /CTED12/CN5/RB1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6        | / /AN4/C1INB/ / /U1RX/TCKIB/CTED13/CN6/RB2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 7        | /AN5/C1INA/ / /CN7/RB3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 8        | Vss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 9        | OSCI/CLKI/AN13/CN30/RA2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 10       | OSCO/CLKO/AN14/CN29/RA3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 11       | SOSCI/AN15/ / /CN1/RB4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 12       | SOSCO/SCLKI/AN16/PWRLCLK/ /CN0/RA4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 13       | VDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 14       | PGED3/AN17/ASDA1/ / /OC1E/CLCINA/CN27/RB5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 15       | PGEC3/AN18/ASCL1/ / /OC1F/CLCINB/CN24/RB6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 16       | AN19/U1TX/INT0/CN23/RB7 AN19/U1TX/ / /INT0/CN23/RB7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 17       | AN20/SCL1/U1CTS/C3OUT/OC1B/CTED10/CN22/RB8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 18       | AN21/SDA1/T1CK/U1RTS/U1BCLK/IC2/ /CLC10/CTED4/CN21/RB9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 19       | /IC1/ / /CTED3/CN9/RA7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 20       | /OC1A/CTED1/INT2/CN8/RA6 VCAP OR VDDCORE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 21<br>22 | PGED2/SDI1/ /OC1C/CTED11/CN16/RB10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 22<br>23 | PGEC2/SCK1/OC2A/CTED9/CN15/RB11           /AN12/HLVDIN/         /           /AN12/HLVDIN/         /           /B12         //                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 24       | / /AN11/SD01/OCFB/ /OC1D/CTPLS/CN13/RB13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 25       | /CVREF/ / /AN10/ / /C1OUT/OCFA/CTED5/INT1/CN12/RB14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 26       | / /AN9/ /REFO/SS1/TCKIA/CTED6/CN11/RB15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 27       | Vss/AVss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 28       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

Legend: Values in indicate pin function differences between PIC24F(V)XXKM202 and PIC24F(V)XXKM102 devices.

#### 1.1.4 EASY MIGRATION

The PIC24FV16KM204 family devices have two variants. The KM20X variant provides the full feature set of the device, while the KM10X offers a reduced peripheral set, allowing for the balance of features and cost (refer to Table 1-1). Both variants allow for a smooth migration path as applications grow and evolve.

The consistent pinout scheme used throughout the entire family also helps in migrating to the next larger device. This is true when moving between devices with the same pin count, different die variants, or even moving from 20-pin or 28-pin devices to 44-pin/48-pin devices.

The PIC24F family is pin compatible with devices in the dsPIC33 family, and shares some compatibility with the pinout schema for PIC18 and dsPIC30. This extends the ability of applications to grow from the relatively simple to the powerful and complex, yet still selecting a Microchip device.

#### 1.2 Other Special Features

- Communications: The PIC24FV16KM204 family incorporates a range of serial communication peripherals to handle a range of application requirements. There is an MSSP module which implements both SPI and I<sup>2</sup>C™ protocols, and supports both Master and Slave modes of operation for each. Devices also include one of two UARTs with built-in IrDA<sup>®</sup> encoders/decoders.

- Analog Features: Select members of the PIC24FV16KM204 family include two 8-bit Digital-to-Analog Converters which offer support in Idle mode, and left and right justified input data, as well as up to two operational amplifiers with selectable power and speed modes.

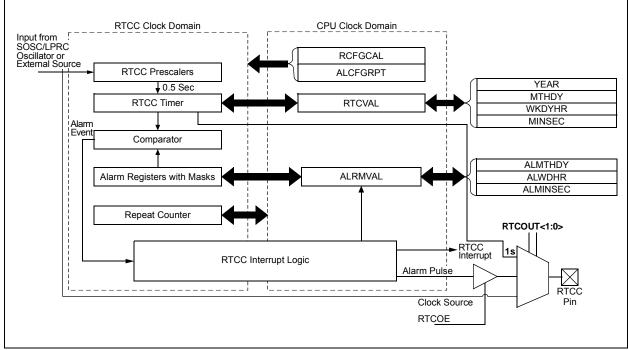

- Real-Time Clock/Calendar (RTCC): This module implements a full-featured clock and calendar with alarm functions in hardware, freeing up timer resources and program memory space for use of the core application.

- 12-Bit A/D Converter: This module incorporates programmable acquisition time, allowing for a channel to be selected and a conversion to be initiated without waiting for a sampling period, and faster sampling speed. The 16-deep result buffer can be used either in Sleep, to reduce power, or in Active mode to improve throughput.

- Charge Time Measurement Unit (CTMU) Interface: The PIC24FV16KM204 family includes the new CTMU interface module, which can be used for capacitive touch sensing, proximity sensing, and also for precision time measurement and pulse generation. The CTMU can also be connected to the operational amplifiers to provide active guarding, which provides increased robustness in the presence of noise in capacitive touch applications.

#### 1.3 Details on Individual Family Members

Devices in the PIC24FV16KM204 family are available in 20-pin, 28-pin, 44-pin and 48-pin packages. The general block diagram for all devices is shown in Figure 1-1.

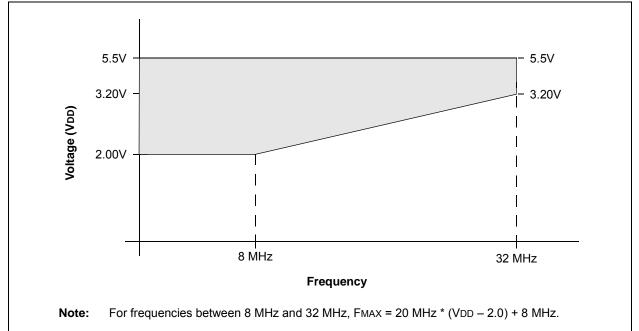

Members of the PIC24FV16KM204 family are available as both standard and high-voltage devices. High-voltage devices, designated with an "FV" in the part number (such as PIC24FV16KM204), accommodate an operating VDD range of 2.0V to 5.5V and have an on-board voltage regulator that powers the core. Peripherals operate at VDD.

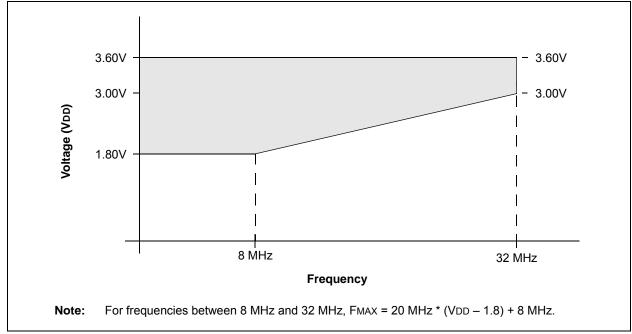

Standard devices, designated by "F" (such as PIC24F16KM204), function over a lower VDD range of 1.8V to 3.6V. These parts do not have an internal regulator, and both the core and peripherals operate directly from VDD.

The PIC24FV16KM204 family may be thought of as two different device groups, both offering slightly different sets of features. These differ from each other in multiple ways:

- · The size of the Flash program memory

- The number of external analog channels available

- The number of Digital-to-Analog Converters

- · The number of operational amplifiers

- The number of analog comparators

- The presence of a Real-Time Clock and Calendar (RTCC)

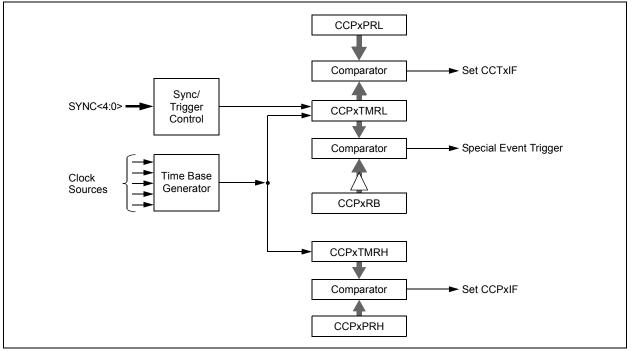

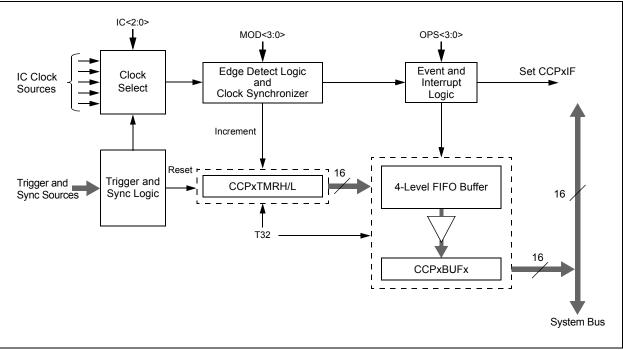

- The number and type of CCP modules (i.e., MCCP vs. SCCP)

- The number of serial communication modules (both MSSPs and UARTs)

- The number of Configurable Logic Cell (CLC) modules

The general differences between the different sub-families are shown in Table 1-1 and Table 1-2.

A list of the pin features available on the PIC24FV16KM204 family devices, sorted by function, is provided in Table 1-5.

| TABLE 1-1: | DEVICE FEATURES FOR THE PIC24F16KM204 FAMILY |

|------------|----------------------------------------------|

|------------|----------------------------------------------|

| TABLE 1-1: DEVICE FEATURES FO                    | R THE PIC24F16                                                                                                                                      |                    | •                      |                        |  |  |  |

|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------------------------|------------------------|--|--|--|

| Features                                         | PIC24F16KM204                                                                                                                                       | PIC24F08KM204      | PIC24F16KM202          | PIC24F08KM202          |  |  |  |

| Operating Frequency                              |                                                                                                                                                     | DC-3               | 2 MHz                  |                        |  |  |  |

| Program Memory (bytes)                           | 16K                                                                                                                                                 | 8K                 | 16K                    | 8K                     |  |  |  |

| Program Memory (instructions)                    | 5632                                                                                                                                                | 2816               | 5632                   | 2816                   |  |  |  |

| Data Memory (bytes)                              |                                                                                                                                                     | 20                 | )48                    |                        |  |  |  |

| Data EEPROM Memory (bytes)                       |                                                                                                                                                     | 5                  | 12                     |                        |  |  |  |

| Interrupt Sources (soft vectors/NMI traps)       |                                                                                                                                                     | 40 (               | 36/4)                  |                        |  |  |  |

| Voltage Range                                    |                                                                                                                                                     | 1.8-               | 3.6V                   |                        |  |  |  |

| I/O Ports                                        | PORTA<<br>PORTB<<br>PORTC                                                                                                                           | :15:0>             | -                      | RTA<7:0><br>RTB<15:0>  |  |  |  |

| Total I/O Pins                                   | 38                                                                                                                                                  |                    |                        | 24                     |  |  |  |

| Timers                                           | (One 16-bit timer, f                                                                                                                                |                    | l1<br>Ps with up to tv | vo 16/32 timers each)  |  |  |  |

| Capture/Compare/PWM modules<br>MCCP<br>SCCP      | 3<br>2                                                                                                                                              |                    |                        |                        |  |  |  |

| Serial Communications<br>MSSP<br>UART            |                                                                                                                                                     |                    | 2<br>2                 |                        |  |  |  |

| Input Change Notification Interrupt              | 37                                                                                                                                                  |                    | 23                     |                        |  |  |  |

| 12-Bit Analog-to-Digital Module (input channels) | 22                                                                                                                                                  | 22                 | 19                     | 19                     |  |  |  |

| Analog Comparators                               | 3                                                                                                                                                   |                    |                        |                        |  |  |  |

| 8-Bit Digital-to-Analog Converters               | 2                                                                                                                                                   |                    |                        |                        |  |  |  |

| Operational Amplifiers                           | 2                                                                                                                                                   |                    |                        |                        |  |  |  |

| Charge Time Measurement Unit (CTMU)              |                                                                                                                                                     | Y                  | es                     |                        |  |  |  |

| Real-Time Clock and Calendar (RTCC)              | Yes                                                                                                                                                 |                    |                        |                        |  |  |  |

| Configurable Logic Cell (CLC)                    |                                                                                                                                                     |                    | 2                      |                        |  |  |  |

| Resets (and delays)                              | POR, BOR, RESET Instruction, MCLR, WDT, Illegal Opcode,<br>REPEAT Instruction, Hardware Traps, Configuration Word Mismatch<br>(PWRT, OST, PLL Lock) |                    |                        |                        |  |  |  |

| Instruction Set                                  | 76 Base Inst                                                                                                                                        | ructions, Multiple | e Addressing N         | ng Mode Variations     |  |  |  |

| Packages                                         | 44-Pin QFI<br>48-Pin L                                                                                                                              |                    |                        | 28-Pin<br>SOP/SOIC/QFN |  |  |  |

NOTES:

#### TABLE 4-25: A/D REGISTER MAP

| File Name | -25:<br>Addr. | Bit 15  | Bit 14                                                                                   | Bit 13  | Bit 12  | Bit 11   | Bit 10       | Bit 9      | Bit 8                 | Bit 7                 | Bit 6                 | Bit 5                 | Bit 4                  | Bit 3                  | Bit 2   | Bit 1   | Bit 0   | All    |

|-----------|---------------|---------|------------------------------------------------------------------------------------------|---------|---------|----------|--------------|------------|-----------------------|-----------------------|-----------------------|-----------------------|------------------------|------------------------|---------|---------|---------|--------|

|           |               | 2.1.10  |                                                                                          | 2       | 2.4.12  | 2        | 20.10        | 2          | 2                     |                       | 2                     | 2                     |                        | 2                      |         |         | 2.10    | Resets |

| ADC1BUF0  | 300h          |         | A/D Data Buffer 0/Threshold for Channel 0/Threshold for Channel 0 & 12 in Window Compare |         |         |          |              |            |                       |                       |                       | xxxx                  |                        |                        |         |         |         |        |

| ADC1BUF1  | 302h          |         |                                                                                          |         |         | A/D Da   | ata Buffer 1 | /Threshold | for Channel 1/        | Threshold for         | Channel 1 & 1         | 3 in Window           | Compare                |                        |         |         |         | xxxx   |

| ADC1BUF2  | 304h          |         |                                                                                          |         |         | A/D Da   | ata Buffer 2 | /Threshold | for Channel 2/        | Threshold for         | Channel 2 & 1         | 4 in Window           | Compare                |                        |         |         |         | XXXX   |

| ADC1BUF3  | 306h          |         |                                                                                          |         |         | A/D Da   | ata Buffer 3 | /Threshold | for Channel 3/        | Threshold for         | Channel 3 & 1         | 5 in Window           | Compare                |                        |         |         |         | XXXX   |

| ADC1BUF4  | 308h          |         |                                                                                          |         |         | A/D Da   | ata Buffer 4 | /Threshold | for Channel 4/        | Threshold for         | Channel 4 & 1         | 6 in Window           | Compare                |                        |         |         |         | xxxx   |

| ADC1BUF5  | 30Ah          |         |                                                                                          |         |         | A/D Da   | ata Buffer 5 | /Threshold | for Channel 5/        | Threshold for         | Channel 5 & 1         | 7 in Window           | Compare                |                        |         |         |         | xxxx   |

| ADC1BUF6  | 30Ch          |         |                                                                                          |         |         | A/D Da   | ata Buffer 6 | /Threshold | for Channel 6/        | Threshold for         | Channel 6 & 1         | 8 in Window           | Compare                |                        |         |         |         | xxxx   |

| ADC1BUF7  | 30Eh          |         |                                                                                          |         |         | A/D Da   | ata Buffer 7 | /Threshold | for Channel 7/        | Threshold for         | Channel 7 & 1         | 9 in Window           | Compare                |                        |         |         |         | xxxx   |

| ADC1BUF8  | 310h          |         |                                                                                          |         |         | A/D Da   | ata Buffer 8 | /Threshold | for Channel 8/        | Threshold for         | Channel 8 & 2         | 0 in Window           | Compare                |                        |         |         |         | xxxx   |

| ADC1BUF9  | 312h          |         |                                                                                          |         |         | A/D Da   | ata Buffer 9 | /Threshold | for Channel 9/        | Threshold for         | Channel 9 & 2         | 1 in Window           | Compare                |                        |         |         |         | xxxx   |

| ADC1BUF10 | 314h          |         |                                                                                          |         |         | A/D Data | a Buffer 10/ | Threshold  | for Channel 10        | /Threshold for        | r Channel 10 &        | 22 in Window          | w Compare              |                        |         |         |         | xxxx   |

| ADC1BUF11 | 316h          |         |                                                                                          |         |         | A/D Dat  | a Buffer 11/ | Threshold  | for Channel 11        | /Threshold for        | Channel 11 &          | 23 in Window          | v Compare              |                        |         |         |         | xxxx   |

| ADC1BUF12 | 318h          |         |                                                                                          |         |         | A/D Dat  | a Buffer 12  | /Threshold | for Channel 12        | 2/Threshold fo        | r Channel 0 &         | 12 in Window          | v Compare              |                        |         |         |         | xxxx   |

| ADC1BUF13 | 31Ah          |         |                                                                                          |         |         | A/D Dat  | a Buffer 13  | /Threshold | for Channel 13        | 3/Threshold fo        | r Channel 1 &         | 13 in Window          | v Compare              |                        |         |         |         | xxxx   |

| ADC1BUF14 | 31Ch          |         |                                                                                          |         |         | A/D Dat  | a Buffer 14  | /Threshold | for Channel 14        | 4/Threshold fo        | r Channel 2 &         | 14 in Window          | v Compare              |                        |         |         |         | xxxx   |

| ADC1BUF15 | 31Eh          |         |                                                                                          |         |         | A/D Dat  | a Buffer 15  | /Threshold | for Channel 1         | 5/Threshold fo        | r Channel 3 &         | 15 in Window          | v Compare              |                        |         |         |         | xxxx   |

| ADC1BUF16 | 320h          |         |                                                                                          |         |         | A/D Dat  | a Buffer 16  | /Threshold | for Channel 1         | 6/Threshold fo        | r Channel 4 &         | 16 in Window          | v Compare              |                        |         |         |         | xxxx   |

| ADC1BUF17 | 322h          |         |                                                                                          |         |         | A/D Dat  | a Buffer 17  | /Threshold | for Channel 1         | 7/Threshold fo        | r Channel 5 &         | 17 in Window          | v Compare              |                        |         |         |         | xxxx   |

| ADC1BUF18 | 324h          |         |                                                                                          |         |         | A/D Dat  | a Buffer 18  | /Threshold | for Channel 18        | 8/Threshold fo        | r Channel 6 &         | 18 in Window          | v Compare              |                        |         |         |         | xxxx   |

| ADC1BUF19 | 326h          |         |                                                                                          |         |         | A/D Dat  | a Buffer 19  | /Threshold | for Channel 19        | 9/Threshold fo        | r Channel 7 &         | 19 in Window          | v Compare              |                        |         |         |         | xxxx   |

| ADC1BUF20 | 328h          |         |                                                                                          |         |         | A/D Dat  | a Buffer 20  | /Threshold | for Channel 20        | 0/Threshold fo        | r Channel 8 &         | 20 in Window          | v Compare              |                        |         |         |         | xxxx   |

| ADC1BUF21 | 32Ah          |         |                                                                                          |         |         | A/D Dat  | a Buffer 21  | /Threshold | for Channel 2         | 1/Threshold fo        | r Channel 9 &         | 21 in Window          | v Compare              |                        |         |         |         | xxxx   |

| ADC1BUF22 | 32Ch          |         |                                                                                          |         |         | A/D Data | a Buffer 22/ | Threshold  | for Channel 22        | 2/Threshold for       | r Channel 10 &        | 22 in Window          | w Compare              |                        |         |         |         | xxxx   |

| ADC1BUF23 | 32Eh          |         |                                                                                          |         |         | A/D Data | a Buffer 23/ | Threshold  | for Channel 23        | 3/Threshold for       | r Channel 11 &        | 23 in Window          | w Compare              |                        |         |         |         | xxxx   |

| AD1CON1   | 340h          | ADON    | _                                                                                        | ADSIDL  | _       | _        | MODE12       | FORM1      | FORM0                 | SSRC3                 | SSRC2                 | SSRC1                 | SSRC0                  | _                      | ASAM    | SAMP    | DONE    | 0000   |

| AD1CON2   | 342h          | PVCFG1  | PVCFG0                                                                                   | NVCFG0  | _       | BUFREGEN | CSCNA        | _          | _                     | BUFS                  | SMPI4                 | SMPI3                 | SMPI2                  | SMPI1                  | SMPI0   | BUFM    | ALTS    | 0000   |

| AD1CON3   | 344h          | ADRC    | EXTSAM                                                                                   |         | SAMC4   | SAMC3    | SAMC2        | SAMC1      | SAMC0                 | ADCS7                 | ADCS6                 | ADCS5                 | ADCS4                  | ADCS3                  | ADCS2   | ADCS1   | ADCS0   | 0000   |

| AD1CHS    | 348h          | CH0NB2  | CH0NB1                                                                                   | CH0NB0  | CH0SB4  | CH0SB3   | CH0SB2       | CH0SB1     | CH0SB0                | CH0NA2                | CH0NA1                | CH0NA0                | CH0SA4                 | CH0SA3                 | CH0SA2  | CH0SA1  | CH0SA0  | 0000   |

| AD1CSSH   | 34Eh          | _       | CSS30                                                                                    | CSS29   | CSS28   | CSS27    | CSS26        | _          | _                     | CSS23                 | CSS22                 | CSS21                 | CSS20 <sup>(1)</sup>   | CSS19 <sup>(1)</sup>   | CSS18   | CSS17   | CSS16   | 0000   |

| AD1CSSL   | 350h          | CSS15   | CSS14                                                                                    | CSS13   | CSS12   | CSS11    | CSS10        | CSS9       | CSS8 <sup>(1,2)</sup> | CSS7 <sup>(1,2)</sup> | CSS6 <sup>(1,2)</sup> | CSS5 <sup>(1)</sup>   | CSS4                   | CSS3                   | CSS2    | CSS1    | CSS0    | 0000   |

| AD1CON5   | 354h          | ASEN    | LPEN                                                                                     | CTMREQ  | BGREQ   | r        | _            | ASINT1     | ASINT0                | _                     | _                     | —                     | _                      | WM1                    | WM0     | CM1     | CM0     | 0000   |

| AD1CHITH  | 356h          | _       | —                                                                                        | —       | —       | _        | _            | —          | —                     | CHH23                 | CHH22                 | CHH21                 | CHH20 <sup>(1)</sup>   | CHH19 <sup>(1)</sup>   | CHH18   | CHH17   | CHH16   | 0000   |

| AD1CHITL  | 358h          | CHH15   | CHH14                                                                                    | CHH13   | CHH12   | CHH11    | CHH10        | CHH9       | CHH8 <sup>(1,2)</sup> | CHH7 <sup>(1,2)</sup> | CHH6 <sup>(1,2)</sup> | CHH5 <sup>(1)</sup>   | CHH4                   | CHH3                   | CHH2    | CHH1    | CHH0    | 0000   |

| AD1CTMENH | 360h          | _       | —                                                                                        | —       | _       | _        | _            | _          | _                     | CTMEN23               | CTMEN22               | CTMEN21               | CTMEN20 <sup>(1)</sup> | CTMEN19 <sup>(1)</sup> | CTMEN18 | CTMEN17 | CTMEN16 | 0000   |

| AD1CTMENL | 362h          | CTMEN15 | CTMEN14                                                                                  | CTMEN13 | CTMEN12 | CTMEN11  | CTMEN10      | CTMEN9     | CTMEN8((1,2)          | CTMEN7(1,2)           | CTMEN6(1,2)           | CTMEN5 <sup>(1)</sup> | CTMEN4                 | CTMEN3                 | CTMEN2  | CTMEN1  | CTMEN0  | 0000   |

$\label{eq:Legend: Legend: Legend: u = unchanged, --= unimplemented, q = value depends on condition, r = reserved.$

Note 1: These bits are not implemented in 20-pin devices.

2: These bits are not implemented in 28-pin devices.

#### 5.2 RTSP Operation

The PIC24F Flash program memory array is organized into rows of 32 instructions or 96 bytes. RTSP allows the user to erase blocks of 1 row, 2 rows and 4 rows (32, 64 and 128 instructions) at a time, and to program one row at a time. It is also possible to program single words.

The 1-row (96 bytes), 2-row (192 bytes) and 4-row (384 bytes) erase blocks, and single row write block (96 bytes) are edge-aligned, from the beginning of program memory.

When data is written to program memory using TBLWT instructions, the data is not written directly to memory. Instead, data written using Table Writes is stored in holding latches until the programming sequence is executed.

Any number of TBLWT instructions can be executed and a write will be successfully performed. However, 32 TBLWT instructions are required to write the full row of memory.

The basic sequence for RTSP programming is to set up a Table Pointer, then do a series of TBLWT instructions to load the buffers. Programming is performed by setting the control bits in the NVMCON register.

Data can be loaded in any order and the holding registers can be written to multiple times before performing a write operation. Subsequent writes, however, will wipe out any previous writes.

| Note: | Writing         | to | а | location | multiple | times, |

|-------|-----------------|----|---|----------|----------|--------|

|       | without erasing |    |   |          | recommer | nded.  |

All of the Table Write operations are single-word writes (two instruction cycles), because only the buffers are written. A programming cycle is required for programming each row.

#### 5.3 Enhanced In-Circuit Serial Programming

Enhanced ICSP uses an on-board bootloader, known as the Program Executive (PE), to manage the programming process. Using an SPI data frame format, the Program Executive can erase, program and verify program memory. For more information on Enhanced ICSP, see the device programming specification.

#### 5.4 Control Registers

There are two SFRs used to read and write the program Flash memory: NVMCON and NVMKEY.

The NVMCON register (Register 5-1) controls the blocks that need to be erased, which memory type is to be programmed and when the programming cycle starts.

NVMKEY is a write-only register that is used for write protection. To start a programming or erase sequence, the user must consecutively write 55h and AAh to the NVMKEY register. Refer to **Section 5.5 "Programming Operations"** for further details.

#### 5.5 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. During a programming or erase operation, the processor stalls (waits) until the operation is finished. Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished. **REGISTER 7-1:**

RCON: RESET CONTROL REGISTER<sup>(1)</sup>

| R/W-0, H   | S R/W-0, HS                    | R/W-0                 | R/W-0                | U-0                  | U-0                                 | R/W-0             | R/W-0          |

|------------|--------------------------------|-----------------------|----------------------|----------------------|-------------------------------------|-------------------|----------------|

| TRAPR      |                                | SBOREN                | RETEN <sup>(3)</sup> | _                    | _                                   | СМ                | PMSLP          |

| bit 15     |                                |                       |                      |                      |                                     |                   | bit 8          |

|            |                                |                       |                      |                      |                                     |                   |                |

| R/W-0, H   | S R/W-0, HS                    | R/W-0, HS             | R/W-0, HS            | R/W-0, HS            | R/W-0, HS                           | R/W-1, HS         | R/W-1, HS      |

| EXTR       | SWR                            | SWDTEN <sup>(2)</sup> | WDTO                 | SLEEP                | IDLE                                | BOR               | POR            |

| bit 7      |                                |                       |                      |                      |                                     |                   | bit C          |

|            |                                |                       |                      |                      |                                     |                   |                |

| Legend:    |                                | HS = Hardwar          | e Settable bit       |                      |                                     |                   |                |

| R = Read   | able bit                       | W = Writable t        | pit                  | U = Unimplen         | nented bit, read                    | as '0'            |                |

| -n = Value | e at POR                       | '1' = Bit is set      |                      | '0' = Bit is cle     | ared                                | x = Bit is unkn   | own            |

|            |                                |                       |                      |                      |                                     |                   |                |

| bit 15     | -                              | Reset Flag bit        |                      |                      |                                     |                   |                |

|            | •                              | onflict Reset has     |                      |                      |                                     |                   |                |

| 1.11.4.4   |                                | onflict Reset has     |                      |                      | <b>E</b> 1                          |                   |                |

| bit 14     |                                | gal Opcode or l       |                      |                      | r Flag bit<br>or Uninitialized V    | / register used   | aa an Addraaa  |

|            |                                | aused a Reset         | on, an illegal a     | duress mode c        |                                     | v register used   | as an Address  |

|            |                                | opcode or Unir        | nitialized W Re      | set has not oc       | curred                              |                   |                |

| bit 13     | SBOREN: So                     | oftware Enable/D      | Disable of BOF       | R bit                |                                     |                   |                |

|            | 1 = BOR is tu                  | rned on in softw      | are                  |                      |                                     |                   |                |

|            |                                | rned off in softw     |                      |                      |                                     |                   |                |

| bit 12     |                                | ention Sleep Mo       |                      |                      |                                     |                   |                |

|            |                                |                       |                      |                      | Regulator (RETR<br>ge Regulator (VF |                   |                |

| bit 11-10  | -                              | ted: Read as '0       |                      |                      |                                     |                   |                |

| bit 9      | -                              | ation Word Misr       |                      | lag bit              |                                     |                   |                |

|            | -                              | Iration Word Mis      |                      | -                    |                                     |                   |                |

|            | 0 = A Configu                  | ration Word Mis       | match Reset          | has not occurre      | ed                                  |                   |                |

| bit 8      | PMSLP: Prog                    | gram Memory Po        | ower During S        | leep bit             |                                     |                   |                |

|            |                                | memory bias vo        |                      |                      |                                     |                   |                |

|            | 0 = Program<br>Standby         |                       | oltage is pow        | ered down du         | iring Sleep and                     | the voltage re    | gulator enters |

| bit 7      | •                              | nal Reset (MCLF       | R) Pin hit           |                      |                                     |                   |                |

| bit i      |                                | Clear (pin) Rese      |                      | d                    |                                     |                   |                |

|            |                                | Clear (pin) Rese      |                      |                      |                                     |                   |                |

| bit 6      | SWR: Softwa                    | re reset (Instru      | uction) Flag bit     | t                    |                                     |                   |                |

|            |                                | instruction has t     |                      |                      |                                     |                   |                |

|            |                                | instruction has r     |                      |                      |                                     |                   |                |

| bit 5      |                                | oftware Enable/[      | Disable of WD        | l bit <sup>(2)</sup> |                                     |                   |                |

|            | 1 = WDT is ei<br>0 = WDT is di |                       |                      |                      |                                     |                   |                |

|            |                                |                       |                      |                      | <b>-</b>                            |                   |                |

| Note 1:    | All of the Reset               | •                     | be set or clear      | ed in software.      | Setting one of the                  | nese bits in soft | ware does not  |

| 2:         | If the FWDTEN                  |                       | tion bits are '1     | 1' (upprogram        | med) the WDT i                      | is alwavs enabl   | ed renardless  |

| <b>_</b> . | of the SWDTEN                  |                       |                      |                      |                                     | ie amayo chabi    |                |

| -          |                                |                       |                      |                      |                                     |                   |                |

#### 3: This is implemented on PIC24FV16KMXXX parts only; not used on PIC24F16KMXXX devices.

### **REGISTER 7-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

| bit 4 | WDTO: Watchdog Timer Time-out Flag bit<br>1 = WDT time-out has occurred<br>0 = WDT time-out has not occurred                                           |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3 | SLEEP: Wake-up from Sleep Flag bit<br>1 = Device has been in Sleep mode<br>0 = Device has not been in Sleep mode                                       |

| bit 2 | IDLE: Wake-up from Idle Flag bit<br>1 = Device has been in Idle mode<br>0 = Device has not been in Idle mode                                           |

| bit 1 | <b>BOR:</b> Brown-out Reset Flag bit<br>1 = A Brown-out Reset has occurred (the BOR is also set after a POR)<br>0 = A Brown-out Reset has not occurred |

| bit 0 | <b>POR:</b> Power-on Reset Flag bit<br>1 = A Power-on Reset has occurred<br>0 = A Power-on Reset has not occurred                                      |

|       |                                                                                                                                                        |

- **Note 1:** All of the Reset status bits may be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the FWDTEN<1:0> Configuration bits are '11' (unprogrammed), the WDT is always enabled regardless of the SWDTEN bit setting.

- 3: This is implemented on PIC24FV16KMXXX parts only; not used on PIC24F16KMXXX devices.

#### TABLE 7-1: RESET FLAG BIT OPERATION

| Flag Bit          | Setting Event                                     | Clearing Event          |

|-------------------|---------------------------------------------------|-------------------------|

| TRAPR (RCON<15>)  | Trap Conflict Event                               | POR                     |

| IOPUWR (RCON<14>) | Illegal Opcode or Uninitialized W Register Access | POR                     |

| CM (RCON<9>)      | Configuration Mismatch Reset                      | POR                     |

| EXTR (RCON<7>)    | MCLR Reset                                        | POR                     |

| SWR (RCON<6>)     | RESET Instruction                                 | POR                     |

| WDTO (RCON<4>)    | WDT Time-out                                      | PWRSAV Instruction, POR |

| SLEEP (RCON<3>)   | PWRSAV #SLEEP Instruction                         | POR                     |

| IDLE (RCON<2>)    | PWRSAV #IDLE Instruction                          | POR                     |

| BOR (RCON<1>)     | POR, BOR                                          | —                       |

| POR (RCON<0>)     | POR                                               | —                       |

Note: All Reset flag bits may be set or cleared by the user software.

#### REGISTER 8-31: IPC18: INTERRUPT PRIORITY CONTROL REGISTER 18

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0     | U-0     | U-0     |

|---------|-----|-----|-----|-----|---------|---------|---------|

| _       | —   | —   | —   | —   | —       | —       | —       |

| bit 15  |     | •   |     |     | •       |         | bit 8   |

|         |     |     |     |     |         |         |         |

| U-0     | U-0 | U-0 | U-0 | U-0 | R/W-1   | R/W-0   | R/W-0   |

| _       | —   | —   | —   | —   | HLVDIP2 | HLVDIP1 | HLVDIP0 |

| bit 7   |     |     |     |     |         |         | bit 0   |

|         |     |     |     |     |         |         |         |

| Logondi |     |     |     |     |         |         |         |

| Legend: |  |

|---------|--|

|---------|--|

bit 2-0

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

#### bit 15-3 Unimplemented: Read as '0'

HLVDIP<2:0>: High/Low-Voltage Detect Interrupt Priority bits

- 111 = Interrupt is Priority 7 (highest priority interrupt)

- •

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

| U-0       U-0       U-0       U-0       U-0       U-0       U-0       U-0         -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | REGISTER | 9-2: CLKL                                                                                                                                                                                                                                                        | DIV: CLOCK L                                                                                                                                                                                                                                                                                                                   |                                                                                                                       | GISTER               |                  |                  |        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|----------------------|------------------|------------------|--------|

| bit 15       bit         U-0       U-0       U-0       U-0       U-0       U-0                  bit       7                                                                                                 <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | R/W-0    | R/W-0                                                                                                                                                                                                                                                            | R/W-1                                                                                                                                                                                                                                                                                                                          | R/W-1                                                                                                                 |                      | R/W-0            | R/W-0            | R/W-1  |

| U-0       U-0       U-0       U-0       U-0       U-0       U-0       U-0         -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ROI      | DOZE2                                                                                                                                                                                                                                                            | DOZE1                                                                                                                                                                                                                                                                                                                          | DOZE0                                                                                                                 | DOZEN <sup>(1)</sup> | RCDIV2           | RCDIV1           | RCDIV0 |