#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

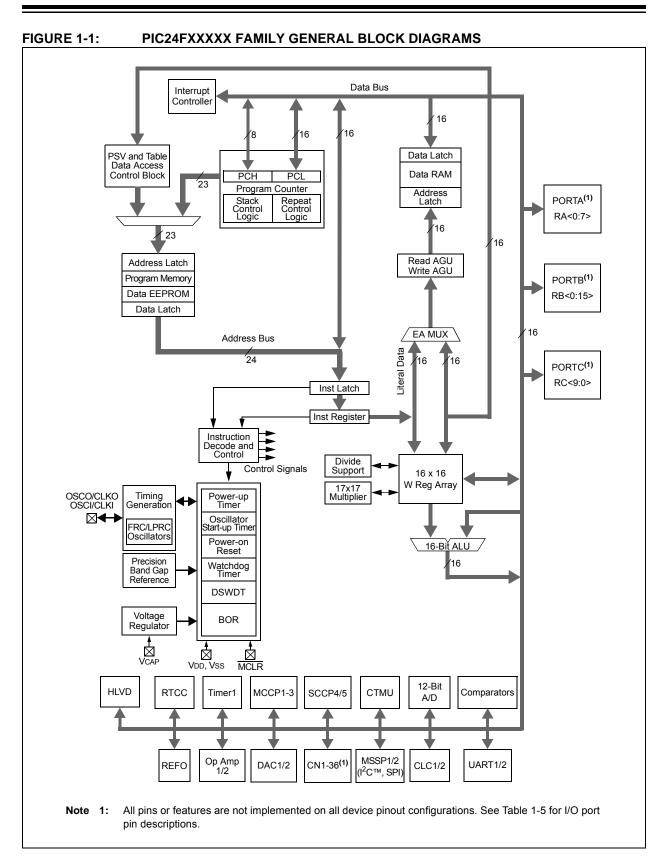

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 37                                                                            |

| Program Memory Size        | 16KB (5.5K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 1K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5V                                                                       |

| Data Converters            | A/D 22x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

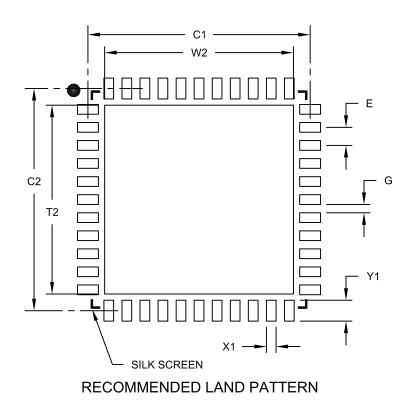

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 44-TQFP                                                                       |

| Supplier Device Package    | 44-TQFP (10x10)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fv16km104-i-pt |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                |      | N                     | lemory       | 1               |                   |              |                  |      |      | Pe                  | riphe     | rals   |             |      |      |     |           |

|----------------|------|-----------------------|--------------|-----------------|-------------------|--------------|------------------|------|------|---------------------|-----------|--------|-------------|------|------|-----|-----------|

| Device         | Pins | Flash Program (bytes) | SRAM (bytes) | EE Data (bytes) | Voltage Range (V) | 16-Bit Timer | 16-Bit MCCP/SCCP | MSSP | UART | 12-Bit A/D Channels | 8-Bit DAC | Op Amp | Comparators | CTMU | RTCC | CLC | ICD BRKPT |

|                |      |                       |              |                 |                   | 5V           | Devic            | es   |      |                     |           |        |             |      |      |     |           |

| PIC24FV16KM204 | 44   | 16K                   | 2K           | 512             | 2.0-5.5           | 1            | 3/2              | 2    | 2    | 22                  | 2         | 2      | 3           | Yes  | Yes  | 2   | 3         |

| PIC24FV16KM202 | 28   | 16K                   | 2K           | 512             | 2.0-5.5           | 1            | 3/2              | 2    | 2    | 19                  | 2         | 2      | 3           | Yes  | Yes  | 2   | 3         |

| PIC24FV08KM204 | 44   | 8K                    | 2K           | 512             | 2.0-5.5           | 1            | 3/2              | 2    | 2    | 22                  | 2         | 2      | 3           | Yes  | Yes  | 2   | 3         |

| PIC24FV08KM202 | 28   | 8K                    | 2K           | 512             | 2.0-5.5           | 1            | 3/2              | 2    | 2    | 19                  | 2         | 2      | 3           | Yes  | Yes  | 2   | 3         |

| PIC24FV16KM104 | 44   | 16K                   | 1K           | 512             | 2.0-5.5           | 1            | 1/1              | 1    | 1    | 22                  | —         | _      | 1           | Yes  | _    | 1   | 3         |

| PIC24FV16KM102 | 28   | 16K                   | 1K           | 512             | 2.0-5.5           | 1            | 1/1              | 1    | 1    | 19                  | _         | _      | 1           | Yes  | _    | 1   | 3         |

| PIC24FV08KM102 | 28   | 8K                    | 1K           | 512             | 2.0-5.5           | 1            | 1/1              | 1    | 1    | 19                  | _         | _      | 1           | Yes  | _    | 1   | 3         |

| PIC24FV08KM101 | 20   | 8K                    | 1K           | 512             | 2.0-5.5           | 1            | 1/1              | 1    | 1    | 16                  | _         | -      | 1           | Yes  | _    | 1   | 3         |

|                |      |                       |              |                 |                   | 3V           | Devic            | es   |      |                     |           |        |             |      |      |     |           |

| PIC24F16KM204  | 44   | 16K                   | 2K           | 512             | 1.8-3.6           | 1            | 3/2              | 2    | 2    | 22                  | 2         | 2      | 3           | Yes  | Yes  | 2   | 3         |

| PIC24F16KM202  | 28   | 16K                   | 2K           | 512             | 1.8-3.6           | 1            | 3/2              | 2    | 2    | 19                  | 2         | 2      | 3           | Yes  | Yes  | 2   | 3         |

| PIC24F08KM204  | 44   | 8K                    | 2K           | 512             | 1.8-3.6           | 1            | 3/2              | 2    | 2    | 22                  | 2         | 2      | 3           | Yes  | Yes  | 2   | 3         |

| PIC24F08KM202  | 28   | 8K                    | 2K           | 512             | 1.8-3.6           | 1            | 3/2              | 2    | 2    | 19                  | 2         | 2      | 3           | Yes  | Yes  | 2   | 3         |

| PIC24F16KM104  | 44   | 16K                   | 1K           | 512             | 1.8-3.6           | 1            | 1/1              | 1    | 1    | 22                  | _         | —      | 1           | Yes  | —    | 1   | 3         |

| PIC24F16KM102  | 28   | 16K                   | 1K           | 512             | 1.8-3.6           | 1            | 1/1              | 1    | 1    | 19                  | _         | _      | 1           | Yes  | _    | 1   | 3         |

| PIC24F08KM102  | 28   | 8K                    | 1K           | 512             | 1.8-3.6           | 1            | 1/1              | 1    | 1    | 19                  | —         | —      | 1           | Yes  | —    | 1   | 3         |

| PIC24F08KM101  | 20   | 8K                    | 1K           | 512             | 1.8-3.6           | 1            | 1/1              | 1    | 1    | 16                  |           |        | 1           | Yes  | _    | 1   | 3         |

### TABLE 1-5: PIC24FV16KM204 FAMILY PINOUT DESCRIPTION (CONTINUED)

|          |                                  |                                  | F             |                        |                |                                  |                                  | FV            |                        |                |     |        |                                                |

|----------|----------------------------------|----------------------------------|---------------|------------------------|----------------|----------------------------------|----------------------------------|---------------|------------------------|----------------|-----|--------|------------------------------------------------|

|          |                                  | I                                | Pin Numb      | ber                    |                |                                  | I                                | Pin Numb      | er                     |                |     |        |                                                |

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | I/O | Buffer | Description                                    |

| SCL1     | 12                               | 17                               | 14            | 44                     | 48             | 12                               | 17                               | 14            | 44                     | 48             | I/O | I2C    | MSSP1 I <sup>2</sup> C Clock                   |

| SDA1     | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | I/O | I2C    | MSSP1 I <sup>2</sup> C Data                    |

| SCL2     | _                                | 7                                | 4             | 24                     | 26             | _                                | 7                                | 4             | 24                     | 26             | I/O | I2C    | MSSP2 I <sup>2</sup> C Clock                   |

| SDA2     | _                                | 6                                | 3             | 23                     | 25             | _                                | 6                                | 3             | 23                     | 25             | I/O | I2C    | MSSP2 I <sup>2</sup> C Data                    |

| SCLKI    | 10                               | 12                               | 9             | 34                     | 37             | 10                               | 12                               | 9             | 34                     | 37             | Ι   | ST     | Secondary Clock Digital Input                  |

| SOSCI    | 9                                | 11                               | 8             | 33                     | 36             | 9                                | 11                               | 8             | 33                     | 36             | Ι   | ANA    | Secondary Oscillator Input                     |

| SOSCO    | 10                               | 12                               | 9             | 34                     | 37             | 10                               | 12                               | 9             | 34                     | 37             | Ι   | ANA    | Secondary Oscillator Output                    |

| T1CK     | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | Ι   | ST     | Timer1 Digital Input Cock                      |

| TCKIA    | 18                               | 26                               | 23            | 15                     | 16             | 18                               | 26                               | 23            | 15                     | 16             | Ι   | ST     | MCCP/SCCP Time Base Clock Input A              |

| TCKIB    | 6                                | 6                                | 3             | 23                     | 25             | 6                                | 6                                | 3             | 23                     | 25             | Ι   | ST     | MCCP/SCCP Time Base Clock Input B              |

| U1CTS    | 12                               | 17                               | 14            | 44                     | 48             | 12                               | 17                               | 14            | 44                     | 48             | Ι   | ST     | UART1 Clear-To-Send Input                      |

| U1RTS    | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | 0   | _      | UART1 Request-To-Send Output                   |

| U1BCLK   | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | 0   | —      | UART1 16x Baud Rate Clock Output               |

| U1RX     | 6                                | 6                                | 3             | 2                      | 2              | 6                                | 6                                | 3             | 2                      | 2              | Ι   | ST     | UART1 Receive                                  |

| U1TX     | 11                               | 16                               | 13            | 3                      | 3              | 11                               | 16                               | 13            | 3                      | 3              | 0   | _      | UART1 Transmit                                 |

| U2CTS    | _                                | 12                               | 9             | 34                     | 37             | _                                | 12                               | 9             | 34                     | 37             | I   | ST     | UART2 Clear-To-Send Input                      |

| U2RTS    | _                                | 11                               | 8             | 33                     | 36             | _                                | 11                               | 8             | 33                     | 36             | 0   | _      | UART2 Request-To-Send Output                   |

| U2BCLK   | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | 0   | _      | UART2 16x Baud Rate Clock Output               |

| U2RX     | _                                | 5                                | 2             | 22                     | 24             | —                                | 5                                | 2             | 22                     | 24             | Ι   | ST     | UART2 Receive                                  |

| U2TX     | _                                | 4                                | 1             | 21                     | 23             | —                                | 4                                | 1             | 21                     | 23             | 0   | _      | UART2 Transmit                                 |

| ULPWU    | 4                                | 4                                | 1             | 21                     | 23             | 4                                | 4                                | 1             | 21                     | 23             | Ι   | ANA    | Ultra Low-Power Wake-up Input                  |

| VCAP     | _                                | _                                |               | —                      | _              | 14                               | 20                               | 17            | 7                      | 7              | Р   | —      | Regulator External Filter Capacitor Connection |

| Vdd      | 20                               | 28                               | 25            | 17,28,28               | 18,30,30       | 20                               | 28                               | 25            | 17,28,28               | 18,30,30       | Р   | —      | Device Positive Supply Voltage                 |

| VDDCORE  | _                                | _                                | _             | —                      | _              | 14                               | 20                               | 17            | 7                      | 7              | Р   | —      | Microcontroller Core Supply Voltage            |

| Vpp      | 1                                | 1                                | 26            | 18                     | 19             | 1                                | 1                                | 26            | 18                     | 19             | Р   | —      | High-Voltage Programming Pin                   |

| VREF+    | 2                                | 2                                | 27            | 19                     | 21             | 2                                | 2                                | 27            | 19                     | 21             | I   | ANA    | A/D Reference Voltage Positive Input           |

| VREF-    | 3                                | 3                                | 28            | 20                     | 22             | 3                                | 3                                | 28            | 20                     | 22             | Ι   | ANA    | A/D Reference Voltage Negative Input           |

| Vss      | 19                               | 27                               | 24            | 16,29,29               | 17,31,31       | 19                               | 27                               | 24            | 16,29,29               | 17,31,31       | Р   | —      | Device Ground Return Voltage                   |

Legend: ANA = Analog level input/output, ST = Schmitt Trigger input buffer, I<sup>2</sup>C<sup>™</sup> = I<sup>2</sup>C/SMBus input buffer

NOTES:

#### TABLE 4-9: MCCP2 REGISTER MAP

| File Name | Addr. | Bit 15  | Bit 14 | Bit 13               | Bit 12               | Bit 11               | Bit 10               | Bit 9                | Bit 8                | Bit 7        | Bit 6        | Bit 5   | Bit 4                 | Bit 3   | Bit 2   | Bit 1                  | Bit 0      | All<br>Resets |

|-----------|-------|---------|--------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|--------------|--------------|---------|-----------------------|---------|---------|------------------------|------------|---------------|

| CCP2CON1L | 164h  | CCPON   | _      | CCPSIDL              | r                    | TMRSYNC              | CLKSEL2              | CLKSEL1              | CLKSEL0              | TMRPS1       | TMRPS0       | T32     | CCSEL                 | MOD3    | MOD2    | MOD1                   | MOD0       | 0000          |

| CCP2CON1H | 166h  | OPSSRC  | RTRGEN | _                    | _                    | IOPS3                | IOPS2                | IOPS1                | IOPS0                | TRIGEN       | ONESHOT      | ALTSYNC | SYNC4                 | SYNC3   | SYNC2   | SYNC1                  | SYNC0      | 0000          |

| CCP2CON2L | 168h  | PWMRSEN | ASDGM  |                      | SSDG                 |                      |                      | _                    | _                    | ASDG7        | ASDG6        | ASDG5   | ASDG4                 | ASDG3   | ASDG2   | ASDG1                  | ASDG0      | 0000          |

| CCP2CON2H | 16Ah  | OENSYNC | -      | OCFEN <sup>(1)</sup> | OCEEN <sup>(1)</sup> | OCDEN <sup>(1)</sup> | OCCEN <sup>(1)</sup> | OCBEN <sup>(1)</sup> | OCAEN                | ICGSM1       | ICGSM0       | _       | AUXOUT1               | AUXOUT0 | ICSEL2  | ICSEL1                 | ICSEL0     | 0100          |

| CCP2CON3L | 16Ch  | _       | _      | _                    | _                    | _                    | _                    | _                    | _                    | _            |              | DT5     | DT4                   | DT3     | DT2     | DT1                    | DT0        | 0000          |

| CCP2CON3H | 16Eh  | OETRIG  | OSCNT2 | OSCNT1               | OSCNT0               | _                    | OUTM2 <sup>(1)</sup> | OUTM1 <sup>(1)</sup> | OUTM0 <sup>(1)</sup> | _            | _            | POLACE  | POLBDF <sup>(1)</sup> | PSSACE1 | PSSACE0 | PSSBDF1 <sup>(1)</sup> | PSSBDF0(1) | 0000          |

| CCP2STATL | 170h  | _       | -      |                      | _                    |                      |                      | _                    | _                    | CCPTRIG      | TRSET        | TRCLR   | ASEVT                 | SCEVT   | ICDIS   | ICOV                   | ICBNE      | 0000          |

| CCP2TMRL  | 174h  |         |        |                      |                      |                      |                      | MCC                  | P2 Time Ba           | ase Register | r Low Word   |         |                       |         |         |                        |            | 0000          |

| CCP2TMRH  | 176h  |         |        |                      |                      |                      |                      | MCC                  | P2 Time Ba           | se Register  | High Word    |         |                       |         |         |                        |            | 0000          |

| CCP2PRL   | 178h  |         |        |                      |                      |                      |                      | MCCP2                | Time Base            | Period Regi  | ister Low Wo | rd      |                       |         |         |                        |            | FFFF          |

| CCP2PRH   | 17Ah  |         |        |                      |                      |                      |                      | MCCP2                | Time Base I          | Period Regi  | ster High Wo | rd      |                       |         |         |                        |            | FFFF          |

| CCP2RAL   | 17Ch  |         |        |                      |                      |                      |                      | 0                    | utput Comp           | oare 2 Data  | Word A       |         |                       |         |         |                        |            | 0000          |

| CCP2RBL   | 180h  |         |        |                      |                      |                      |                      | 0                    | utput Comp           | oare 2 Data  | Word B       |         |                       |         |         |                        |            | 0000          |

| CCP2BUFL  | 184h  |         |        |                      |                      |                      |                      | Input                | Capture 2            | Data Buffer  | Low Word     |         |                       |         |         |                        |            | 0000          |

| CCP2BUFH  | 186h  |         |        |                      |                      |                      |                      | Input                | Capture 2            | Data Buffer  | High Word    |         |                       |         |         |                        |            | 0000          |

PIC24FV16KM204 FAMILY

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

Note 1: These bits are available only on PIC24F(V)16KM2XX devices.

#### 7.2.1 POR AND LONG OSCILLATOR START-UP TIMES

The oscillator start-up circuitry and its associated delay timers are not linked to the device Reset delays that occur at power-up. Some crystal circuits (especially low-frequency crystals) will have a relatively long start-up time. Therefore, one or more of the following conditions is possible after SYSRST is released:

- The oscillator circuit has not begun to oscillate.

- The Oscillator Start-up Timer (OST) has not expired (if a crystal oscillator is used).

- The PLL has not achieved a lock (if PLL is used).

The device will not begin to execute code until a valid clock source has been released to the system. Therefore, the oscillator and PLL start-up delays must be considered when the Reset delay time must be known.

#### 7.2.2 FAIL-SAFE CLOCK MONITOR (FSCM) AND DEVICE RESETS

If the FSCM is enabled, it will begin to monitor the system clock source when SYSRST is released. If a valid clock source is not available at this time, the device will automatically switch to the FRC Oscillator and the user can switch to the desired crystal oscillator in the Trap Service Routine (TSR).

### 7.3 Special Function Register Reset States

Most of the Special Function Registers (SFRs) associated with the PIC24F CPU and peripherals are reset to a particular value at a device Reset. The SFRs are grouped by their peripheral or CPU function and their Reset values are specified in each section of this manual.

The Reset value for each SFR does not depend on the type of Reset, with the exception of four registers. The Reset value for the Reset Control register, RCON, will depend on the type of device Reset. The Reset value for the Oscillator Control register, OSCCON, will depend on the type of Reset and the programmed values of the FNOSCx bits in the Flash Configuration Word (FOSCSEL<2:0>); see Table 7-2. The RCFGCAL and NVMCON registers are only affected by a POR.

### 7.4 Brown-out Reset (BOR)

The PIC24FXXXXX family devices implement a BOR circuit, which provides the user several configuration and power-saving options. The BOR is controlled by the BORV<1:0> and BOREN<1:0> Configuration bits (FPOR<6:5,1:0>). There are a total of four BOR configurations, which are provided in Table 7-3.

The BOR threshold is set by the BORV<1:0> bits. If BOR is enabled (any values of BOREN<1:0>, except '00'), any drop of VDD below the set threshold point will reset the device. The chip will remain in BOR until VDD rises above the threshold.

If the Power-up Timer is enabled, it will be invoked after VDD rises above the threshold. Then, it will keep the chip in Reset for an additional time delay, TPWRT, if VDD drops below the threshold while the Power-up Timer is running. The chip goes back into a BOR and the Power-up Timer will be initialized. Once VDD rises above the threshold, the Power-up Timer will execute the additional time delay.

BOR and the Power-up Timer (PWRT) are independently configured. Enabling the Brown-out Reset does not automatically enable the PWRT.

### 7.4.1 LOW-POWER BOR (LPBOR)

The Low-Power BOR is an alternate setting for the BOR, designed to consume minimal power. In LPBOR mode, BORV<1:0> (FPOR<6:5>) = 00. The BOR trip point is approximately 2.0V. Due to the low current consumption, the accuracy of the LPBOR mode can vary.

Unlike the other BOR modes, LPBOR mode will not cause a device Reset when VDD drops below the trip point. Instead, it re-arms the POR circuit to ensure that the device will reset properly in the event that VDD continues to drop below the minimum operating voltage.

The device will continue to execute code when VDD is below the level of the LPBOR trip point. A device that requires falling edge BOR protection to prevent code from improperly executing should use one of the other BOR voltage settings.

| R/W-0        | R-0, HSC        | U-0               | U-0             | U-0               | U-0              | U-0             | U-0    |

|--------------|-----------------|-------------------|-----------------|-------------------|------------------|-----------------|--------|

| ALTIVT       | DISI            | —                 | —               | —                 | —                | —               | —      |

| bit 15       |                 |                   |                 |                   |                  |                 | bit 8  |

|              |                 |                   |                 |                   |                  |                 |        |

| U-0          | U-0             | U-0               | U-0             | U-0               | R/W-0            | R/W-0           | R/W-0  |

| —            | —               | —                 | —               | —                 | INT2EP           | INT1EP          | INT0EP |

| bit 7        |                 |                   |                 |                   |                  |                 | bit 0  |

|              |                 |                   |                 |                   |                  |                 |        |

| Legend:      |                 | HSC = Hardw       | are Settable/C  | learable bit      |                  |                 |        |

| R = Readab   | le bit          | W = Writable b    | oit             | U = Unimplem      | nented bit, read | d as '0'        |        |

| -n = Value a | t POR           | '1' = Bit is set  |                 | '0' = Bit is clea | ared             | x = Bit is unkn | iown   |

|              |                 |                   |                 |                   |                  |                 |        |

| bit 15       | ALTIVT: Enat    | ole Alternate Int | errupt Vector 7 | Table bit         |                  |                 |        |

|              |                 | rnate Interrupt   | •               | ,                 |                  |                 |        |

|              |                 | ndard (default) I | •               | r Table (IVT)     |                  |                 |        |

| bit 14       | 21011 2101      | struction Status  |                 |                   |                  |                 |        |

|              |                 | ruction is active |                 |                   |                  |                 |        |

| bit 13-3     |                 | ted: Read as '0   |                 |                   |                  |                 |        |

| bit 2        | •               | ernal Interrupt 2 |                 | Polarity Solact k | ait              |                 |        |

|              |                 | s on the negativ  | -               |                   | JIL              |                 |        |

|              | •               | s on the positive | •               |                   |                  |                 |        |

| bit 1        |                 | ernal Interrupt 1 | •               | Polarity Select b | oit              |                 |        |

|              | 1 = Interrupt i | s on the negativ  | ve edge         | -                 |                  |                 |        |

|              | 0 = Interrupt i | s on the positive | e edge          |                   |                  |                 |        |

| bit 0        | INTOEP: Exte    | ernal Interrupt 0 | Edge Detect F   | Polarity Select b | oit              |                 |        |

|              |                 | s on the negativ  | U U             |                   |                  |                 |        |

|              | 0 = Interrupt i | s on the positive | e edge          |                   |                  |                 |        |

#### REGISTER 8-4: INTCON2: INTERRUPT CONTROL REGISTER 2

#### REGISTER 8-19: IPC0: INTERRUPT PRIORITY CONTROL REGISTER 0

|                                                           | R/W-1                                                                                                                                                               | R/W-0                                                                                                                                                                                     | R/W-0                                                                                        | U-0                         | R/W-1            | R/W-0           | R/W-0   |

|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-----------------------------|------------------|-----------------|---------|

| _                                                         | T1IP2                                                                                                                                                               | T1IP1                                                                                                                                                                                     | T1IP0                                                                                        | _                           | CCP2IP2          | CCP2IP1         | CCP2IP0 |

| bit 15                                                    |                                                                                                                                                                     |                                                                                                                                                                                           |                                                                                              |                             |                  |                 | bit 8   |

|                                                           |                                                                                                                                                                     |                                                                                                                                                                                           |                                                                                              |                             |                  |                 |         |

| U-0                                                       | R/W-1                                                                                                                                                               | R/W-0                                                                                                                                                                                     | R/W-0                                                                                        | U-0                         | R/W-1            | R/W-0           | R/W-0   |

|                                                           | CCP1IP2                                                                                                                                                             | CCP1IP1                                                                                                                                                                                   | CCP1IP0                                                                                      |                             | INT0IP2          | INT0IP1         | INT0IP0 |

| bit 7                                                     |                                                                                                                                                                     |                                                                                                                                                                                           |                                                                                              |                             |                  |                 | bit C   |

| Legend:                                                   |                                                                                                                                                                     |                                                                                                                                                                                           |                                                                                              |                             |                  |                 |         |

| R = Readab                                                | ole bit                                                                                                                                                             | W = Writable                                                                                                                                                                              | bit                                                                                          | U = Unimplen                | nented bit, read | d as '0'        |         |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x |                                                                                                                                                                     |                                                                                                                                                                                           |                                                                                              |                             |                  | x = Bit is unkr | nown    |

| bit 15                                                    | Unimplemen                                                                                                                                                          | ted: Read as '(                                                                                                                                                                           | )'                                                                                           |                             |                  |                 |         |

| bit 14-12                                                 | -                                                                                                                                                                   | imer1 Interrupt                                                                                                                                                                           |                                                                                              |                             |                  |                 |         |

|                                                           |                                                                                                                                                                     | ot is Priority 7 (h                                                                                                                                                                       | -                                                                                            | interrupt)                  |                  |                 |         |

|                                                           | •                                                                                                                                                                   |                                                                                                                                                                                           |                                                                                              |                             |                  |                 |         |

|                                                           | •                                                                                                                                                                   |                                                                                                                                                                                           |                                                                                              |                             |                  |                 |         |

|                                                           | 001 = Interrup                                                                                                                                                      | ot is Priority 1                                                                                                                                                                          |                                                                                              |                             |                  |                 |         |

|                                                           |                                                                                                                                                                     | ot source is disa                                                                                                                                                                         | abled                                                                                        |                             |                  |                 |         |

| bit 11                                                    | Unimplemen                                                                                                                                                          | ted: Read as '(                                                                                                                                                                           | )'                                                                                           |                             |                  |                 |         |

| bit 10-8                                                  | CCP2IP<2:0>                                                                                                                                                         | Capture/Com                                                                                                                                                                               | pare 2 Event                                                                                 | Interrupt Priority          | y bits           |                 |         |

|                                                           | 111 = Interrup                                                                                                                                                      | ot is Priority 7 (h                                                                                                                                                                       | ighest priority                                                                              | interrupt)                  |                  |                 |         |

|                                                           |                                                                                                                                                                     |                                                                                                                                                                                           |                                                                                              |                             |                  |                 |         |

|                                                           | •                                                                                                                                                                   |                                                                                                                                                                                           |                                                                                              |                             |                  |                 |         |

|                                                           | •<br>•                                                                                                                                                              |                                                                                                                                                                                           |                                                                                              |                             |                  |                 |         |

|                                                           | •<br>•<br>001 = Interrup<br>000 = Interrup                                                                                                                          | ot is Priority 1<br>ot source is disa                                                                                                                                                     | abled                                                                                        |                             |                  |                 |         |

| bit 7                                                     | 000 = Interrup                                                                                                                                                      |                                                                                                                                                                                           |                                                                                              |                             |                  |                 |         |

| bit 7<br>bit 6-4                                          | 000 = Interrup<br><b>Unimplemen</b>                                                                                                                                 | ot source is disa<br>ted: Read as '(                                                                                                                                                      | )'                                                                                           | Interrupt Priority          | y bits           |                 |         |

|                                                           | 000 = Interrup<br>Unimplemen<br>CCP1IP<2:0>                                                                                                                         | ot source is disa<br>ted: Read as '(                                                                                                                                                      | )'<br>ipare 1 Event                                                                          |                             | y bits           |                 |         |

|                                                           | 000 = Interrup<br>Unimplemen<br>CCP1IP<2:0>                                                                                                                         | ot source is disa<br>t <b>ed:</b> Read as '(<br>>: Capture/Com                                                                                                                            | )'<br>ipare 1 Event                                                                          |                             | y bits           |                 |         |

|                                                           | 000 = Interrup<br>Unimplemen<br>CCP1IP<2:0>                                                                                                                         | ot source is disa<br>t <b>ed:</b> Read as '(<br>>: Capture/Com                                                                                                                            | )'<br>ipare 1 Event                                                                          |                             | y bits           |                 |         |

|                                                           | 000 = Interrup<br>Unimplemen<br>CCP1IP<2:0>                                                                                                                         | ot source is disa<br>ted: Read as '(<br>>: Capture/Com<br>ot is Priority 7 (h                                                                                                             | )'<br>ipare 1 Event                                                                          |                             | y bits           |                 |         |

|                                                           | 000 = Interrup<br>Unimplemen<br>CCP1IP<2:0><br>111 = Interrup<br>•<br>•<br>•<br>001 = Interrup                                                                      | ot source is disa<br>ted: Read as '(<br>>: Capture/Com<br>ot is Priority 7 (h                                                                                                             | ) <sup>,</sup><br>Ipare 1 Event<br>Iighest priority                                          |                             | y bits           |                 |         |

|                                                           | 000 = Interrup<br>Unimplemen<br>CCP1IP<2:0><br>111 = Interrup<br>•<br>•<br>001 = Interrup<br>000 = Interrup                                                         | ot source is disa<br>ted: Read as '(<br>>: Capture/Com<br>ot is Priority 7 (h<br>ot is Priority 1                                                                                         | <sub>)'</sub><br>npare 1 Event<br>nighest priority<br>abled                                  |                             | y bits           |                 |         |

| bit 6-4                                                   | 000 = Interrup<br>Unimplemen<br>CCP1IP<2:0><br>111 = Interrup<br>•<br>•<br>001 = Interrup<br>000 = Interrup<br>Unimplemen<br>INT0IP<2:0>                            | ot source is disa<br><b>ted:</b> Read as '(<br><b>:</b> Capture/Com<br>ot is Priority 7 (h<br>ot is Priority 1<br>ot source is disa<br><b>ted:</b> Read as '(<br><b>:</b> External Interr | )'<br>Ipare 1 Event<br>Iighest priority<br>abled<br>)'<br>upt 0 Interrupt                    | interrupt)<br>Priority bits | y bits           |                 |         |

| bit 6-4<br>bit 3                                          | 000 = Interrup<br>Unimplemen<br>CCP1IP<2:0><br>111 = Interrup<br>•<br>•<br>001 = Interrup<br>000 = Interrup<br>Unimplemen<br>INT0IP<2:0>                            | ot source is disa<br><b>ted:</b> Read as '(<br><b>:</b> Capture/Comot<br>ot is Priority 7 (h<br>ot is Priority 1<br>ot source is disa<br><b>ted:</b> Read as '(                           | )'<br>Ipare 1 Event<br>Iighest priority<br>abled<br>)'<br>upt 0 Interrupt                    | interrupt)<br>Priority bits | y bits           |                 |         |

| bit 6-4<br>bit 3                                          | 000 = Interrup<br>Unimplemen<br>CCP1IP<2:0><br>111 = Interrup<br>•<br>•<br>001 = Interrup<br>000 = Interrup<br>Unimplemen<br>INT0IP<2:0>                            | ot source is disa<br><b>ted:</b> Read as '(<br><b>:</b> Capture/Com<br>ot is Priority 7 (h<br>ot is Priority 1<br>ot source is disa<br><b>ted:</b> Read as '(<br><b>:</b> External Interr | )'<br>Ipare 1 Event<br>Iighest priority<br>abled<br>)'<br>upt 0 Interrupt                    | interrupt)<br>Priority bits | y bits           |                 |         |

| bit 6-4<br>bit 3                                          | 000 = Interrup<br>Unimplemen<br>CCP1IP<2:0><br>111 = Interrup<br>•<br>•<br>001 = Interrup<br>000 = Interrup<br>Unimplemen<br>INT0IP<2:0>                            | ot source is disa<br><b>ted:</b> Read as '(<br><b>:</b> Capture/Com<br>ot is Priority 7 (h<br>ot is Priority 1<br>ot source is disa<br><b>ted:</b> Read as '(<br><b>:</b> External Interr | )'<br>Ipare 1 Event<br>Iighest priority<br>abled<br>)'<br>upt 0 Interrupt                    | interrupt)<br>Priority bits | y bits           |                 |         |

| bit 6-4<br>bit 3                                          | 000 = Interrup<br>Unimplemen<br>CCP1IP<2:0><br>111 = Interrup<br>001 = Interrup<br>000 = Interrup<br>Unimplemen<br>INT0IP<2:0>:<br>111 = Interrup<br>001 = Interrup | ot source is disa<br>ted: Read as '(<br>: Capture/Com<br>ot is Priority 7 (h<br>ot is Priority 1<br>tot source is disa<br>ted: Read as '(<br>: External Interr<br>pt is Priority 7 (      | )'<br>ipare 1 Event<br>ighest priority<br>abled<br>)'<br>upt 0 Interrupt<br>highest priority | interrupt)<br>Priority bits | y bits           |                 |         |

NOTES:

NOTES:

### 10.2.2 IDLE MODE

Idle mode includes these features:

- · The CPU will stop executing instructions.

- · The WDT is automatically cleared.

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 10.6 "Selective Peripheral Module Control").

- If the WDT or FSCM is enabled, the LPRC will also remain active.

The device will wake from Idle mode on any of these events:

- · Any interrupt that is individually enabled

- Any device Reset

- A WDT time-out

On wake-up from Idle, the clock is reapplied to the CPU and instruction execution begins immediately, starting with the instruction following the PWRSAV instruction or the first instruction in the ISR.

#### 10.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction will be held off until entry into Sleep or Idle mode has completed. The device will then wake-up from Sleep or Idle mode.

#### 10.2.3.1 Power-on Resets (PORs)

VDD voltage is monitored to produce PORs. When a true POR occurs, the entire device is reset.

#### 10.3 Ultra Low-Power Wake-up

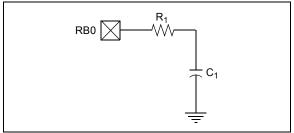

The Ultra Low-Power Wake-up (ULPWU) on pin, RB0, allows a slow falling voltage to generate an interrupt without excess current consumption.

To use this feature:

- 1. Charge the capacitor on RB0 by configuring the RB0 pin to an output and setting it to '1'.

- 2. Stop charging the capacitor by configuring RB0 as an input.

- 3. Discharge the capacitor by setting the ULPEN and ULPSINK bits in the ULPWCON register.

- 4. Configure Sleep mode.

- 5. Enter Sleep mode.

When the voltage on RB0 drops below VIL, the device wakes up and executes the next instruction.

This feature provides a low-power technique for periodically waking up the device from Sleep mode.

The time-out is dependent on the discharge time of the RC circuit on RB0.

When the ULPWU module wakes the device from Sleep mode, the ULPWUIF bit (IFS5<0>) is set. Software can check this bit upon wake-up to determine the wake-up source.

See Example 10-2 for initializing the ULPWU module.

#### EXAMPLE 10-2: ULTRA LOW-POWER WAKE-UP INITIALIZATION

```

//********

// 1. Charge the capacitor on RBO

TRISBbits.TRISB0 = 0;

LATBbits.LATB0 = 1;

for(i = 0; i < 10000; i++) Nop();</pre>

//2. Stop Charging the capacitor

on RBO

11

//*******************************

TRISBbits.TRISB0 = 1;

//3. Enable ULPWU Interrupt

IFS5bits.ULPWUIF = 0;

IEC5bits.ULPWUIE = 1;

IPC21bits.ULPWUIP = 0x7;

//*********************************

//4. Enable the Ultra Low Power

11

Wakeup module and allow

11

capacitor discharge

ULPWCONbits.ULPEN = 1;

ULPWCONbit.ULPSINK = 1;

//5. Enter Sleep Mode

11

Sleep();

//for sleep, execution will

//resume here

```

A series resistor, between RB0 and the external capacitor provides overcurrent protection for the AN2/ULPWU/RB0 pin and enables software calibration of the time-out (see Figure 10-1).

#### FIGURE 10-1: SERIES RESISTOR

A timer can be used to measure the charge time and discharge time of the capacitor. The charge time can then be adjusted to provide the desired delay in Sleep. This technique compensates for the affects of temperature, voltage and component accuracy. The peripheral can also be configured as a simple, programmable Low-Voltage Detect (LVD) or temperature sensor.

#### REGISTER 13-6: CCPxCON3H: CCPx CONTROL 3 HIGH REGISTERS

| R/W-0         | R/W-0                 | R/W-0                                  | R/W-0                                | U-0                 | R/W-0                | R/W-0                  | R/W-0                  |

|---------------|-----------------------|----------------------------------------|--------------------------------------|---------------------|----------------------|------------------------|------------------------|

| OETRIG        | OSCNT2                | OSCNT1                                 | OSCNT0                               | _                   | OUTM2 <sup>(1)</sup> | OUTM1 <sup>(1)</sup>   | OUTM0 <sup>(1)</sup>   |

| bit 15        |                       |                                        |                                      |                     |                      |                        | bit 8                  |

|               |                       |                                        |                                      |                     |                      |                        |                        |

| U-0           | U-0                   | R/W-0                                  | R/W-0                                | R/W-0               | R/W-0                | R/W-0                  | R/W-0                  |

|               |                       | POLACE                                 | POLBDF <sup>(1)</sup>                | PSSACE1             | PSSACE0              | PSSBDF1 <sup>(1)</sup> | PSSBDF0 <sup>(1)</sup> |

| bit 7         |                       |                                        |                                      |                     |                      |                        | bit C                  |

| Legend:       |                       |                                        |                                      |                     |                      |                        |                        |

| R = Readabl   | le bit                | W = Writable                           | bit                                  | U = Unimplen        | nented bit, read     | d as '0'               |                        |

| -n = Value at | POR                   | '1' = Bit is set                       |                                      | '0' = Bit is cle    |                      | x = Bit is unkn        | own                    |

|               |                       |                                        |                                      |                     |                      |                        | -                      |

| bit 15        | OETRIG: CC            | Px Dead-Time                           | Select bit                           |                     |                      |                        |                        |

|               | 1 = For Trigg         | ered mode (TF                          | RIGEN = 1): Mo                       | dule does not       | drive enabled o      | output pins until      | triggered              |

|               |                       | output pin opera                       |                                      |                     |                      |                        |                        |

| bit 14-12     | OSCNT<2:0>            | : One-Shot Ev                          | ent Count bits                       |                     |                      |                        |                        |

|               |                       |                                        | nt by 7 time ba                      |                     |                      |                        |                        |

|               |                       |                                        | nt by 6 time ba                      |                     |                      |                        |                        |

|               |                       |                                        | nt by 5 time bas<br>nt by 4 time bas |                     |                      |                        |                        |

|               |                       |                                        | nt by 3 time bas                     |                     |                      |                        |                        |

|               |                       |                                        | nt by 2 time ba                      |                     |                      |                        |                        |

|               |                       |                                        | nt by 1 time ba                      |                     |                      |                        |                        |

|               | 000 <b>= Do no</b>    | t extend one-sl                        | not Trigger ever                     | nt                  |                      |                        |                        |

| bit 11        | -                     | ted: Read as '                         |                                      |                     |                      |                        |                        |

| bit 10-8      | OUTM<2:0>:            | PWMx Output                            | Mode Control I                       | oits <sup>(1)</sup> |                      |                        |                        |

|               | 111 = Reserv          |                                        |                                      |                     |                      |                        |                        |

|               | 110 = Output          |                                        | 1. f                                 |                     |                      |                        |                        |

|               |                       | DC Output mod<br>DC Output mod         |                                      |                     |                      |                        |                        |

|               | 011 = Reserv          | •                                      |                                      |                     |                      |                        |                        |

|               | 010 = Half-Br         | idge Output me                         | ode                                  |                     |                      |                        |                        |

|               |                       | Pull Output mod                        |                                      |                     |                      |                        |                        |

|               | 000 <b>= Steera</b> l | ble Single Outp                        | out mode                             |                     |                      |                        |                        |

| bit 7-6       | -                     | ted: Read as '                         |                                      |                     |                      |                        |                        |

| bit 5         |                       | -                                      | s, OCxA, OCxC                        | and OCxE, P         | olarity Control      | bit                    |                        |

|               |                       | in polarity is ac<br>in polarity is ac |                                      |                     |                      |                        |                        |

| bit 4         |                       |                                        | s, OCxB, OCxE                        | and OCxF Po         | plarity Control b    | <sub>Dit</sub> (1)     |                        |

|               |                       | in polarity is ac                      |                                      |                     |                      |                        |                        |

|               |                       | in polarity is ac                      |                                      |                     |                      |                        |                        |

| bit 3-2       | PSSACE<1:0            | >: PWMx Outp                           | out Pins, OCxA                       | , OCxC and O        | CxE, Shutdowr        | State Control b        | oits                   |

|               | 11 = Pins are         | driven active v                        | vhen a shutdow                       | n event occur       | S                    |                        |                        |

|               |                       |                                        | when a shutdo                        |                     | urs                  |                        |                        |

|               |                       |                                        | n a shutdown e                       |                     |                      |                        | (4)                    |

| bit 1-0       |                       |                                        |                                      |                     |                      | State Control b        | oits <sup>(1)</sup>    |

|               |                       |                                        | vhen a shutdov                       |                     |                      |                        |                        |

|               |                       |                                        | when a shutdo                        |                     |                      |                        |                        |

|               | ux = Pins are         | па пуп-тпре                            | dance state wh                       | ien a shuluowi      | i eveni occurs       |                        |                        |

**Note 1:** These bits are implemented in MCCPx modules only.

# 14.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on MSSP, refer to the "PIC24F Family Reference Manual".

The Master Synchronous Serial Port (MSSP) module is an 8-bit serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, Shift registers, display drivers, A/D Converters, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>)

- Full Master mode

- Slave mode (with general address call)

The SPI interface supports these modes in hardware:

- Master mode

- Slave mode

- · Daisy-Chaining Operation in Slave mode

- Synchronized Slave Operation

The  $I^2C$  interface supports the following modes in hardware:

- Master mode

- · Multi-Master mode

- Slave mode with 10-Bit and 7-Bit Addressing and Address Masking

- Byte NACKing

- Selectable Address and Data Hold, and Interrupt Masking

### 14.1 I/O Pin Configuration for SPI

In SPI Master mode, the MSSP module will assert control over any pins associated with the SDOx and SCKx outputs. This does not automatically disable other digital functions associated with the pin and may result in the module driving the digital I/O port inputs. To prevent this, the MSSP module outputs must be disconnected from their output pins while the module is in SPI Master mode. While disabling the module temporarily may be an option, it may not be a practical solution in all applications.

The SDOx and SCKx outputs for the module can be selectively disabled by using the SDOxDIS and SCKxDIS bits in the PADCFG1 register (Register 14-10). Setting the bit disconnects the corresponding output for a particular module from its assigned pin.

### REGISTER 14-3: SSPxCON1: MSSPx CONTROL REGISTER 1 (SPI MODE)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   |     | —   | —   | —   |     | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0 | R/W-0                | R/W-0                | R/W-0 | R/W-0                | R/W-0                | R/W-0                | R/W-0                |

|-------|----------------------|----------------------|-------|----------------------|----------------------|----------------------|----------------------|

| WCOL  | SSPOV <sup>(1)</sup> | SSPEN <sup>(2)</sup> | СКР   | SSPM3 <sup>(3)</sup> | SSPM2 <sup>(3)</sup> | SSPM1 <sup>(3)</sup> | SSPM0 <sup>(3)</sup> |

| bit 7 |                      |                      |       |                      |                      |                      | bit 0                |

| Legend:    |                   |                                 |                                                                                   |                                                |

|------------|-------------------|---------------------------------|-----------------------------------------------------------------------------------|------------------------------------------------|

| R = Read   | able bit          | W = Writable bit                | U = Unimplemented bit                                                             | , read as '0'                                  |

| -n = Value | e at POR          | '1' = Bit is set                | '0' = Bit is cleared                                                              | x = Bit is unknown                             |

|            |                   |                                 |                                                                                   |                                                |

| bit 15-8   | Unimple           | mented: Read as '0'             |                                                                                   |                                                |

| bit 7      | WCOL: \           | Vrite Collision Detect bit      |                                                                                   |                                                |

|            |                   | •                               | while it is still transmitting the                                                | previous word (must be cleared in              |

|            | softw<br>0 = No c | ,                               |                                                                                   |                                                |

| bit 6      |                   |                                 | Port Receive Overflow Indicate                                                    | or bit(1)                                      |

| bit 0      | SPI Slav          |                                 |                                                                                   |                                                |

|            |                   |                                 | SPxBUF register is still holding                                                  | g the previous data. In case of over-          |

|            |                   |                                 |                                                                                   | ave mode. The user must read the               |

|            | 0 = No c          |                                 | g data, to avoid setting overflo                                                  | w (must be cleared in software).               |

| bit 5      |                   | Master Synchronous Serial F     | Port Enable bit(2)                                                                |                                                |

| DIL 5      |                   | •                               | ures SCKx, SDOx, SDIx and                                                         | SSx as serial nort nins                        |

|            |                   |                                 | jures these pins as I/O port pi                                                   | · ·                                            |

| bit 4      | CKP: Clo          | ock Polarity Select bit         |                                                                                   |                                                |

|            | 1 = Idle s        | state for clock is a high level |                                                                                   |                                                |

|            |                   | state for clock is a low level  |                                                                                   |                                                |

| bit 3-0    | SSPM<3            | :0>: Master Synchronous Se      | rial Port Mode Select bits <sup>(3)</sup>                                         |                                                |

|            |                   | SPI Master mode, Clock = Fo     |                                                                                   |                                                |

|            |                   |                                 | x pin; <u>SSx</u> pin control is disabl<br>(x pin; <u>SSx</u> pin control is enab | ed, $\overline{SSx}$ can be used as an I/O pin |

|            |                   | SPI Master mode, Clock = TM     |                                                                                   |                                                |

|            |                   | SPI Master mode, Clock = Fo     | •                                                                                 |                                                |

|            |                   | PI Master mode, Clock = Fo      |                                                                                   |                                                |

|            | 0000 = 5          | SPI Master mode, Clock = Fo     | SC/2                                                                              |                                                |

| Note 1:    | In Master mo      | de, the overflow bit is not set | t since each new reception (a                                                     | nd transmission) is initiated by               |

|            | writing to the    | SSPxBUF register.               |                                                                                   |                                                |

- 2: When enabled, these pins must be properly configured as inputs or outputs.

- **3:** Bit combinations not specifically listed here are either reserved or implemented in  $I^2C^{TM}$  mode only.

| R/W-0         | R/W-0                                                                                                                               | R/W-0                                                                                                                                              | R/W-0           | R/W-0             | R/W-0            | R/W-0           | R/W-0         |