Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                     |

| Number of I/O              | 37                                                                             |

| Program Memory Size        | 16KB (5.5K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | 512 x 8                                                                        |

| RAM Size                   | 1K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5V                                                                        |

| Data Converters            | A/D 22x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 48-UFQFN Exposed Pad                                                           |

| Supplier Device Package    | 48-UQFN (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fv16km104t-i-mv |

### **Table of Contents**

| 1.0   | Device Overview                                             |     |

|-------|-------------------------------------------------------------|-----|

| 2.0   | Guidelines for Getting Started with 16-Bit Microcontrollers | 29  |

| 3.0   | CPU                                                         |     |

| 4.0   | Memory Organization                                         | 41  |

| 5.0   | Flash Program Memory                                        | 67  |

| 6.0   | Data EEPROM Memory                                          |     |

| 7.0   | Resets                                                      | 79  |

| 8.0   | Interrupt Controller                                        | 85  |

| 9.0   | Oscillator Configuration                                    | 121 |

| 10.0  | Power-Saving Features                                       | 131 |

| 11.0  | I/O Ports                                                   | 137 |

| 12.0  | Timer1                                                      | 141 |

| 13.0  | Capture/Compare/PWM/Timer Modules (MCCP and SCCP)           | 143 |

| 14.0  | Master Synchronous Serial Port (MSSP)                       |     |

| 15.0  | Universal Asynchronous Receiver Transmitter (UART)          | 173 |

| 16.0  | Real-Time Clock and Calendar (RTCC)                         | 181 |

| 17.0  | Configurable Logic Cell (CLC)                               | 195 |

| 18.0  | High/Low-Voltage Detect (HLVD)                              | 207 |

|       | 12-Bit A/D Converter with Threshold Detect                  |     |

| 20.0  | 8-Bit Digital-to-Analog Converter (DAC)                     | 229 |

| 21.0  | Dual Operational Amplifier Module                           | 233 |

| 22.0  | Comparator Module                                           | 235 |

| 23.0  | Comparator Voltage Reference                                | 239 |

| 24.0  | Charge Time Measurement Unit (CTMU)                         | 241 |

| 25.0  | Special Features                                            | 249 |

| 26.0  | Development Support                                         | 261 |

| 27.0  | Electrical Characteristics                                  | 265 |

|       | Packaging Information                                       |     |

| Appe  | endix A: Revision History                                   | 325 |

| Index | X                                                           | 327 |

| The I | Microchip Web Site                                          | 333 |

| Custo | omer Change Notification Service                            | 333 |

| Custo | omer Support                                                | 333 |

| Produ | uct Identification System                                   | 335 |

TABLE 1-5: PIC24FV16KM204 FAMILY PINOUT DESCRIPTION (CONTINUED)

|          |                                  |                                  | F             |                        |                |                                  |                                  | FV            |                        |                |     |        |                            |

|----------|----------------------------------|----------------------------------|---------------|------------------------|----------------|----------------------------------|----------------------------------|---------------|------------------------|----------------|-----|--------|----------------------------|

|          |                                  | I                                | Pin Numb      | er                     |                |                                  | F                                | Pin Numb      | er                     |                |     |        |                            |

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | I/O | Buffer | Description                |

| C1OUT    | 17                               | 25                               | 22            | 14                     | 15             | 17                               | 25                               | 22            | 14                     | 15             | 0   | _      | Comparator 1 Output        |

| C2INA    | _                                | 5                                | 2             | 22                     | 24             | _                                | 5                                | 2             | 22                     | 24             | ı   | ANA    | Comparator 2 Input A (+)   |

| C2INB    | _                                | 4                                | 1             | 21                     | 23             | _                                | 4                                | 1             | 21                     | 23             | ı   | ANA    | Comparator 2 Input B (-)   |

| C2INC    | _                                | 7                                | 4             | 24                     | 26             | _                                | 7                                | 4             | 24                     | 26             | ı   | ANA    | Comparator 2 Input C (+)   |

| C2IND    | _                                | 6                                | 3             | 23                     | 25             | _                                | 6                                | 3             | 23                     | 25             | ı   | ANA    | Comparator 2 Input D (-)   |

| C2OUT    | _                                | 20                               | 17            | 7                      | 7              | _                                | 16                               | 13            | 43                     | 47             | 0   | _      | Comparator 2 Output        |

| C3INA    | _                                | 26                               | 23            | 15                     | 16             | _                                | 26                               | 23            | 15                     | 16             | ı   | ANA    | Comparator 3 Input A (+)   |

| C3INB    | _                                | 25                               | 22            | 14                     | 15             | _                                | 25                               | 22            | 14                     | 15             | ı   | ANA    | Comparator 3 Input B (-)   |

| C3INC    | _                                | 2                                | 27            | 19                     | 21             | _                                | 2                                | 27            | 19                     | 21             | I   | ANA    | Comparator 3 Input C (+)   |

| C3IND    | _                                | 4                                | 1             | 21                     | 23             | _                                | 4                                | 1             | 21                     | 23             | ı   | ANA    | Comparator 3 Input D (-)   |

| C3OUT    | _                                | 17                               | 14            | 44                     | 48             | _                                | 17                               | 14            | 44                     | 48             | 0   | _      | Comparator 3 Output        |

| CLC10    | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | 0   | _      | CLC 1 Output               |

| CLC2O    | _                                | 19                               | 16            | 6                      | 6              | _                                | 19                               | 16            | 6                      | 6              | 0   | _      | CLC 2 Output               |

| CLCINA   | 9                                | 14                               | 11            | 41                     | 45             | 9                                | 14                               | 11            | 41                     | 45             | I   | ST     | CLC External Input A       |

| CLCINB   | 10                               | 15                               | 12            | 42                     | 46             | 10                               | 15                               | 12            | 42                     | 46             | I   | ST     | CLC External Input B       |

| CLKI     | 7                                | 9                                | 6             | 30                     | 33             | 7                                | 9                                | 6             | 30                     | 33             | I   | ANA    | Primary Clock Input        |

| CLKO     | 8                                | 10                               | 7             | 31                     | 34             | 8                                | 10                               | 7             | 31                     | 34             | 0   | _      | System Clock Output        |

| CN0      | 10                               | 12                               | 9             | 34                     | 37             | 10                               | 12                               | 9             | 34                     | 37             | I   | ST     | Interrupt-on-Change Inputs |

| CN1      | 9                                | 11                               | 8             | 33                     | 36             | 9                                | 11                               | 8             | 33                     | 36             | I   | ST     | Interrupt-on-Change Inputs |

| CN2      | 2                                | 2                                | 27            | 19                     | 21             | 2                                | 2                                | 27            | 19                     | 21             | I   | ST     | Interrupt-on-Change Inputs |

| CN3      | 3                                | 3                                | 28            | 20                     | 22             | 3                                | 3                                | 28            | 20                     | 22             | I   | ST     | Interrupt-on-Change Inputs |

| CN4      | 4                                | 4                                | 1             | 21                     | 23             | 4                                | 4                                | 1             | 21                     | 23             | I   | ST     | Interrupt-on-Change Inputs |

| CN5      | 5                                | 5                                | 2             | 22                     | 24             | 5                                | 5                                | 2             | 22                     | 24             | I   | ST     | Interrupt-on-Change Inputs |

| CN6      | 6                                | 6                                | 3             | 23                     | 25             | 6                                | 6                                | 3             | 23                     | 25             |     | ST     | Interrupt-on-Change Inputs |

| CN7      | _                                | 7                                | 4             | 24                     | 26             | _                                | 7                                | 4             | 24                     | 26             |     | ST     | Interrupt-on-Change Inputs |

| CN8      | 14                               | 20                               | 17            | 7                      | 7              | _                                | _                                | _             | _                      | _              |     | ST     | Interrupt-on-Change Inputs |

| CN9      | _                                | 19                               | 16            | 6                      | 6              | _                                | 19                               | 16            | 6                      | 6              |     | ST     | Interrupt-on-Change Inputs |

| CN10     | _                                | _                                | _             | 27                     | 29             | _                                | _                                | _             | 27                     | 29             |     | ST     | Interrupt-on-Change Inputs |

| CN11     | 18                               | 26                               | 23            | 15                     | 16             | 18                               | 26                               | 23            | 15                     | 16             | I   | ST     | Interrupt-on-Change Inputs |

| CN12     | 17                               | 25                               | 22            | 14                     | 15             | 17                               | 25                               | 22            | 14                     | 15             | I   | ST     | Interrupt-on-Change Inputs |

**Legend:** ANA = Analog level input/output, ST = Schmitt Trigger input buffer, I<sup>2</sup>C™ = I<sup>2</sup>C/SMBus input buffer

**NOTES:**

TABLE 4-8: MCCP1 REGISTER MAP

| File Name | Addr. | Bit 15  | Bit 14                               | Bit 13  | Bit 12 | Bit 11  | Bit 10  | Bit 9   | Bit 8       | Bit 7         | Bit 6        | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-----------|-------|---------|--------------------------------------|---------|--------|---------|---------|---------|-------------|---------------|--------------|---------|---------|---------|---------|---------|---------|---------------|

| CCP1CON1L | 140h  | CCPON   | _                                    | CCPSIDL | r      | TMRSYNC | CLKSEL2 | CLKSEL1 | CLKSEL0     | TMRPS1        | TMRPS0       | T32     | CCSEL   | MOD3    | MOD2    | MOD1    | MOD0    | 0000          |

| CCP1CON1H | 142h  | OPSSRC  | RTRGEN                               | -       | -      | OPS3    | OPS2    | OPS1    | OPS0        | TRIGEN        | ONESHOT      | ALTSYNC | SYNC4   | SYNC3   | SYNC2   | SYNC1   | SYNC0   | 0000          |

| CCP1CON2L | 144h  | PWMRSEN | ASDGM                                | -       | SSDG   |         | 1       | _       | _           | ASDG7         | ASDG6        | ASDG5   | ASDG4   | ASDG3   | ASDG2   | ASDG1   | ASDG0   | 0000          |

| CCP1CON2H | 146h  | OENSYNC |                                      | OCFEN   | OCEEN  | OCDEN   | OCCEN   | OCBEN   | OCAEN       | ICGSM1        | ICGSM0       | _       | AUXOUT1 | AUXOUT0 | ICS2    | ICS1    | ICS0    | 0100          |

| CCP1CON3L | 148h  | _       |                                      | -       | -      |         | 1       | _       | _           | _             |              | DT5     | DT4     | DT3     | DT2     | DT1     | DT0     | 0000          |

| CCP1CON3H | 14Ah  | OETRIG  | OSCNT2                               | OSCNT1  | OSCNT0 |         | OUTM2   | OUTM1   | OUTM0       | _             | _            | POLACE  | POLBDF  | PSSACE1 | PSSACE0 | PSSBDF1 | PSSBDF0 | 0000          |

| CCP1STATL | 14Ch  | _       |                                      | -       | -      |         | 1       | _       | _           | CCPTRIG       | TRSET        | TRCLR   | ASEVT   | SCEVT   | ICDIS   | ICOV    | ICBNE   | 0000          |

| CCP1TMRL  | 150h  |         |                                      |         |        |         |         | MCCI    | P1 Time Ba  | se Register   | Low Word     |         |         |         |         |         |         | 0000          |

| CCP1TMRH  | 152h  |         |                                      |         |        |         |         | MCCF    | P1 Time Bas | se Register   | High Word    |         |         |         |         |         |         | 0000          |

| CCP1PRL   | 154h  |         |                                      |         |        |         |         | MCCP1   | Γime Base F | Period Regis  | ster Low Wor | rd      |         |         |         |         |         | FFFF          |

| CCP1PRH   | 156h  |         |                                      |         |        |         |         | MCCP1 T | īme Base F  | Period Regis  | ster High Wo | rd      |         |         |         |         |         | FFFF          |

| CCP1RAL   | 158h  |         |                                      |         |        |         |         | O       | utput Comp  | are 1 Data \  | Nord A       |         |         |         |         |         |         | 0000          |

| CCP1RBL   | 15Ch  |         | Output Compare 1 Data Word B         |         |        |         |         |         |             |               |              |         |         | 0000    |         |         |         |               |

| CCP1BUFL  | 160h  |         | Input Capture 1 Data Buffer Low Word |         |        |         |         |         |             |               |              |         |         |         | 0000    |         |         |               |

| CCP1BUFH  | 162h  |         |                                      | •       | •      | •       | •       | Input   | Capture 1 [ | Data Buffer I | High Word    |         |         | •       | •       |         | •       | 0000          |

$\textbf{Legend:} \quad x = \text{unknown}, \ u = \text{unchanged}, \ --= \text{unimplemented}, \ q = \text{value depends on condition}, \ r = \text{reserved}.$

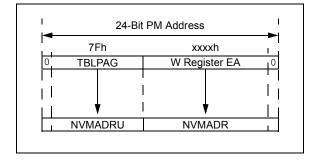

### 6.3 NVM Address Register

As with Flash program memory, the NVM Address registers, NVMADRU and NVMADR, form the 24-bit Effective Address (EA) of the selected row or word for data EEPROM operations. The NVMADRU register is used to hold the upper 8 bits of the EA, while the NVMADR register is used to hold the lower 16 bits of the EA. These registers are not mapped into the Special Function Register (SFR) space; instead, they directly capture the EA<23:0> of the last Table Write instruction that has been executed and select the data EEPROM row to erase. Figure 6-1 depicts the program memory EA that is formed for programming and erase operations.

Like program memory operations, the Least Significant bit (LSb) of NVMADR is restricted to even addresses. This is because any given address in the data EEPROM space consists of only the lower word of the program memory width; the upper word, including the uppermost "phantom byte", are unavailable. This means that the LSb of a data EEPROM address will always be '0'.

Similarly, the Most Significant bit (MSb) of NVMADRU is always '0', since all addresses lie in the user program space.

FIGURE 6-1: DATA EEPROM

ADDRESSING WITH

TBLPAG AND NVM

ADDRESS REGISTERS

#### 6.4 Data EEPROM Operations

The EEPROM block is accessed using Table Read and Write operations, similar to those used for program memory. The TBLWTH and TBLRDH instructions are not required for data EEPROM operations since the memory is only 16 bits wide (data on the lower address is valid only). The following programming operations can be performed on the data EEPROM:

- · Erase one, four or eight words

- · Bulk erase the entire data EEPROM

- · Write one word

- · Read one word

- **Note 1:** Unexpected results will be obtained if the user attempts to read the EEPROM while a programming or erase operation is underway.

- 2: The XC16 C compiler includes library procedures to automatically perform the Table Read and Table Write operations, manage the Table Pointer and write buffers, and unlock and initiate memory write sequences. This eliminates the need to create assembler macros or time critical routines in C for each application.

The library procedures are used in the code examples detailed in the following sections. General descriptions of each process are provided for users who are not using the XC16 compiler libraries.

### 8.0 INTERRUPT CONTROLLER

Note:

This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the Interrupt Controller, refer to the "PIC24F Family Reference Manual", "Interrupts" (DS39707).

The PIC24F interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the CPU. It has the following features:

- Up to Eight Processor Exceptions and Software Traps

- · Seven User-Selectable Priority Levels

- · Interrupt Vector Table (IVT) with up to 118 Vectors

- Unique Vector for Each Interrupt or Exception Source

- Fixed Priority within a Specified User Priority Level

- Alternate Interrupt Vector Table (AIVT) for Debug Support

- · Fixed Interrupt Entry and Return Latencies

### 8.1 Interrupt Vector Table (IVT)

The IVT is shown in Figure 8-1. The IVT resides in the program memory, starting at location, 000004h. The IVT contains 126 vectors, consisting of eight non-maskable trap vectors, plus up to 118 sources of interrupt. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit-wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR).

Interrupt vectors are prioritized in terms of their natural priority; this is linked to their position in the vector table. All other things being equal, lower addresses have a higher natural priority. For example, the interrupt associated with Vector 0 will take priority over interrupts at any other vector address.

PIC24FV16KM204 family devices implement non-maskable traps and unique interrupts; these are summarized in Table 8-1.

# 8.1.1 ALTERNATE INTERRUPT VECTOR TABLE (AIVT)

The Alternate Interrupt Vector Table (AIVT) is located after the IVT, as shown in Figure 8-1. Access to the AIVT is provided by the ALTIVT control bit (INTCON2<15>). If the ALTIVT bit is set, all interrupt and exception processes will use the alternate vectors instead of the default vectors. The alternate vectors are organized in the same manner as the default vectors.

The AIVT supports emulation and debugging efforts by providing a means to switch between an application and a support environment without requiring the interrupt vectors to be reprogrammed. This feature also enables switching between applications for evaluation of different software algorithms at run time. If the AIVT is not needed, the AIVT should be programmed with the same addresses used in the IVT.

#### 8.2 Reset Sequence

A device Reset is not a true exception, because the interrupt controller is not involved in the Reset process. The PIC24F devices clear their registers in response to a Reset, which forces the Program Counter (PC) to zero. The microcontroller then begins program execution at location, 000000h. The user programs a GOTO instruction at the Reset address, which redirects the program execution to the appropriate start-up routine.

Note:

Any unimplemented or unused vector locations in the IVT and AIVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

#### REGISTER 8-3: INTCON1: INTERRUPT CONTROL REGISTER 1

| R/W-0  | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| NSTDIS | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | R/W-0, HS | R/W-0, HS | R/W-0, HS | R/W-0, HS | U-0   |

|-------|-----|-----|-----------|-----------|-----------|-----------|-------|

| _     | _   | _   | MATHERR   | ADDRERR   | STKERR    | OSCFAIL   | _     |

| bit 7 |     |     |           |           |           |           | bit 0 |

| Legend:           | HS = Hardware Settable bit |                             |                    |

|-------------------|----------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |

bit 15 NSTDIS: Interrupt Nesting Disable bit

1 = Interrupt nesting is disabled0 = Interrupt nesting is enabled

bit 14-5 **Unimplemented:** Read as '0'

bit 4 MATHERR: Arithmetic Error Trap Status bit

1 = Overflow trap has occurred0 = Overflow trap has not occurred

bit 3 ADDRERR: Address Error Trap Status bit

1 = Address error trap has occurred0 = Address error trap has not occurred

bit 2 STKERR: Stack Error Trap Status bit

1 = Stack error trap has occurred0 = Stack error trap has not occurred

bit 1 OSCFAIL: Oscillator Failure Trap Status bit

1 = Oscillator failure trap has occurred0 = Oscillator failure trap has not occurred

bit 0 Unimplemented: Read as '0'

#### REGISTER 8-4: INTCON2: INTERRUPT CONTROL REGISTER 2

| R/W-0  | R-0, HSC | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|----------|-----|-----|-----|-----|-----|-------|

| ALTIVT | DISI     | _   | _   | _   | _   | _   | _     |

| bit 15 |          |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-----|-----|-----|--------|--------|--------|

| _     | _   | _   | _   | _   | INT2EP | INT1EP | INT0EP |

| bit 7 |     |     |     |     |        |        | bit 0  |

**Legend:** HSC = Hardware Settable/Clearable bit

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 ALTIVT: Enable Alternate Interrupt Vector Table bit

1 = Uses Alternate Interrupt Vector Table (AIVT)

0 = Uses standard (default) Interrupt Vector Table (IVT)

bit 14 DISI: DISI Instruction Status bit

1 = DISI instruction is active

0 = DISI instruction is not active

bit 13-3 **Unimplemented:** Read as '0'

bit 2 INT2EP: External Interrupt 2 Edge Detect Polarity Select bit

1 = Interrupt is on the negative edge0 = Interrupt is on the positive edge

bit 1 INT1EP: External Interrupt 1 Edge Detect Polarity Select bit

1 = Interrupt is on the negative edge0 = Interrupt is on the positive edge

bit 0 INTOEP: External Interrupt 0 Edge Detect Polarity Select bit

1 = Interrupt is on the negative edge0 = Interrupt is on the positive edge

#### REGISTER 8-17: IEC5: INTERRUPT ENABLE CONTROL REGISTER 5

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0   |

|-------|-----|-----|-----|-----|-----|-----|---------|

| _     | _   | _   | _   | _   | _   | _   | ULPWUIE |

| bit 7 |     |     |     |     |     |     | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-1 **Unimplemented:** Read as '0'

bit 0 **ULPWUIE:** Ultra Low-Power Wake-up Interrupt Enable bit

1 = Interrupt request is enabled0 = Interrupt request is not enabled

#### REGISTER 8-18: IEC6: INTERRUPT ENABLE CONTROL REGISTER 5

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  | R/W-0  |

|-------|-----|-----|-----|-----|-----|--------|--------|

| _     | _   | _   | _   | _   | _   | CLC2IE | CLC1IE |

| bit 7 |     |     |     |     |     |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-2 Unimplemented: Read as '0'

bit 1 CLC2IE: Configurable Logic Cell 2 Interrupt Enable bit

1 = Interrupt request is enabled0 = Interrupt request is not enabled

bit 0 CLC1IE: Configurable Logic Cell 1 Interrupt Enable bit

1 = Interrupt request is enabled0 = Interrupt request is not enabled

#### REGISTER 8-27: IPC10: INTERRUPT PRIORITY CONTROL REGISTER 10

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   |     | _   |     | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | R/W-1   | R/W-0   | R/W-0   | U-0 | U-0 | U-0 | U-0   |

|-------|---------|---------|---------|-----|-----|-----|-------|

| _     | CCT5IP2 | CCT5IP1 | CCT5IP0 | _   | _   | _   | _     |

| bit 7 |         |         |         |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-7 **Unimplemented:** Read as '0'

bit 6-4 CCT5IP<2:0>: Capture/Compare 5 Timer Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

•

.

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

bit 3-0 **Unimplemented:** Read as '0'

### 9.4 Clock Switching Operation

With few limitations, applications are free to switch between any of the four clock sources (POSC, SOSC, FRC and LPRC) under software control and at any time. To limit the possible side effects that could result from this flexibility, PIC24F devices have a safeguard lock built into the switching process.

Note: The Primary Oscillator mode has three different submodes (XT, HS and EC), which are determined by the POSCMDx Configuration bits. While an application can switch to and from Primary Oscillator mode in software, it cannot switch between the different primary submodes without reprogramming the device.

#### 9.4.1 ENABLING CLOCK SWITCHING

To enable clock switching, the FCKSM1 Configuration bit in the FOSC Configuration register must be programmed to '0'. (Refer to **Section 25.0 "Special Features"** for further details.) If the FCKSM1 Configuration bit is unprogrammed ('1'), the clock switching function and FSCM function are disabled; this is the default setting.

The NOSCx control bits (OSCCON<10:8>) do not control the clock selection when clock switching is disabled. However, the COSCx bits (OSCCON<14:12>) will reflect the clock source selected by the FNOSCx Configuration bits.

The OSWEN control bit (OSCCON<0>) has no effect when clock switching is disabled; it is held at '0' at all times.

# 9.4.2 OSCILLATOR SWITCHING SEQUENCE

At a minimum, performing a clock switch requires this basic sequence:

- If desired, read the COSCx bits (OSCCON<14:12>) to determine the current oscillator source.

- Perform the unlock sequence to allow a write to the OSCCON register high byte.

- Write the appropriate value to the NOSCx bits (OSCCON<10:8>) for the new oscillator source.

- 4. Perform the unlock sequence to allow a write to the OSCCON register low byte.

- Set the OSWEN bit to initiate the oscillator switch.

Once the basic sequence is completed, the system clock hardware responds automatically, as follows:

- The clock switching hardware compares the COSCx bits with the new value of the NOSCx bits. If they are the same, then the clock switch is a redundant operation. In this case, the OSWEN bit is cleared automatically and the clock switch is aborted.

- If a valid clock switch has been initiated, the LOCK (OSCCON<5>) and CF (OSCCON<3>) bits are cleared.

- The new oscillator is turned on by the hardware

if it is not currently running. If a crystal oscillator

must be turned on, the hardware will wait until

the OST expires. If the new source is using the

PLL, then the hardware waits until a PLL lock is

detected (LOCK = 1).

- The hardware waits for 10 clock cycles from the new clock source and then performs the clock switch.

- The hardware clears the OSWEN bit to indicate a successful clock transition. In addition, the NOSCx bits value is transferred to the COSCx bits.

- The old clock source is turned off at this time, with the exception of LPRC (if WDT, FSCM or RTCC with LPRC as a clock source is enabled) or SOSC (if SOSCEN remains enabled).

- **Note 1:** The processor will continue to execute code throughout the clock switching sequence. Timing-sensitive code should not be executed during this time.

- 2: Direct clock switches between any Primary Oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transitional clock source between the two PLL modes.

#### REGISTER 13-7: CCPxSTATL: CCPx STATUS REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R-0     | W1-0  | W1-0  | R/C-0 | R/C-0 | R/C-0 | R/C-0 | R/C-0 |

|---------|-------|-------|-------|-------|-------|-------|-------|

| CCPTRIG | TRSET | TRCLR | ASEVT | SCEVT | ICDIS | ICOV  | ICBNE |

| bit 7   |       |       |       |       |       |       | bit 0 |

Legend:C = Clearable bitR = Readable bitW1 = Write '1' onlyU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 15-8 **Unimplemented:** Read as '0'

bit 7 CCPTRIG: CCPx Trigger Status bit

1 = Timer has been triggered and is running

0 = Timer has not been triggered and is held in Reset

bit 6 TRSET: CCPx Trigger Set Request bit

Write '1' to this location to trigger the timer when TRIGEN = 1 (location always reads as '0').

bit 5 TRCLR: CCPx Trigger Clear Request bit

Write '1' to this location to cancel the timer Trigger when TRIGEN = 1 (location always reads as '0').

bit 4 ASEVT: CCPx Auto-Shutdown Event Status/Control bit

1 = A shutdown event is in progress; CCPx outputs are in the shutdown state

0 = CCPx outputs operate normally

bit 3 SCEVT: Single Edge Compare Event Status bit

1 = A single edge compare event has occurred

0 = A single edge compare event has not occurred

bit 2 ICDIS: Input Capture x Disable bit

1 = Event on Input Capture x pin (ICx) does not generate a capture event

0 = Event on Input Capture x pin will generate a capture event

bit 1 ICOV: Input Capture x Buffer Overflow Status bit

1 = The Input Capture x FIFO buffer has overflowed

0 = The Input Capture x FIFO buffer has not overflowed

bit 0 ICBNE: Input Capture x Buffer Status bit

1 = Input Capture x buffer has data available

0 = Input Capture x buffer is empty

### 14.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP)

Note:

This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on MSSP, refer to the "PIC24F Family Reference Manual".

The Master Synchronous Serial Port (MSSP) module is an 8-bit serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, Shift registers, display drivers, A/D Converters, etc. The MSSP module can operate in one of two modes:

- · Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C™)

- Full Master mode

- Slave mode (with general address call)

The SPI interface supports these modes in hardware:

- · Master mode

- · Slave mode

- · Daisy-Chaining Operation in Slave mode

- · Synchronized Slave Operation

The I<sup>2</sup>C interface supports the following modes in hardware:

- · Master mode

- · Multi-Master mode

- Slave mode with 10-Bit and 7-Bit Addressing and Address Masking

- Byte NACKing

- Selectable Address and Data Hold, and Interrupt Masking

#### 14.1 I/O Pin Configuration for SPI

In SPI Master mode, the MSSP module will assert control over any pins associated with the SDOx and SCKx outputs. This does not automatically disable other digital functions associated with the pin and may result in the module driving the digital I/O port inputs. To prevent this, the MSSP module outputs must be disconnected from their output pins while the module is in SPI Master mode. While disabling the module temporarily may be an option, it may not be a practical solution in all applications.

The SDOx and SCKx outputs for the module can be selectively disabled by using the SDOxDIS and SCKxDIS bits in the PADCFG1 register (Register 14-10). Setting the bit disconnects the corresponding output for a particular module from its assigned pin.

### REGISTER 17-5: CLCxGLSH: CLCx GATE LOGIC INPUT SELECT HIGH REGISTER (CONTINUED)

| bit 3 | G3D2T: Gate 3 Data Source 2 True Enable bit                  |

|-------|--------------------------------------------------------------|

|       | 1 = The Data Source 2 inverted signal is enabled for Gate 3  |

|       | 0 = The Data Source 2 inverted signal is disabled for Gate 3 |

| bit 2 | G3D2N: Gate 3 Data Source 2 Negated Enable bit               |

|       | 1 = The Data Source 2 inverted signal is enabled for Gate 3  |

|       | 0 = The Data Source 2 inverted signal is disabled for Gate 3 |

| bit 1 | G3D1T: Gate 3 Data Source 1 True Enable bit                  |

|       | 1 = The Data Source 1 inverted signal is enabled for Gate 3  |

|       | 0 = The Data Source 1 inverted signal is disabled for Gate 3 |

| bit 0 | G3D1N: Gate 3 Data Source 1 Negated Enable bit               |

|       | 1 = The Data Source 1 inverted signal is enabled for Gate 3  |

|       | 0 = The Data Source 1 inverted signal is disabled for Gate 3 |

# TABLE 19-4: NUMERICAL EQUIVALENTS OF VARIOUS RESULT CODES: 10-BIT FRACTIONAL FORMATS

| Vin/Vref   | 10-Bit Differential<br>Output Code<br>(11-bit result) | 16-Bit Fractional Format<br>Equivalent Decimal Valu | -     | 16-Bit Signed Fractional Fo<br>Equivalent Decimal Val |        |  |  |

|------------|-------------------------------------------------------|-----------------------------------------------------|-------|-------------------------------------------------------|--------|--|--|

| +1023/1024 | 011 1111 1111                                         | 1111 1111 1100 0000                                 | 0.999 | 0111 1111 1110 0000                                   | 0.999  |  |  |

| +1022/1024 | 011 1111 1110                                         | 1111 1111 1000 0000                                 | 0.998 | 0111 1111 1000 0000                                   | 0.998  |  |  |

|            | •••                                                   |                                                     |       |                                                       |        |  |  |

| +1/1024    | 000 0000 0001                                         | 0000 0000 0100 0000                                 | 0.001 | 0000 0000 0010 0000                                   | 0.001  |  |  |

| 0/1024     | 000 0000 0000                                         | 0000 0000 0000 0000                                 | 0.000 | 0000 0000 0000 0000                                   | 0.000  |  |  |

| -1/1024    | 101 1111 1111                                         | 0000 0000 0000 0000                                 | 0.000 | 1111 1111 1110 0000                                   | -0.001 |  |  |

|            | •••                                                   |                                                     |       |                                                       |        |  |  |

| -1023/1024 | 100 0000 0001                                         | 0000 0000 0000 0000                                 | 0.000 | 1000 0000 0010 0000                                   | -0.999 |  |  |

| -1024/1024 | 100 0000 0000                                         | 0000 0000 0000 0000                                 | 0.000 | 1000 0000 0000 0000                                   | -1.000 |  |  |

### REGISTER 21-1: AMPxCON: OP AMP x CONTROL REGISTER<sup>(1)</sup>

| R/W-0  | U-0 | R/W-0   | R/W-0  | U-0 | U-0 | U-0 | U-0   |

|--------|-----|---------|--------|-----|-----|-----|-------|

| AMPEN  | _   | AMPSIDL | AMPSLP | _   | _   | _   | _     |

| bit 15 |     |         |        |     |     |     | bit 8 |

| R/W-0  | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|--------|-----|---------|---------|---------|---------|---------|---------|

| SPDSEL | _   | NINSEL2 | NINSEL1 | NINSEL0 | PINSEL2 | PINSEL1 | PINSEL0 |

| bit 7  |     |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 AMPEN: Op Amp x Control Module Enable bit

1 = Module is enabled0 = Module is disabled

bit 14 Unimplemented: Read as '0'

bit 13 AMPSIDL: Op Amp x Peripheral Stop in Idle Mode bit

1 = Discontinues module operation when device enters Idle mode

0 = Continues module operation in Idle mode

bit 12 AMPSLP: Op Amp x Peripheral Enabled in Sleep Mode bit

1 = Continues module operation when device enters Sleep mode

0 = Discontinues module operation in Sleep mode

bit 11-8 Unimplemented: Read as '0'

bit 7 SPDSEL: Op Amp x Power/Speed Select bit

1 = Higher power and bandwidth (faster response time)

0 = Lower power and bandwidth (slower response time)

bit 6 **Unimplemented:** Read as '0'

bit 5-3 NINSEL<2:0>: Negative Op Amp Input Select bits

111 = Reserved; do not use

110 = Reserved; do not use

101 = Op amp negative input is connected to the op amp output (voltage follower)

100 = Reserved; do not use

011 = Reserved; do not use

010 = Op amp negative input is connected to the OAxIND pin

001 = Op amp negative input is connected to the OAxINB pin

000 = Op amp negative input is connected to AVss

bit 2-0 PINSEL<2:0>: Positive Op Amp Input Select bits

111 = Op amp positive input is connected to the output of the A/D input multiplexer

110 = Reserved; do not use

101 = Op amp positive input is connected to the DAC1 output for OA1 (DAC2 output for OA2)

100 = Reserved; do not use

011 = Reserved; do not use

010 = Op amp positive input is connected to the OAxINC pin

001 = Op amp positive input is connected to the OAxINA pin

000 = Op amp positive input is connected to AVss

Note 1: This register is available only on PIC24F(V)16KM2XX devices.

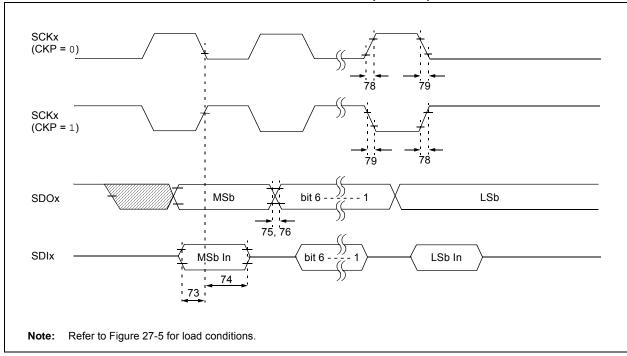

FIGURE 27-11: EXAMPLE SPI MASTER MODE TIMING (CKE = 0)

TABLE 27-29: EXAMPLE SPI MODE REQUIREMENTS (MASTER MODE, CKE = 0)

| Param<br>No. | Symbol                | Characteristic                             | Min | Max | Units | Conditions |

|--------------|-----------------------|--------------------------------------------|-----|-----|-------|------------|

| 73           | TDIV2scH,<br>TDIV2scL | Setup Time of SDIx Data Input to SCKx Edge | 20  | _   | ns    |            |

| 74           | TscH2DIL,<br>TscL2DIL | Hold Time of SDIx Data Input to SCKx Edge  | 40  | _   | ns    |            |

| 75           | TDOR                  | SDOx Data Output Rise Time                 | _   | 25  | ns    |            |

| 76           | TDOF                  | SDOx Data Output Fall Time                 | _   | 25  | ns    |            |

| 78           | TscR                  | SCKx Output Rise Time (Master mode)        | _   | 25  | ns    |            |

| 79           | TscF                  | SCKx Output Fall Time (Master mode)        | _   | 25  | ns    |            |

|              | FSCK                  | SCKx Frequency                             | _   | 10  | MHz   |            |

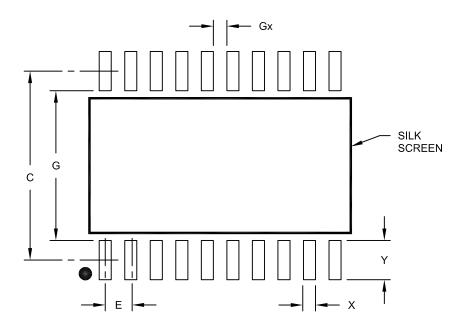

20-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                          | Units |            |      |      |  |

|--------------------------|-------|------------|------|------|--|

| Dimension                | MIN   | NOM        | MAX  |      |  |

| Contact Pitch            | Е     | E 1.27 BSC |      |      |  |

| Contact Pad Spacing      | С     |            | 9.40 |      |  |

| Contact Pad Width (X20)  | Х     |            |      | 0.60 |  |

| Contact Pad Length (X20) | Υ     |            |      | 1.95 |  |

| Distance Between Pads    | Gx    | 0.67       |      |      |  |

| Distance Between Pads    | G     | 7.45       |      |      |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2094A

| CMSTAT (Comparator Status)                   | 238 |

|----------------------------------------------|-----|

| CMxCON (Comparator x Control)                |     |

| CORCON (CPU Control)                         |     |

| CORCON (CPU Core Control)                    | 90  |

| CTMUCON1H (CTMU Control 1 High)              | 246 |

| CTMUCON1L (CTMU Control 1 Low)               | 244 |

| CTMUCON2L (CTMU Control 2 Low)               |     |

| CVRCON (Comparator Voltage                   |     |

| Reference Control)                           | 240 |

| DACxCON (DACx Control)                       |     |

| DEVID (Device ID)                            | 255 |

| DEVREV (Device Revision)                     | 256 |

| FBS (Boot Segment Configuration)             |     |

| FGS (General Segment Configuration)          |     |

| FICD (In-Circuit Debugger Configuration)     |     |

| FOSC (Oscillator Configuration)              |     |

| FOSCSEL (Oscillator Selection Configuration) |     |

| FPOR (Reset Configuration)                   |     |

| FWDT (Watchdog Timer Configuration)          |     |

| HLVDCON (High/Low-Voltage Detect Control)    |     |

| IEC0 (Interrupt Enable Control 0)            |     |

| IEC1 (Interrupt Enable Control 1)            | 99  |

| IEC2 (Interrupt Enable Control 2)            |     |

| IEC3 (Interrupt Enable Control 3)            |     |

| IEC4 (Interrupt Enable Control 4)            |     |

| IEC5 (Interrupt Enable Control 5)            |     |

| IEC6 (Interrupt Enable Control 6)            |     |

| IFS0 (Interrupt Flag Status 0)               |     |

| IFS1 (Interrupt Flag Status 1)               |     |

| IFS2 (Interrupt Flag Status 2)               |     |

| IFS3 (Interrupt Flag Status 3)               | 95  |

| IFS4 (Interrupt Flag Status 4)               | 96  |

| IFS5 (Interrupt Flag Status 5)               |     |

| IFS6 (Interrupt Flag Status 6)               | 97  |

| INTCON1 (Interrupt Control 1)                |     |

| INTCON2 (Interrupt Control 2)                |     |

| INTTREG (Interrupt Control and Status)       |     |

| IPC0 (Interrupt Priority Control 0)          |     |

| IPC1 (Interrupt Priority Control 1)          |     |

| IPC10 (Interrupt Priority Control 10)        |     |

| IPC12 (Interrupt Priority Control 12)        |     |

| IPC15 (Interrupt Priority Control 15)        |     |

| IPC16 (Interrupt Priority Control 16)        |     |

| IPC18 (Interrupt Priority Control 18)        |     |

| IPC19 (Interrupt Priority Control 19)        | 116 |

| IPC2 (Interrupt Priority Control 2)          | 105 |

| IPC20 (Interrupt Priority Control 20)        |     |

| IPC24 (Interrupt Priority Control 24)        | 117 |

| IPC3 (Interrupt Priority Control 3)          |     |

| IPC4 (Interrupt Priority Control 4)          | 107 |

| IPC5 (Interrupt Priority Control 5)          | 108 |

| IPC6 (Interrupt Priority Control 6)          |     |

| IPC7 (Interrupt Priority Control 7)          | 110 |

| MINSEC (RTCC Minutes and Seconds Value)      |     |

| MTHDY (RTCC Month and Day Value)             |     |

| NVMCON (Flash Memory Control)                | 69  |

| NVMCON (Nonvolatile Memory Control)          | 74  |

| OSCCON (Oscillator Control)                  |     |

| OSCTUN (FRC Oscillator Tune)                 |     |

| PADCEG1 (Pad Configuration Control)                     | 1/1    |

|---------------------------------------------------------|--------|

| RCFGCAL (RTCC Calibration                               |        |

| and Configuration)                                      |        |

| RCON (Reset Control)                                    |        |

| REFOCON (Reference Oscillator Control)                  | 129    |

| RTCCSWT (RTCC Control/Sample                            |        |

| Window Timer)                                           |        |

| RTCPWC (RTCC Configuration 2)                           | 185    |

| SR (ALU STATUS)                                         | 38, 89 |

| SSPxADD (MSSPx Slave Address/Baud                       |        |

| Rate Generator)                                         |        |

| SSPxCON1 (MSSPx Control 1, I <sup>2</sup> C Mode)       | 166    |

| SSPxCON1 (MSSPx Control 1, SPI Mode)                    | 165    |

| SSPxCON2 (MSSPx Control 2, I <sup>2</sup> C Mode)       | 167    |

| SSPxCON3 (MSSPx Control 3, I <sup>2</sup> C Mode)       | 169    |

| SSPxCON3 (MSSPx Control 3, SPI Mode)                    |        |

| SSPxMSK (I <sup>2</sup> C Slave Address Mask)           | 170    |

| SSPxSTAT (MSSPx Status, I <sup>2</sup> C Mode)          | 163    |

| SSPxSTAT (MSSPx Status, SPI Mode)                       | 162    |

| T1CON (Timer1 Control)                                  |        |

| ULPWCON (ULPWU Control)                                 | 133    |

| UxMODE (UARTx Mode)                                     | 176    |

| UxRXREG (UARTx Receive)                                 |        |

| UxSTA (UARTx Status and Control)                        |        |

| UxTXREG (UARTx Transmit)                                |        |

| WKDYHR (RTCC Weekday and Hours Value)                   |        |

| YEAR (RTCC Year Value)                                  |        |

| Resets                                                  | 107    |

| Brown-out Reset (BOR)                                   | 83     |

| Clock Source Selection                                  |        |

| Delay Times                                             |        |

| Device Times                                            |        |

| Low-Power BOR (LPBOR)                                   |        |

| RCON Flag Operation                                     |        |

| SFR States                                              |        |

| Retention Regulator (RETREG)                            |        |

| Revision History                                        |        |

| RTCC                                                    | 525    |

| Alarm Configuration                                     | 102    |

| Alarm Mask Settings (figure)                            | 103    |

| ALRMVAL Register Mappings                               |        |

| Calibration                                             |        |

| Module Registers                                        |        |

| Mapping                                                 |        |

| Clock Source Selection                                  |        |

|                                                         |        |

| Write Lock                                              |        |

| Power Control                                           |        |

| RTCVAL Register Mappings                                |        |

| Source Clock                                            | 181    |

| S                                                       |        |

|                                                         |        |

| Serial Peripheral Interface. See SPI Mode.<br>SFR Space | 11     |

| Software Stack                                          |        |

|                                                         | 03     |

| SPI Mode                                                | 150    |

| I/O Pin Configuration                                   | 159    |

U

| T                                                    |       |

|------------------------------------------------------|-------|

| Timer1                                               | . 141 |

| Timing Diagrams                                      |       |

| A/D Conversion                                       | . 295 |

| Brown-out Reset Characteristics                      | . 284 |

| Capture/Compare/PWM (MCCPx, SCCPx)                   | . 285 |

| CLKO and I/O Timing                                  |       |

| Example SPI Master Mode (CKE = 0)                    | . 286 |

| Example SPI Master Mode (CKE = 1)                    | . 287 |

| Example SPI Slave Mode (CKE = 0)                     | . 288 |

| Example SPI Slave Mode (CKE = 1)                     | . 289 |

| External Clock                                       | . 280 |

| I <sup>2</sup> C Bus Data                            | . 290 |

| I <sup>2</sup> C Bus Start/Stop Bits                 |       |

| MSSPx I <sup>2</sup> C Bus Data                      |       |

| MSSPx I <sup>2</sup> C Bus Start/Stop Bits           | . 292 |

| Reset, Watchdog Timer. Oscillator Start-up Timer,    |       |

| Power-up Timer Characteristics                       | . 283 |

| Timing Requirements                                  |       |

| Capture/Compare/PWM (MCCPx, SCCPx)                   | . 285 |

| Comparator                                           |       |

| Comparator Voltage Reference Settling Time           |       |

| I <sup>2</sup> C Bus Data (Slave Mode)               |       |

| I <sup>2</sup> C Bus Data Requirements (Master Mode) |       |

| I <sup>2</sup> C Bus Start/Stop Bits (Master Mode)   |       |

| I <sup>2</sup> C Bus Start/Stop Bits (Slave Mode)    |       |

| SPI Mode (Master Mode, CKE = 0)                      |       |

| SPI Mode (Master Mode, CKE = 1)                      |       |

| SPI Mode (Slave Mode, CKE = 0)                       |       |

| SPI Slave Mode (CKE = 1)                             | . 289 |

| UART                                                      |     |

|-----------------------------------------------------------|-----|

| Baud Rate Generator (BRG)                                 | 174 |

| Break and Sync Transmit Sequence                          | 175 |

| IrDA Support<br>Operation of UxCTS and UxRTS Control Pins | 175 |

| Operation of UxCTS and UxRTS Control Pins                 | 175 |

| Receiving in 8-Bit or 9-Bit Data Mode                     |     |

| Transmitting in 8-Bit Data Mode                           |     |

| Transmitting in 9-Bit Data Mode                           | 175 |

| Universal Asynchronous Receiver                           |     |

| Transmitter (UART)                                        | 173 |

| V                                                         |     |

| Voltage Regulator (VREG)                                  | 134 |

| Voltage-Frequency Graph                                   |     |

| (PIC24F16KM204 Extended)                                  | 267 |

| Voltage-Frequency Graph                                   |     |

| (PIC24F16KM204 Industrial)                                | 266 |

| Voltage-Frequency Graph                                   |     |

| (PIC24FV16KM204 Extended)                                 | 267 |

| Voltage-Frequency Graph                                   |     |

| (PIC24FV16KM204 Industrial)                               | 266 |

| W                                                         |     |

| Watchdog Timer (WDT)                                      | 257 |

| Windowed Operation                                        |     |

| WWW Address                                               | 332 |

| WWW. On-Line Support                                      | 11  |