Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0 0              |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                     |

| Number of I/O              | 37                                                                             |

| Program Memory Size        | 16KB (5.5K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | 512 x 8                                                                        |

| RAM Size                   | 1K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5V                                                                        |

| Data Converters            | A/D 22x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-TQFP                                                                        |

| Supplier Device Package    | 44-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fv16km104t-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.0 DEVICE OVERVIEW

This document contains device-specific information for the following devices:

- PIC24FV08KM101 PIC24F08KM101

- PIC24FV08KM102

- PIC24F08KM102

PIC24F16KM102

- PIC24FV16KM102

- PIC24FV16KM104 PIC24F16KM104

- PIC24FV08KM202 PIC24F08KM202

- PIC24FV08KM204 PIC24F08KM204

- PIC24FV16KM202

- PIC24F16KM202

- PIC24FV16KM204 PIC24F16KM204

The PIC24FV16KM204 family introduces many new analog features to the extreme low-power Microchip devices. This is a 16-bit microcontroller family with a broad peripheral feature set and enhanced computational performance. This family also offers a new migration option for those high-performance applications which may be outgrowing their 8-bit platforms, but do not require the numerical processing power of a Digital Signal Processor (DSC).

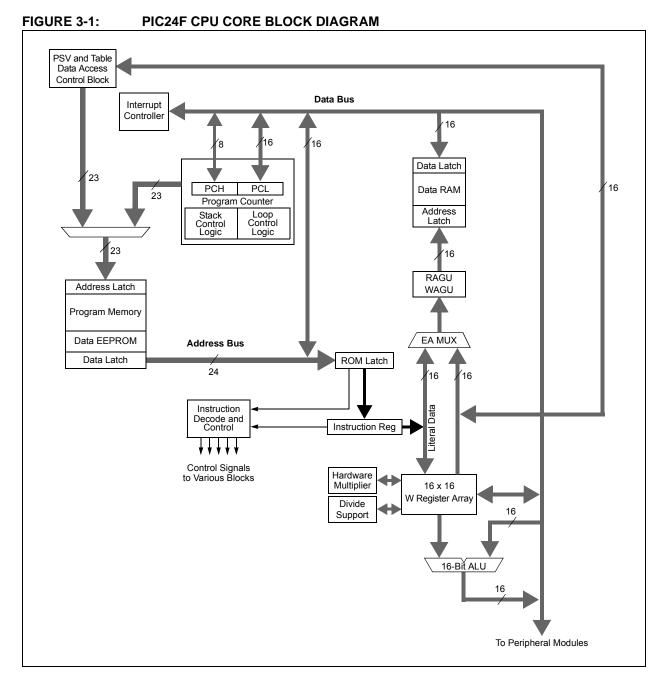

## 1.1 Core Features

## 1.1.1 16-BIT ARCHITECTURE

Central to all PIC24F devices is the 16-bit modified Harvard architecture, first introduced with Microchip's  $dsPIC^{\textcircled{B}}$  Digital Signal Controllers. The PIC24F CPU core offers a wide range of enhancements, such as:

- 16-bit data and 24-bit address paths with the ability to move information between data and memory spaces

- Linear Addressing of up to 16 Mbytes (program space) and 16 Kbytes (data)

- A 16-element working register array with built-in software stack support

- A 17 x 17 hardware multiplier with support for integer math

- Hardware support for 32-bit by 16-bit division

- An instruction set that supports multiple addressing modes and is optimized for high-level languages, such as C

- Operational performance up to 16 MIPS

## 1.1.2 POWER-SAVING TECHNOLOGY

All of the devices in the PIC24FV16KM204 family incorporate a range of features that can significantly reduce power consumption during operation. Key features include:

- On-the-Fly Clock Switching, to allow the device clock to be changed under software control to the Timer1 source or the internal, low-power RC Oscillator during operation, allowing users to incorporate power-saving ideas into their software designs.

- Doze Mode Operation, when timing-sensitive applications, such as serial communications, require the uninterrupted operation of peripherals, the CPU clock speed can be selectively reduced, allowing incremental power savings without missing a beat.

- Instruction-Based Power-Saving Modes, to allow the microcontroller to suspend all operations or selectively shut down its core while leaving its peripherals active with a single instruction in software.

## 1.1.3 OSCILLATOR OPTIONS AND FEATURES

The PIC24FV16KM204 family offers five different oscillator options, allowing users a range of choices in developing application hardware. These include:

- Two Crystal modes using crystals or ceramic resonators.

- Two External Clock (EC) modes offering the option of a divide-by-2 clock output.

- Two Fast Internal Oscillators (FRCs), one with a nominal 8 MHz output and the other with a nominal 500 kHz output. These outputs can also be divided under software control to provide clock speed as low as 31 kHz or 2 kHz.

- A Phase Locked Loop (PLL) frequency multiplier, available to the external oscillator modes and the 8 MHz FRC Oscillator, which allows clock speeds of up to 32 MHz.

- A separate internal RC Oscillator (LPRC) with a fixed 31 kHz output, which provides a low-power option for timing-insensitive applications.

The internal oscillator block also provides a stable reference source for the Fail-Safe Clock Monitor (FSCM). This option constantly monitors the main clock source against a reference signal provided by the internal oscillator and enables the controller to switch to the internal oscillator, allowing for continued low-speed operation or a safe application shutdown.

### TABLE 1-2: DEVICE FEATURES FOR THE PIC24F16KM104 FAMILY

|                                                     |                                          |                    |                       | 1                                        |

|-----------------------------------------------------|------------------------------------------|--------------------|-----------------------|------------------------------------------|

| Features                                            | PIC24F16KM104                            | PIC24F16KM102      | PIC24F08KM102         | PIC24F08KM101                            |

| Operating Frequency                                 |                                          | DC-3               | 2 MHz                 |                                          |

| Program Memory (bytes)                              | 16K                                      | 16K                | 8K                    | 8K                                       |

| Program Memory (instructions)                       | 5632                                     | 5632               | 2816                  | 2816                                     |

| Data Memory (bytes)                                 |                                          | 10                 | 24                    |                                          |

| Data EEPROM Memory (bytes)                          |                                          | 5                  | 12                    |                                          |

| Interrupt Sources (soft vectors/NMI traps)          |                                          | 25 (2              | 21/4)                 |                                          |

| Voltage Range                                       |                                          | 1.8-               | 3.6V                  |                                          |

| I/O Ports                                           | PORTA<11:0><br>PORTB<15:0><br>PORTC<9:0> | PORTA<br>PORTB     |                       | PORTA<6:0><br>PORTB<15:12,9:7,<br>4,2:0> |

| Total I/O Pins                                      | 38                                       | 24                 | ŀ                     | 18                                       |

| Timers                                              | (One 16-bit timer, t                     |                    | 5<br>Ps with up to tv | vo 16/32 timers each)                    |

| Capture/Compare/PWM modules<br>MCCP<br>SCCP         |                                          |                    | 1                     |                                          |

| Serial Communications<br>MSSP<br>UART               |                                          |                    | 1                     |                                          |

| Input Change Notification Interrupt                 | 37                                       | 23                 | }                     | 17                                       |

| 12-Bit Analog-to-Digital Module<br>(input channels) | 22                                       | 19                 | )                     | 16                                       |

| Analog Comparators                                  |                                          |                    | 1                     |                                          |

| 8-Bit Digital-to-Analog Converters                  |                                          | -                  | _                     |                                          |

| Operational Amplifiers                              |                                          | -                  | _                     |                                          |

| Charge Time Measurement Unit (CTMU)                 |                                          | Y                  | es                    |                                          |

| Real-Time Clock and Calendar (RTCC)                 |                                          | -                  | _                     |                                          |

| Configurable Logic Cell (CLC)                       |                                          |                    | 1                     |                                          |

| Resets (and delays)                                 |                                          |                    |                       | , Illegal Opcode,<br>tion Word Mismatch  |

| Instruction Set                                     | 76 Base Inst                             | ructions, Multiple | e Addressing N        | Iode Variations                          |

| Packages                                            | 44-Pin<br>QFN/TQFP,<br>48-Pin UQFN       | 28-F<br>SPDIP/SSOP |                       | 20-Pin<br>SOIC/SSOP/PDIP                 |

## 2.4.1 CONSIDERATIONS FOR CERAMIC CAPACITORS

In recent years, large value, low-voltage, surface-mount ceramic capacitors have become very cost effective in sizes up to a few tens of microfarad. The low-ESR, small physical size and other properties make ceramic capacitors very attractive in many types of applications.

Ceramic capacitors are suitable for use with the internal voltage regulator of this microcontroller. However, some care is needed in selecting the capacitor to ensure that it maintains sufficient capacitance over the intended operating range of the application.

Typical low-cost, 10  $\mu$ F ceramic capacitors are available in X5R, X7R and Y5V dielectric ratings (other types are also available, but are less common). The initial tolerance specifications for these types of capacitors are often specified as ±10% to ±20% (X5R and X7R), or -20%/+80% (Y5V). However, the effective capacitance that these capacitors provide in an application circuit will also vary based on additional factors, such as the applied DC bias voltage and the temperature. The total in-circuit tolerance is, therefore, much wider than the initial tolerance specification.

The X5R and X7R capacitors typically exhibit satisfactory temperature stability (ex:  $\pm 15\%$  over a wide temperature range, but consult the manufacturer's data sheets for exact specifications). However, Y5V capacitors typically have extreme temperature tolerance specifications of  $\pm 22\%/-82\%$ . Due to the extreme temperature tolerance, a 10 µF nominal rated Y5V type capacitor may not deliver enough total capacitance to meet minimum internal voltage regulator stability and transient response requirements. Therefore, Y5V capacitors are not recommended for use with the internal regulator if the application must operate over a wide temperature range.

In addition to temperature tolerance, the effective capacitance of large value ceramic capacitors can vary substantially, based on the amount of DC voltage applied to the capacitor. This effect can be very significant, but is often overlooked or is not always documented.

A typical DC bias voltage vs. capacitance graph for X7R type capacitors is shown in Figure 2-4.

#### DC BIAS VOLTAGE vs. FIGURE 2-4: CAPACITANCE **CHARACTERISTICS** Capacitance Change (%) 0 -10 16V Capacitor -20 -30 -40 10V Capacitor -50 -60 -70 6.3V Capacitor -80 -9 10 11 12 13 2 8 15 16 DC Bias Voltage (VDC)

When selecting a ceramic capacitor to be used with the internal voltage regulator, it is suggested to select a high-voltage rating, so that the operating voltage is a small percentage of the maximum rated capacitor voltage. For example, choose a ceramic capacitor rated at 16V for the 3.3V or 2.5V core voltage. Suggested capacitors are shown in Table 2-1.

## 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of ohms, not to exceed 100Ω.

Pull-up resistors, series diodes, and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits, and pins, Voltage Input High (VIH) and Voltage Input Low (VIL) requirements.

For device emulation, ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins), programmed into the device, matches the physical connections for the ICSP to the Microchip debugger/emulator tool.

For more information on available Microchip development tools connection requirements, refer to **Section 26.0 "Development Support"**.

| Register(s) Name | Description                                    |

|------------------|------------------------------------------------|

| W0 through W15   | Working Register Array                         |

| PC               | 23-Bit Program Counter                         |

| SR               | ALU STATUS Register                            |

| SPLIM            | Stack Pointer Limit Value Register             |

| TBLPAG           | Table Memory Page Address Register             |

| PSVPAG           | Program Space Visibility Page Address Register |

| RCOUNT           | Repeat Loop Counter Register                   |

| CORCON           | CPU Control Register                           |

### TABLE 4-6: TIMER1 REGISTER MAP

|           |       |        | -                                                                                                                                                                 | -                    |        |        |        |                |        |              |       |       |       |       |       |       |       |               |

|-----------|-------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------|--------|--------|----------------|--------|--------------|-------|-------|-------|-------|-------|-------|-------|---------------|

| File Name | Addr. | Bit 15 | Bit 14                                                                                                                                                            | Bit 13               | Bit 12 | Bit 11 | Bit 10 | Bit 9          | Bit 8  | Bit 7        | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| TMR1      | 100h  |        |                                                                                                                                                                   | Timer1 Register xxxx |        |        |        |                |        |              |       |       |       |       |       |       |       |               |

| PR1       | 102h  |        |                                                                                                                                                                   |                      |        |        |        |                | Timer1 | Period Regis | ster  |       |       |       |       |       |       | FFFF          |

| T1CON     | 104h  | TON    | -         TSIDL         -         -         TECS1         TECS0         -         TGATE         TCKPS0         -         TSYNC         TCS         -         0000 |                      |        |        |        |                |        |              |       |       |       |       |       |       |       |               |

| Lanandi   |       |        | le ave a a d                                                                                                                                                      |                      |        |        |        | and the second |        |              |       |       |       |       |       |       |       |               |

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition, r = reserved.

### TABLE 4-7: CLC1-2 REGISTER MAP

| File Name               | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| CLC1CONL                | 122h  | LCEN   | —      | _      | —      | INTP   | INTN   | —     | —     | LCOE  | LCOUT | LCPOL | —     | _     | MODE2 | MODE1 | MODE0 | 0000          |

| CLC1CONH                | 124h  | _      | _      |        | _      | _      | _      | _     | _     | _     | _     | _     | _     | G4POL | G3POL | G2POL | G1POL | 0000          |

| CLC1SEL                 | 126h  | _      | DS42   | DS41   | DS40   |        | DS32   | DS31  | DS30  | —     | DS22  | DS21  | DS20  | _     | DS12  | DS11  | DS10  | 0000          |

| CLC1GLSL                | 12Ah  | G2D4T  | G2D4N  | G2D3T  | G2D3N  | G2D2T  | G2D2N  | G2D1T | G2D1N | G1D4T | G1D4N | G1D3T | G1D3N | G1D2T | G1D2N | G1D1T | G1D1N | 0000          |

| CLC1GLSH                | 12Ch  | G4D4T  | G4D4N  | G4D3T  | G4D3N  | G4D2T  | G4D2N  | G4D1T | G4D1N | G3D4T | G3D4N | G3D3T | G3D3N | G3D2T | G3D2N | G3D1T | G3D1N | 0000          |

| CLC2CONL <sup>(1)</sup> | 12Eh  | LCEN   | _      | -      | _      | INTP   | INTN   | _     | _     | LCOE  | LCOUT | LCPOL | —     | _     | MODE2 | MODE1 | MODE0 | 0000          |

| CLC2CONH <sup>(1)</sup> | 130h  | —      | —      | _      | —      | _      | _      | —     | _     | _     | _     | _     | —     | G4POL | G3POL | G2POL | G1POL | 0000          |

| CLC2SEL <sup>(1)</sup>  | 132h  | —      | DS42   | DS41   | DS40   | _      | DS32   | DS31  | DS30  | _     | DS22  | DS21  | DS20  | —     | DS12  | DS11  | DS10  | 0000          |

| CLC2GLSL <sup>(1)</sup> | 136h  | G2D4T  | G2D4N  | G2D3T  | G2D3N  | G2D2T  | G2D2N  | G2D1T | G2D1N | G1D4T | G1D4N | G1D3T | G1D3N | G1D2T | G1D2N | G1D1T | G1D1N | 0000          |

| CLC2GLSH <sup>(1)</sup> | 138h  | G4D4T  | G4D4N  | G4D3T  | G4D3N  | G4D2T  | G4D2N  | G4D1T | G4D1N | G3D4T | G3D4N | G3D3T | G3D3N | G3D2T | G3D2N | G3D1T | G3D1N | 0000          |

**Legend:** x = unknown, u = unchanged, --- = unimplemented, q = value depends on condition, r = reserved.

Note 1: These registers are available only on PIC24F(V)16KM2XX devices.

### TABLE 4-11: SCCP4 REGISTER MAP

| File Name                | Addr. | Bit 15  | Bit 14                                                                                        | Bit 13  | Bit 12 | Bit 11  | Bit 10  | Bit 9     | Bit 8       | Bit 7        | Bit 6       | Bit 5  | Bit 4   | Bit 3   | Bit 2   | Bit 1  | Bit 0  | All<br>Resets |

|--------------------------|-------|---------|-----------------------------------------------------------------------------------------------|---------|--------|---------|---------|-----------|-------------|--------------|-------------|--------|---------|---------|---------|--------|--------|---------------|

| CCP4CON1L <sup>(1)</sup> | 1ACh  | CCPON   | _                                                                                             | CCPSIDL | r      | TMRSYNC | CLKSEL2 | CLKSEL1   | CLKSEL0     | TMRPS1       | TMRPS0      | T32    | CCSEL   | MOD3    | MOD2    | MOD1   | MOD0   | 0000          |

| CCP4CON1H(1)             | 1AEh  | OPSSRC  | SSRC RTRGEN IOPS3 IOPS2 IOPS1 IOPS0 TRIGEN ONESHOT ALTSYNC SYNC4 SYNC3 SYNC2 SYNC1 SYNC0 0000 |         |        |         |         |           |             |              |             |        |         | 0000    |         |        |        |               |

| CCP4CON2L <sup>(1)</sup> | 1B0h  | PWMRSEN | ASDGM                                                                                         | _       | SSDG   | _       | _       | _         | _           | ASDG7        | ASDG6       | ASDG5  | ASDG4   | ASDG3   | ASDG2   | ASDG1  | ASDG0  | 0000          |

| CCP4CON2H <sup>(1)</sup> | 1B2h  | OENSYNC | _                                                                                             | _       | _      | _       | _       | _         | OCAEN       | ICGSM1       | ICGSM0      | _      | AUXOUT1 | AUXOUT0 | ICSEL2  | ICSEL1 | ICSEL0 | 0100          |

| CCP4CON3H <sup>(1)</sup> | 1B6h  | OETRIG  | OSCNT2                                                                                        | OSCNT1  | OSCNT0 | _       | _       | _         | —           | _            | _           | POLACE | _       | PSSACE1 | PSSACE0 | _      | —      | 0000          |

| CCP4STATL <sup>(1)</sup> | 1B8h  | _       | CCPTRIG TRSET TRCLR ASEVT SCEVT ICDIS ICOV ICBNE 0000                                         |         |        |         |         |           |             |              |             |        |         | 0000    |         |        |        |               |

| CCP4TMRL <sup>(1)</sup>  | 1BCh  |         |                                                                                               |         |        |         |         | SCCP4     | 1 Time Base | Register Lo  | ow Word     |        |         |         |         |        |        | 0000          |

| CCP4TMRH <sup>(1)</sup>  | 1BEh  |         |                                                                                               |         |        |         |         | SCCP4     | Time Base   | Register Hi  | gh Word     |        |         |         |         |        |        | 0000          |

| CCP4PRL <sup>(1)</sup>   | 1C0h  |         |                                                                                               |         |        |         |         | SCCP4 Tir | ne Base Pe  | riod Registe | er Low Word |        |         |         |         |        |        | FFFF          |

| CCP4PRH <sup>(1)</sup>   | 1C2h  |         |                                                                                               |         |        |         |         | SCCP4 Tir | ne Base Pe  | riod Registe | r High Word |        |         |         |         |        |        | FFFF          |

| CCP4RAL <sup>(1)</sup>   | 1C4h  |         |                                                                                               |         |        |         |         | Out       | put Compar  | e 4 Data Wo  | ord A       |        |         |         |         |        |        | 0000          |

| CCP4RBL <sup>(1)</sup>   | 1C8h  |         | Output Compare 4 Data Word B 0000                                                             |         |        |         |         |           |             |              |             |        |         |         |         |        |        |               |

| CCP4BUFL <sup>(1)</sup>  | 1CCh  |         | Input Capture 4 Data Buffer Low Word 0000                                                     |         |        |         |         |           |             |              |             |        |         |         |         |        |        |               |

| CCP4BUFH <sup>(1)</sup>  | 1CEh  |         | Input Capture 4 Data Buffer High Word 0000                                                    |         |        |         |         |           |             |              |             |        |         |         |         |        |        |               |

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

**Note 1:** These registers are available only on PIC24F(V)16KM2XX devices.

#### TABLE 4-21: PORTA REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 <sup>(4,5)</sup> | Bit 10 <sup>(4,5)</sup> | Bit 9 <sup>(4,5)</sup> | Bit 8 <sup>(4,5)</sup> | Bit 7 <sup>(4)</sup> | Bit 6 <sup>(3)</sup> | Bit 5 <sup>(2)</sup> | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets       |

|-----------|-------|--------|--------|--------|--------|-------------------------|-------------------------|------------------------|------------------------|----------------------|----------------------|----------------------|--------|--------|--------|--------|--------|---------------------|

| TRISA     | 2C0h  |        | _      | _      | _      | TRISA11                 | TRISA10                 | TRISA9                 | TRISA8                 | TRISA7               | TRISA6               | _                    | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 0FDF <sup>(1)</sup> |

| PORTA     | 2C2h  | _      | —      | —      |        | RA11                    | RA10                    | RA9                    | RA8                    | RA7                  | RA6                  | RA5                  | RA4    | RA3    | RA2    | RA1    | RA0    | xxxx                |

| LATA      | 2C4h  | _      | —      | —      |        | LATA11                  | LATA10                  | LATA9                  | LATA8                  | LATA7                | LATA6                | _                    | LATA4  | LATA3  | LATA2  | LATA1  | LATA0  | xxxx                |

| ODCA      | 2C6h  | _      | —      | _      | _      | ODA11                   | ODA10                   | ODA9                   | ODA8                   | ODA7                 | ODA6                 | _                    | ODA4   | ODA3   | ODA2   | ODA1   | ODA0   | 0000                |

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition, r = reserved.

Note 1: Reset value depends on the device type; the PIC24F16KM204 value is shown.

2: These bits are only available when MCLRE (FPOR<7>) = 0.

3: These bits are not implemented in FV devices.

4: These bits are not implemented in 20-pin devices.

5: These bits are not implemented in 28-pin devices.

### TABLE 4-22: PORTB REGISTER MAP

| File Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11 <sup>(2)</sup> | Bit 10 <sup>(2)</sup> | Bit 9  | Bit 8  | Bit 7  | Bit 6 <sup>(2)</sup> | Bit 5 <sup>(2)</sup> | Bit 4  | Bit 3 <sup>(2)</sup> | Bit 2  | Bit 1  | Bit 0  | All<br>Resets       |

|-----------|-------|---------|---------|---------|---------|-----------------------|-----------------------|--------|--------|--------|----------------------|----------------------|--------|----------------------|--------|--------|--------|---------------------|

| TRISB     | 2C8h  | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11               | TRISB10               | TRISB9 | TRISB8 | TRISB7 | TRISB6               | TRISB5               | TRISB4 | TRISB3               | TRISB2 | TRISB1 | TRISB0 | <sub>FFFF</sub> (1) |

| PORTB     | 2CAh  | RB15    | RB14    | RB13    | RB12    | RB11                  | RB10                  | RB9    | RB8    | RB7    | RB6                  | RB5                  | RB4    | RB3                  | RB2    | RB1    | RB0    | xxxx                |

| LATB      | 2CCh  | LATB15  | LATB14  | LATB13  | LATB12  | LATB11                | LATB10                | LATB9  | LATB8  | LATB7  | LATB6                | LATB5                | LATB4  | LATB3                | LATB2  | LATB1  | LATB0  | xxxx                |

| ODCB      | 2CEh  | ODB15   | ODB14   | ODB13   | ODB12   | ODB11                 | ODB10                 | ODB9   | ODB8   | ODB7   | ODB6                 | ODB5                 | ODB4   | ODB3                 | ODB2   | ODB1   | ODB0   | 0000                |

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition, r = reserved.

Note 1: Reset value depends on the device type; the PIC24F16KM204 value is shown.

2: These bits are not implemented in 20-pin devices.

### TABLE 4-23: PORTC REGISTER MAP

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 <sup>(2,3)</sup> | Bit 8 <sup>(2,3)</sup> | Bit 7 <sup>(2,3)</sup> | Bit 6 <sup>(2,3)</sup> | Bit 5 <sup>(2,3)</sup> | Bit 4 <sup>(2,3)</sup> | Bit 3 <sup>(2,3)</sup> | Bit 2 <sup>(2,3)</sup> | Bit 1 <sup>(2,3)</sup> | Bit 0 <sup>(2,3)</sup> | All<br>Resets       |

|--------------|-------|--------|--------|--------|--------|--------|--------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|---------------------|

| TRISC        | 2D0h  | _      | _      |        | _      | —      | _      | TRISC9                 | TRISC8                 | TRISC7                 | TRISC6                 | TRISC5                 | TRISC4                 | TRISC3                 | TRISC2                 | TRISC1                 | TRISC0                 | 03FF <sup>(1)</sup> |

| PORTC        | 2D2h  | —      | _      | _      | -      | —      | _      | RC9                    | RC8                    | RC7                    | RC6                    | RC5                    | RC4                    | RC3                    | RC2                    | RC1                    | RC0                    | xxxx                |

| LATTC        | 2D4h  | —      | _      | _      | -      | —      | _      | LATC9                  | LATC8                  | LATC7                  | LATC6                  | LATC5                  | LATC4                  | LATC3                  | LATC2                  | LATC1                  | LATC0                  | xxxx                |

| ODCC         | 2D6h  | _      | _      | —      | -      | —      | _      | ODC9                   | ODC8                   | ODC7                   | ODC6                   | ODC5                   | ODC4                   | ODC3                   | ODC2                   | ODC1                   | ODC0                   | 0000                |

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

Note 1: Reset value depends on the device type; the PIC24F16KM204 value is shown.

**2:** These bits are not implemented in 20-pin devices.

3: These bits are not implemented in 28-pin devices.

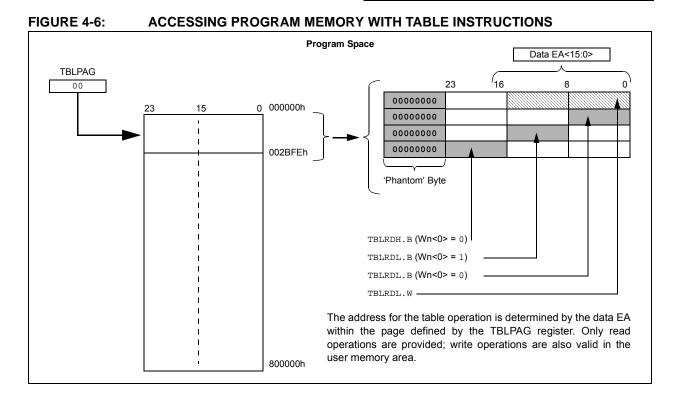

### 4.3.2 DATA ACCESS FROM PROGRAM MEMORY AND DATA EEPROM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program memory without going through Data Space. It also offers a direct method of reading or writing a word of any address within data EEPROM memory. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

Note: The TBLRDH and TBLWTH instructions are not used while accessing data EEPROM memory.

The PC is incremented by 2 for each successive 24-bit program word. This allows program memory addresses to directly map to Data Space addresses. Program memory can thus be regarded as two 16-bit, word-wide address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space which contains the least significant data word, and TBLRDH and TBLWTH access the space which contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from program space. Both function as either byte or word operations.

TBLRDL (Table Read Low): In Word mode, it maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>). In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when byte select is '1'; the lower byte is selected when it is '0'.

TBLRDH (Table Read High): In Word mode, it maps the entire upper word of a program address (P<23:16>) to a data address. Note that D<15:8>, the 'phantom' byte, will always be '0'.

In Byte mode, it maps the upper or lower byte of the program word to D<7:0> of the data address, as above. Note that the data will always be '0' when the upper 'phantom' byte is selected (Byte Select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in **Section 5.0 "Flash Program Memory"**.

For all table operations, the area of program memory space to be accessed is determined by the Table Memory Page Address register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

**Note:** Only Table Read operations will execute in the configuration memory space, and only then, in implemented areas, such as the Device ID. Table Write operations are not allowed.

© 2013 Microchip Technology Inc.

### EXAMPLE 5-5: INITIATING A PROGRAMMING SEQUENCE – ASSEMBLY LANGUAGE CODE

| DISI | #5          | ; | Block all interrupts<br>for next 5 instructions |

|------|-------------|---|-------------------------------------------------|

| MOV  | #0x55, W0   |   |                                                 |

| MOV  | W0, NVMKEY  | ; | Write the 55 key                                |

| MOV  | #0xAA, W1   | ; |                                                 |

| MOV  | W1, NVMKEY  | ; | Write the AA key                                |

| BSET | NVMCON, #WR | ; | Start the erase sequence                        |

| NOP  |             | ; | 2 NOPs required after setting WR                |

| NOP  |             | ; |                                                 |

| BTSC | NVMCON, #15 | ; | Wait for the sequence to be completed           |

| BRA  | \$-2        | ; |                                                 |

|      |             |   |                                                 |

### EXAMPLE 5-6: INITIATING A PROGRAMMING SEQUENCE – 'C' LANGUAGE CODE

| // C example using MPLAB C30 |                                                 |

|------------------------------|-------------------------------------------------|

| asm("DISI #5");              | // Block all interrupts for next 5 instructions |

| builtin_write_NVM();         | // Perform unlock sequence and set WR           |

## 9.4 Clock Switching Operation

With few limitations, applications are free to switch between any of the four clock sources (POSC, SOSC, FRC and LPRC) under software control and at any time. To limit the possible side effects that could result from this flexibility, PIC24F devices have a safeguard lock built into the switching process.

Note: The Primary Oscillator mode has three different submodes (XT, HS and EC), which are determined by the POSCMDx Configuration bits. While an application can switch to and from Primary Oscillator mode in software, it cannot switch between the different primary submodes without reprogramming the device.

## 9.4.1 ENABLING CLOCK SWITCHING

To enable clock switching, the FCKSM1 Configuration bit in the FOSC Configuration register must be programmed to '0'. (Refer to **Section 25.0** "**Special Features**" for further details.) If the FCKSM1 Configuration bit is unprogrammed ('1'), the clock switching function and FSCM function are disabled; this is the default setting.

The NOSCx control bits (OSCCON<10:8>) do not control the clock selection when clock switching is disabled. However, the COSCx bits (OSCCON<14:12>) will reflect the clock source selected by the FNOSCx Configuration bits.

The OSWEN control bit (OSCCON<0>) has no effect when clock switching is disabled; it is held at '0' at all times.

### 9.4.2 OSCILLATOR SWITCHING SEQUENCE

At a minimum, performing a clock switch requires this basic sequence:

- 1. If desired, read the COSCx bits (OSCCON<14:12>) to determine the current oscillator source.

- 2. Perform the unlock sequence to allow a write to the OSCCON register high byte.

- 3. Write the appropriate value to the NOSCx bits (OSCCON<10:8>) for the new oscillator source.

- 4. Perform the unlock sequence to allow a write to the OSCCON register low byte.

- 5. Set the OSWEN bit to initiate the oscillator switch.

Once the basic sequence is completed, the system clock hardware responds automatically, as follows:

- 1. The clock switching hardware compares the COSCx bits with the new value of the NOSCx bits. If they are the same, then the clock switch is a redundant operation. In this case, the OSWEN bit is cleared automatically and the clock switch is aborted.

- If a valid clock switch has been initiated, the LOCK (OSCCON<5>) and CF (OSCCON<3>) bits are cleared.

- The new oscillator is turned on by the hardware if it is not currently running. If a crystal oscillator must be turned on, the hardware will wait until the OST expires. If the new source is using the PLL, then the hardware waits until a PLL lock is detected (LOCK = 1).

- 4. The hardware waits for 10 clock cycles from the new clock source and then performs the clock switch.

- 5. The hardware clears the OSWEN bit to indicate a successful clock transition. In addition, the NOSCx bits value is transferred to the COSCx bits.

- The old clock source is turned off at this time, with the exception of LPRC (if WDT, FSCM or RTCC with LPRC as a clock source is enabled) or SOSC (if SOSCEN remains enabled).

Note 1: The processor will continue to execute code throughout the clock switching sequence. Timing-sensitive code should not be executed during this time.

2: Direct clock switches between any Primary Oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transitional clock source between the two PLL modes.

NOTES:

## FIGURE 13-4: 32-BIT TIMER MODE

### REGISTER 14-10: PADCFG1: PAD CONFIGURATION CONTROL REGISTER

| U-0          | U-0                                 | U-0                                                            | U-0          | R/W-0                  | R/W-0                  | R/W-0           | R/W-0   |  |

|--------------|-------------------------------------|----------------------------------------------------------------|--------------|------------------------|------------------------|-----------------|---------|--|

| _            | —                                   | _                                                              | _            | SDO2DIS <sup>(1)</sup> | SCK2DIS <sup>(1)</sup> | SDO1DIS         | SCK1DIS |  |

| bit 15       |                                     |                                                                |              |                        |                        |                 | bit     |  |

|              |                                     |                                                                |              |                        |                        |                 |         |  |

| U-0          | U-0                                 | U-0                                                            | U-0          | U-0                    | U-0                    | U-0             | U-0     |  |

|              | —                                   |                                                                |              |                        | —                      | _               | —       |  |

| bit 7        |                                     |                                                                |              |                        |                        |                 | bit (   |  |

|              |                                     |                                                                |              |                        |                        |                 |         |  |

| Legend:      |                                     |                                                                |              |                        |                        |                 |         |  |

| R = Readabl  | e bit                               | W = Writable b                                                 | pit          | U = Unimplem           | nented bit, read       | as '0'          |         |  |

| n = Value at | POR                                 | '1' = Bit is set                                               |              | '0' = Bit is clea      | ared                   | x = Bit is unkn | own     |  |

|              |                                     |                                                                |              |                        |                        |                 |         |  |

| bit 15-12    | Unimplemen                          | ted: Read as '0                                                | ,            |                        |                        |                 |         |  |

| bit 11       | SDO2DIS: MS                         | SDO2DIS: MSSP2 SDO2 Pin Disable bit <sup>(1)</sup>             |              |                        |                        |                 |         |  |

|              |                                     | 1 = The SPI output data (SDO2) of MSSP2 to the pin is disabled |              |                        |                        |                 |         |  |

|              |                                     | 0 = The SPI output data (SDO2) of MSSP2 is output to the pin   |              |                        |                        |                 |         |  |

| bit 10       |                                     | SCK2DIS: MSSP2 SCK2 Pin Disable bit <sup>(1)</sup>             |              |                        |                        |                 |         |  |

|              |                                     | clock (SCK2) of<br>clock (SCK2) of                             |              |                        | נ                      |                 |         |  |

| bit 9        |                                     | SSP1 SDO1 Pir                                                  |              |                        |                        |                 |         |  |

|              |                                     | output data (SD                                                |              | 1 to the pin is d      | isabled                |                 |         |  |

|              |                                     | output data (SD                                                | ,            |                        |                        |                 |         |  |

| bit 8        | SCK1DIS: MSSP1 SCK1 Pin Disable bit |                                                                |              |                        |                        |                 |         |  |

|              | 1 = The SPI                         | clock (SCK1) of                                                | MSSP1 to the | e pin is disabled      | t                      |                 |         |  |

|              | 0 = The SPI                         | clock (SCK1) of                                                | MSSP1 is ou  | tput to the pin        |                        |                 |         |  |

| bit 7-0      | Unimplemen                          | ted: Read as '0                                                | ,            |                        |                        |                 |         |  |

|              |                                     |                                                                |              |                        |                        |                 |         |  |

**Note 1:** These bits are implemented only on PIC24FXXKM20X devices.

NOTES:

## 25.0 SPECIAL FEATURES

- **Note:** This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the Watchdog Timer, High-Level Device Integration and Programming Diagnostics, refer to the individual sections of the *"PIC24F Family Reference Manual"* provided below:

- "Watchdog Timer (WDT)" (DS39697)

- "Programming and Diagnostics" (DS39716)

PIC24FXXXXX family devices include several features intended to maximize application flexibility and reliability, and minimize cost through elimination of external components. These are:

- Flexible Configuration

- Watchdog Timer (WDT)

- Code Protection

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- In-Circuit Emulation

## 25.1 Configuration Bits

The Configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped, starting at program memory location, F80000h. A complete list of Configuration register locations is provided in Table 25-1. A detailed explanation of the various bit functions is provided in Register 25-1 through Register 25-9.

The address, F80000h, is beyond the user program memory space. In fact, it belongs to the configuration memory space (800000h-FFFFFFh), which can only be accessed using Table Reads and Table Writes.

#### TABLE 25-1: CONFIGURATION REGISTERS LOCATIONS

| Configuration<br>Register | Address |

|---------------------------|---------|

| FBS                       | F80000  |

| FGS                       | F80004  |

| FOSCSEL                   | F80006  |

| FOSC                      | F80008  |

| FWDT                      | F8000A  |

| FPOR                      | F8000C  |

| FICD                      | F8000E  |

### REGISTER 25-1: FBS: BOOT SEGMENT CONFIGURATION REGISTER

| U-0   | U-0 | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-----|-----|-------|-------|-------|-------|

| —     | —   | —   | —   | BSS2  | BSS1  | BSS0  | BWRP  |

| bit 7 |     |     |     |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

#### bit 7-4 Unimplemented: Read as '0'

- bit 3-1 BSS<2:0>: Boot Segment Program Flash Code Protection bits

- 111 = No boot program Flash segment

- 011 = Reserved

- 110 = Standard security, boot program Flash segment starts at 200h, ends at 000AFEh

- 010 = High-security, boot program Flash segment starts at 200h, ends at 000AFEh

- 101 = Standard security, boot program Flash segment starts at 200h, ends at 0015FEh<sup>(1)</sup>

- 001 = High-security, boot program Flash segment starts at 200h, ends at 0015FEh<sup>(1)</sup>

- 100 = Reserved

- 000 = Reserved

### bit 0 BWRP: Boot Segment Program Flash Write Protection bit

- 1 = Boot Segment may be written

- 0 = Boot Segment is write-protected

#### Note 1: This selection should not be used in PIC24FV08KMXXX devices.

## 27.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of the PIC24FV16KM204 family electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the PIC24FV16KM204 family are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these, or any other conditions above the parameters indicated in the operation listings of this specification, is not implied.

## Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias                                     | 40°C to +125°C       |

|--------------------------------------------------------------------|----------------------|

| Storage temperature                                                | 65°C to +150°C       |

| Voltage on VDD with respect to Vss (PIC24FXXKMXXX)                 | -0.3V to +4.5V       |

| Voltage on VDD with respect to Vss (PIC24FVXXKMXXX)                | -0.3V to +6.5V       |

| Voltage on any combined analog and digital pin with respect to Vss | 0.3V to (VDD + 0.3V) |

| Voltage on any digital only pin with respect to Vss                | 0.3V to (VDD + 0.3V) |

| Voltage on MCLR/VPP pin with respect to Vss                        | -0.3V to +9.0V       |

| Maximum current out of Vss pin                                     |                      |

| Maximum current into Vod pin <sup>(1)</sup>                        |                      |

| Maximum output current sunk by any I/O pin                         |                      |

| Maximum output current sourced by any I/O pin                      |                      |

| Maximum current sunk by all ports                                  |                      |

| Maximum current sourced by all ports <sup>(1)</sup>                | 200 mA               |

Note 1: Maximum allowable current is a function of device maximum power dissipation (see Table 27-1).

**†** Notice: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Param<br>No. | Symbol | Characteristic                                         | Min | Тур | Max | Units | Comments |

|--------------|--------|--------------------------------------------------------|-----|-----|-----|-------|----------|

| 300          | TRESP  | Response Time <sup>*(1)</sup>                          | _   | 150 | 400 | ns    |          |

| 301          | Тмс2о∨ | Comparator Mode Change to<br>Output Valid <sup>*</sup> | —   | _   | 10  | μs    |          |

### TABLE 27-26: COMPARATOR TIMING REQUIREMENTS

Parameters are characterized but not tested.

\*

**Note 1:** Response time is measured with one comparator input at (VDD – 1.5)/2, while the other input transitions from Vss to VDD.

### TABLE 27-27: COMPARATOR VOLTAGE REFERENCE SETTLING TIME SPECIFICATIONS

| Param<br>No. | Symbol | Characteristic               | Min | Тур | Max | Units | Comments |

|--------------|--------|------------------------------|-----|-----|-----|-------|----------|

| VR310        | TSET   | Settling Time <sup>(1)</sup> |     |     | 10  | μS    |          |

Note 1: Settling time is measured while CVRSS = 1 and the CVR<3:0> bits transition from '0000' to '1111'.

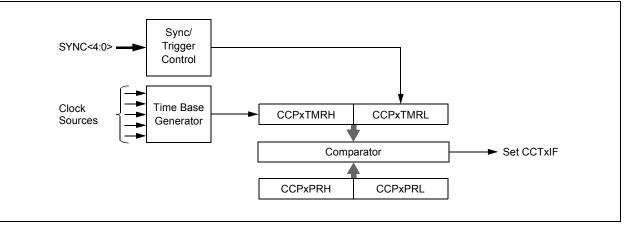

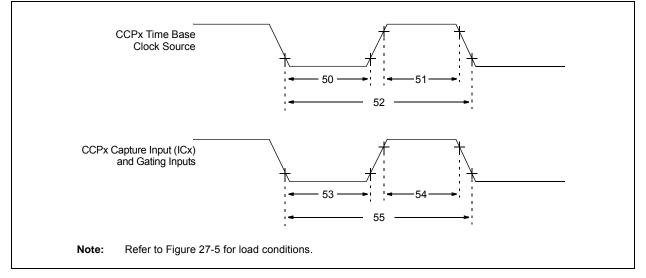

## FIGURE 27-10: CAPTURE/COMPARE/PWM TIMINGS (MCCPx, SCCPx MODULES)

### TABLE 27-28: CAPTURE/COMPARE/PWM REQUIREMENTS (MCCPx, SCCPx MODULES)

| Param<br>No. | Symbol | Characteristic                         | Min        | Max | Units | Conditions                         |

|--------------|--------|----------------------------------------|------------|-----|-------|------------------------------------|

| 50           | TCLKL  | CCPx Time Base Clock Source Low Time   | TCY/2      | _   | ns    |                                    |

| 51           | ТсікН  | CCPx Time Base Clock Source High Time  | Tcy/2      | _   | ns    |                                    |

| 52           | TCLK   | CCPx Time Base Clock Source Period     | Тсү        | -   | ns    |                                    |

| 53           | TccL   | CCPx Capture or Gating Input Low Time  | TCLK       | —   | ns    |                                    |

| 54           | ТссН   | CCPx Capture or Gating Input High Time | TCLK       | _   | ns    |                                    |

| 55           | TCCP   | CCPx Capture or Gating Input Period    | 2 * Tclk/N | —   | ns    | N = Prescale<br>Value (1, 4 or 16) |

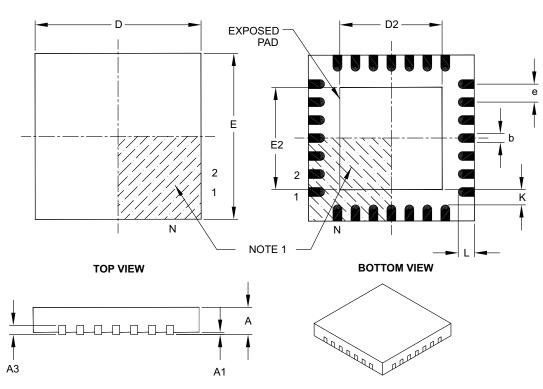

## 28-Lead Plastic Quad Flat, No Lead Package (ML) – 6x6 mm Body [QFN] with 0.55 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units            | MILLIMETERS |          |      |

|------------------------|------------------|-------------|----------|------|

|                        | Dimension Limits | MIN         | NOM      | MAX  |

| Number of Pins         | N                |             | 28       |      |

| Pitch                  | e                |             | 0.65 BSC |      |

| Overall Height         | A                | 0.80        | 0.90     | 1.00 |

| Standoff               | A1               | 0.00        | 0.02     | 0.05 |

| Contact Thickness      | A3               | 0.20 REF    |          |      |

| Overall Width          | E                | 6.00 BSC    |          |      |

| Exposed Pad Width      | E2               | 3.65        | 3.70     | 4.20 |

| Overall Length         | D                | 6.00 BSC    |          |      |

| Exposed Pad Length     | D2               | 3.65        | 3.70     | 4.20 |

| Contact Width          | b                | 0.23        | 0.30     | 0.35 |

| Contact Length         | L                | 0.50        | 0.55     | 0.70 |

| Contact-to-Exposed Pad | К                | 0.20        | -        | —    |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-105B

NOTES:

## **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| Product Group<br>Pin Count<br>Tape and Reel Fl |                                                                                                                                    | <ul> <li>Examples:</li> <li>a) PIC24FV16KM204-I/ML: Wide Voltage Range,<br/>General Purpose, 16-Kbyte Program Memory,<br/>44-Pin, Industrial Temp., QFN Package</li> <li>b) PIC24F08KM102-I/SS: Standard Voltage Range,<br/>General Purpose with Reduced Feature Set,<br/>8-Kbyte Program Memory, 28-Pin, Industrial<br/>Temp., SSOP Package</li> </ul> |

|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Architecture                                   | 24 = 16-bit modified Harvard without DSP                                                                                           |                                                                                                                                                                                                                                                                                                                                                         |

| Flash Memory Family                            | <ul><li>F = Standard voltage range Flash program memory</li><li>FV = Wide voltage range Flash program memory</li></ul>             |                                                                                                                                                                                                                                                                                                                                                         |

| Product Group                                  | KM2 = General Purpose PIC24F Lite Microcontroller<br>KM1 = General Purpose PIC24F Lite Microcontroller with<br>Reduced Feature Set |                                                                                                                                                                                                                                                                                                                                                         |

| Pin Count                                      | 01 = 20-pin<br>02 = 28-pin<br>04 = 44-pin                                                                                          |                                                                                                                                                                                                                                                                                                                                                         |

| Temperature Range                              | I = $-40^{\circ}$ C to $+85^{\circ}$ C (Industrial)<br>E = $-40^{\circ}$ C to $+125^{\circ}$ C (Extended)                          |                                                                                                                                                                                                                                                                                                                                                         |

| Package                                        | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                               |                                                                                                                                                                                                                                                                                                                                                         |

| Pattern                                        | Three-digit QTP, SQTP, Code or Special Requirements<br>(blank otherwise)<br>ES = Engineering Sample                                |                                                                                                                                                                                                                                                                                                                                                         |