Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                   |                                                                               |

|---------------------------|-------------------------------------------------------------------------------|

| Product Status            | Active                                                                        |

| Core Processor            | PIC                                                                           |

| Core Size                 | 16-Bit                                                                        |

| Speed                     | 32MHz                                                                         |

| Connectivity              | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals               | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O             | 23                                                                            |

| Program Memory Size       | 16KB (5.5K x 24)                                                              |

| Program Memory Type       | FLASH                                                                         |

| EEPROM Size               | 512 x 8                                                                       |

| RAM Size                  | 2K x 8                                                                        |

| oltage - Supply (Vcc/Vdd) | 2V ~ 5V                                                                       |

| Data Converters           | A/D 19x10b/12b; D/A 2x8b                                                      |

| Oscillator Type           | Internal                                                                      |

| Operating Temperature     | -40°C ~ 125°C (TA)                                                            |

| Mounting Type             | Surface Mount                                                                 |

| Package / Case            | 28-SOIC (0.295", 7.50mm Width)                                                |

| Supplier Device Package   | 28-SOIC                                                                       |

| Purchase URL              | https://www.e-xfl.com/product-detail/microchip-technology/pic24fv16km202-e-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 4-5: | INTERRUPT CONTROLLER REGISTER MAP  |  |

|------------|------------------------------------|--|

| IADLL TJ.  | INTERNO I CONTINUELLI NEGISTEN MAI |  |

| File Name | Addr. | Bit 15 | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10  | Bit 9   | Bit 8   | Bit 7  | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|-----------|-------|--------|---------|---------|---------|--------|---------|---------|---------|--------|---------|---------|---------|---------|----------|----------|----------|---------------|

| INTCON1   | 80h   | NSTDIS | _       | _       | _       | _      |         | _       | _       | _      |         | _       | MATHERR | ADDRERR | STKERR   | OSCFAIL  | _        | 0000          |

| INTCON2   | 82h   | ALTIVT | DISI    | _       | _       | _      | _       | _       | _       | _      | _       | _       | _       | _       | INT2EP   | INT1EP   | INT0EP   | 0000          |

| IFS0      | 84h   | NVMIF  | _       | AD1IF   | U1TXIF  | U1RXIF | _       | _       | CCT2IF  | CCT1IF | CCP4IF  | CCP3IF  | _       | T1IF    | CCP2IF   | CCP1IF   | INT0IF   | 0000          |

| IFS1      | 86h   | U2TXIF | U2RXIF  | INT2IF  | CCT4IF  | CCT3IF | _       | _       | _       | _      | CCP5IF  | _       | INT1IF  | CNIF    | CMIF     | BCL1IF   | SSP1IF   | 0000          |

| IFS2      | 88h   | _      | _       | _       | _       | _      | _       | CCT5IF  | _       | _      | _       | _       | _       | _       | _        | _        | _        | 0000          |

| IFS3      | 8Ah   | _      | RTCIF   | _       | _       | _      | _       | _       | _       | _      | _       | _       | _       | _       | BCL2IF   | SSP2IF   | _        | 0000          |

| IFS4      | 8Ch   | DAC2IF | DAC1IF  | CTMUIF  | _       | _      | _       | _       | HLVDIF  | _      | _       | _       | _       | _       | U2ERIF   | U1ERIF   | _        | 0000          |

| IFS5      | 8Eh   | _      | _       | _       | _       | _      | _       | _       | _       | _      | _       | _       | _       | _       | _        | _        | ULPWUIF  | 0000          |

| IFS6      | 90h   | _      | _       | _       | _       | _      | _       | _       | _       | _      | _       | _       | _       | _       | _        | CLC2IF   | CLC1IF   | 0000          |

| IEC0      | 94h   | NVMIE  | _       | AD1IE   | U1TXIE  | U1RXIE | _       | _       | CCT2IE  | CCT1IE | CCP4IE  | CCP3IE  | _       | T1IE    | CCP2IE   | CCP1IE   | INT0IE   | 0000          |

| IEC1      | 96h   | U2TXIE | U2RXIE  | INT2IE  | CCT4IE  | CCT3IE | _       | _       | _       | _      | CCP5IE  | _       | INT1IE  | CNIE    | CMIE     | BCL1IE   | SSP1IE   | 0000          |

| IEC2      | 98h   | _      | _       | _       | _       | _      | _       | CCT5IE  | _       | _      | _       | _       | _       | _       | _        | _        | _        | 0000          |

| IEC3      | 9Ah   | _      | RTCIE   | _       | _       | _      | _       | _       | _       | _      | _       | _       | _       | _       | BCL2IE   | SSP2IE   | _        | 0000          |

| IEC4      | 9Ch   | DAC2IE | DAC1IE  | CTMUIE  | _       | _      | _       | _       | HLVDIE  | _      | _       | _       | _       | _       | U2ERIE   | U1ERIE   | _        | 0000          |

| IEC5      | 9Eh   | _      | _       | _       | _       | _      | _       | _       | _       | _      | _       | _       | _       | _       | _        | _        | ULPWUIE  | 0000          |

| IEC6      | A0h   | _      | _       | _       | _       | _      | _       | _       | _       | _      | _       | _       | _       | _       | _        | CLC2IE   | CLC1IE   | 0000          |

| IPC0      | A4h   | _      | T1IP2   | T1IP1   | T1IP0   | _      | CCP2IP2 | CCP2IP1 | CCP2IP0 | _      | CCP1IP2 | CCP1IP1 | CCP1IP0 | _       | INT0IP2  | INT0IP1  | INT0IP0  | 4444          |

| IPC1      | A6h   | _      | CCT1IP2 | CCT1IP1 | CCT1IP0 | _      | CCP4IP2 | CCP4IP1 | CCP4IP0 | _      | CCP3IP2 | CCP3IP1 | CCP3IP0 | _       | _        | _        | _        | 4440          |

| IPC2      | A8h   | _      | U1RXIP2 | U1RXIP1 | U1RXIP0 | _      | _       | _       | _       | _      | _       | _       | _       | _       | CCT2IP2  | CCT2IP1  | CCT2IP0  | 4004          |

| IPC3      | AAh   | _      | NVMIP2  | NVMIP1  | NVMIP0  | _      | _       | _       | _       | _      | AD1IP2  | AD1IP1  | AD1IP0  | _       | U1TXIP2  | U1TXIP1  | U1TXIP0  | 4044          |

| IPC4      | ACh   | _      | CNIP2   | CNIP1   | CNIP0   | _      | CMIP2   | CMIP1   | CMIP0   | _      | BCL1IP2 | BCL1IP1 | BCL1IP0 | _       | SSP1IP2  | SSP1IP1  | SSP1IP0  | 4444          |

| IPC5      | AEh   | _      | _       | _       | _       | _      | CCP5IP2 | CCP5IP1 | CCP5IP0 | _      | _       | _       | _       | _       | INT1IP2  | INT1IP1  | INT1IP0  | 0404          |

| IPC6      | B0h   | _      | CCT3IP2 | CCT3IP1 | CCT3IP0 | _      | _       | _       | _       | _      | _       | _       | _       | _       | _        | _        | _        | 4000          |

| IPC7      | B2h   | _      | U2TXIP2 | U2TXIP1 | U2TXIP0 | _      | U2RXIP2 | U2RXIP1 | U2RXIP0 | _      | INT2IP2 | INT2IP1 | INT2IP0 | _       | CCT4IP2  | CCT4IP1  | CCT4IP0  | 4444          |

| IPC10     | B8h   | _      | _       | _       | _       | _      | _       | _       | _       | _      | CCT5IP2 | CCT5IP1 | CCT5IP0 | _       | _        | _        | _        | 0040          |

| IPC12     | BCh   | _      | _       | _       | _       | _      | BCL2IP2 | BCL2IP1 | BCL2IP0 | _      | SSP2IP2 | SSP2IP1 | SSP2IP0 | _       | _        | _        | _        | 0440          |

| IPC15     | C2h   | _      | _       | _       | _       | _      | RTCIP2  | RTCIP1  | RTCIP0  | _      | _       | _       | _       | _       | _        | _        | _        | 0400          |

| IPC16     | C4h   | _      | _       | _       | _       | _      | U2ERIP2 | U2ERIP1 | U2ERIP0 | _      | U1ERIP2 | U1ERIP1 | U1ERIP0 | _       | _        | _        | _        | 0440          |

| IPC18     | C8h   | _      | _       | _       | _       | _      | _       | _       | _       | _      | _       | _       | _       | _       | HLVDIP2  | HLVDIP1  | HLVDIP0  | 0004          |

| IPC19     | CAh   | _      | DAC2IP2 | DAC2IP1 | DAC2IP0 | _      | DAC1IP2 | DAC1IP1 | DAC1IP0 | _      | CTMUIP2 | CTMUIP1 | CTMUIP0 | _       | _        | _        | _        | 4440          |

| IPC20     | CCh   | _      | _       | _       | _       | _      | _       | _       | _       | _      | _       | _       | _       | _       | ULPWUIP2 | ULPWUIP1 | ULPWUIP0 | 0004          |

| IPC24     | D4h   | _      | _       | _       | _       | _      | _       | _       | _       | _      | CLC2IP2 | CLC2IP1 | CLC2IP0 | _       | CLC1IP2  | CLC1IP1  | CLC1IP0  | 0044          |

| INTTREG   | E0h   | CPUIRQ | _       | VHOLD   | _       | ILR3   | ILR2    | ILR1    | ILR0    | _      | VECNUM6 | VECNUM5 | VECNUM4 | VECNUM3 | VECNUM2  | VECNUM1  | VECNUM0  | 0000          |

**Legend:** x = unknown, u = unchanged, --= unimplemented, q = value depends on condition, r = reserved.

## 5.0 FLASH PROGRAM MEMORY

Note:

This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on Flash programming, refer to the "PIC24F Family Reference Manual", "Program Memory" (DS39715).

The PIC24FV16KM204 family of devices contains internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable when operating with VDD over 1.8V.

Flash memory can be programmed in three ways:

- In-Circuit Serial Programming™ (ICSP™)

- Run-Time Self-Programming (RTSP)

- Enhanced In-Circuit Serial Programming (Enhanced ICSP)

ICSP allows a PIC24FXXXXX device to be serially programmed while in the end application circuit. This is simply done with two lines for the programming clock and programming data (which are named PGECx and PGEDx, respectively), and three other lines for power (VDD), ground (VSS) and Master Clear/Program Mode Entry Voltage (MCLR/VPP). This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or custom firmware to be programmed.

Run-Time Self-Programming (RTSP) is accomplished using TBLRD (Table Read) and TBLWT (Table Write) instructions. With RTSP, the user may write program memory data in blocks of 32 instructions (96 bytes) at a time, and erase program memory in blocks of 32, 64 and 128 instructions (96,192 and 384 bytes) at a time.

The NVMOP<1:0> (NVMCON<1:0>) bits decide the erase block size.

# 5.1 Table Instructions and Flash Programming

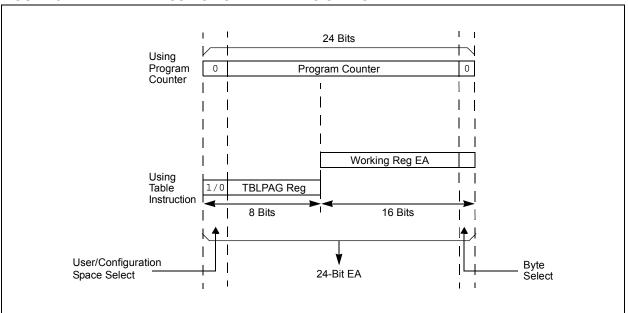

Regardless of the method used, Flash memory programming is done with the Table Read and Write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using the TBLPAG<7:0> bits and the Effective Address (EA) from a W register, specified in the table instruction, as depicted in Figure 5-1.

The TBLRDL and the TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

FIGURE 5-1: ADDRESSING FOR TABLE REGISTERS

### 7.4.2 SOFTWARE ENABLED BOR

When BOREN<1:0> = 01, the BOR can be enabled or disabled by the user in software. This is done with the control bit, SBOREN (RCON<13>). Setting SBOREN enables the BOR to function as previously described. Clearing the SBOREN disables the BOR entirely. The SBOREN bit operates only in this mode; otherwise, it is read as '0'.

Placing BOR under software control gives the user the additional flexibility of tailoring the application to its environment without having to reprogram the device to change the BOR configuration. It also allows the user to tailor the incremental current that the BOR consumes. While the BOR current is typically very small, it may have some impact in low-power applications.

Note:

Even when the BOR is under software control, the Brown-out Reset voltage level is still set by the BORV<1:0> Configuration bits; it can not be changed in software.

#### 7.4.3 DETECTING BOR

When BOR is enabled, the BOR bit (RCON<1>) is always reset to '1' on any BOR or POR event. This makes it difficult to determine if a BOR event has occurred just by reading the state of BOR alone. A more reliable method is to simultaneously check the state of both POR and BOR. This assumes that the POR and BOR bits are reset to '0' in the software immediately after any POR event. If the BOR bit is '1' while POR is '0', it can be reliably assumed that a BOR event has occurred.

#### 7.4.4 DISABLING BOR IN SLEEP MODE

When BOREN<1:0> = 10, BOR remains under hardware control and operates as previously described. However, whenever the device enters Sleep mode, BOR is automatically disabled. When the device returns to any other operating mode, BOR is automatically re-enabled.

This mode allows for applications to recover from brown-out situations, while actively executing code, when the device requires BOR protection the most. At the same time, it saves additional power in Sleep mode by eliminating the small incremental BOR current.

Note:

BOR levels differ depending on device type; PIC24FV16KM204 devices are at different levels than those of PIC24F16KM204 devices. See Section 27.0 "Electrical Characteristics" for BOR voltage levels.

#### REGISTER 8-6: IFS1: INTERRUPT FLAG STATUS REGISTER 1

| R/W-0, HS | U-0 | U-0 | U-0   |

|-----------|-----------|-----------|-----------|-----------|-----|-----|-------|

| U2TXIF    | U2RXIF    | INT2IF    | CCT4IF    | CCT3IF    | _   | _   | _     |

| bit 15    |           |           |           |           |     |     | bit 8 |

| U-0   | R/W-0, HS | U-0 | R/W-0, HS |

|-------|-----------|-----|-----------|-----------|-----------|-----------|-----------|

| _     | CCP5IF    | _   | INT1IF    | CNIF      | CMIF      | BCL1IF    | SSP1IF    |

| bit 7 |           |     |           |           |           |           | bit 0     |

**Legend:** HS = Hardware Settable bit

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 U2TXIF: UART2 Transmitter Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 13 INT2IF: External Interrupt 2 Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 12 CCT4IF: Capture/Compare 4 Timer Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 11 CCT3IF: Capture/Compare 3 Timer Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 10-7 **Unimplemented:** Read as '0'

bit 6 CCP5IF: Capture/Compare 5 Event Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 5 **Unimplemented:** Read as '0'

bit 4 **INT1IF:** External Interrupt 1 Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 3 CNIF: Input Change Notification Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 2 **CMIF:** Comparator Interrupt Flag Status Bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 1 **BCL1IF:** MSSP1 I<sup>2</sup>C™ Bus Collision Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 0 SI2C1IF: MSSP1 SPI/I<sup>2</sup>C Event Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

### REGISTER 8-21: IPC2: INTERRUPT PRIORITY CONTROL REGISTER 2

| U-0    | R/W-1   | R/W-0   | R/W-0   | U-0 | U-0 | U-0 | U-0   |

|--------|---------|---------|---------|-----|-----|-----|-------|

| _      | U1RXIP2 | U1RXIP1 | U1RXIP0 | _   | _   | _   | _     |

| bit 15 |         |         |         |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-1   | R/W-0   | R/W-0   |

|-------|-----|-----|-----|-----|---------|---------|---------|

| _     | _   | _   | _   | _   | CCT2IP2 | CCT2IP1 | CCT2IP0 |

| bit 7 |     |     |     |     |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **Unimplemented:** Read as '0'

bit 14-12 U1RXIP<2:0>: UART1 Receiver Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

•

.

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

bit 11-3 Unimplemented: Read as '0'

bit 2-0 CCT2IP<2:0>: Capture/Compare 2 Timer Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

•

\_

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

#### REGISTER 8-26: **IPC7: INTERRUPT PRIORITY CONTROL REGISTER 7**

| U-0    | R/W-1   | R/W-0   | R/W-0   | U-0 | R/W-1   | R/W-0   | R/W-0   |

|--------|---------|---------|---------|-----|---------|---------|---------|

| _      | U2TXIP2 | U2TXIP1 | U2TXIP0 | _   | U2RXIP2 | U2RXIP1 | U2RXIP0 |

| bit 15 |         |         |         |     |         |         | bit 8   |

| U-0   | R/W-1   | R/W-0   | R/W-0   | U-0 | R/W-1   | R/W-0   | R/W-0   |

|-------|---------|---------|---------|-----|---------|---------|---------|

| _     | INT2IP2 | INT2IP1 | INT2IP0 | _   | CCT4IP2 | CCT4IP1 | CCT4IP0 |

| bit 7 |         |         |         |     |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 Unimplemented: Read as '0'

bit 14-12 U2TXIP<2:0>: UART2 Transmitter Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

bit 11 Unimplemented: Read as '0'

bit 10-8 U2RXIP<2:0>: UART2 Receiver Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

bit 7 Unimplemented: Read as '0'

bit 6-4 INT2IP<2:0>: External Interrupt 2 Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

bit 3 Unimplemented: Read as '0'

bit 2-0 CCT4IP<2:0>: Capture/Compare 4 Timer Interrupt Priority bits

111 = Interrupt is Priority 7 (highest priority interrupt)

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

NOTES:

## REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER (CONTINUED)

bit 7 CLKLOCK: Clock Selection Lock Enable bit

If FSCM is Enabled (FCKSM1 =  $\underline{1}$ ):

1 = Clock and PLL selections are locked

0 = Clock and PLL selections are not locked and may be modified by setting the OSWEN bit

If FSCM is Disabled (FCKSM1 = 0):

Clock and PLL selections are never locked and may be modified by setting the OSWEN bit.

bit 6 **Unimplemented:** Read as '0' bit 5 **LOCK:** PLL Lock Status bit<sup>(2)</sup>

1 = PLL module is in lock or PLL module start-up timer is satisfied

0 = PLL module is out of lock, PLL start-up timer is running or PLL is disabled

bit 4 Unimplemented: Read as '0'

1 = FSCM has detected a clock failure0 = No clock failure has been detected

bit 2 **SOSCDRV**: Secondary Oscillator Drive Strength bit<sup>(3)</sup>

1 = High-power SOSC circuit is selected

0 = Low/high-power select is done via the SOSCSRC Configuration bit

bit 1 SOSCEN: 32 kHz Secondary Oscillator (SOSC) Enable bit

1 = Enables the Secondary Oscillator0 = Disables the Secondary Oscillator

bit 0 **OSWEN:** Oscillator Switch Enable bit

1 = Initiates an oscillator switch to the clock source specified by the NOSC<2:0> bits

0 = Oscillator switch is complete

Note 1: Reset values for these bits are determined by the FNOSCx Configuration bits.

2: This bit also resets to '0' during any valid clock switch or whenever a non-PLL Clock mode is selected.

3: When SOSC is selected to run from a digital clock input, rather than an external crystal (SOSCSRC = 0), this bit has no effect.

#### REGISTER 9-3: OSCTUN: FRC OSCILLATOR TUNE REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-0               | R/W-0               | R/W-0               | R/W-0               | R/W-0               | R/W-0               |

|-------|-----|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

| _     | _   | TUN5 <sup>(1)</sup> | TUN4 <sup>(1)</sup> | TUN3 <sup>(1)</sup> | TUN2 <sup>(1)</sup> | TUN1 <sup>(1)</sup> | TUN0 <sup>(1)</sup> |

| bit 7 |     |                     |                     |                     |                     |                     | bit 0               |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-6 **Unimplemented:** Read as '0'

bit 5-0 **TUN<5:0>:** FRC Oscillator Tuning bits<sup>(1)</sup>

011111 = Maximum frequency deviation

011110

•

\_

•

000001

000000 = Center frequency, oscillator is running at factory calibrated frequency

111111

•

\_

100001

100000 = Minimum frequency deviation

**Note 1:** Increments or decrements of TUN<5:0> may not change the FRC frequency in equal steps over the FRC tuning range and may not be monotonic.

#### REGISTER 13-1: CCPxCON1L: CCPx CONTROL 1 LOW REGISTERS

| R/W-0  | U-0 | R/W-0   | r-0 | R/W-0   | R/W-0                  | R/W-0                  | R/W-0                  |

|--------|-----|---------|-----|---------|------------------------|------------------------|------------------------|

| CCPON  | _   | CCPSIDL | r   | TMRSYNC | CLKSEL2 <sup>(1)</sup> | CLKSEL1 <sup>(1)</sup> | CLKSEL0 <sup>(1)</sup> |

| bit 15 |     |         |     |         |                        |                        | bit 8                  |

| R/W-0  | R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|--------|-------|-------|-------|-------|-------|-------|

| TMRPS1 | TMRPS0 | T32   | CCSEL | MOD3  | MOD2  | MOD1  | MOD0  |

| bit 7  |        |       |       |       |       |       | bit 0 |

| Legend:           | r = Reserved bit |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 15 CCPON: CCPx Module Enable bit

1 = Module is enabled with an operating mode specified by the MOD<3:0> control bits

0 = Module is disabled

bit 14 **Unimplemented:** Read as '0'

bit 13 CCPSIDL: CCPx Stop in Idle Mode Bit

1 = Discontinues module operation when device enters Idle mode

0 = Continues module operation in Idle mode

bit 12 Reserved: Maintain as '0'

bit 11 TMRSYNC: Time Base Clock Synchronization bit

1 = Asynchronous module time base clock is selected and synchronized to the internal system clocks (CLKSEL<2:0> ≠ 000)

0 = Synchronous module time base clock is selected and does not require synchronization (CLKSEL<2:0> = 000)

bit 10-8 CLKSEL<2:0>: CCPx Time Base Clock Select bits<sup>(1)</sup>

111 = External TCLKIA input

110 = External TCLKIB input

101 = CLC1

100 = Reserved

011 = LPRC (31 kHz source)

010 = Secondary Oscillator

001 = Reserved

000 = System clock (TcY)

bit 7-6 TMRPS<1:0>: Time Base Prescale Select bits

11 = 1:64 Prescaler

10 = 1:16 Prescaler

01 = 1:4 Prescaler

00 = 1:1 Prescaler

bit 5 T32: 32-Bit Time Base Select bit

1 = Uses 32-bit time base for timer, single edge output compare or input capture function

0 = Uses 16-bit time base for timer, single edge output compare or input capture function

bit 4 CCSEL: Capture/Compare Mode Select bit

1 = Input Capture peripheral

0 = Output Compare/PWM/Timer peripheral (exact function is selected by the MOD<3:0> bits)

Note 1: Clock options are limited in some operating modes. See Table 13-1 for restrictions.

## REGISTER 14-3: SSPxCON1: MSSPx CONTROL REGISTER 1 (SPI MODE)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   |     | 1   |     | I   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0 | R/W-0                | R/W-0                | R/W-0 | R/W-0                | R/W-0                | R/W-0                | R/W-0                |

|-------|----------------------|----------------------|-------|----------------------|----------------------|----------------------|----------------------|

| WCOL  | SSPOV <sup>(1)</sup> | SSPEN <sup>(2)</sup> | CKP   | SSPM3 <sup>(3)</sup> | SSPM2 <sup>(3)</sup> | SSPM1 <sup>(3)</sup> | SSPM0 <sup>(3)</sup> |

| bit 7 |                      |                      |       |                      |                      |                      | bit 0                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 Unimplemented: Read as '0'

bit 7 WCOL: Write Collision Detect bit

1 = The SSPxBUF register is written while it is still transmitting the previous word (must be cleared in software)

0 = No collision

bit 6 SSPOV: Master Synchronous Serial Port Receive Overflow Indicator bit<sup>(1)</sup>

SPI Slave mode:

1 = A new byte is received while the SSPxBUF register is still holding the previous data. In case of overflow, the data in SSPxSR is lost. Overflow can only occur in Slave mode. The user must read the SSPxBUF, even if only transmitting data, to avoid setting overflow (must be cleared in software).

0 = No overflow

bit 5 SSPEN: Master Synchronous Serial Port Enable bit (2)

1 = Enables the serial port and configures SCKx, SDOx, SDIx and SSx as serial port pins

0 = Disables the serial port and configures these pins as I/O port pins

bit 4 CKP: Clock Polarity Select bit

1 = Idle state for clock is a high level

0 = Idle state for clock is a low level

bit 3-0 SSPM<3:0>: Master Synchronous Serial Port Mode Select bits<sup>(3)</sup>

1010 = SPI Master mode, Clock = Fosc/(2 \* ([SSPxADD] + 1))

0101 = SPI Slave mode, Clock = SCKx pin; SSx pin control is disabled, SSx can be used as an I/O pin

0100 = SPI Slave mode, Clock = SCKx pin; SSx pin control is enabled

0011 = SPI Master mode, Clock = TMR2 output/2

0010 = SPI Master mode, Clock = Fosc/32

0001 = SPI Master mode, Clock = Fosc/8

0000 = SPI Master mode. Clock = Fosc/2

**Note 1:** In Master mode, the overflow bit is not set since each new reception (and transmission) is initiated by writing to the SSPxBUF register.

2: When enabled, these pins must be properly configured as inputs or outputs.

3: Bit combinations not specifically listed here are either reserved or implemented in I<sup>2</sup>C™ mode only.

## REGISTER 16-11: RTCCSWT: RTCC CONTROL/SAMPLE WINDOW TIMER REGISTER(1)

| R/W-x    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| PWCSTAB7 | PWCSTAB6 | PWCSTAB5 | PWCSTAB4 | PWCSTAB3 | PWCSTAB2 | PWCSTAB1 | PWCSTAB0 |

| bit 15   |          |          |          |          |          |          | bit 8    |

| R/W-x    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| PWCSAMP7 | PWCSAMP6 | PWCSAMP5 | PWCSAMP4 | PWCSAMP3 | PWCSAMP2 | PWCSAMP1 | PWCSAMP0 |

| bit 7    |          |          |          |          |          |          | bit 0    |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 **PWCSTAB<7:0>:** PWM Stability Window Timer bits

11111111 = Stability window is 255 TPWCCLK clock periods

:

00000000 = Stability window is 0 TPWCCLK clock periods

The sample window starts when the alarm event triggers. The stability window timer starts counting from every alarm event when PWCEN = 1.

bit 7-0 **PWCSAMP<7:0>:** PWM Sample Window Timer bits

11111111 = Sample window is always enabled, even when PWCEN = 0

111111110 = Sample window is 254 TPWCCLK clock periods

.

00000000 = Sample window is 0 TPWCCLK clock periods

The sample window timer starts counting at the end of the stability window when PWCEN = 1. If PWCSTAB<7:0> = 00000000, the sample window timer starts counting from every alarm event when PWCEN = 1.

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

# TABLE 19-4: NUMERICAL EQUIVALENTS OF VARIOUS RESULT CODES: 10-BIT FRACTIONAL FORMATS

| Vin/Vref   | 10-Bit Differential<br>Output Code<br>(11-bit result) | 16-Bit Fractional Format<br>Equivalent Decimal Valu | -     | 16-Bit Signed Fractional Format/<br>Equivalent Decimal Value |        |  |  |  |  |

|------------|-------------------------------------------------------|-----------------------------------------------------|-------|--------------------------------------------------------------|--------|--|--|--|--|

| +1023/1024 | 011 1111 1111                                         | 1111 1111 1100 0000                                 | 0.999 | 0111 1111 1110 0000                                          | 0.999  |  |  |  |  |

| +1022/1024 | 011 1111 1110                                         | 1111 1111 1000 0000                                 | 0.998 | 0111 1111 1000 0000                                          | 0.998  |  |  |  |  |

| •••        |                                                       |                                                     |       |                                                              |        |  |  |  |  |

| +1/1024    | 000 0000 0001                                         | 0000 0000 0100 0000                                 | 0.001 | 0000 0000 0010 0000                                          | 0.001  |  |  |  |  |

| 0/1024     | 000 0000 0000                                         | 0000 0000 0000 0000                                 | 0.000 | 0000 0000 0000 0000                                          | 0.000  |  |  |  |  |

| -1/1024    | 101 1111 1111                                         | 0000 0000 0000 0000                                 | 0.000 | 1111 1111 1110 0000                                          | -0.001 |  |  |  |  |

|            |                                                       | •••                                                 |       |                                                              |        |  |  |  |  |

| -1023/1024 | 100 0000 0001                                         | 0000 0000 0000 0000                                 | 0.000 | 1000 0000 0010 0000                                          | -0.999 |  |  |  |  |

| -1024/1024 | 100 0000 0000                                         | 0000 0000 0000 0000                                 | 0.000 | 1000 0000 0000 0000                                          | -1.000 |  |  |  |  |

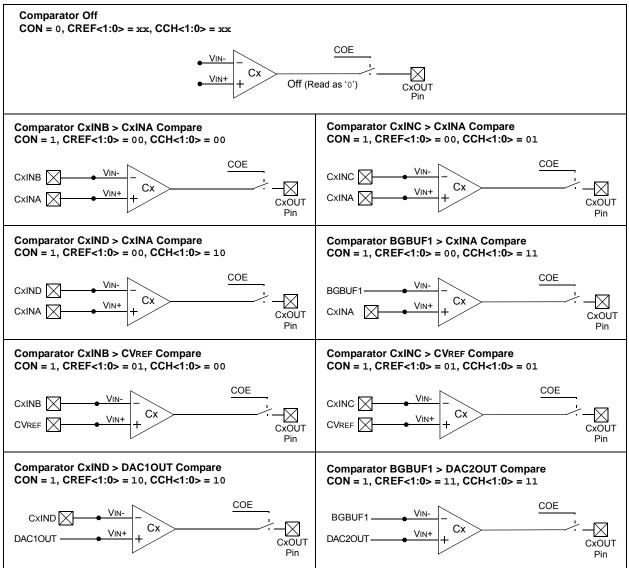

## FIGURE 22-2: INDIVIDUAL COMPARATOR CONFIGURATIONS

### **REGISTER 25-9: DEVREV: DEVICE REVISION REGISTER**

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0    |

|--------|-----|-----|-----|-----|-----|-----|--------|

| _      | _   |     | _   | _   | _   | _   | _      |

| bit 23 |     |     |     |     |     |     | bit 16 |

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | R    | R    | R    | R     |

|-------|-----|-----|-----|------|------|------|-------|

| _     | _   | _   | _   | REV3 | REV2 | REV1 | REV0  |

| bit 7 |     |     |     |      |      |      | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 23-4 Unimplemented: Read as '0'

bit 3-0 **REV<3:0>:** Minor Revision Identifier bits

# 25.4 Program Verification and Code Protection

For all devices in the PIC24FXXXXX family, code protection for the Boot Segment is controlled by the Configuration bit, BSS0, and the General Segment by the Configuration bit, GCP. These bits inhibit external reads and writes to the program memory space This has no direct effect in normal execution mode.

Write protection is controlled by bit, BWRP, for the Boot Segment and bit, GWRP, for the General Segment in the Configuration Word. When these bits are programmed to '0', internal write and erase operations to program memory are blocked.

## 25.5 In-Circuit Serial Programming

PIC24FXXXXX family microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock (PGECx) and data (PGEDx), and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

## 25.6 In-Circuit Debugger

When MPLAB® ICD 3, MPLAB REAL ICE™ or PICkit™ 3 is selected as a debugger, the in-circuit debugging functionality is enabled. This function allows simple debugging functions when used with MPLAB IDE. Debugging functionality is controlled through the PGECx and PGEDx pins.

To use the in-circuit debugger function of the device, the design must implement ICSP connections to  $\overline{\text{MCLR}}$ , VDD, Vss, PGECx, PGEDx and the pin pair. In addition, when the feature is enabled, some of the resources are not available for general use. These resources include the first 80 bytes of data RAM and two I/O pins.

**TABLE 27-1: THERMAL OPERATING CONDITIONS**

| Rating                                                                                                                                                                                                 | Symbol | Min | Тур         | Max  | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|-------------|------|------|

| Operating Junction Temperature Range                                                                                                                                                                   | TJ     | -40 | _           | +140 | °C   |

| Operating Ambient Temperature Range                                                                                                                                                                    | TA     | -40 | _           | +125 | °C   |

| Power Dissipation   Internal Chip Power Dissipation: $PINT = VDD \ x \ (IDD - \Sigma \ IOH)$ $I/O \ Pin \ Power \ Dissipation:   PI/O = \Sigma \ (\{VDD - VOH\} \ x \ IOH) + \Sigma \ (VOL \ x \ IOL)$ | PD     | ı   | PINT + PI/C | )    | W    |

| Maximum Allowed Power Dissipation                                                                                                                                                                      | PDMAX  | (   | Α           | W    |      |

TABLE 27-2: THERMAL PACKAGING CHARACTERISTICS

| Characteristic                           | Symbol | Тур  | Max | Unit | Notes |

|------------------------------------------|--------|------|-----|------|-------|

| Package Thermal Resistance, 20-Pin PDIP  | θЈА    | 62.4 | _   | °C/W | 1     |

| Package Thermal Resistance, 28-Pin SPDIP | θЈА    | 60   | _   | °C/W | 1     |

| Package Thermal Resistance, 20-Pin SSOP  | θЈА    | 108  | _   | °C/W | 1     |

| Package Thermal Resistance, 28-Pin SSOP  | θЈА    | 71   | _   | °C/W | 1     |

| Package Thermal Resistance, 20-Pin SOIC  | θЈА    | 75   | _   | °C/W | 1     |

| Package Thermal Resistance, 28-Pin SOIC  | θЈА    | 80.2 | _   | °C/W | 1     |

| Package Thermal Resistance, 20-Pin QFN   | θЈА    | 43   | _   | °C/W | 1     |

| Package Thermal Resistance, 28-Pin QFN   | θЈА    | 32   | _   | °C/W | 1     |

| Package Thermal Resistance, 44-Pin QFN   | θЈА    | 29   | _   | °C/W | 1     |

| Package Thermal Resistance, 44-Pin TQFP  | θЈА    | 40   | _   | °C/W | 1     |

| Package Thermal Resistance, 48-Pin UQFN  | θЈА    | 41   | _   | °C/W | 1     |

**Note 1:** Junction to ambient thermal resistance, Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.

TABLE 27-3: DC CHARACTERISTICS: TEMPERATURE AND VOLTAGE SPECIFICATIONS

| DC CHARACTERISTICS |          |                                                                  | Standard Operating Conditions Operating temperature |                    |     |       | s: 1.8V to 3.6V (PIC24F16KMXXX)<br>2.0V to 5.5V (PIC24FV16KMXXX)<br>-40°C $\leq$ TA $\leq$ +85°C for Industrial<br>-40°C $\leq$ TA $\leq$ +125°C for Extended |  |  |

|--------------------|----------|------------------------------------------------------------------|-----------------------------------------------------|--------------------|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Param<br>No.       | Symbol   | Characteristic                                                   | Min                                                 | Typ <sup>(1)</sup> | Max | Units | Conditions                                                                                                                                                    |  |  |

| DC10               | VDD      | Supply Voltage                                                   | 1.8                                                 | _                  | 3.6 | V     | For PIC24F devices                                                                                                                                            |  |  |

|                    |          |                                                                  | 2.0                                                 | _                  | 5.5 | V     | For PIC24FV devices                                                                                                                                           |  |  |

| DC12               | DC12 VDR | RAM Data Retention Voltage <sup>(2)</sup>                        | 1.6                                                 | _                  | _   | V     | For PIC24F devices                                                                                                                                            |  |  |

|                    |          |                                                                  | 1.8                                                 | _                  | _   | V     | For PIC24FV devices                                                                                                                                           |  |  |

| DC16               | VPOR     | VDD Start Voltage<br>to Ensure Internal<br>Power-on Reset Signal | Vss                                                 | _                  | 0.7 | V     |                                                                                                                                                               |  |  |

| DC17               | SVDD     | VDD Rise Rate<br>to Ensure Internal<br>Power-on Reset Signal     | 0.05                                                | _                  | _   | V/ms  | 0-3.3V in 0.1s<br>0-2.5V in 60 ms                                                                                                                             |  |  |

**Note 1:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

<sup>2:</sup> This is the limit to which VDD can be lowered without losing RAM data.

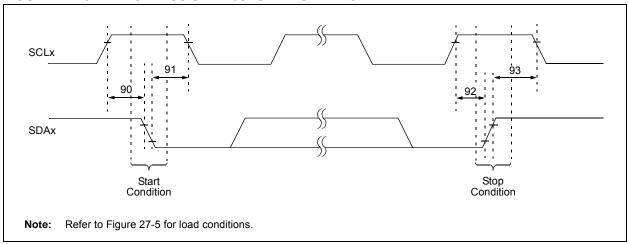

FIGURE 27-15: I<sup>2</sup>C™ BUS START/STOP BITS TIMING

TABLE 27-33: I<sup>2</sup>C™ BUS START/STOP BITS REQUIREMENTS (SLAVE MODE)

| Param.<br>No. | Symbol  | Characteristic                |              | Min  | Max | Units | Conditions                                            |

|---------------|---------|-------------------------------|--------------|------|-----|-------|-------------------------------------------------------|

| 90 Tsu:       | Tsu:sta | Start Condition<br>Setup Time | 100 kHz mode | 4700 | _   | ns    | Only relevant for Repeated Start condition            |

|               |         |                               | 400 kHz mode | 600  | _   |       |                                                       |

| 91            | THD:STA | Start Condition<br>Hold Time  | 100 kHz mode | 4000 | _   | ns    | After this period, the first clock pulse is generated |

|               |         |                               | 400 kHz mode | 600  | _   |       |                                                       |

| 92            | Tsu:sto | Stop Condition                | 100 kHz mode | 4700 | _   | ns    |                                                       |

|               |         | Setup Time                    | 400 kHz mode | 600  | _   |       |                                                       |

| 93            | THD:STO | Stop Condition<br>Hold Time   | 100 kHz mode | 4000 | _   | ns    |                                                       |

|               |         |                               | 400 kHz mode | 600  | _   |       |                                                       |

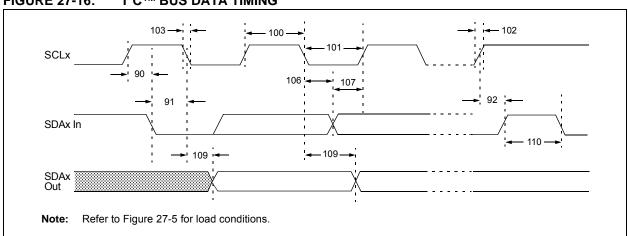

FIGURE 27-16: I<sup>2</sup>C™ BUS DATA TIMING

## 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | MILLIMETERS |          |          |      |  |

|-------------------------|-------------|----------|----------|------|--|

| Dimension               | MIN         | NOM      | MAX      |      |  |

| Number of Pins          | N           |          | 44       |      |  |

| Pitch                   | е           |          | 0.65 BSC |      |  |

| Overall Height          | Α           | 0.80     | 0.90     | 1.00 |  |

| Standoff                | A1          | 0.00     | 0.02     | 0.05 |  |

| Terminal Thickness      | A3          | 0.20 REF |          |      |  |

| Overall Width           | Е           |          | 8.00 BSC |      |  |

| Exposed Pad Width       | E2          | 6.25     | 6.45     | 6.60 |  |

| Overall Length          | О           | 8.00 BSC |          |      |  |

| Exposed Pad Length      | D2          | 6.25     | 6.45     | 6.60 |  |

| Terminal Width          | b           | 0.20     | 0.30     | 0.35 |  |

| Terminal Length         | L           | 0.30     | 0.40     | 0.50 |  |

| Terminal-to-Exposed-Pad | K           | 0.20     | -        | -    |  |

## Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated

- 3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension. usually without tolerance. for information purposes only.

Microchip Technology Drawing C04-103C Sheet 2 of 2

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our

knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data

Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### **Trademarks**

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MTP, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

Analog-for-the-Digital Age, Application Maestro, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, SQI, Serial Quad I/O, Total Endurance, TSHARC, UniWinDriver, WiperLock, ZENA and Z-Scale are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

GestIC and ULPP are registered trademarks of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2013, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

ISBN: 978-1-62077-358-1

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.