Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                   |                                                                               |

|---------------------------|-------------------------------------------------------------------------------|

| Product Status            | Active                                                                        |

| Core Processor            | PIC                                                                           |

| Core Size                 | 16-Bit                                                                        |

| Speed                     | 32MHz                                                                         |

| Connectivity              | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals               | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O             | 23                                                                            |

| Program Memory Size       | 16KB (5.5K x 24)                                                              |

| Program Memory Type       | FLASH                                                                         |

| EEPROM Size               | 512 x 8                                                                       |

| RAM Size                  | 2K x 8                                                                        |

| oltage - Supply (Vcc/Vdd) | 2V ~ 5V                                                                       |

| Oata Converters           | A/D 19x10b/12b; D/A 2x8b                                                      |

| Oscillator Type           | Internal                                                                      |

| perating Temperature      | -40°C ~ 125°C (TA)                                                            |

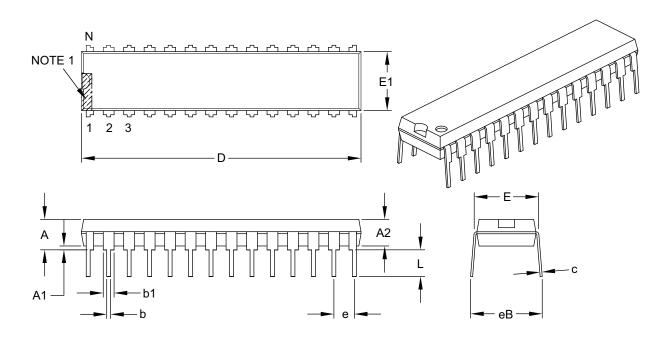

| Nounting Type             | Through Hole                                                                  |

| Package / Case            | 28-DIP (0.300", 7.62mm)                                                       |

| Supplier Device Package   | 28-SPDIP                                                                      |

| Purchase URL              | https://www.e-xfl.com/product-detail/microchip-technology/pic24fv16km202-e-sp |

TABLE 1-5: PIC24FV16KM204 FAMILY PINOUT DESCRIPTION (CONTINUED)

|          |                                  |                                  | F             |                        |                |                                  |                                  | FV            |                        |                |     |        |                                             |

|----------|----------------------------------|----------------------------------|---------------|------------------------|----------------|----------------------------------|----------------------------------|---------------|------------------------|----------------|-----|--------|---------------------------------------------|

|          |                                  | ı                                | Pin Numb      | er                     |                |                                  | ı                                | Pin Numb      | er                     |                |     |        |                                             |

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | I/O | Buffer | Description                                 |

| CTED1    | 11                               | 20                               | 17            | 7                      | 7              | 11                               | 2                                | 27            | 19                     | 21             | I   | ST     | CTMU Trigger Edge Inputs                    |

| CTED2    | 15                               | 23                               | 20            | 10                     | 11             | 15                               | 23                               | 20            | 10                     | 11             | I   | ST     | CTMU Trigger Edge Inputs                    |

| CTED3    | _                                | 19                               | 16            | 6                      | 6              | _                                | 19                               | 16            | 6                      | 6              | ı   | ST     | CTMU Trigger Edge Inputs                    |

| CTED4    | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | I   | ST     | CTMU Trigger Edge Inputs                    |

| CTED5    | 17                               | 25                               | 22            | 14                     | 15             | 17                               | 25                               | 22            | 14                     | 15             | ı   | ST     | CTMU Trigger Edge Inputs                    |

| CTED6    | 18                               | 26                               | 23            | 15                     | 16             | 18                               | 26                               | 23            | 15                     | 16             | ı   | ST     | CTMU Trigger Edge Inputs                    |

| CTED7    | _                                | _                                | _             | 5                      | 5              | _                                | _                                | _             | 5                      | 5              | ı   | ST     | CTMU Trigger Edge Inputs                    |

| CTED8    | _                                | _                                | _             | 13                     | 14             | _                                | _                                | _             | 13                     | 14             | ı   | ST     | CTMU Trigger Edge Inputs                    |

| CTED9    | _                                | 22                               | 19            | 9                      | 10             | _                                | 22                               | 19            | 9                      | 10             | ı   | ST     | CTMU Trigger Edge Inputs                    |

| CTED10   | 12                               | 17                               | 14            | 44                     | 48             | 12                               | 17                               | 14            | 44                     | 48             | ı   | ST     | CTMU Trigger Edge Inputs                    |

| CTED11   | _                                | 21                               | 18            | 8                      | 9              | _                                | 21                               | 18            | 8                      | 9              | ı   | ST     | CTMU Trigger Edge Inputs                    |

| CTED12   | 5                                | 5                                | 2             | 22                     | 24             | 5                                | 5                                | 2             | 22                     | 24             | I   | ST     | CTMU Trigger Edge Inputs                    |

| CTED13   | 6                                | 6                                | 3             | 23                     | 25             | 6                                | 6                                | 3             | 23                     | 25             | I   | ST     | CTMU Trigger Edge Inputs                    |

| CTPLS    | 16                               | 24                               | 21            | 11                     | 12             | 16                               | 24                               | 21            | 11                     | 12             | 0   | _      | CTMU Pulse Output                           |

| CVREF    | 17                               | 25                               | 22            | 14                     | 15             | 17                               | 25                               | 22            | 14                     | 15             | 0   | ANA    | Comparator Voltage Reference Output         |

| CVREF+   | 2                                | 2                                | 27            | 19                     | 21             | 2                                | 2                                | 27            | 19                     | 21             | I   | ANA    | Comparator Voltage Reference Positive Input |

| CVREF-   | 3                                | 3                                | 28            | 20                     | 22             | 3                                | 3                                | 28            | 20                     | 22             | I   | ANA    | Comparator Voltage Reference Negative Input |

| DAC1OUT  | _                                | 23                               | 20            | 10                     | 11             | _                                | 23                               | 20            | 10                     | 11             | 0   | ANA    | DAC1 Output                                 |

| DAC1REF+ | _                                | 2                                | 27            | 19                     | 21             | _                                | 2                                | 27            | 19                     | 21             | I   | ANA    | DAC1 Positive Voltage Reference Input       |

| DAC2OUT  | _                                | 25                               | 22            | 14                     | 15             | _                                | 25                               | 22            | 14                     | 15             | 0   | ANA    | DAC2 Output                                 |

| DAC2REF+ | _                                | 26                               | 23            | 15                     | 16             | _                                | 26                               | 23            | 15                     | 16             | I   | ANA    | DAC2 Positive Voltage Reference Input       |

| HLVDIN   | 15                               | 23                               | 20            | 10                     | 11             | 15                               | 23                               | 20            | 10                     | 11             | I   | ANA    | External High/Low-Voltage Detect Input      |

| IC1      | 14                               | 19                               | 16            | 6                      | 6              | 11                               | 19                               | 16            | 6                      | 6              | I   | ST     | MCCP1 Input Capture Input                   |

| IC2      | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | ı   | ST     | MCCP2 Input Capture Input                   |

| IC3      | _                                | 23                               | 20            | 13                     | 14             | _                                | 23                               | 20            | 13                     | 14             | Ī   | ST     | MCCP3 Input Capture Input                   |

| IC4      | _                                | 14                               | 11            | 5                      | 5              | _                                | 14                               | 11            | 5                      | 5              | I   | ST     | SCCP4 Input Capture Input                   |

| IC5      | _                                | 15                               | 12            | 12                     | 13             | _                                | 15                               | 12            | 12                     | 13             | I   | ST     | SCCP5 Input Capture Input                   |

| INT0     | 11                               | 16                               | 13            | 43                     | 47             | 11                               | 16                               | 13            | 43                     | 47             | I   | ST     | External Interrupt 0 Input                  |

| INT1     | 17                               | 25                               | 22            | 14                     | 15             | 17                               | 25                               | 22            | 14                     | 15             | I   | ST     | External Interrupt 1 Input                  |

| INT2     | 14                               | 20                               | 17            | 7                      | 7              | 15                               | 23                               | 20            | 10                     | 11             | I   | ST     | External Interrupt 2 Input                  |

**Legend:** ANA = Analog level input/output, ST = Schmitt Trigger input buffer, I<sup>2</sup>C™ = I<sup>2</sup>C/SMBus input buffer

# 2.4.1 CONSIDERATIONS FOR CERAMIC CAPACITORS

In recent years, large value, low-voltage, surface-mount ceramic capacitors have become very cost effective in sizes up to a few tens of microfarad. The low-ESR, small physical size and other properties make ceramic capacitors very attractive in many types of applications.

Ceramic capacitors are suitable for use with the internal voltage regulator of this microcontroller. However, some care is needed in selecting the capacitor to ensure that it maintains sufficient capacitance over the intended operating range of the application.

Typical low-cost,  $10~\mu F$  ceramic capacitors are available in X5R, X7R and Y5V dielectric ratings (other types are also available, but are less common). The initial tolerance specifications for these types of capacitors are often specified as  $\pm 10\%$  to  $\pm 20\%$  (X5R and X7R), or -20%/+80% (Y5V). However, the effective capacitance that these capacitors provide in an application circuit will also vary based on additional factors, such as the applied DC bias voltage and the temperature. The total in-circuit tolerance is, therefore, much wider than the initial tolerance specification.

The X5R and X7R capacitors typically exhibit satisfactory temperature stability (ex:  $\pm 15\%$  over a wide temperature range, but consult the manufacturer's data sheets for exact specifications). However, Y5V capacitors typically have extreme temperature tolerance specifications of  $\pm 22\%$ . Due to the extreme temperature tolerance, a 10 µF nominal rated Y5V type capacitor may not deliver enough total capacitance to meet minimum internal voltage regulator stability and transient response requirements. Therefore, Y5V capacitors are not recommended for use with the internal regulator if the application must operate over a wide temperature range.

In addition to temperature tolerance, the effective capacitance of large value ceramic capacitors can vary substantially, based on the amount of DC voltage applied to the capacitor. This effect can be very significant, but is often overlooked or is not always documented.

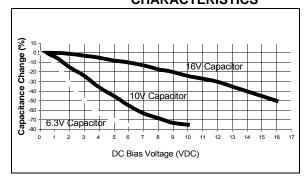

A typical DC bias voltage vs. capacitance graph for X7R type capacitors is shown in Figure 2-4.

FIGURE 2-4: DC BIAS VOLTAGE vs. CAPACITANCE CHARACTERISTICS

When selecting a ceramic capacitor to be used with the internal voltage regulator, it is suggested to select a high-voltage rating, so that the operating voltage is a small percentage of the maximum rated capacitor voltage. For example, choose a ceramic capacitor rated at 16V for the 3.3V or 2.5V core voltage. Suggested capacitors are shown in Table 2-1.

#### 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming  $^{\text{TM}}$  (ICSP $^{\text{TM}}$ ) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of ohms, not to exceed  $100\Omega$ .

Pull-up resistors, series diodes, and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits, and pins, Voltage Input High (VIH) and Voltage Input Low (VIL) requirements.

For device emulation, ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins), programmed into the device, matches the physical connections for the ICSP to the Microchip debugger/emulator tool.

For more information on available Microchip development tools connection requirements, refer to **Section 26.0 "Development Support"**.

#### 2.6 External Oscillator Pins

Many microcontrollers have options for at least two oscillators: a high-frequency Primary Oscillator and a low-frequency Secondary Oscillator (refer to for **Section 9.0 "Oscillator Configuration"**details).

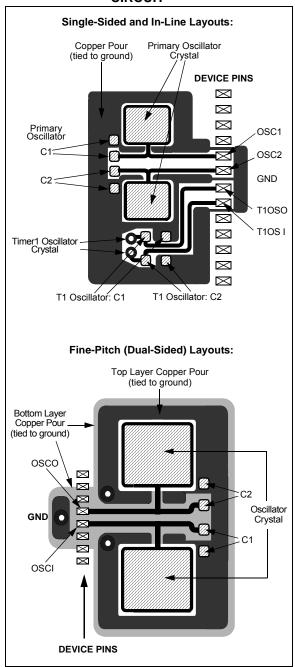

The oscillator circuit should be placed on the same side of the board as the device. Place the oscillator circuit close to the respective oscillator pins with no more than 0.5 inch (12 mm) between the circuit components and the pins. The load capacitors should be placed next to the oscillator itself, on the same side of the board.

Use a grounded copper pour around the oscillator circuit to isolate it from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed.

Layout suggestions are shown in Figure 2-5. In-line packages may be handled with a single-sided layout that completely encompasses the oscillator pins. With fine-pitch packages, it is not always possible to completely surround the pins and components. A suitable solution is to tie the broken guard sections to a mirrored ground layer. In all cases, the guard trace(s) must be returned to ground.

In planning the application's routing and I/O assignments, ensure that adjacent port pins and other signals, in close proximity to the oscillator, are benign (i.e., free of high frequencies, short rise and fall times, and other similar noise).

For additional information and design guidance on oscillator circuits, please refer to these Microchip Application Notes, available at the corporate web site (www.microchip.com):

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC™ and PICmicro<sup>®</sup> Devices"

- AN849, "Basic PICmicro<sup>®</sup> Oscillator Design"

- AN943, "Practical PICmicro<sup>®</sup> Oscillator Analysis and Design"

- · AN949, "Making Your Oscillator Work"

#### 2.7 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state. Alternatively, connect a 1  $k\Omega$  to 10  $k\Omega$  resistor to Vss on unused pins and drive the output to logic low.

FIGURE 2-5: SUGGESTED PLACEMENT

OF THE OSCILLATOR

CIRCUIT

TABLE 4-3: CPU CORE REGISTERS MAP

| File<br>Name | Addr. | Bit 15             | Bit 14  | Bit 13    | Bit 12    | Bit 11    | Bit 10    | Bit 9    | Bit 8    | Bit 7      | Bit 6    | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|--------------|-------|--------------------|---------|-----------|-----------|-----------|-----------|----------|----------|------------|----------|----------|----------|----------|----------|----------|----------|---------------|

| WREG0        | 0h    |                    | WREG0 ( |           |           |           |           |          |          |            |          |          |          | 0000     |          |          |          |               |

| WREG1        | 2h    |                    | WREG1 ( |           |           |           |           |          |          |            |          |          |          |          | 0000     |          |          |               |

| WREG2        | 4h    |                    |         |           |           |           |           |          | W        | REG2       |          |          |          |          |          |          |          | 0000          |

| WREG3        | 6h    |                    |         |           |           |           |           |          | W        | REG3       |          |          |          |          |          |          |          | 0000          |

| WREG4        | 8h    |                    |         |           |           |           |           |          | W        | REG4       |          |          |          |          |          |          |          | 0000          |

| WREG5        | Ah    |                    |         |           |           |           |           |          | W        | REG5       |          |          |          |          |          |          |          | 0000          |

| WREG6        | Ch    |                    |         |           |           |           |           |          | W        | REG6       |          |          |          |          |          |          |          | 0000          |

| WREG7        | Eh    |                    |         |           |           |           |           |          | W        | REG7       |          |          |          |          |          |          |          | 0000          |

| WREG8        | 10h   |                    |         |           |           |           |           |          | W        | REG8       |          |          |          |          |          |          |          | 0000          |

| WREG9        | 12h   |                    |         |           |           |           |           |          | W        | REG9       |          |          |          |          |          |          |          | 0000          |

| WREG10       | 14h   |                    |         |           |           |           |           |          | WI       | REG10      |          |          |          |          |          |          |          | 0000          |

| WREG11       | 16h   |                    |         |           |           |           |           |          | W        | REG11      |          |          |          |          |          |          |          | 0000          |

| WREG12       | 18h   |                    |         |           |           |           |           |          | WI       | REG12      |          |          |          |          |          |          |          | 0000          |

| WREG13       | 1Ah   |                    |         |           |           |           |           |          | WI       | REG13      |          |          |          |          |          |          |          | 0000          |

| WREG14       | 1Ch   |                    |         |           |           |           |           |          | WI       | REG14      |          |          |          |          |          |          |          | 0000          |

| WREG15       | 1Eh   |                    |         |           |           |           |           |          | WI       | REG15      |          |          |          |          |          |          |          | 0800          |

| SPLIM        | 20h   |                    |         |           |           |           |           |          | SPLI     | √ Register |          |          |          |          |          |          |          | xxxx          |

| PCL          | 2Eh   |                    |         |           |           |           |           |          | PCL      | Register   |          |          |          |          |          |          |          | 0000          |

| PCH          | 30h   | _                  | _       | _         | _         | _         | _         | _        | _        | PCH7       | PCH6     | PCH5     | PCH4     | PCH3     | PCH2     | PCH1     | PCH0     | 0000          |

| TBLPAG       | 32h   | _                  | _       | _         | _         | _         | _         | _        | _        | TBLPAG7    | TBLPAG6  | TBLPAG5  | TBLPAG4  | TBLPAG3  | TBLPAG2  | TBLPAG1  | TBLPAG0  | 0000          |

| PSVPAG       | 34h   | _                  |         |           |           |           |           |          |          |            |          |          | 0000     |          |          |          |          |               |

| RCOUNT       | 36h   | RCOUNT Register xx |         |           |           |           |           |          |          |            |          | xxxx     |          |          |          |          |          |               |

| SR           | 42h   |                    | _       | _         | _         | _         | _         | _        | DC       | IPL2       | IPL1     | IPL0     | RA       | N        | OV       | Z        | С        | 0000          |

| CORCON       | 44h   |                    |         |           |           |           |           |          |          |            |          |          | 0000     |          |          |          |          |               |

| DISICNT      | 52h   | _                  | _       | DISICNT13 | DISICNT12 | DISICNT11 | DISICNT10 | DISICNT9 | DISICNT8 | DISICNT7   | DISICNT6 | DISICNT5 | DISICNT4 | DISICNT3 | DISICNT2 | DISICNT1 | DISICNT0 | xxxx          |

**Legend:** x = unknown, u = unchanged, --= unimplemented, q = value depends on condition, r = reserved.

#### 6.4.1.1 Data EEPROM Bulk Erase

To erase the entire data EEPROM (bulk erase), the address registers do not need to be configured because this operation affects the entire data EEPROM. The following sequence helps in performing a bulk erase:

- 1. Configure NVMCON to Bulk Erase mode.

- Clear the NVMIF status bit and enable the NVM interrupt (optional).

- 3. Write the key sequence to NVMKEY.

- 4. Set the WR bit to begin the erase cycle.

- 5. Either poll the WR bit or wait for the NVM interrupt (NVMIF is set).

A typical bulk erase sequence is provided in Example 6-3.

#### 6.4.2 SINGLE-WORD WRITE

To write a single word in the data EEPROM, the following sequence must be followed:

- Erase one data EEPROM word (as mentioned in the previous section) if the PGMONLY bit (NVMCON<12>) is set to '1'.

- 2. Write the data word into the data EEPROM latch.

- 3. Program the data word into the EEPROM:

- Configure the NVMCON register to program one EEPROM word (NVMCON<5:0> = 0001xx).

- Clear the NVMIF status bit and enable the NVM interrupt (optional).

- Write the key sequence to NVMKEY.

- Set the WR bit to begin the erase cycle.

- Either poll the WR bit or wait for the NVM interrupt (NVMIF is set).

- To get cleared, wait until NVMIF is set.

A typical single-word write sequence is provided in Example 6-4.

#### **EXAMPLE 6-3: DATA EEPROM BULK ERASE**

```

// Set up NVMCON to bulk erase the data EEPROM

NVMCON = 0x4050;

// Disable Interrupts For 5 Instructions

asm volatile ("disi #5");

// Issue Unlock Sequence and Start Erase Cycle

__builtin_write_NVM();

```

#### EXAMPLE 6-4: SINGLE-WORD WRITE TO DATA EEPROM

```

int __attribute__ ((space(eedata))) eeData = 0x1234;

// New data to write to EEPROM

int newData;

The variable eeData must be a Global variable declared outside of any method

the code following this comment can be written inside the method that will execute the write

unsigned int offset;

// Set up NVMCON to erase one word of data EEPROM

NVMCON = 0x4004;

// Set up a pointer to the EEPROM location to be erased

// Initizlize lower word of address

offset = __builtin_tbloffset(&eeData);

__builtin_tblwtl(offset, newData);

// Write EEPROM data to write latch

asm volatile ("disi #5");

// Disable Interrupts For 5 Instructions

__builtin_write_NVM();

// Issue Unlock Sequence & Start Write Cycle

while(NVMCONbits.WR=1);

// Optional: Poll WR bit to wait for

// write sequence to complete

```

## REGISTER 7-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)

bit 4 WDTO: Watchdog Timer Time-out Flag bit

1 = WDT time-out has occurred

0 = WDT time-out has not occurred

bit 3 SLEEP: Wake-up from Sleep Flag bit

1 = Device has been in Sleep mode

0 = Device has not been in Sleep mode

**IDLE:** Wake-up from Idle Flag bit 1 = Device has been in Idle mode

0 = Device has not been in Idle mode

bit 1 BOR: Brown-out Reset Flag bit

bit 2

1 = A Brown-out Reset has occurred (the BOR is also set after a POR)

0 = A Brown-out Reset has not occurred

bit 0 **POR:** Power-on Reset Flag bit

1 = A Power-on Reset has occurred

0 = A Power-on Reset has not occurred

**Note 1:** All of the Reset status bits may be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the FWDTEN<1:0> Configuration bits are '11' (unprogrammed), the WDT is always enabled regardless of the SWDTEN bit setting.

- 3: This is implemented on PIC24FV16KMXXX parts only; not used on PIC24F16KMXXX devices.

TABLE 7-1: RESET FLAG BIT OPERATION

| Flag Bit          | Setting Event                                     | Clearing Event          |

|-------------------|---------------------------------------------------|-------------------------|

| TRAPR (RCON<15>)  | Trap Conflict Event                               | POR                     |

| IOPUWR (RCON<14>) | Illegal Opcode or Uninitialized W Register Access | POR                     |

| CM (RCON<9>)      | Configuration Mismatch Reset                      | POR                     |

| EXTR (RCON<7>)    | MCLR Reset                                        | POR                     |

| SWR (RCON<6>)     | RESET Instruction                                 | POR                     |

| WDTO (RCON<4>)    | WDT Time-out                                      | PWRSAV Instruction, POR |

| SLEEP (RCON<3>)   | PWRSAV #SLEEP Instruction                         | POR                     |

| IDLE (RCON<2>)    | PWRSAV #IDLE Instruction                          | POR                     |

| BOR (RCON<1>)     | POR, BOR                                          | _                       |

| POR (RCON<0>)     | POR                                               | _                       |

**Note:** All Reset flag bits may be set or cleared by the user software.

# 7.2.1 POR AND LONG OSCILLATOR START-UP TIMES

The oscillator start-up circuitry and its associated delay timers are not linked to the device Reset delays that occur at power-up. Some crystal circuits (especially low-frequency crystals) will have a relatively long start-up time. Therefore, one or more of the following conditions is possible after SYSRST is released:

- · The oscillator circuit has not begun to oscillate.

- The Oscillator Start-up Timer (OST) has not expired (if a crystal oscillator is used).

- The PLL has not achieved a lock (if PLL is used).

The device will not begin to execute code until a valid clock source has been released to the system. Therefore, the oscillator and PLL start-up delays must be considered when the Reset delay time must be known.

# 7.2.2 FAIL-SAFE CLOCK MONITOR (FSCM) AND DEVICE RESETS

If the FSCM is enabled, it will begin to monitor the system clock source when SYSRST is released. If a valid clock source is not available at this time, the device will automatically switch to the FRC Oscillator and the user can switch to the desired crystal oscillator in the Trap Service Routine (TSR).

# 7.3 Special Function Register Reset States

Most of the Special Function Registers (SFRs) associated with the PIC24F CPU and peripherals are reset to a particular value at a device Reset. The SFRs are grouped by their peripheral or CPU function and their Reset values are specified in each section of this manual.

The Reset value for each SFR does not depend on the type of Reset, with the exception of four registers. The Reset value for the Reset Control register, RCON, will depend on the type of device Reset. The Reset value for the Oscillator Control register, OSCCON, will depend on the type of Reset and the programmed values of the FNOSCx bits in the Flash Configuration Word (FOSCSEL<2:0>); see Table 7-2. The RCFGCAL and NVMCON registers are only affected by a POR.

#### 7.4 Brown-out Reset (BOR)

The PIC24FXXXXX family devices implement a BOR circuit, which provides the user several configuration and power-saving options. The BOR is controlled by the BORV<1:0> and BOREN<1:0> Configuration bits (FPOR<6:5,1:0>). There are a total of four BOR configurations, which are provided in Table 7-3.

The BOR threshold is set by the BORV<1:0> bits. If BOR is enabled (any values of BOREN<1:0>, except '00'), any drop of VDD below the set threshold point will reset the device. The chip will remain in BOR until VDD rises above the threshold.

If the Power-up Timer is enabled, it will be invoked after VDD rises above the threshold. Then, it will keep the chip in Reset for an additional time delay, TPWRT, if VDD drops below the threshold while the Power-up Timer is running. The chip goes back into a BOR and the Power-up Timer will be initialized. Once VDD rises above the threshold, the Power-up Timer will execute the additional time delay.

BOR and the Power-up Timer (PWRT) are independently configured. Enabling the Brown-out Reset does not automatically enable the PWRT.

#### 7.4.1 LOW-POWER BOR (LPBOR)

The Low-Power BOR is an alternate setting for the BOR, designed to consume minimal power. In LPBOR mode, BORV<1:0> (FPOR<6:5>) = 00. The BOR trip point is approximately 2.0V. Due to the low current consumption, the accuracy of the LPBOR mode can vary.

Unlike the other BOR modes, LPBOR mode will not cause a device Reset when VDD drops below the trip point. Instead, it re-arms the POR circuit to ensure that the device will reset properly in the event that VDD continues to drop below the minimum operating voltage.

The device will continue to execute code when VDD is below the level of the LPBOR trip point. A device that requires falling edge BOR protection to prevent code from improperly executing should use one of the other BOR voltage settings.

#### **REGISTER 8-2: CORCON: CPU CONTROL REGISTER**

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | R/C-0, HSC          | R/W-0              | U-0 | U-0   |

|-------|-----|-----|-----|---------------------|--------------------|-----|-------|

| _     | _   | _   | _   | IPL3 <sup>(2)</sup> | PSV <sup>(1)</sup> | _   |       |

| bit 7 |     |     |     |                     |                    |     | bit 0 |

| Legend:           | C = Clearable bit | HSC = Hardware Settable/Clearable bit |                    |  |  |

|-------------------|-------------------|---------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read as '0'    |                    |  |  |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared                  | x = Bit is unknown |  |  |

bit 15-4 Unimplemented: Read as '0'

bit 3 IPL3: CPU Interrupt Priority Level Status bit<sup>(2)</sup>

1 = CPU Interrupt Priority Level is greater than 70 = CPU Interrupt Priority Level is 7 or less

bit 1-0 **Unimplemented:** Read as '0'

Note 1: See Register 3-2 for the description of this bit, which is not dedicated to interrupt control functions.

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

Note: Bit 2 is described in Section 3.0 "CPU".

NOTES:

#### REGISTER 12-1: T1CON: TIMER1 CONTROL REGISTER

| R/W-0  | U-0 | R/W-0 | U-0 | U-0 | U-0 | R/W-0                | R/W-0                |

|--------|-----|-------|-----|-----|-----|----------------------|----------------------|

| TON    | _   | TSIDL | _   | _   | _   | TECS1 <sup>(1)</sup> | TECS0 <sup>(1)</sup> |

| bit 15 |     |       |     |     |     |                      | bit 8                |

| U-0   | R/W-0 | R/W-0  | R/W-0  | U-0 | R/W-0 | R/W-0 | U-0   |

|-------|-------|--------|--------|-----|-------|-------|-------|

| _     | TGATE | TCKPS1 | TCKPS0 | _   | TSYNC | TCS   | _     |

| bit 7 |       |        |        |     |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 TON: Timer1 On bit

1 = Starts 16-bit Timer1

0 = Stops 16-bit Timer1

bit 14 **Unimplemented:** Read as '0'

bit 13 TSIDL: Timer1 Stop in Idle Mode bit

1 = Discontinues module operation when device enters Idle mode

0 = Continues module operation in Idle mode

bit 12-10 Unimplemented: Read as '0'

bit 9-8 **TECS<1:0>:** Timer1 Extended Clock Select bits<sup>(1)</sup>

11 = Reserved; do not use

10 = Timer1 uses the LPRC as the clock source 01 = Timer1 uses the External Clock (EC) from T1CK

00 = Timer1 uses the Secondary Oscillator (SOSC) as the clock source

bit 7 **Unimplemented:** Read as '0'

bit 6 TGATE: Timer1 Gated Time Accumulation Enable bit

When TCS = 1: This bit is ignored. When TCS = 0:

1 = Gated time accumulation is enabled0 = Gated time accumulation is disabled

bit 5-4 TCKPS<1:0>: Timer1 Input Clock Prescale Select bits

11 = 1:256 10 = 1:64 01 = 1:8 00 = 1:1

bit 3 Unimplemented: Read as '0'

bit 2 TSYNC: Timer1 External Clock Input Synchronization Select bit

When TCS = 1:

1 = Synchronizes External Clock input

0 = Does not synchronize External Clock input

When TCS = 0: This bit is ignored.

bit 1 TCS: Timer1 Clock Source Select bit

1 = Timer1 clock source is selected by TECS<1:0>

0 = Internal clock (Fosc/2)

bit 0 **Unimplemented:** Read as '0'

**Note 1:** The TECSx bits are valid only when TCS = 1.

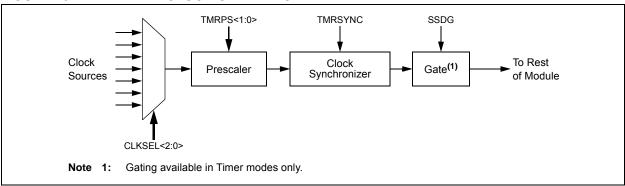

#### 13.1 Time Base Generator

The Timer Clock Generator (TCG) generates a clock for the module's internal time base, using one of the clock signals already available on the microcontroller. This is used as the time reference for the module in its three major modes. The internal time base is shown in Figure 13-2.

There are eight inputs available to the clock generator, which are selected using the CLKSEL<2:0> bits (CCPxCON1L<10:8>). Available sources include the FRC and LPRC, the Secondary Oscillator, and the TCLKI External Clock inputs. The system clock is the default source (CLKSEL<2:0> = 000). On PIC24FV16KM204 family devices, clock sources to the MCCPx module must be synchronized with the system clock; as a result, when clock sources are selected, clock input timing restrictions or module operating restrictions may exist. Table 13-1 describes which time base sources are valid for the various operating modes.

TABLE 13-1: VALID TIMER OPTIONS FOR MCCPx/SCCPx MODES

| CLKSEL               | Tir                 | ner                  | Input   | Output  |

|----------------------|---------------------|----------------------|---------|---------|

| <2:0> <sup>(1)</sup> | Sync <sup>(2)</sup> | Async <sup>(3)</sup> | Capture | Compare |

| 111                  | Х                   | _                    | _       |         |

| 110                  | Х                   | _                    | _       | _       |

| 101                  | Х                   | _                    | _       | _       |

| 011                  | Х                   | _                    | _       |         |

| 010                  | Х                   | _                    | _       | _       |

| 001                  | Х                   | _                    | _       | _       |

| 000(4)               | _                   | Х                    | Х       | Х       |

- **Note 1:** See Register 13-1 for the description of the time base sources.

- 2: Synchronous Operation: TMRSYNC (CCPxCON1L<11>) = 1 and TRIGEN (CCPxCON1H<7>) = 0.

- **3:** Asynchronous Operation: (TMRSYNC = 0) or Triggered mode (TRIGEN = 1).

- **4:** When CLKSEL<2:0> = 000, the TMRSYNC bit must be cleared.

FIGURE 13-2: TIMER CLOCK GENERATOR

#### REGISTER 14-8: SSPxADD: MSSPx SLAVE ADDRESS/BAUD RATE GENERATOR REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 | _   |     |     |     |     |     | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| ADD7  | ADD6  | ADD5  | ADD4  | ADD3  | ADD2  | ADD1  | ADD0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 **Unimplemented:** Read as '0'

bit 7-0 ADD<7:0>: Slave Address/Baud Rate Generator Value bits

SPI Master and I<sup>2</sup>C™ Master modes:

Reload value for the Baud Rate Generator. Clock period is (([SPxADD] + 1) \* 2)/Fosc.

I<sup>2</sup>C Slave modes:

Represents 7 or 8 bits of the slave address, depending on the addressing mode used:

7-Bit mode: Address is ADD<7:1>; ADD<0> is ignored.

10-Bit LSb mode: ADD<7:0> are the Least Significant bits of the address.

10-Bit MSb mode: ADD<2:1> are the two Most Significant bits of the address; ADD<7:3> are always

'11110' as a specification requirement; ADD<0> is ignored.

#### REGISTER 14-9: SSPxMSK: I<sup>2</sup>C™ SLAVE ADDRESS MASK REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-1               |

|-------|-------|-------|-------|-------|-------|-------|---------------------|

| MSK7  | MSK6  | MSK5  | MSK4  | MSK3  | MSK2  | MSK1  | MSK0 <sup>(1)</sup> |

| bit 7 |       |       |       |       |       |       | bit 0               |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 Unimplemented: Read as '0'

bit 7-0 MSK<7:0>: Slave Address Mask Select bits<sup>(1)</sup>

1 = Masking of corresponding bit of SSPxADD is enabled

0 = Masking of corresponding bit of SSPxADD is disabled

Note 1: MSK0 is not used as a mask bit in 7-bit addressing.

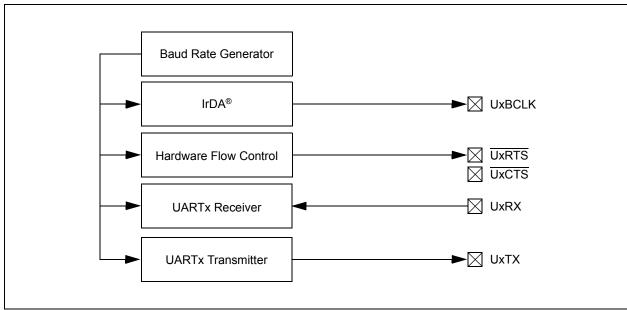

# 15.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

Note:

This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the Universal Asynchronous Receiver Transmitter, refer to the "PIC24F Family Reference Manual", "UART" (DS39708).

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in this PIC24F device family. The UART is a full-duplex, asynchronous system that can communicate with peripheral devices, such as personal computers, LIN/J2602, RS-232 and RS-485 interfaces. This module also supports a hardware flow control option with the  $\overline{\text{UxCTS}}$  and  $\overline{\text{UxRTS}}$  pins, and also includes an IrDA® encoder and decoder.

The primary features of the UART module are:

- Full-Duplex, 8-Bit or 9-Bit Data Transmission through the UxTX and UxRX Pins

- Even, Odd or No Parity Options (for 8-bit data)

- · One or Two Stop bits

- Hardware Flow Control Option with UxCTS and UxRTS Pins

- Fully Integrated Baud Rate Generator (IBRG) with 16-Bit Prescaler

- Baud Rates Ranging from 1 Mbps to 15 bps at 16 MIPS

- 4-Deep, First-In-First-Out (FIFO) Transmit Data Buffer

- · 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-Bit mode with Address Detect (9<sup>th</sup> bit = 1)

- · Transmit and Receive Interrupts

- · Loopback mode for Diagnostic Support

- · Support for Sync and Break Characters

- · Supports Automatic Baud Rate Detection

- IrDA® Encoder and Decoder Logic

- · 16x Baud Clock Output for IrDA Support

A simplified block diagram of the UARTx module is shown in Figure 15-1. The UARTx module consists of these important hardware elements:

- · Baud Rate Generator

- · Asynchronous Transmitter

- Asynchronous Receiver

Note:

Throughout this section, references to register and bit names that may be associated with a specific USART module are referred to generically by the use of 'x' in place of the specific module number. Thus, "UxSTA" might refer to the USART Status register for either USART1 or USART2.

FIGURE 15-1: UARTX MODULE SIMPLIFIED BLOCK DIAGRAM

### REGISTER 15-2: UxSTA: UARTX STATUS AND CONTROL REGISTER (CONTINUED)

| bit 5 | ADDEN: Address Character Detect bit (bit 8 of received data = 1)                                                                                                           |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul><li>1 = Address Detect mode is enabled; if 9-bit mode is not selected, this does not take effect</li><li>0 = Address Detect mode is disabled</li></ul>                 |

| bit 4 | RIDLE: Receiver Idle bit (read-only)                                                                                                                                       |

|       | 1 = Receiver is Idle                                                                                                                                                       |

|       | 0 = Receiver is active                                                                                                                                                     |

| bit 3 | PERR: Parity Error Status bit (read-only)                                                                                                                                  |

|       | <ul><li>1 = Parity error has been detected for the current character (character at the top of the receive FIFO)</li><li>0 = Parity error has not been detected</li></ul>   |

| bit 2 | FERR: Framing Error Status bit (read-only)                                                                                                                                 |

|       | <ul><li>1 = Framing error has been detected for the current character (character at the top of the receive FIFO)</li><li>0 = Framing error has not been detected</li></ul> |

| bit 1 | OERR: Receive Buffer Overrun Error Status bit (clear/read-only)                                                                                                            |

|       | 1 = Receive buffer has overflowed                                                                                                                                          |

|       | 0 = Receive buffer has not overflowed (clearing a previously set OERR bit (1 $\rightarrow$ 0 transition) will reset the receiver buffer and the RSR to the empty state)    |

| bit 0 | URXDA: UARTx Receive Buffer Data Available bit (read-only)                                                                                                                 |

|       | 1 = Receive buffer has data; at least one more characters can be read                                                                                                      |

#### REGISTER 17-1: CLCxCONL: CLCx CONTROL REGISTER (LOW) (CONTINUED)

bit 2-0 MODE<2:0>: CLCx Mode bits

111 = Cell is a 1-input transparent latch with S and R

110 = Cell is a JK flip-flop with R

101 = Cell is a 2-input D flip-flop with R

100 = Cell is a 1-input D flip-flop with S and R

011 = Cell is an SR latch

010 = Cell is a 4-input AND

001 = Cell is an OR-XOR

000 = Cell is a AND-OR

#### REGISTER 17-2: CLCxCONH: CLCx CONTROL REGISTER (HIGH)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-----|-------|-------|-------|-------|

| _     | _   | _   | _   | G4POL | G3POL | G2POL | G1POL |

| bit 7 |     |     |     |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-4 Unimplemented: Read as '0'

bit 3 G4POL: Gate 4 Polarity Control bit

1 = The output of Channel 4 logic is inverted when applied to the logic cell

0 = The output of Channel 4 logic is not inverted

bit 2 G3POL: Gate 3 Polarity Control bit

1 = The output of Channel 3 logic is inverted when applied to the logic cell

0 = The output of Channel 3 logic is not inverted

bit 1 G2POL: Gate 2 Polarity Control bit

1 = The output of Channel 2 logic is inverted when applied to the logic cell

0 = The output of Channel 2 logic is not inverted

bit 0 **G1POL:** Gate 1 Polarity Control bit

1 = The output of Channel 1 logic is inverted when applied to the logic cell

0 = The output of Channel 1 logic is not inverted

#### REGISTER 17-4: CLCxGLSL: CLCx GATE LOGIC INPUT SELECT LOW REGISTER

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------|-------|-------|-------|

| G2D4T  | G2D4N | G2D3T | G2D3N | G2D2T | G2D2N | G2D1T | G2D1N |

| bit 15 |       |       |       |       |       |       | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| G1D4T | G1D4N | G1D3T | G1D3N | G1D2T | G1D2N | G1D1T | G1D1N |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15 | G2D4T: Gate 2 Data Source 4 True Enable bit                  |

|--------|--------------------------------------------------------------|

|        | 1 = The Data Source 4 inverted signal is enabled for Gate 2  |

|        | 0 = The Data Source 4 inverted signal is disabled for Gate 2 |

| bit 14 | G2D4N: Gate 2 Data Source 4 Negated Enable bit               |

|        | 1 = The Data Source 4 inverted signal is enabled for Gate 2  |

|        | 0 = The Data Source 4 inverted signal is disabled for Gate 2 |

| bit 13 | G2D3T: Gate 2 Data Source 3 True Enable bit                  |

|        | 1 = The Data Source 3 inverted signal is enabled for Gate 2  |

|        | 0 = The Data Source 3 inverted signal is disabled for Gate 2 |

| bit 12 | G2D3N: Gate 2 Data Source 3 Negated Enable bit               |

|        | 1 = The Data Source 3 inverted signal is enabled for Gate 2  |

|        | 0 = The Data Source 3 inverted signal is disabled for Gate 2 |

| bit 11 | G2D2T: Gate 2 Data Source 2 True Enable bit                  |

|        | 1 = The Data Source 2 inverted signal is enabled for Gate 2  |

|        | 0 = The Data Source 2 inverted signal is disabled for Gate 2 |

| bit 10 | G2D2N: Gate 2 Data Source 2 Negated Enable bit               |

|        | 1 = The Data Source 2 inverted signal is enabled for Gate 2  |

|        | 0 = The Data Source 2 inverted signal is disabled for Gate 2 |

| bit 9  | G2D1T: Gate 2 Data Source 1 True Enable bit                  |

|        | 1 = The Data Source 1 inverted signal is enabled for Gate 2  |

|        | 0 = The Data Source 1 inverted signal is disabled for Gate 2 |

| bit 8  | <b>G2D1N:</b> Gate 2 Data Source 1 Negated Enable bit        |

|        | 1 = The Data Source 2 inverted signal is enabled for Gate 1  |

|        | 0 = The Data Source 2 inverted signal is disabled for Gate 1 |

| bit 7  | G1D4T: Gate 1 Data Source 4 True Enable bit                  |

|        | 1 = The Data Source 4 inverted signal is enabled for Gate 1  |

|        | 0 = The Data Source 4 inverted signal is disabled for Gate 1 |

| bit 6  | G1D4N: Gate 1 Data Source 4 Negated Enable bit               |

|        | 1 = The Data Source 4 inverted signal is enabled for Gate 1  |

|        | 0 = The Data Source 4 inverted signal is disabled for Gate 1 |

| bit 5  | G1D3T: Gate 1 Data Source 3 True Enable bit                  |

|        | 1 = The Data Source 3 inverted signal is enabled for Gate 1  |

|        | 0 = The Data Source 3 inverted signal is disabled for Gate 1 |

| bit 4  | G1D3N: Gate 1 Data Source 3 Negated Enable bit               |

|        | 1 = The Data Source 3 inverted signal is enabled for Gate 1  |

|        | 0 = The Data Source 3 inverted signal is disabled for Gate 1 |

#### REGISTER 19-5: AD1CHS: A/D SAMPLE SELECT REGISTER

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| CH0NB2 | CH0NB1 | CH0NB0 | CH0SB4 | CH0SB3 | CH0SB2 | CH0SB1 | CH0SB0 |

| bit 15 |        |        |        |        |        |        | bit 8  |

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| CH0NA2 | CH0NA1 | CH0NA0 | CH0SA4 | CH0SA3 | CH0SA2 | CH0SA1 | CH0SA0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

```

bit 15-13

CH0NB<2:0>: Sample B Channel 0 Negative Input Select bits

111 = AN6^{(1)}

110 = AN5<sup>(2)</sup>

101 = AN4

100 = AN3

011 = AN2

010 = AN1

001 = AN0

```

bit 12-8 CH0SB<4:0>: S/H Amplifier Positive Input Select for MUX B Multiplexer Setting bits

```

000 = AVss

11111 = Unimplemented, do not use

11110 = AVDD^{(3)}

11101 = AVss<sup>(3)</sup>

11100 = Upper guardband rail (0.785 * VDD)

11011 = Lower guardband rail (0.215 * VDD)

11010 = Internal Band Gap Reference (VBG)(3)

11000-11001 = Unimplemented, do not use

10001 = No channels are connected, all inputs are floating (used for CTMU)

10111 = No channels are connected, all inputs are floating (used for CTMU)

10110 = No channels are connected, all inputs are floating (used for CTMU temperature sensor input);

does not require the corresponding CTMEN22 (AD1CTMENH<6>) bit)

10101 = Channel 0 positive input is AN21

10100 = Channel 0 positive input is AN20

10011 = Channel 0 positive input is AN19

10010 = Channel 0 positive input is AN18<sup>(2)</sup>

10001 = Channel 0 positive input is AN17<sup>(2)</sup>

01001 = Channel 0 positive input is AN9

01000 = Channel 0 positive input is AN8<sup>(1)</sup>

00111 = Channel 0 positive input is AN7<sup>(1)</sup>

00110 = Channel 0 positive input is AN6<sup>(1)</sup>

00101 = Channel 0 positive input is AN5<sup>(2)</sup>

00100 = Channel 0 positive input is AN4

```

- Note 1: This is implemented on 44-pin devices only.

- This is implemented on 28-pin and 44-pin devices only.

00011 = Channel 0 positive input is AN3 00010 = Channel 0 positive input is AN2 00001 = Channel 0 positive input is AN1 00000 = Channel 0 positive input is AN0

3: The band gap value used for this input is 2x or 4x the internal VBG, which is selected when PVCFG<1:0> = 1x.

TABLE 27-6: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

| DC CHARACTERISTICS |                |         | Operating temperatu |       | <b>2.0V</b> to -40°C ≤ | 1.8V to 3.6V (PIC24F16KMXXX)<br>2.0V to 5.5V (PIC24FV16KMXXX)<br>-40°C ≤ TA ≤ +85°C for Industrial<br>-40°C ≤ TA ≤ +125°C for Extended |  |  |

|--------------------|----------------|---------|---------------------|-------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Parameter No.      | Device         | Typical | Max                 | Units | Conditions             |                                                                                                                                        |  |  |

| IDD Current        |                |         |                     |       |                        |                                                                                                                                        |  |  |

| D20                | PIC24FV16KMXXX | 269     | 450                 | μΑ    | 2.0V                   |                                                                                                                                        |  |  |

|                    |                | 465     | 830                 | μA    | 5.0V                   | 0.5 MIPS,                                                                                                                              |  |  |

|                    | PIC24F16KMXXX  | 200     | 330                 | μA    | 1.8V                   | Fosc = 1 MHz <sup>(1)</sup>                                                                                                            |  |  |

|                    |                | 410     | 750                 | μΑ    | 3.3V                   |                                                                                                                                        |  |  |

| DC22               | PIC24FV16KMXXX | 490     | _                   | μA    | 2.0V                   |                                                                                                                                        |  |  |

|                    |                | 880     | _                   | μA    | 5.0V                   | 1 MIPS,                                                                                                                                |  |  |

|                    | PIC24F16KMXXX  | 407     | 1                   | μΑ    | 1.8V                   | Fosc = 2 MHz <sup>(1)</sup>                                                                                                            |  |  |

|                    |                | 800     | _                   | μA    | 3.3V                   |                                                                                                                                        |  |  |

| DC24               | PIC24FV16KMXXX | 13.0    | 15.0                | mA    | 5.0V                   | 16 MIPS,                                                                                                                               |  |  |

|                    | PIC24F16KMXXX  | 12.0    | 13.0                | mA    | 3.3V                   | Fosc = 32 MHz <sup>(1)</sup>                                                                                                           |  |  |

| DC26               | PIC24FV16KMXXX | 2.0     | _                   | mA    | 2.0V                   |                                                                                                                                        |  |  |

|                    |                | 3.5     | 1                   | mA    | 5.0V                   | FRC (4 MIPS),                                                                                                                          |  |  |

|                    | PIC24F16KMXXX  | 1.80    | _                   | mA    | 1.8V                   | Fosc = 8 MHz                                                                                                                           |  |  |

|                    |                | 3.40    |                     | mA    | 3.3V                   |                                                                                                                                        |  |  |

| DC30               | PIC24FV16KMXXX | 48.0    | 250                 | μΑ    | 2.0V                   |                                                                                                                                        |  |  |

|                    |                | 75.0    | 275                 | μΑ    | 5.0V                   | LPRC (15.5 KIPS),                                                                                                                      |  |  |

|                    | PIC24F16KMXXX  | 8.1     | 28.0                | μΑ    | 1.8V                   | Fosc = 31 kHz                                                                                                                          |  |  |

|                    |                | 13.50   | 55.00               | μA    | 3.3V                   |                                                                                                                                        |  |  |

**Legend:** Unshaded rows represent PIC24F16KMXXX devices and shaded rows represent PIC24FV16KMXXX devices.

**Note 1:** The oscillator is in External Clock mode (FOSCSEL<2:0> = 010, FOSC<1:0> = 00).

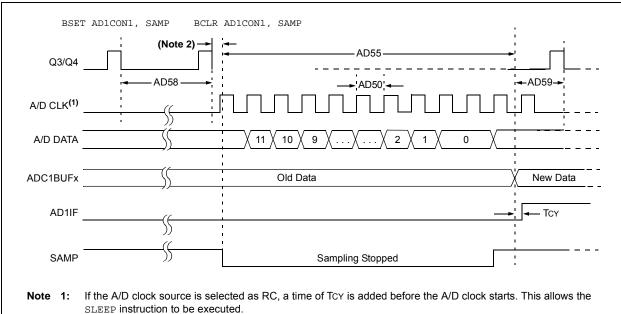

#### FIGURE 27-19: A/D CONVERSION TIMING

SLEEP instruction to be executed.

2: This is a minimal RC delay (typically 100 ns) which also disconnects the holding capacitor from the analog input.

#### TABLE 27-38: A/D CONVERSION TIMING REQUIREMENTS<sup>(1)</sup>

| Orange of Orange in the Orange |       |                                                   |                                                     |      |          |               |                                                                                                                                            |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------------------------------------------------|-----------------------------------------------------|------|----------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| AC CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |                                                   | Standard Operating Conditions Operating temperature |      |          | <b>2.0V</b> 1 | as: 1.8V to 3.6V (PIC24F16KM204)<br>2.0V to 5.5V (PIC24FV16KM204)<br>-40°C ≤ TA ≤ +85°C for Industrial<br>-40°C ≤ TA ≤ +125°C for Extended |  |  |  |  |

| Param<br>No.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Sym   | Characteristic                                    | Min.                                                | Тур  | Max.     | Units         | Conditions                                                                                                                                 |  |  |  |  |

| Clock Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |                                                   |                                                     |      |          |               |                                                                                                                                            |  |  |  |  |

| AD50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | TAD   | A/D Clock Period                                  | 600                                                 | _    | _        | ns            | Tcy = 75 ns, AD1CON3 in default state                                                                                                      |  |  |  |  |