Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 23                                                                            |

| Program Memory Size        | 16KB (5.5K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5V                                                                       |

| Data Converters            | A/D 19x10b/12b; D/A 2x8b                                                      |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                |

| Supplier Device Package    | 28-SOIC                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fv16km202-i-so |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Pin Diagrams (Continued)**

|          | 28-Pin QFN <sup>(1)</sup>                                                            | 22<br>21 RB13<br>20 RB12                         |

|----------|--------------------------------------------------------------------------------------|--------------------------------------------------|

|          | RB3 4<br>Vss 5<br>RA2 6<br>RA3 7<br><u>8 9 10 11 12 <b>13</b> 1</u>                  | 18 RB10<br>17 RA6 or VDDcore<br>16 RA7<br>15 RB9 |

|          | R 85<br>R 85<br>R 85<br>R 82<br>R 82<br>R 82<br>R 82<br>R 82<br>R 82<br>R 82<br>R 82 | 5<br>0<br>2<br>2                                 |

| Pin      | Pin Features                                                                         | Pin Features                                     |

|          | PIC24FXXKMX02                                                                        | PIC24FVXXKMX02                                   |

| 1        | PGED1/AN2/CTCMP/ULPWU/C1IND/ / / /CN4/I                                              | RB0                                              |

| 2        | PGEC1/ / /AN3/C1INC/ / /CTED12/CN                                                    | I5/RB1                                           |

| 3        | / /AN4/C1INB/ / /U1RX/TCKIB/CTED1                                                    | 13/CN6/RB2                                       |

| 4        | /AN5/C1INA/ / /CN7/RB3                                                               |                                                  |

| 5        | Vss                                                                                  |                                                  |

| 6        | OSCI/CLKI/AN13/CN30/RA2                                                              |                                                  |

| 7        | OSCO/CLKO/AN14/CN29/RA3                                                              |                                                  |

| 8        | SOSCI/AN15/ / /CN1/RB4                                                               |                                                  |

| 9        | SOSCO/SCLKI/AN16/PWRLCLK/ /CN0/RA4                                                   |                                                  |

| 10       |                                                                                      |                                                  |

| 11       | PGED3/AN17/ASDA1/ / /OC1E/CLCINA/CN27/RB5                                            |                                                  |

| 12       | PGEC3/AN18/ASCL1/ / /OC1F/CLCINB/CN24/RB6<br>AN19/U1TX/INT0/CN23/RB7                 | AN19/U1TX/ /OC1A/INT0/CN23/RB7                   |

| 13<br>14 | AN19/0112/IN10/CN23/RB7<br>AN20/SCL1/U1CTS/C3OUT/OC1B/CTED10/CN22/RB8                | AN 19/011X/ /OCTA/IN10/CN23/RB7                  |

| 14       | AN21/SDA1/T1CK/U1RTS/U1BCLK/IC2/ /CLC10/CTED4/CN                                     | 121/PB0                                          |

| 16       | /IC1/ / /CTED3/CN9/RA7                                                               | vz //KD9                                         |

| 17       | /OC1A/CTED1/INT2/CN8/RA6                                                             | VDDCORE/VCAP                                     |

| 18       | PGED2/SDI1/ /OC1C/CTED11/CN16/RB10                                                   |                                                  |

| 19       | PGEC2/SCK1/OC2A/CTED9/CN15/RB11                                                      | <u></u>                                          |

| 20       | /AN12/HLVDIN/ / / /CTED2/CN14/RB12                                                   | /AN12/HLVDIN/SS2/ / /CTED2/INT2/CN14/RB12        |

| 21       | / /AN11/SDO1/OCFB/OC3B/OC1D/CTPLS/CN13                                               | 3/RB13                                           |

| 22       | /CVREF/ / /AN10/ / /C1OUT                                                            | OCFA/CTED5/INT1/CN12/RB14                        |

| 23       | / /AN9/ /REFO/SS1/TCKIA/CTED6/CN                                                     | I11/RB15                                         |

| 24       | Vss                                                                                  |                                                  |

| 25       | Vdd                                                                                  |                                                  |

| 26       | MCLR/Vpp/RA5                                                                         |                                                  |

|          | CVREF+/VREF+/ /AN0/ /CN2/RA0                                                         | CVREF+/VREF+/ /AN0/ /CTED1/CN2/RA0               |

| 27       |                                                                                      |                                                  |

Legend:Values inindicate pin function differences between PIC24F(V)XXKM202 and PIC24F(V)XXKM102 devices.Note 1:Exposed pad on underside of device is connected to Vss.

### REGISTER 8-29: IPC15: INTERRUPT PRIORITY CONTROL REGISTER 15

| U-0           | U-0           | U-0                | U-0              | U-0                                | R/W-1      | R/W-0              | R/W-0  |

|---------------|---------------|--------------------|------------------|------------------------------------|------------|--------------------|--------|

|               | —             | _                  | —                |                                    | RTCIP2     | RTCIP1             | RTCIP0 |

| bit 15        | -             | -                  |                  |                                    |            |                    | bit 8  |

|               |               |                    |                  |                                    |            |                    |        |

| U-0           | U-0           | U-0                | U-0              | U-0                                | U-0        | U-0                | U-0    |

|               | —             | —                  | —                | —                                  | —          | —                  | —      |

| bit 7         |               |                    |                  |                                    |            | -                  | bit 0  |

|               |               |                    |                  |                                    |            |                    |        |

| Legend:       |               |                    |                  |                                    |            |                    |        |

| R = Readable  | e bit         | W = Writable bit   |                  | U = Unimplemented bit, read as '0' |            |                    |        |

| -n = Value at | POR           | '1' = Bit is set   |                  | '0' = Bit is cleared               |            | x = Bit is unknown |        |

|               |               |                    |                  |                                    |            |                    |        |

| bit 15-11     | Unimplemen    | ted: Read as '     | )'               |                                    |            |                    |        |

| bit 10-8      | RTCIP<2:0>:   | Real-Time Clo      | ck and Calend    | ar Interrupt Pric                  | ority bits |                    |        |

|               | 111 = Interru | pt is Priority 7 ( | highest priority | interrupt)                         |            |                    |        |

|               | •             |                    |                  |                                    |            |                    |        |

|               | •             |                    |                  |                                    |            |                    |        |

|               | •             |                    |                  |                                    |            |                    |        |

|               |               | pt is Priority 1   |                  |                                    |            |                    |        |

|               | 000 = Interru | pt source is dis   | abled            |                                    |            |                    |        |

| bit 7-0       | Unimplemen    | ted: Read as '     | )'               |                                    |            |                    |        |

|               |               |                    |                  |                                    |            |                    |        |

| U-0                   | R/W-1                                                                                                                                               | R/W-0                                | R/W-0   | U-0              | R/W-1             | R/W-0           | R/W-0   |  |  |  |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|---------|------------------|-------------------|-----------------|---------|--|--|--|

| _                     | DAC2IP2                                                                                                                                             | DAC2IP1                              | DAC2IP0 |                  | DAC1IP2           | DAC1IP1         | DAC1IP0 |  |  |  |

| bit 15                |                                                                                                                                                     |                                      |         |                  |                   |                 | bit 8   |  |  |  |

| U-0                   | R/W-1                                                                                                                                               | R/W-0                                | R/W-0   | U-0              | U-0               | U-0             | U-0     |  |  |  |

| _                     | CTMUIP2                                                                                                                                             | CTMUIP1                              | CTMUIP0 | _                |                   | _               | _       |  |  |  |

| bit 7                 |                                                                                                                                                     |                                      |         |                  |                   |                 | bit (   |  |  |  |

| Legend:               |                                                                                                                                                     |                                      |         |                  |                   |                 |         |  |  |  |

| Legena.<br>R = Readab | le hit                                                                                                                                              | W = Writable                         | hit     | II = Unimple     | mented bit, read  | las 'O'         |         |  |  |  |

| -n = Value a          |                                                                                                                                                     | '1' = Bit is set                     | on      | '0' = Bit is cle |                   | x = Bit is unkr |         |  |  |  |

|                       |                                                                                                                                                     |                                      |         |                  | aleu              |                 |         |  |  |  |

| bit 15                | Unimplemen                                                                                                                                          | ted: Read as '                       | )'      |                  |                   |                 |         |  |  |  |

| bit 14-12             | -                                                                                                                                                   |                                      |         | 2 Event Interr   | unt Priority hits |                 |         |  |  |  |

|                       | <b>DAC2IP&lt;2:0&gt;:</b> Digital-to-Analog Converter 2 Event Interrupt Priority bits<br>111 = Interrupt is Priority 7 (highest priority interrupt) |                                      |         |                  |                   |                 |         |  |  |  |

|                       | •                                                                                                                                                   |                                      |         |                  |                   |                 |         |  |  |  |

|                       | •                                                                                                                                                   |                                      |         |                  |                   |                 |         |  |  |  |

|                       | •                                                                                                                                                   |                                      |         |                  |                   |                 |         |  |  |  |

|                       | 001 = Interru<br>000 = Interru                                                                                                                      | pt is Priority 1<br>pt source is dis | abled   |                  |                   |                 |         |  |  |  |

| bit 11                | Unimplemen                                                                                                                                          | ted: Read as '                       | )'      |                  |                   |                 |         |  |  |  |

| bit 10-8              | DAC1IP<2:0>: Digital-to-Analog Converter 1 Event Interrupt Priority bits                                                                            |                                      |         |                  |                   |                 |         |  |  |  |

|                       | 111 = Interrupt is Priority 7 (highest priority interrupt)                                                                                          |                                      |         |                  |                   |                 |         |  |  |  |

|                       | •                                                                                                                                                   |                                      |         |                  |                   |                 |         |  |  |  |

|                       | •                                                                                                                                                   |                                      |         |                  |                   |                 |         |  |  |  |

|                       | •                                                                                                                                                   |                                      |         |                  |                   |                 |         |  |  |  |

|                       | 001 = Interrupt is Priority 1<br>000 = Interrupt source is disabled                                                                                 |                                      |         |                  |                   |                 |         |  |  |  |

| bit 7                 | -                                                                                                                                                   | ted: Read as '                       |         |                  |                   |                 |         |  |  |  |

| bit 6-4               | -                                                                                                                                                   |                                      |         | s                |                   |                 |         |  |  |  |

|                       | CTMUIP<2:0>: CTMU Interrupt Priority bits<br>111 = Interrupt is Priority 7 (highest priority interrupt)                                             |                                      |         |                  |                   |                 |         |  |  |  |

|                       | •                                                                                                                                                   |                                      |         |                  |                   |                 |         |  |  |  |

|                       | •                                                                                                                                                   |                                      |         |                  |                   |                 |         |  |  |  |

|                       | •                                                                                                                                                   |                                      |         |                  |                   |                 |         |  |  |  |

|                       | 001 = Interru                                                                                                                                       | pt is Priority 1<br>pt source is dis | ahlad   |                  |                   |                 |         |  |  |  |

| hit 2 0               |                                                                                                                                                     |                                      |         |                  |                   |                 |         |  |  |  |

| bit 3-0               | Unimplemented: Read as '0'                                                                                                                          |                                      |         |                  |                   |                 |         |  |  |  |

### REGISTER 8-32: IPC19: INTERRUPT PRIORITY CONTROL REGISTER 19

# **10.0 POWER-SAVING FEATURES**

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the *"PIC24F Family Reference Manual"*, "Power-Saving Features with VBAT" (DS30622).

This FRM describes some features which

are not implemented in this device. Sections related to the VBAT pin and Deep Sleep do not apply to the PIC24FV16KM204 family.

The PIC24FV16KM204 family of devices provides the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of circuits being clocked constitutes lower consumed power. All PIC24F devices manage power consumption in four different ways:

- Clock Frequency

- Instruction-Based Sleep and Idle modes

- · Software Controlled Doze mode

- Selective Peripheral Control in Software

Combinations of these methods can be used to selectively tailor an application's power consumption, while still maintaining critical application features, such as timing-sensitive communications.

## 10.1 Clock Frequency and Clock Switching

PIC24F devices allow for a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or high-precision oscillators by simply changing the NOSCx bits. The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in **Section 9.0** "Oscillator Configuration".

### 10.2 Instruction-Based Power-Saving Modes

PIC24F devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution; Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The 'C' syntax of the  $\ensuremath{\mathtt{PWRSAV}}$  instruction is shown in Example 10-1.

Note: SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to "wake-up".

### 10.2.1 SLEEP MODE

Sleep mode includes these features:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption will be reduced to a minimum provided that no I/O pin is sourcing current.

- The I/O pin directions and states are frozen.

- The Fail-Safe Clock Monitor does not operate during Sleep mode since the system clock source is disabled.

- The LPRC clock will continue to run in Sleep mode if the WDT or RTCC with LPRC as the clock source is enabled.

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode.

- Some device features or peripherals may continue to operate in Sleep mode. This includes items, such as the Input Change Notification on the I/O ports or peripherals that use an External Clock input. Any peripheral that requires the system clock source for its operation will be disabled in Sleep mode.

The device will wake-up from Sleep mode on any of these events:

- On any interrupt source that is individually enabled

- · On any form of device Reset

- · On a WDT time-out

On wake-up from Sleep, the processor will restart with the same clock source that was active when Sleep mode was entered.

### EXAMPLE 10-1: 'C' POWER-SAVING ENTRY

## 10.4 Voltage Regulator-Based Power-Saving Features

The PIC24FV16KM204 family series devices have a voltage regulator that has the ability to alter functionality to provide power savings. The on-chip regulator is made up of two basic modules: the Voltage Regulator (VREG) and the Retention Regulator (RETREG). With the combination of VREG and RETREG, the following power modes are available:

### 10.4.1 RUN MODE

In Run mode, the main VREG is providing a regulated voltage with enough current to supply a device running at full speed and the device is not in Sleep mode. The RETREG may or may not be running, but is unused.

### 10.4.2 SLEEP MODE

In Sleep mode, the device is in Sleep and the main VREG is providing a regulated voltage to the core. By default, in Sleep mode, the regulator enters a low-power standby state which consumes reduced quiescent current. The PMSLP bit (RCON<8>) controls the regulator state in Sleep mode. If the PMSLP bit is set, the program Flash memory will stay powered on during Sleep mode and the regulator will stay in its full-power mode.

## 10.4.3 RETENTION REGULATOR

The Retention Regulator, sometimes referred to as the low-voltage regulator, is designed to provide power to the core at a lower voltage than the standard voltage regulator, while consuming significantly lower quiescent current. Refer to **Section 27.0** "Electrical Characteristics" for the voltage output range of the RETREG. This regulator is only used in Sleep mode, and has limited output current to maintain the RAM and provide power for limited peripherals, such as the WDT, while the device is in Sleep. It is controlled by the RETCFG Configuration bit (FPOR<2>) and in firmware by the RETEN bit (RCON<12>). RETCFG must be programmed (= 0) and the RETEN bit must be set (= 1) for the Retention Regulator to be enabled.

### 10.4.4 RETENTION SLEEP MODE

In Retention Sleep mode, the device is in Sleep and all regulated voltage is provided solely by the RETREG, while the main VREG is disabled. Consequently, this mode provides the lowest Sleep power consumption, but has a trade-off of a longer wake-up time. The low-voltage Sleep wake-up time is longer than Sleep mode due to the extra time required to re-enable the VREG and raise the VDDCORE supply rail back to normal regulated levels.

**Note:** The PIC24F16KM204 family devices do not have any internal voltage regulation, and therefore, do not support Retention Sleep mode.

### TABLE 10-1: VOLTAGE REGULATION CONFIGURATION SETTINGS FOR PIC24FXXXXX FAMILY DEVICES

| RETCFG Bit<br>(FPOR<2>) | RETEN Bit<br>(RCON<12> | PMSLP Bit<br>(RCON<8>) | Power Mode<br>During Sleep | Description                                              |

|-------------------------|------------------------|------------------------|----------------------------|----------------------------------------------------------|

| 0                       | 0                      | 1                      | Sleep                      | VREG mode (normal) is unchanged during Sleep.            |

|                         |                        |                        |                            | RETREG is unused.                                        |

| 0                       | 0                      | 0                      | Sleep                      | VREG goes to Low-Power Standby mode during<br>Sleep.     |

|                         |                        |                        | (Standby)                  | RETREG is unused.                                        |

| 0                       | 1                      | 0                      | Retention                  | VREG is off during Sleep.                                |

|                         |                        |                        | Sleep                      | RETREG is enabled and provides Sleep voltage regulation. |

| 1                       | x                      | 1                      | Sleep                      | VREG mode (normal) is unchanged during Sleep.            |

|                         |                        |                        |                            | RETREG is disabled at all times.                         |

| 1                       | х                      | 0                      | Sleep                      | VREG goes to Low-Power Standby mode during<br>Sleep.     |

|                         |                        |                        | (Standby)                  | RETREG is disabled at all times.                         |

### 11.2.2 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation, and a read operation of the same port. Typically, this instruction would be a NOP.

## 11.3 Input Change Notification (ICN)

The Input Change Notification function of the I/O ports allows the PIC24FXXXXX family of devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature is capable of detecting input Change-of-States, even in Sleep mode, when the clocks are disabled. Depending on the device pin count, there are up to 37 external signals (CN0 through CN36) that may be selected (enabled) for generating an interrupt request on a Change-of-State.

There are six control registers associated with the CN module. The CNEN1 and CNEN3 registers contain the interrupt enable control bits for each of the CNx input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each CNx pin also has a weak pull-up/pull-down connected to it. The pull-ups act as a current source that is connected to the pin. The pull-downs act as a current sink to eliminate the need for external resistors when push button or keypad devices are connected.

On any pin, only the pull-up resistor or the pull-down resistor should be enabled, but not both of them. If the push button or the keypad is connected to VDD, enable the pull-down, or if they are connected to VSS, enable the pull-up resistors. The pull-ups are enabled separately using the CNPU1 and CNPU3 registers, which contain the control bits for each of the CNx pins.

Setting any of the control bits enables the weak pull-ups for the corresponding pins. The pull-downs are enabled separately using the CNPD1 and CNPD3 registers, which contain the control bits for each of the CNx pins. Setting any of the control bits enables the weak pull-downs for the corresponding pins.

When the internal pull-up is selected, the pin uses VDD as the pull-up source voltage. When the internal pull-down is selected, the pins are pulled down to Vss by an internal resistor. Make sure that there is no external pull-up source/pull-down sink when the internal pull-ups/pull-downs are enabled.

Note: Pull-ups and pull-downs on Change Notification (CN) pins should always be disabled whenever the port pin is configured as a digital output.

## EXAMPLE 11-1: PORT WRITE/READ EXAMPLE

| MOV 0xFF00, W0;<br>MOV W0, TRISB;                                                 | //Configure PORTB<15:8> as inputs and PORTB<7:0> as outputs                                                                                          |

|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| NOP ;                                                                             | //Delay 1 cycle                                                                                                                                      |

| BTSS PORTB, #13;                                                                  | //Next Instruction                                                                                                                                   |

| <pre>Equivalent `C' Code TRISB = 0xFF00; NOP(); if(PORTBbits.RB13 == 1) { }</pre> | <pre>//Configure PORTB&lt;15:8&gt; as inputs and PORTB&lt;7:0&gt; as outputs //Delay 1 cycle // execute following code if PORTB pin 13 is set.</pre> |

## REGISTER 13-7: CCPxSTATL: CCPx STATUS REGISTER

| U-0           | U-0                                              | U-0                                                | U-0          | U-0               | U-0              | U-0             | U-0           |  |  |  |

|---------------|--------------------------------------------------|----------------------------------------------------|--------------|-------------------|------------------|-----------------|---------------|--|--|--|

| _             | _                                                | —                                                  | _            | —                 | _                | —               |               |  |  |  |

| bit 15        |                                                  |                                                    |              |                   |                  |                 | bit 8         |  |  |  |

|               |                                                  |                                                    | 5/2.2        | 5/2.2             | 5/0.0            | 5/2.2           | 5/2.2         |  |  |  |

| R-0           | W1-0                                             | W1-0                                               | R/C-0        | R/C-0             | R/C-0            | R/C-0           | R/C-0         |  |  |  |

| CCPTRIG       | TRSET                                            | TRCLR                                              | ASEVT        | SCEVT             | ICDIS            | ICOV            | ICBNE         |  |  |  |

| bit 7         |                                                  |                                                    |              |                   |                  |                 | bit 0         |  |  |  |

| Legend:       |                                                  | C = Clearable                                      | bit          |                   |                  |                 |               |  |  |  |

| R = Readabl   | e bit                                            | W1 = Write '1'                                     | only         | U = Unimplem      | nented bit, read | as '0'          |               |  |  |  |

| -n = Value at | POR                                              | '1' = Bit is set                                   |              | '0' = Bit is clea | ared             | x = Bit is unkr | nown          |  |  |  |

|               |                                                  |                                                    |              |                   |                  |                 |               |  |  |  |

| bit 15-8      | Unimplemen                                       | ted: Read as '0                                    | ,            |                   |                  |                 |               |  |  |  |

| bit 7         | CCPTRIG: C                                       | CPx Trigger Sta                                    | tus bit      |                   |                  |                 |               |  |  |  |

|               |                                                  | s been triggered<br>s not been trigg               |              |                   |                  |                 |               |  |  |  |

| <b>h</b> :# 0 |                                                  |                                                    |              | eiu in Resel      |                  |                 |               |  |  |  |

| bit 6         |                                                  | x Trigger Set Re                                   |              | when TRIGEN       | = 1 (location a) | wave reade as   | : '∩')        |  |  |  |

| bit 5         |                                                  | Px Trigger Clear                                   |              |                   |                  | ways icaus as   | , , ,         |  |  |  |

| bit o         |                                                  | is location to ca                                  | •            | Trigger when T    | RIGEN = 1 (lo    | cation alwavs r | eads as '0'). |  |  |  |

| bit 4         |                                                  | x Auto-Shutdow                                     |              |                   | - (-             | ,               | ,             |  |  |  |

|               | 1 = A shutdo                                     | wn event is in p                                   | rogress; CCP | x outputs are in  | the shutdown     | state           |               |  |  |  |

|               | 0 = CCPx ou                                      | itputs operate n                                   | ormally      |                   |                  |                 |               |  |  |  |

| bit 3         | •                                                | le Edge Compa                                      |              |                   |                  |                 |               |  |  |  |

|               |                                                  | edge compare e<br>edge compare e                   |              |                   |                  |                 |               |  |  |  |

| bit 2         | •                                                | Capture x Disat                                    |              | occurred          |                  |                 |               |  |  |  |

| Dit Z         | •                                                | Input Capture :                                    |              | es not generate   | a capture ever   | nt              |               |  |  |  |

|               |                                                  | Input Capture                                      |              |                   |                  |                 |               |  |  |  |

| bit 1         | ICOV: Input Capture x Buffer Overflow Status bit |                                                    |              |                   |                  |                 |               |  |  |  |

|               |                                                  | 1 = The Input Capture x FIFO buffer has overflowed |              |                   |                  |                 |               |  |  |  |

|               |                                                  | t Capture x FIF                                    |              | ot overflowed     |                  |                 |               |  |  |  |

| bit 0         | •                                                | Capture x Buffe                                    |              | -  -   -          |                  |                 |               |  |  |  |

|               |                                                  | apture x buffer h<br>apture x buffer i             |              | adie              |                  |                 |               |  |  |  |

|               |                                                  |                                                    | c sinply     |                   |                  |                 |               |  |  |  |

| U-0           | U-0                        | U-0                               | U-0              | U-0                | U-0            | U-0             | U-0              |

|---------------|----------------------------|-----------------------------------|------------------|--------------------|----------------|-----------------|------------------|

|               | —                          | —                                 |                  | —                  |                | _               |                  |

| bit 15        |                            |                                   |                  |                    |                |                 | bit 8            |

|               |                            |                                   |                  |                    |                |                 |                  |

| R/W-0         | R/W-0                      | R-0                               | R-0              | R-0                | R-0            | R-0             | R-0              |

| SMP           | CKE <sup>(1)</sup>         | D/Ā                               | Р                | S                  | R/W            | UA              | BF               |

| bit 7         |                            |                                   |                  |                    |                |                 | bit (            |

| Legend:       |                            |                                   |                  |                    |                |                 |                  |

| R = Readable  | e bit                      | W = Writable I                    | oit              | U = Unimplem       | ented bit. rea | d as '0'        |                  |

| -n = Value at |                            | '1' = Bit is set                  |                  | '0' = Bit is clea  |                | x = Bit is unkr | nown             |

|               |                            |                                   |                  |                    |                |                 |                  |

| bit 15-8      | Unimplemen                 | ted: Read as '0                   | )'               |                    |                |                 |                  |

| bit 7         | SMP: Sample                | e bit                             |                  |                    |                |                 |                  |

|               | SPI Master m               |                                   |                  |                    |                |                 |                  |

|               |                            | is sampled at                     |                  |                    |                |                 |                  |

|               | •                          | •                                 | the middle of o  | data output time   |                |                 |                  |

|               | SMP must be                | de:<br>cleared when \$            | SPI is used in   | Slave mode         |                |                 |                  |

| bit 6         |                            | ck Select bit <sup>(1)</sup>      |                  |                    |                |                 |                  |

|               | 1 = Transmit o             | occurs on trans                   | ition from acti  | ve to Idle clock s | state          |                 |                  |

|               | 0 = Transmit               | occurs on trans                   | ition from Idle  | to active clock s  | state          |                 |                  |

| bit 5         | D/A: Data/Ad               |                                   |                  |                    |                |                 |                  |

|               | Used in I <sup>2</sup> C™  | mode only.                        |                  |                    |                |                 |                  |

| bit 4         | P: Stop bit                |                                   |                  |                    |                |                 |                  |

|               |                            | node only. This                   | bit is cleared v | when the MSSP:     | x module is di | sabled; SSPEN   | l bit is cleared |

| bit 3         | S: Start bit               |                                   |                  |                    |                |                 |                  |

|               | Used in I <sup>2</sup> C m | •                                 |                  |                    |                |                 |                  |

| bit 2         |                            | rite Information                  | bit              |                    |                |                 |                  |

|               | Used in I <sup>2</sup> C m |                                   |                  |                    |                |                 |                  |

| bit 1         | UA: Update Address bit     |                                   |                  |                    |                |                 |                  |

|               | Used in I <sup>2</sup> C m | ,                                 |                  |                    |                |                 |                  |

| bit 0         | BF: Buffer Fu              |                                   |                  |                    |                |                 |                  |

|               |                            | s complete, SS<br>s not complete, |                  | emntv              |                |                 |                  |

|               |                            | -                                 |                  |                    |                |                 |                  |

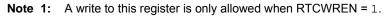

|               | plarity of clock s         | tata ia aat by th                 |                  | DUCONIA (A)        |                |                 |                  |

### REGISTER 14-1: SSPxSTAT: MSSPx STATUS REGISTER (SPI MODE)

# REGISTER 14-3: SSPxCON1: MSSPx CONTROL REGISTER 1 (SPI MODE)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   |     | —   | —   | —   |     | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0 | R/W-0                | R/W-0                | R/W-0 | R/W-0                | R/W-0                | R/W-0                | R/W-0                |

|-------|----------------------|----------------------|-------|----------------------|----------------------|----------------------|----------------------|

| WCOL  | SSPOV <sup>(1)</sup> | SSPEN <sup>(2)</sup> | CKP   | SSPM3 <sup>(3)</sup> | SSPM2 <sup>(3)</sup> | SSPM1 <sup>(3)</sup> | SSPM0 <sup>(3)</sup> |

| bit 7 |                      |                      |       |                      |                      |                      | bit 0                |

| Legend:                                                                                                         |                   |                                                                                                                                                                                                                   |                                           |                                   |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-----------------------------------|--|--|--|--|

| R = Read                                                                                                        | able bit          | W = Writable bit                                                                                                                                                                                                  | U = Unimplemented bit                     | , read as '0'                     |  |  |  |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is c                                                               |                   |                                                                                                                                                                                                                   |                                           | x = Bit is unknown                |  |  |  |  |

|                                                                                                                 |                   |                                                                                                                                                                                                                   |                                           |                                   |  |  |  |  |

| bit 15-8                                                                                                        | Unimple           | mented: Read as '0'                                                                                                                                                                                               |                                           |                                   |  |  |  |  |

| bit 7                                                                                                           | WCOL: \           | WCOL: Write Collision Detect bit                                                                                                                                                                                  |                                           |                                   |  |  |  |  |

|                                                                                                                 |                   | •                                                                                                                                                                                                                 | while it is still transmitting the        | previous word (must be cleared in |  |  |  |  |

|                                                                                                                 | softw<br>0 = No c | ,                                                                                                                                                                                                                 |                                           |                                   |  |  |  |  |

| bit 6                                                                                                           |                   |                                                                                                                                                                                                                   | Port Receive Overflow Indicate            | or bit(1)                         |  |  |  |  |

| bit 0                                                                                                           |                   |                                                                                                                                                                                                                   |                                           |                                   |  |  |  |  |

|                                                                                                                 |                   | <u>SPI Slave mode:</u><br>1 = A new byte is received while the SSPxBUF register is still holding the previous data. In case of over-                                                                              |                                           |                                   |  |  |  |  |

|                                                                                                                 |                   |                                                                                                                                                                                                                   |                                           | ave mode. The user must read the  |  |  |  |  |

| SSPxBUF, even if only transmitting data, to avoid setting overflow (must be cleared in softw<br>0 = No overflow |                   |                                                                                                                                                                                                                   |                                           |                                   |  |  |  |  |

| bit 5                                                                                                           |                   | Master Synchronous Serial F                                                                                                                                                                                       | Port Enable bit(2)                        |                                   |  |  |  |  |

| DIL 5                                                                                                           |                   | •                                                                                                                                                                                                                 | ures SCKx, SDOx, SDIx and                 | SSx as serial nort nins           |  |  |  |  |

|                                                                                                                 |                   |                                                                                                                                                                                                                   | jures these pins as I/O port pi           | · ·                               |  |  |  |  |

| bit 4                                                                                                           | CKP: Clo          | ock Polarity Select bit                                                                                                                                                                                           |                                           |                                   |  |  |  |  |

|                                                                                                                 | 1 = Idle s        | state for clock is a high level                                                                                                                                                                                   |                                           |                                   |  |  |  |  |

|                                                                                                                 |                   | state for clock is a low level                                                                                                                                                                                    |                                           |                                   |  |  |  |  |

| bit 3-0                                                                                                         | SSPM<3            | :0>: Master Synchronous Se                                                                                                                                                                                        | rial Port Mode Select bits <sup>(3)</sup> |                                   |  |  |  |  |

|                                                                                                                 |                   | SPI Master mode, Clock = Fo                                                                                                                                                                                       |                                           |                                   |  |  |  |  |

|                                                                                                                 |                   | 0101 = SPI Slave mode, Clock = SCKx pin; $\overline{SSx}$ pin control is disabled, $\overline{SSx}$ can be used as an I/O pin<br>0100 = SPI Slave mode, Clock = SCKx pin; $\overline{SSx}$ pin control is enabled |                                           |                                   |  |  |  |  |

|                                                                                                                 |                   | SPI Master mode, Clock = TM                                                                                                                                                                                       |                                           |                                   |  |  |  |  |

|                                                                                                                 |                   | SPI Master mode, Clock = Fo                                                                                                                                                                                       | •                                         |                                   |  |  |  |  |

|                                                                                                                 |                   | PI Master mode, Clock = Fo                                                                                                                                                                                        |                                           |                                   |  |  |  |  |

|                                                                                                                 | 0000 = 5          | SPI Master mode, Clock = Fo                                                                                                                                                                                       | SC/2                                      |                                   |  |  |  |  |

| Note 1:                                                                                                         | In Master mo      | de, the overflow bit is not set                                                                                                                                                                                   | t since each new reception (a             | nd transmission) is initiated by  |  |  |  |  |

| writing to the SSPxBUF register.                                                                                |                   |                                                                                                                                                                                                                   |                                           |                                   |  |  |  |  |

- 2: When enabled, these pins must be properly configured as inputs or outputs.

- **3:** Bit combinations not specifically listed here are either reserved or implemented in  $I^2C^{TM}$  mode only.

# REGISTER 14-5: SSPxCON2: MSSPx CONTROL REGISTER 2 (I<sup>2</sup>C<sup>™</sup> MODE)

| U-0        | U-0                                        | U-0                                  | U-0                  | U-0                     | U-0                | U-0                 | U-0                |

|------------|--------------------------------------------|--------------------------------------|----------------------|-------------------------|--------------------|---------------------|--------------------|

| _          |                                            | _                                    |                      |                         | _                  | —                   |                    |

| bit 15     |                                            |                                      |                      |                         |                    |                     | bit 8              |

|            |                                            |                                      |                      |                         |                    |                     |                    |

| R/W-0      | R/W-0                                      | R/W-0                                | R/W-0                | R/W-0                   | R/W-0              | R/W-0               | R/W-0              |

| GCEN       | ACKSTAT                                    | ACKDT <sup>(1)</sup>                 | ACKEN <sup>(2)</sup> | RCEN <sup>(2)</sup>     | PEN <sup>(2)</sup> | RSEN <sup>(2)</sup> | SEN <sup>(2)</sup> |

| bit 7      |                                            |                                      |                      |                         |                    |                     | bit (              |

| Legend:    |                                            |                                      |                      |                         |                    |                     |                    |

| R = Reada  | able bit                                   | W = Writable                         | bit                  | U = Unimplem            | nented bit, read   | d as '0'            |                    |

| -n = Value |                                            | '1' = Bit is set                     |                      | '0' = Bit is clea       |                    | x = Bit is unkn     | lown               |

|            |                                            | 1 Bit io oot                         |                      | o Bit io olot           |                    |                     |                    |

| bit 15-8   | Unimplemen                                 | ted: Read as '                       | 0'                   |                         |                    |                     |                    |

| bit 7      | GCEN: Gene                                 | eral Call Enable                     | bit (Slave mod       | e only)                 |                    |                     |                    |

|            |                                            | interrupt when a call address is o   | 0                    | ddress (0000h)          | is received in     | the SSPxSR          |                    |

| bit 6      |                                            | cknowledge Sta                       |                      | Transmit mode           | ≏ onlv)            |                     |                    |

|            |                                            | edge was not re                      |                      |                         | c only)            |                     |                    |

|            |                                            | edge was receiv                      |                      |                         |                    |                     |                    |

| bit 5      | ACKDT: Ack                                 | nowledge Data                        | bit (Master Red      | ceive mode onl          | y) <sup>(1)</sup>  |                     |                    |

|            | 1 = No Ackno                               | owledge                              |                      |                         |                    |                     |                    |

|            | 0 = Acknowle                               | •                                    |                      |                         |                    |                     |                    |

| bit 4      |                                            | nowledge Sequ                        |                      |                         |                    |                     |                    |

|            |                                            |                                      |                      | SDAx and SC             | CLx pins and       | transmits ACI       | KDT data bit       |

|            |                                            | ically cleared by<br>edge sequence   |                      |                         |                    |                     |                    |

| bit 3      |                                            | ive Enable bit (                     |                      | mode only)(2)           |                    |                     |                    |

| bit 0      |                                            | Receive mode f                       | -                    | , mode only)            |                    |                     |                    |

|            | 0 = Receive i                              |                                      |                      |                         |                    |                     |                    |

| bit 2      | PEN: Stop Co                               | ondition Enable                      | bit (Master mo       | de only) <sup>(2)</sup> |                    |                     |                    |

|            |                                            | Stop condition c                     | n SDAx and SO        | CLx pins; auton         | natically cleare   | ed by hardware      |                    |

|            | 0 = Stop cond                              |                                      |                      |                         | (0)                |                     |                    |

| bit 1      | -                                          | ated Start Cond                      |                      | -                       |                    |                     |                    |

|            |                                            | Repeated Start<br>d Start conditio   |                      | DAx and SCLx            | pins; automati     | ically cleared by   | / hardware         |

| bit 0      | -                                          | ondition Enable                      |                      |                         |                    |                     |                    |

|            | Master Mode                                |                                      | DIC                  |                         |                    |                     |                    |

|            |                                            | <u></u><br>Start condition c         | on SDAx and S        | CLx pins: autor         | natically cleare   | ed by hardware      |                    |

|            | 0 = Start con                              |                                      |                      |                         |                    |                     |                    |

|            | Slave Mode:                                |                                      |                      |                         |                    |                     |                    |

|            |                                            | etching is enabl<br>etching is disab |                      | ve transmit and         | slave receive      | (stretch is enab    | oled)              |

| Note 1:    | The value that wi                          | ill be transmitte                    | d when the use       | r initiates an Ao       | cknowledge se      | equence at the e    | end of a           |

|            |                                            |                                      |                      |                         |                    |                     |                    |

| 2:         | receive.<br>If the I <sup>2</sup> C module |                                      | 1.10                 |                         |                    |                     |                    |

### REGISTER 14-10: PADCFG1: PAD CONFIGURATION CONTROL REGISTER

| U-0                                | U-0         | U-0                                 | U-0                          | R/W-0                              | R/W-0                  | R/W-0           | R/W-0   |  |  |

|------------------------------------|-------------|-------------------------------------|------------------------------|------------------------------------|------------------------|-----------------|---------|--|--|

|                                    | —           |                                     | _                            | SDO2DIS <sup>(1)</sup>             | SCK2DIS <sup>(1)</sup> | SDO1DIS         | SCK1DIS |  |  |

| bit 15                             |             |                                     |                              |                                    |                        |                 | bit     |  |  |

|                                    |             |                                     |                              |                                    |                        |                 |         |  |  |

| U-0                                | U-0         | U-0                                 | U-0                          | U-0                                | U-0                    | U-0             | U-0     |  |  |

|                                    | —           |                                     |                              |                                    | —                      | _               | —       |  |  |

| bit 7                              |             |                                     |                              |                                    |                        |                 | bit (   |  |  |

|                                    |             |                                     |                              |                                    |                        |                 |         |  |  |

| Legend:                            |             |                                     |                              |                                    |                        |                 |         |  |  |

| R = Readable bit W = Writable bit  |             |                                     |                              | U = Unimplemented bit, read as '0' |                        |                 |         |  |  |

| -n = Value at POR '1' = Bit is set |             |                                     |                              | '0' = Bit is clea                  | ared                   | x = Bit is unkn | own     |  |  |

|                                    |             |                                     |                              |                                    |                        |                 |         |  |  |

| bit 15-12                          | Unimplemen  | ted: Read as '0                     | ,                            |                                    |                        |                 |         |  |  |

| bit 11                             | SDO2DIS: MS | SSP2 SDO2 Pir                       | n Disable bit <sup>(1)</sup> | )                                  |                        |                 |         |  |  |

|                                    |             | output data (SD                     | ,                            | •                                  |                        |                 |         |  |  |

|                                    |             | output data (SD                     |                              |                                    | e pin                  |                 |         |  |  |

| bit 10                             |             | SSP2 SCK2 Pir                       |                              |                                    |                        |                 |         |  |  |

|                                    |             | clock (SCK2) of<br>clock (SCK2) of  |                              |                                    | נ                      |                 |         |  |  |

| bit 9                              |             | SSP1 SDO1 Pir                       |                              |                                    |                        |                 |         |  |  |

|                                    |             | output data (SD                     |                              | 1 to the pin is d                  | isabled                |                 |         |  |  |

|                                    |             | output data (SD                     | ,                            |                                    |                        |                 |         |  |  |

| bit 8                              | SCK1DIS: MS | SCK1DIS: MSSP1 SCK1 Pin Disable bit |                              |                                    |                        |                 |         |  |  |

|                                    | 1 = The SPI | clock (SCK1) of                     | MSSP1 to the                 | e pin is disabled                  | t                      |                 |         |  |  |

|                                    | 0 = The SPI | clock (SCK1) of                     | MSSP1 is ou                  | tput to the pin                    |                        |                 |         |  |  |

| bit 7-0                            | Unimplemen  | ted: Read as '0                     | ,                            |                                    |                        |                 |         |  |  |

|                                    |             |                                     |                              |                                    |                        |                 |         |  |  |

**Note 1:** These bits are implemented only on PIC24FXXKM20X devices.

| R/W-0         | U-0                          | R/W-0                                                               | R/W-0                         | R/W-0                                      | U-0                                        | R/W-0 <sup>(2)</sup> | R/W-0 <sup>(2)</sup> |

|---------------|------------------------------|---------------------------------------------------------------------|-------------------------------|--------------------------------------------|--------------------------------------------|----------------------|----------------------|

| UARTEN        | —                            | USIDL                                                               | IREN <sup>(1)</sup>           | RTSMD                                      | _                                          | UEN1                 | UEN0                 |

| bit 15        |                              |                                                                     |                               |                                            |                                            |                      | bit 8                |

| R/C-0, HC     | R/W-0                        | R/W-0, HC                                                           | R/W-0                         | R/W-0                                      | R/W-0                                      | R/W-0                | R/W-0                |