#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-><F

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 23                                                                            |

| Program Memory Size        | 16KB (5.5K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5V                                                                       |

| Data Converters            | A/D 19x10b/12b; D/A 2x8b                                                      |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

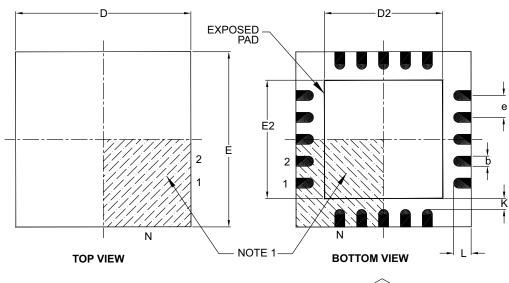

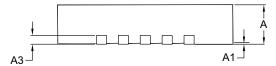

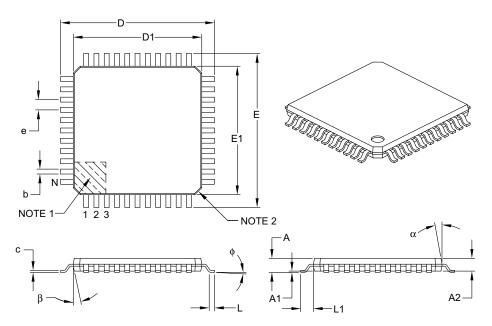

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                |

| Supplier Device Package    | 28-SSOP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fv16km202-i-ss |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.1.4 EASY MIGRATION

The PIC24FV16KM204 family devices have two variants. The KM20X variant provides the full feature set of the device, while the KM10X offers a reduced peripheral set, allowing for the balance of features and cost (refer to Table 1-1). Both variants allow for a smooth migration path as applications grow and evolve.

The consistent pinout scheme used throughout the entire family also helps in migrating to the next larger device. This is true when moving between devices with the same pin count, different die variants, or even moving from 20-pin or 28-pin devices to 44-pin/48-pin devices.

The PIC24F family is pin compatible with devices in the dsPIC33 family, and shares some compatibility with the pinout schema for PIC18 and dsPIC30. This extends the ability of applications to grow from the relatively simple to the powerful and complex, yet still selecting a Microchip device.

# 1.2 Other Special Features

- Communications: The PIC24FV16KM204 family incorporates a range of serial communication peripherals to handle a range of application requirements. There is an MSSP module which implements both SPI and I<sup>2</sup>C™ protocols, and supports both Master and Slave modes of operation for each. Devices also include one of two UARTs with built-in IrDA<sup>®</sup> encoders/decoders.

- Analog Features: Select members of the PIC24FV16KM204 family include two 8-bit Digital-to-Analog Converters which offer support in Idle mode, and left and right justified input data, as well as up to two operational amplifiers with selectable power and speed modes.

- Real-Time Clock/Calendar (RTCC): This module implements a full-featured clock and calendar with alarm functions in hardware, freeing up timer resources and program memory space for use of the core application.

- 12-Bit A/D Converter: This module incorporates programmable acquisition time, allowing for a channel to be selected and a conversion to be initiated without waiting for a sampling period, and faster sampling speed. The 16-deep result buffer can be used either in Sleep, to reduce power, or in Active mode to improve throughput.

- Charge Time Measurement Unit (CTMU) Interface: The PIC24FV16KM204 family includes the new CTMU interface module, which can be used for capacitive touch sensing, proximity sensing, and also for precision time measurement and pulse generation. The CTMU can also be connected to the operational amplifiers to provide active guarding, which provides increased robustness in the presence of noise in capacitive touch applications.

# 1.3 Details on Individual Family Members

Devices in the PIC24FV16KM204 family are available in 20-pin, 28-pin, 44-pin and 48-pin packages. The general block diagram for all devices is shown in Figure 1-1.

Members of the PIC24FV16KM204 family are available as both standard and high-voltage devices. High-voltage devices, designated with an "FV" in the part number (such as PIC24FV16KM204), accommodate an operating VDD range of 2.0V to 5.5V and have an on-board voltage regulator that powers the core. Peripherals operate at VDD.

Standard devices, designated by "F" (such as PIC24F16KM204), function over a lower VDD range of 1.8V to 3.6V. These parts do not have an internal regulator, and both the core and peripherals operate directly from VDD.

The PIC24FV16KM204 family may be thought of as two different device groups, both offering slightly different sets of features. These differ from each other in multiple ways:

- · The size of the Flash program memory

- The number of external analog channels available

- The number of Digital-to-Analog Converters

- · The number of operational amplifiers

- The number of analog comparators

- The presence of a Real-Time Clock and Calendar (RTCC)

- The number and type of CCP modules (i.e., MCCP vs. SCCP)

- The number of serial communication modules (both MSSPs and UARTs)

- The number of Configurable Logic Cell (CLC) modules

The general differences between the different sub-families are shown in Table 1-1 and Table 1-2.

A list of the pin features available on the PIC24FV16KM204 family devices, sorted by function, is provided in Table 1-5.

# TABLE 4-13: MSSP1 (I<sup>2</sup>C<sup>™</sup>/SPI) REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6   | Bit 5    | Bit 4                       | Bit 3       | Bit 2   | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|--------|--------|--------|--------|--------|--------|-------|-------|--------|---------|----------|-----------------------------|-------------|---------|-------|-------|---------------|

| SSP1BUF   | 200h  | —      | _      | _      | —      | —      | —      | _     | —     |        |         | MSSP1 Re | eceive Buffer               | /Transmit R | egister |       |       | 00xx          |

| SSP1CON1  | 202h  | _      | _      | _      | _      | _      | _      | _     | _     | WCOL   | SSPOV   | SSPEN    | CKP                         | SSPM3       | SSPM2   | SSPM1 | SSPM0 | 0000          |

| SSP1CON2  | 204h  | _      | _      | _      | _      | _      | _      | _     | _     | GCEN   | ACKSTAT | ACKDT    | ACKEN                       | RCEN        | PEN     | RSEN  | SEN   | 0000          |

| SSP1CON3  | 206h  | _      | _      | _      | _      | _      | _      | _     | _     | ACKTIM | PCIE    | SCIE     | BOEN                        | SDAHT       | SBCDE   | AHEN  | DHEN  | 0000          |

| SSP1STAT  | 208h  | _      | _      | _      | _      | _      | _      | —     | _     | SMP    | CKE     | D/A      | Р                           | S           | R/W     | UA    | BF    | 0000          |

| SSP1ADD   | 20Ah  | —      | _      | _      | —      | _      | —      |       |       |        |         |          | ress Registe<br>e Reload Re |             |         | de    |       | 0000          |

| SSP1MSK   | 20Ch  | _      | _      | _      | _      | _      | _      |       | _     | MSK7   | MSK6    | MSK5     | MSK4                        | MSK3        | MSK2    | MSK1  | MSK0  | OOFF          |

Legend: x = unknown, u = unchanged, - = unimplemented, q = value depends on condition, r = reserved.

# TABLE 4-14: MSSP2 (I<sup>2</sup>C<sup>™</sup>/SPI) REGISTER MAP

| File Name               | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6      | Bit 5                     | Bit 4                       | Bit 3                                                  | Bit 2                  | Bit 1 | Bit 0 | All<br>Resets |

|-------------------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|--------|------------|---------------------------|-----------------------------|--------------------------------------------------------|------------------------|-------|-------|---------------|

| SSP2BUF <sup>(1)</sup>  | 210h  | —      | _      | —      | —      |        | _      |       | _     |        |            | MSSP2 Re                  | ceive Buffe                 | r/Transmit F                                           | Register               |       |       | 00xx          |

| SSP2CON1 <sup>(1)</sup> | 212h  | _      | _      | _      | _      | _      | _      | _     | _     | WCOL   | SSPOV      | SSPEN                     | CKP                         | SSPM3                                                  | SSPM2                  | SSPM1 | SSPM0 | 0000          |

| SSP2CON2 <sup>(1)</sup> | 214h  | _      | _      | _      | _      | _      | _      | _     | _     | GCEN   | ACKSTAT    | ACKDT                     | ACKEN                       | RCEN                                                   | PEN                    | RSEN  | SEN   | 0000          |

| SSP2CON3 <sup>(1)</sup> | 216h  | _      | _      | _      | _      | _      | _      | _     | _     | ACKTIM | PCIE       | SCIE                      | BOEN                        | SDAHT                                                  | SBCDE                  | AHEN  | DHEN  | 0000          |

| SSP2STAT <sup>(1)</sup> | 218h  | _      | _      | _      | _      | _      | _      | _     | _     | SMP    | CKE        | D/A                       | Р                           | S                                                      | R/W                    | UA    | BF    | 0000          |

| SSP2ADD <sup>(1)</sup>  | 21Ah  | —      | _      | —      | —      | _      | —      | —     | _     |        | N<br>MSSP: | /ISSP2 Add<br>2 Baud Rate | ress Registe<br>e Reload Re | er in I <sup>2</sup> C Sla<br>gister in I <sup>2</sup> | ave Mode<br>C Master M | lode  |       | 0000          |

| SSP2MSK <sup>(1)</sup>  | 21Ch  | —      | _      | _      | _      |        | _      | _     | _     | MSK7   | MSK6       | MSK5                      | MSK4                        | MSK3                                                   | MSK2                   | MSK1  | MSK0  | 00FF          |

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

Note 1: These registers are available only on PIC24F(V)16KM2XX devices.

### TABLE 4-17: OP AMP 1 REGISTER MAP

| File Name              | Addr. | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|------------------------|-------|--------|--------|---------|--------|--------|--------|-------|-------|--------|-------|---------|---------|---------|---------|---------|---------|---------------|

|                        |       |        |        |         |        |        |        |       |       |        |       |         |         |         |         |         |         |               |

| AMP1CON <sup>(1)</sup> | 24Ah  | AMPEN  | _      | AMPSIDL | AMPSLP | _      | _      | _     | —     | SPDSEL | _     | NINSEL2 | NINSEL1 | NINSEL0 | PINSEL2 | PINSEL1 | PINSEL0 | 0000          |

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

Note 1: This registers are available only on PIC24F(V)16KM2XX devices.

#### TABLE 4-18: OP AMP 2 REGISTER MAP

| File Name              | Addr. | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|------------------------|-------|--------|--------|---------|--------|--------|--------|-------|-------|--------|-------|---------|---------|---------|---------|---------|---------|---------------|

| AMP2CON <sup>(1)</sup> | 24Ch  | AMPEN  | _      | AMPSIDL | AMPSLP | _      | _      | _     | _     | SPDSEL | —     | NINSEL2 | NINSEL1 | NINSEL0 | PINSEL2 | PINSEL1 | PINSEL0 | 0000          |

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

Note 1: This registers are available only on PIC24F(V)16KM2XX devices.

#### TABLE 4-19: DAC1 REGISTER MAP

| File Name            | Addr.   | Bit 15                  | Bit 14                  | Bit 13      | Bit 12      | Bit 11      | Bit 10      | Bit 9      | Bit 8      | Bit 7                  | Bit 6      | Bit 5      | Bit 4                  | Bit 3      | Bit 2      | Bit 1      | Bit 0      | All<br>Resets |

|----------------------|---------|-------------------------|-------------------------|-------------|-------------|-------------|-------------|------------|------------|------------------------|------------|------------|------------------------|------------|------------|------------|------------|---------------|

| DAC1CON              | 1) 274h | DACEN                   | -                       | DACSIDL     | DACSLP      | DACFM       | -           | SRDIS      | DACTRIG    | DACOE                  | DACTSEL4   | DACTSEL3   | DACTSEL2               | DACTSEL1   | DACTSEL0   | DACREF1    | DACREF0    | 0000          |

| DAC1DAT <sup>(</sup> | ) 276h  | DACDAT15 <sup>(2)</sup> | DACDAT14 <sup>(2)</sup> | DACDAT13(2) | DACDAT12(2) | DACDAT11(2) | DACDAT10(2) | DACDAT9(2) | DACDAT8(2) | DACDAT7 <sup>(2)</sup> | DACDAT6(2) | DACDAT5(2) | DACDAT4 <sup>(2)</sup> | DACDAT3(2) | DACDAT2(2) | DACDAT1(2) | DACDAT0(2) | 0000          |

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

Note 1: These registers are available only on PIC24F(V)16KM1XX devices.

2: The 8-bit result format depends on the value of the DACFM control bit.

### TABLE 4-20: DAC2 REGISTER MAP

| File Name              | Addr. | Bit 15      | Bit 14      | Bit 13      | Bit 12      | Bit 11      | Bit 10      | Bit 9      | Bit 8      | Bit 7      | Bit 6      | Bit 5      | Bit 4      | Bit 3      | Bit 2      | Bit 1      | Bit 0      | All<br>Resets |

|------------------------|-------|-------------|-------------|-------------|-------------|-------------|-------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|---------------|

| DAC2CON <sup>(1)</sup> | 278h  | DACEN       | -           | DACSIDL     | DACSLP      | DACFM       | -           | SRDIS      | DACTRIG    | DACOE      | DACTSEL4   | DACTSEL3   | DACTSEL2   | DACTSEL1   | DACTSEL0   | DACREF1    | DACREF0    | 0000          |

| DAC2DAT <sup>(1)</sup> | 27Ah  | DACDAT15(2) | DACDAT14(2) | DACDAT13(2) | DACDAT12(2) | DACDAT11(2) | DACDAT10(2) | DACDAT9(2) | DACDAT8(2) | DACDAT7(2) | DACDAT6(2) | DACDAT5(2) | DACDAT4(2) | DACDAT3(2) | DACDAT2(2) | DACDAT1(2) | DACDATO(2) | 0000          |

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

Note 1: These registers are available only on PIC24F(V)16KM2XX devices.

2: The 8-bit result format depends on the value of the DACFM control bit.

# TABLE 4-25: A/D REGISTER MAP

| File Name | -25:<br>Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11   | Bit 10       | Bit 9      | Bit 8                 | Bit 7                 | Bit 6                 | Bit 5               | Bit 4                  | Bit 3                  | Bit 2   | Bit 1   | Bit 0   | All    |

|-----------|---------------|---------|---------|---------|---------|----------|--------------|------------|-----------------------|-----------------------|-----------------------|---------------------|------------------------|------------------------|---------|---------|---------|--------|

|           |               | 2.1.10  |         | 2       | 2.4.12  | 2        | 20.10        | 2          | 2                     |                       | 2                     | 2.1.0               |                        | 2                      |         |         | 2.10    | Resets |

| ADC1BUF0  | 300h          |         |         |         |         | A/D Da   | ata Buffer 0 | /Threshold | for Channel 0/        | Threshold for         | Channel 0 & 1         | 2 in Window         | Compare                |                        |         |         |         | xxxx   |

| ADC1BUF1  | 302h          |         |         |         |         | A/D Da   | ata Buffer 1 | /Threshold | for Channel 1/        | Threshold for         | Channel 1 & 1         | 3 in Window         | Compare                |                        |         |         |         | xxxx   |

| ADC1BUF2  | 304h          |         |         |         |         | A/D Da   | ata Buffer 2 | /Threshold | for Channel 2/        | Threshold for         | Channel 2 & 1         | 4 in Window         | Compare                |                        |         |         |         | XXXX   |

| ADC1BUF3  | 306h          |         |         |         |         | A/D Da   | ata Buffer 3 | /Threshold | for Channel 3/        | Threshold for         | Channel 3 & 1         | 5 in Window         | Compare                |                        |         |         |         | XXXX   |

| ADC1BUF4  | 308h          |         |         |         |         | A/D Da   | ata Buffer 4 | /Threshold | for Channel 4/        | Threshold for         | Channel 4 & 1         | 6 in Window         | Compare                |                        |         |         |         | xxxx   |

| ADC1BUF5  | 30Ah          |         |         |         |         | A/D Da   | ata Buffer 5 | /Threshold | for Channel 5/        | Threshold for         | Channel 5 & 1         | 7 in Window         | Compare                |                        |         |         |         | xxxx   |

| ADC1BUF6  | 30Ch          |         |         |         |         | A/D Da   | ata Buffer 6 | /Threshold | for Channel 6/        | Threshold for         | Channel 6 & 1         | 8 in Window         | Compare                |                        |         |         |         | xxxx   |

| ADC1BUF7  | 30Eh          |         |         |         |         | A/D Da   | ata Buffer 7 | /Threshold | for Channel 7/        | Threshold for         | Channel 7 & 1         | 9 in Window         | Compare                |                        |         |         |         | xxxx   |

| ADC1BUF8  | 310h          |         |         |         |         | A/D Da   | ata Buffer 8 | /Threshold | for Channel 8/        | Threshold for         | Channel 8 & 2         | 0 in Window         | Compare                |                        |         |         |         | xxxx   |

| ADC1BUF9  | 312h          |         |         |         |         | A/D Da   | ata Buffer 9 | /Threshold | for Channel 9/        | Threshold for         | Channel 9 & 2         | 1 in Window         | Compare                |                        |         |         |         | xxxx   |

| ADC1BUF10 | 314h          |         |         |         |         | A/D Data | a Buffer 10/ | Threshold  | for Channel 10        | /Threshold for        | r Channel 10 &        | 22 in Window        | w Compare              |                        |         |         |         | xxxx   |

| ADC1BUF11 | 316h          |         |         |         |         | A/D Dat  | a Buffer 11/ | Threshold  | for Channel 11        | /Threshold for        | Channel 11 &          | 23 in Window        | v Compare              |                        |         |         |         | xxxx   |

| ADC1BUF12 | 318h          |         |         |         |         | A/D Dat  | a Buffer 12  | /Threshold | for Channel 12        | 2/Threshold fo        | r Channel 0 &         | 12 in Window        | v Compare              |                        |         |         |         | xxxx   |

| ADC1BUF13 | 31Ah          |         |         |         |         | A/D Dat  | a Buffer 13  | /Threshold | for Channel 13        | 3/Threshold fo        | r Channel 1 &         | 13 in Window        | v Compare              |                        |         |         |         | xxxx   |

| ADC1BUF14 | 31Ch          |         |         |         |         | A/D Dat  | a Buffer 14  | /Threshold | for Channel 14        | 4/Threshold fo        | r Channel 2 &         | 14 in Window        | v Compare              |                        |         |         |         | xxxx   |

| ADC1BUF15 | 31Eh          |         |         |         |         | A/D Dat  | a Buffer 15  | /Threshold | for Channel 1         | 5/Threshold fo        | r Channel 3 &         | 15 in Window        | v Compare              |                        |         |         |         | xxxx   |

| ADC1BUF16 | 320h          |         |         |         |         | A/D Dat  | a Buffer 16  | /Threshold | for Channel 1         | 6/Threshold fo        | r Channel 4 &         | 16 in Window        | v Compare              |                        |         |         |         | xxxx   |

| ADC1BUF17 | 322h          |         |         |         |         | A/D Dat  | a Buffer 17  | /Threshold | for Channel 1         | 7/Threshold fo        | r Channel 5 &         | 17 in Window        | v Compare              |                        |         |         |         | xxxx   |

| ADC1BUF18 | 324h          |         |         |         |         | A/D Dat  | a Buffer 18  | /Threshold | for Channel 18        | 8/Threshold fo        | r Channel 6 &         | 18 in Window        | v Compare              |                        |         |         |         | xxxx   |

| ADC1BUF19 | 326h          |         |         |         |         | A/D Dat  | a Buffer 19  | /Threshold | for Channel 19        | 9/Threshold fo        | r Channel 7 &         | 19 in Window        | v Compare              |                        |         |         |         | xxxx   |

| ADC1BUF20 | 328h          |         |         |         |         | A/D Dat  | a Buffer 20  | /Threshold | for Channel 20        | 0/Threshold fo        | r Channel 8 &         | 20 in Window        | v Compare              |                        |         |         |         | xxxx   |

| ADC1BUF21 | 32Ah          |         |         |         |         | A/D Dat  | a Buffer 21  | /Threshold | for Channel 2         | 1/Threshold fo        | r Channel 9 &         | 21 in Window        | v Compare              |                        |         |         |         | xxxx   |

| ADC1BUF22 | 32Ch          |         |         |         |         | A/D Data | a Buffer 22/ | Threshold  | for Channel 22        | 2/Threshold for       | r Channel 10 &        | 22 in Window        | w Compare              |                        |         |         |         | xxxx   |

| ADC1BUF23 | 32Eh          |         |         |         |         | A/D Data | a Buffer 23/ | Threshold  | for Channel 23        | 3/Threshold for       | r Channel 11 &        | 23 in Window        | w Compare              |                        |         |         |         | xxxx   |

| AD1CON1   | 340h          | ADON    | _       | ADSIDL  | _       | _        | MODE12       | FORM1      | FORM0                 | SSRC3                 | SSRC2                 | SSRC1               | SSRC0                  | _                      | ASAM    | SAMP    | DONE    | 0000   |

| AD1CON2   | 342h          | PVCFG1  | PVCFG0  | NVCFG0  | _       | BUFREGEN | CSCNA        | _          | _                     | BUFS                  | SMPI4                 | SMPI3               | SMPI2                  | SMPI1                  | SMPI0   | BUFM    | ALTS    | 0000   |

| AD1CON3   | 344h          | ADRC    | EXTSAM  |         | SAMC4   | SAMC3    | SAMC2        | SAMC1      | SAMC0                 | ADCS7                 | ADCS6                 | ADCS5               | ADCS4                  | ADCS3                  | ADCS2   | ADCS1   | ADCS0   | 0000   |

| AD1CHS    | 348h          | CH0NB2  | CH0NB1  | CH0NB0  | CH0SB4  | CH0SB3   | CH0SB2       | CH0SB1     | CH0SB0                | CH0NA2                | CH0NA1                | CH0NA0              | CH0SA4                 | CH0SA3                 | CH0SA2  | CH0SA1  | CH0SA0  | 0000   |

| AD1CSSH   | 34Eh          | _       | CSS30   | CSS29   | CSS28   | CSS27    | CSS26        | _          | _                     | CSS23                 | CSS22                 | CSS21               | CSS20 <sup>(1)</sup>   | CSS19 <sup>(1)</sup>   | CSS18   | CSS17   | CSS16   | 0000   |

| AD1CSSL   | 350h          | CSS15   | CSS14   | CSS13   | CSS12   | CSS11    | CSS10        | CSS9       | CSS8 <sup>(1,2)</sup> | CSS7 <sup>(1,2)</sup> | CSS6 <sup>(1,2)</sup> | CSS5 <sup>(1)</sup> | CSS4                   | CSS3                   | CSS2    | CSS1    | CSS0    | 0000   |

| AD1CON5   | 354h          | ASEN    | LPEN    | CTMREQ  | BGREQ   | r        | _            | ASINT1     | ASINT0                | _                     | _                     | —                   | _                      | WM1                    | WM0     | CM1     | CM0     | 0000   |

| AD1CHITH  | 356h          | _       | —       | —       | —       | _        | _            | —          | —                     | CHH23                 | CHH22                 | CHH21               | CHH20 <sup>(1)</sup>   | CHH19 <sup>(1)</sup>   | CHH18   | CHH17   | CHH16   | 0000   |

| AD1CHITL  | 358h          | CHH15   | CHH14   | CHH13   | CHH12   | CHH11    | CHH10        | CHH9       | CHH8 <sup>(1,2)</sup> | CHH7 <sup>(1,2)</sup> | CHH6 <sup>(1,2)</sup> | CHH5 <sup>(1)</sup> | CHH4                   | CHH3                   | CHH2    | CHH1    | CHH0    | 0000   |

| AD1CTMENH | 360h          | _       | —       | —       | _       | _        | _            | _          | _                     | CTMEN23               | CTMEN22               | CTMEN21             | CTMEN20 <sup>(1)</sup> | CTMEN19 <sup>(1)</sup> | CTMEN18 | CTMEN17 | CTMEN16 | 0000   |

| AD1CTMENL | 362h          | CTMEN15 | CTMEN14 | CTMEN13 | CTMEN12 | CTMEN11  | CTMEN10      | CTMEN9     | CTMEN8((1,2)          | CTMEN7(1,2)           | CTMEN6(1,2)           | CTMEN5(1)           | CTMEN4                 | CTMEN3                 | CTMEN2  | CTMEN1  | CTMEN0  | 0000   |

$\label{eq:Legend: Legend: Legend: u = unchanged, --= unimplemented, q = value depends on condition, r = reserved.$

Note 1: These bits are not implemented in 20-pin devices.

2: These bits are not implemented in 28-pin devices.

#### U-0 R/W-1 R/W-0 R/W-0 U-0 R/W-1 R/W-0 R/W-0 CNIP2 CNIP1 CNIP0 CMIP2 CMIP1 CMIP0 bit 15 bit 8 U-0 R/W-1 R/W-0 R/W-0 U-0 R/W-1 R/W-0 R/W-0 BCL1IP2 BCL1IP1 BCL1IP0 SSP1IP2 SSP1IP1 SSP1IP0 \_\_\_\_ \_\_\_\_ bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15 Unimplemented: Read as '0' bit 14-12 CNIP<2:0>: Input Change Notification Interrupt Priority bits 111 = Interrupt is Priority 7 (highest priority interrupt) 001 = Interrupt is Priority 1 000 = Interrupt source is disabled bit 11 Unimplemented: Read as '0' bit 10-8 CMIP<2:0>: Comparator Interrupt Priority bits 111 = Interrupt is Priority 7 (highest priority interrupt) 001 = Interrupt is Priority 1 000 = Interrupt source is disabled Unimplemented: Read as '0' bit 7 BCL1IP<2:0>: MSSP1 I<sup>2</sup>C<sup>™</sup> Bus Collision Interrupt Priority bits bit 6-4 111 = Interrupt is Priority 7 (highest priority interrupt) 001 = Interrupt is Priority 1 000 = Interrupt source is disabled bit 3 Unimplemented: Read as '0' bit 2-0 **SSP1IP<2:0>:** MSSP1 SPI/I<sup>2</sup>C Event Interrupt Priority bits 111 = Interrupt is Priority 7 (highest priority interrupt) 001 = Interrupt is Priority 1 000 = Interrupt source is disabled

### REGISTER 8-23: IPC4: INTERRUPT PRIORITY CONTROL REGISTER 4

| U-0         U-0         U-0         U-0         U-0         U-0         U-0           -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         - <t< th=""><th>REGISTER</th><th>9-2: CLKL</th><th>DIV: CLOCK L</th><th></th><th>6151EK</th><th></th><th></th><th></th></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | REGISTER | 9-2: CLKL                                                                                                                                                                                                                                                        | DIV: CLOCK L                                                                                                                                                                                                                                                                                                                      |                                                                                                                  | 6151EK               |                  |                  |        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|----------------------|------------------|------------------|--------|

| bit 15       bit 1         U-0       U-0       U-0       U-0       U-0       U-0         -       -       -       -       -       -         bit 7       bit 10       U-0       U-0       U-0       U-0         Egend:       R       Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       RO: Recover on Interrupt bit       1 = Interrupts clear the DOZEN bit, and reset the CPU and peripheral clock ratio to 1:1       0 = Interrupts have no effect on the DOZEN bit         bit 14-12       DOZE       DOZE       2:0: CPU and Peripheral Clock Ratio Select bits       111 = 1:28         110 = 1:4       101 = 1:28       100 = 1:16       112       100 = 1:16         011 = 1:1       DOZE       2:0: CPU and peripheral clock ratio are set to 1:1       111 = 13:25 kHz (divide-by-26)         110 = 125 kHz (divide-by-26)       111 = 13:25 kHz (divide-by-26)       111:1       111 = 25 kHz (divide-by-32)         100 = 50 KHz (divide-by-32)       100 = 20 KHz (divide-by-32)       100 = 20 KHz (divide-by-32)         111 = 195 kHz (divide-by-32)       111 = 13:25 kHz (divide-by-32)       100 = 25 kHz (divide-by-32)         111 = 195 kHz (divide-by-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0    | R/W-0                                                                                                                                                                                                                                                            | R/W-1                                                                                                                                                                                                                                                                                                                             | R/W-1                                                                                                            |                      | R/W-0            | R/W-0            | R/W-1  |

| U-0         U-0         U-0         U-0         U-0         U-0         U-0           -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ROI      | DOZE2                                                                                                                                                                                                                                                            | DOZE1                                                                                                                                                                                                                                                                                                                             | DOZE0                                                                                                            | DOZEN <sup>(1)</sup> | RCDIV2           | RCDIV1           | RCDIV0 |

| -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | bit 15   |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                   |                                                                                                                  |                      |                  |                  | bit 8  |

| -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 11.0     | 11.0                                                                                                                                                                                                                                                             | 11.0                                                                                                                                                                                                                                                                                                                              | 11.0                                                                                                             | 11.0                 | 11.0             | 11.0             | 11.0   |

| Legend:<br>R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'<br>-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown<br>bit 15 ROI: Recover on Interrupt bit<br>1 = Interrupts clear the DOZEN bit, and reset the CPU and peripheral clock ratio to 1:1<br>0 = Interrupts have no effect on the DOZEN bit<br>bit 14-12 DOZE-2:0-: CPU and Peripheral Clock Ratio Select bits<br>111 = 1:128<br>110 = 1:64<br>110 = 1:132<br>100 = 1:16<br>011 = 1:3<br>100 = 1:16<br>011 = 1:2<br>000 = 1:1<br>bit 11 DOZEN: Doze Enable bit <sup>(1)</sup><br>1 = DOZE-2:0-> bits specify the CPU and peripheral clock ratio<br>0 = CPU and peripheral clock ratio are set to 1:1<br>bit 10-8 RCDIV-2:0->: FRC Postscaler Select bits<br>When COSC-2:0-> (OSCCON<14:12>) = 111:<br>111 = 31.25 kHz (divide-by-256)<br>110 = 125 kHz (divide-by-2)<br>100 = 500 kHz (divide-by-2)<br>100 = 2 MHz (divide-by-2) - default<br>001 = 4 MHz (divide-by-2) - default<br>001 = 4 MHz (divide-by-2)<br>100 = 8 MHz (divide-by-2)<br>100 = 15 kHz (divide-by-2)<br>100 = 15 kHz (divide-by-2)<br>100 = 125 kHz (divide-by-   | 0-0      | 0-0                                                                                                                                                                                                                                                              | 0-0                                                                                                                                                                                                                                                                                                                               | 0-0                                                                                                              | 0-0                  | 0-0              | 0-0              | 0-0    |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       ROI: Recover on Interrupt bit       1 = Interrupts clear the DOZEN bit, and reset the CPU and peripheral clock ratio to 1:1       0 = Interrupts have no effect on the DOZEN bit         bit 14-12       DOZE-2:0>: CPU and Peripheral Clock Ratio Select bits       111 = 1:128         101 = 1:64       101 = 1:32       100 = 1:16         001 = 1:1       000 = 1:11       DOZEN: Doze Enable bit <sup>(1)</sup> 1 = DOZE<2:0>: Dits specify the CPU and peripheral clock ratio       0 = CPU and peripheral clock ratio are set to 1:1         bit 10       DOZEN: Doze Enable bit <sup>(1)</sup> 1 = DOZE         1 = 1:2       000 = 1:1       111 = 31.25 kHz (divide-by-256)         1 = 250 kHz (divide-by-256)       111 = 31.25 kHz (divide-by-256)         1 = 255 kHz (divide-by-32)       100 = 500 kHz (divide-by-32)         1 = 1 = 255 kHz (divide-by-32)       100 = 2 MHz (divide-by-41)         1 = 1 = 152 kHz (divide-by-32)       100 = 2 MHz (divide-by-32)         1 = 1 = 15 kHz (divide-by-32)       110 = 15.62 kHz (divide-by-256)         1 = 1 = 12       111 = 1.18         1 = 1 = 112       111 = 1.18         1 = 1 = 102 kHz (divide-by-32)       100 = 2 kHz (di                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | bit 7    |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                   |                                                                                                                  |                      |                  |                  | bit 0  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       ROI: Recover on Interrupt bit       1 = Interrupts clear the DOZEN bit, and reset the CPU and peripheral clock ratio to 1:1       0 = Interrupts have no effect on the DOZEN bit         bit 14-12       DOZE-2:0>: CPU and Peripheral Clock Ratio Select bits       111 = 1:128         101 = 1:64       101 = 1:32       100 = 1:16         001 = 1:1       000 = 1:11       DOZEN: Doze Enable bit <sup>(1)</sup> 1 = DOZE<2:0>: Dits specify the CPU and peripheral clock ratio       0 = CPU and peripheral clock ratio are set to 1:1         bit 10       DOZEN: Doze Enable bit <sup>(1)</sup> 1 = DOZE         1 = 1:2       000 = 1:1       111 = 31.25 kHz (divide-by-256)         1 = 250 kHz (divide-by-256)       111 = 31.25 kHz (divide-by-256)         1 = 255 kHz (divide-by-32)       100 = 500 kHz (divide-by-32)         1 = 1 = 255 kHz (divide-by-32)       100 = 2 MHz (divide-by-41)         1 = 1 = 152 kHz (divide-by-32)       100 = 2 MHz (divide-by-32)         1 = 1 = 15 kHz (divide-by-32)       110 = 15.62 kHz (divide-by-256)         1 = 1 = 12       111 = 1.18         1 = 1 = 112       111 = 1.18         1 = 1 = 102 kHz (divide-by-32)       100 = 2 kHz (di                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Logondu  |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                   |                                                                                                                  |                      |                  |                  |        |

| <pre>in = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15 ROI: Recover on Interrupt bit 1 = Interrupts clear the DOZEN bit, and reset the CPU and peripheral clock ratio to 1:1 0 = Interrupts have no effect on the DOZEN bit bit 14-12 DOZE-2:0&gt;: CPU and Peripheral Clock Ratio Select bits 111 = 1:128 110 = 1:64 101 = 1:32 100 = 1:1 001 = 1:4 001 = 1:2 000 = 1:1 bit 11 DOZEN: Doze Enable bit<sup>(1)</sup> 1 = DOZE-2:0&gt; bits specify the CPU and peripheral clock ratio 0 = CPU and peripheral clock ratio are set to 1:1 bit 10-8 RCDIVe2:0&gt;: FRC Postscaler Select bits When COSC&lt;2:0&gt; (OSCCON(14:12&gt;) = 111: 111 = 31.25 kHz (divide-by-266) 110 = 125 kHz (divide-by-4) 011 = 150 kHz (divide-by-4) 011 = 150 kHz (divide-by-4) 011 = 15.8 kHz (divide-by-4) 011 = 15.8 kHz (divide-by-4) 101 = 15.62 kHz (divide-by-256) 110 = 7.81 kHz (divide-by-4) 011 = 62.5 kHz (divide-by-4) 011 = 25 kHz (divide-by-4) 011 = 15.62 kHz (divide-by-4) 011 = 25 kHz (divide-by-4) 011 = 25 kHz (divide-by-4) 011 = 15.62 kHz (divide-by-4) 011 = 15.62 kHz (divide-by-4) 011 = 02.5 kHz (divide-by-4) 011 = 15.62 kHz (divide-by-4) 011 = 15.62 kHz (divide-by-2) - default 011 = 02.5 kHz (divide-by-4) 011 = 1.5 kHz (divide-by-4) 011 = 0.5 kH</pre>                                                                                                            | -        | le bit                                                                                                                                                                                                                                                           | W = Writable                                                                                                                                                                                                                                                                                                                      | bit                                                                                                              | U = Unimplem         | nented bit, read | d as '0'         |        |

| bit 15 ROI: Recover on Interrupt bit<br>1 = Interrupts clear the DOZEN bit, and reset the CPU and peripheral clock ratio to 1:1<br>0 = Interrupts have no effect on the DOZEN bit<br>DOZE-2:00: CPU and Peripheral Clock Ratio Select bits<br>111 = 1:128<br>110 = 1:64<br>101 = 1:32<br>100 = 1:16<br>011 = 1:8<br>010 = 1:4<br>001 = 1:2<br>000 = 1:1<br>bit 11 DOZEN: Doze Enable bit <sup>(1)</sup><br>1 = DOZE-2:00: bits specify the CPU and peripheral clock ratio<br>0 = CPU and peripheral clock ratio are set to 1:1<br>bit 10-8 RCDV-2:00: FRC Postscaler Select bits<br>When COSC-2:00: (OSCCON<14:12>) = 111:<br>111 = 31.25 kHz (divide-by-256)<br>110 = 125 kHz (divide-by-256)<br>110 = 125 kHz (divide-by-32)<br>100 = 500 kHz (divide-by-29)<br>011 = 1 MHz (divide-by-2) - default<br>000 = 8 MHz (divide-by-2) - default<br>101 = 25 kHz (divide-by-26)<br>110 = 7.81 kHz (divide-by-32)<br>100 = 7.81 kHz (divide-by-32)<br>100 = 125 kHz (divide-by-2) - default<br>001 = 125 kHz (divide-by-2) - default<br>001 = 125 kHz (divide-by-32)<br>100 = 125 kHz (divide-by-32)<br>100 = 125 kHz (divide-by-32)<br>100 = 125 kHz (divide-by-32)<br>100 = 7.81 kHz (divide-by-32)<br>100 = 125 kHz (divide-by-4)<br>011 = 62.5 kHz (divide-by-4)<br>011 = 50.5 kHz (divide-by-4)<br>011 = 15.5 kHz (divide-by-4)<br>011 = 15.5 kHz (divide-by-4)<br>011 = 62.5 kHz (divide-by-4)<br>011 = 6 |          |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                   |                                                                                                                  | -                    |                  |                  | nown   |

| $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          | 1 = Interrupts<br>0 = Interrupts                                                                                                                                                                                                                                 | s clear the DOZ<br>s have no effect                                                                                                                                                                                                                                                                                               | EN bit, and re<br>t on the DOZE                                                                                  | N bit                | d peripheral cl  | ock ratio to 1:1 |        |

| 1 = DOZE<2:0> bits specify the CPU and peripheral clock ratio 0 = CPU and peripheral clock ratio are set to 1:1 bit 10-8 $RCDIV<2:0>: FRC Postscaler Select bits When COSC<2:0> (OSCCON<14:12>) = 111: 111 = 31.25 kHz (divide-by-256) 110 = 125 kHz (divide-by-264) 101 = 250 kHz (divide-by-32) 100 = 500 kHz (divide-by-32) 100 = 500 kHz (divide-by-4) 011 = 1 MHz (divide-by-4) 010 = 2 MHz (divide-by-2) - default 000 = 8 MHz (divide-by-2) 100 = 8 MHz (divide-by-2) = 110: 111 = 1.95 kHz (divide-by-256) 110 = 7.81 kHz (divide-by-256) 110 = 7.81 kHz (divide-by-32) 100 = 31.25 kHz (divide-by-3) 100 = 31.25 kHz (divide-by-4) 011 = 125 kHz (divide-by-4) 010 = 125 kHz (divide-by-4) 010 = 125 kHz (divide-by-2) - default 000 = 500 kHz (divide-by-1)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          | 111 = 1:128<br>110 = 1:64<br>101 = 1:32<br>100 = 1:16<br>011 = 1:8<br>010 = 1:4<br>001 = 1:2                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                   |                                                                                                                  |                      |                  |                  |        |

| bit 10-8 <b>RCDIV-2:0&gt;:</b> FRC Postscaler Select bits<br>When COSC<2:0> (OSCCON<14:12>) = 111:<br>111 = 31.25 kHz (divide-by-256)<br>110 = 125 kHz (divide-by-64)<br>101 = 250 kHz (divide-by-32)<br>100 = 500 kHz (divide-by-16)<br>011 = 1 MHz (divide-by-8)<br>010 = 2 MHz (divide-by-8)<br>010 = 2 MHz (divide-by-2) – default<br>000 = 8 MHz (divide-by-2) – default<br>000 = 8 MHz (divide-by-1)<br>When COSC<2:0> (OSCCON<14:12>) = 110:<br>111 = 1.95 kHz (divide-by-26)<br>110 = 7.81 kHz (divide-by-32)<br>100 = 31.25 kHz (divide-by-32)<br>100 = 31.25 kHz (divide-by-8)<br>011 = 62.5 kHz (divide-by-8)<br>010 = 125 kHz (divide-by-4)<br>011 = 250 kHz (divide-by-2) – default<br>000 = 500 kHz (divide-by-1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | bit 11   | 1 = DOZE<2                                                                                                                                                                                                                                                       | :0> bits specify                                                                                                                                                                                                                                                                                                                  |                                                                                                                  |                      | ratio            |                  |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | bit 10-8 | When COSC<br>111 = 31.25 K<br>110 = 125 K<br>101 = 250 K<br>100 = 500 K<br>011 = 1 MHz<br>010 = 2 MHz<br>001 = 4 MHz<br>000 = 8 MHz<br>When COSC<br>111 = 1.95 K<br>100 = 7.81 K<br>101 = 15.62 K<br>100 = 31.25 K<br>011 = 62.5 K<br>010 = 125 K<br>001 = 250 K | <2:0> (OSCCO<br>kHz (divide-by-2<br>dz (divide-by-2<br>dz (divide-by-32<br>dz (divide-by-32<br>dz (divide-by-38)<br>(divide-by-4)<br>(divide-by-4)<br>(divide-by-2)<br>- (divide-by-2)<br>- (divide-by-2)<br>- (divide-by-2)<br>- (divide-by-2)<br>- (z (divide-by-3)<br>dz (divide-by-4)<br>dz (divide-by-4)<br>dz (divide-by-2) | <u>N&lt;14:12&gt;) = 1</u><br>256)<br>)<br>)<br>default<br><u>N&lt;14:12&gt;) = 1</u><br>56)<br>4)<br>32)<br>16) | -                    |                  |                  |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | bit 7-0  |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                   | )'                                                                                                               |                      |                  |                  |        |

#### REGISTER 9-2: CLKDIV: CLOCK DIVIDER REGISTER

**Note 1:** This bit is automatically cleared when the ROI bit is set and an interrupt occurs.

### REGISTER 13-1: CCPxCON1L: CCPx CONTROL 1 LOW REGISTERS (CONTINUED)

bit 3-0 MOD<3:0>: CCPx Mode Select bits

For CCSEL = 1 (Input Capture modes):

- 1xxx = Reserved

- 011x = Reserved

- 0101 = Capture every 16th rising edge

- 0100 = Capture every 4th rising edge

- 0011 = Capture every rising and falling edge

- 0010 = Capture every falling edge

- 0001 = Capture every rising edge

- 0000 = Capture every rising and falling edge (Edge Detect mode)

- For CCSEL = 0 (Output Compare/Timer modes):

- 1111 = External Input mode: Pulse generator is disabled, source is selected by ICS<2:0>

- 1110 = Reserved

- 110x = Reserved

- 10xx = Reserved

- 0111 = Variable Frequency Pulse mode

- 0110 = Center-Aligned Pulse Compare mode, buffered

- 0101 = Dual Edge Compare mode, buffered

- 0100 = Dual Edge Compare mode

- 0011 = 16-Bit/32-Bit Single Edge mode, toggle output on compare match

- 0010 = 16-Bit/32-Bit Single Edge mode, drive output low on compare match

- 0001 = 16-Bit/32-Bit Single Edge mode, drive output high on compare match

- 0000 = 16-Bit/32-Bit Timer mode, output functions are disabled

- **Note 1:** Clock options are limited in some operating modes. See Table 13-1 for restrictions.

### REGISTER 13-7: CCPxSTATL: CCPx STATUS REGISTER

| U-0           | U-0           | U-0                                    | U-0           | U-0               | U-0              | U-0             | U-0           |

|---------------|---------------|----------------------------------------|---------------|-------------------|------------------|-----------------|---------------|

| _             | _             | —                                      | _             | —                 | _                | —               |               |

| bit 15        |               |                                        |               |                   |                  |                 | bit 8         |

|               |               |                                        | 5/0.0         | 5/2.2             | 5/0.0            | 5/2.2           | 5/2.2         |

| R-0           | W1-0          | W1-0                                   | R/C-0         | R/C-0             | R/C-0            | R/C-0           | R/C-0         |

| CCPTRIG       | TRSET         | TRCLR                                  | ASEVT         | SCEVT             | ICDIS            | ICOV            | ICBNE         |

| bit 7         |               |                                        |               |                   |                  |                 | bit 0         |

| Legend:       |               | C = Clearable                          | bit           |                   |                  |                 |               |

| R = Readabl   | e bit         | W1 = Write '1'                         | only          | U = Unimplem      | nented bit, read | as '0'          |               |

| -n = Value at | POR           | '1' = Bit is set                       |               | '0' = Bit is clea | ared             | x = Bit is unkr | nown          |

|               |               |                                        |               |                   |                  |                 |               |

| bit 15-8      | Unimplemen    | ted: Read as '0                        | ,             |                   |                  |                 |               |

| bit 7         | CCPTRIG: C    | CPx Trigger Sta                        | tus bit       |                   |                  |                 |               |

|               |               | s been triggered<br>s not been trigg   |               |                   |                  |                 |               |

| <b>h</b> :# 0 |               |                                        |               | eiu in Resel      |                  |                 |               |

| bit 6         |               | x Trigger Set Re                       |               | when TRIGEN       | = 1 (location a) | wave reade as   | : '∩')        |