#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 37                                                                            |

| Program Memory Size        | 16KB (5.5K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5V                                                                       |

| Data Converters            | A/D 22x10b/12b; D/A 2x8b                                                      |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

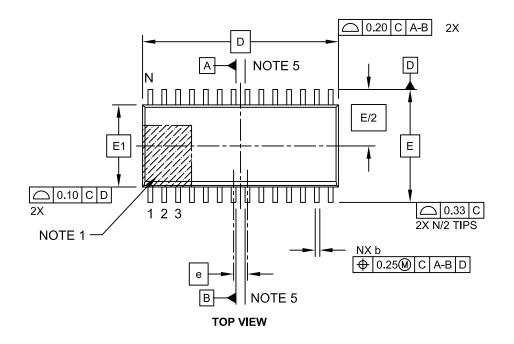

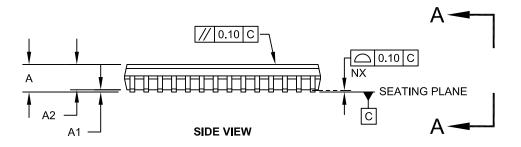

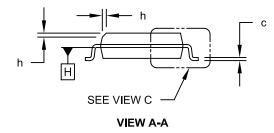

| Package / Case             | 44-TQFP                                                                       |

| Supplier Device Package    | 44-TQFP (10x10)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fv16km204-e-pt |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Pin Diagrams (Continued)

| 20-1     | Pin SPDIP/SSOP/SOIC       MCLR/RA5       1       28       AVDD         RA0       2       27       AVss         RA1       23       26       RB15         RB0       4       C25       RB14         RB1       5       24       RB13         RB2       6       23       RB12         RB3       7       22       RB11         Vss       8       21       RB10         RA3       10       C0       RA6 or Vbbcore         RA3       10       C0       RA7         RB4       111       18       RB9         RA4       112       17       RB8         Vob       13       16       RB7         RB5<       14       15       RB6 |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin      | Pin Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|          | PIC24FXXKMX02 PIC24FVXXKMX02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1        | MCLR/Vpp/RA5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2        | CVREF+/VREF+/ /AN0/ /CN2/RA0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3        | CVREF-/VREF-/AN1/CN3/RA1 CVREF-/VREF-/AN1/RA1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4        | PGED1/AN2/CTCMP/ULPWU/C1IND/ / / /CN4/RB0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5        | PGEC1/ / /AN3/C1INC/ / /CTED12/CN5/RB1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6        | / /AN4/C1INB/ / /U1RX/TCKIB/CTED13/CN6/RB2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 7        | /AN5/C1INA/ / /CN7/RB3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 8        | Vss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 9        | OSCI/CLKI/AN13/CN30/RA2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 10       | OSCO/CLKO/AN14/CN29/RA3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 11       | SOSCI/AN15/ / /CN1/RB4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 12       | SOSCO/SCLKI/AN16/PWRLCLK/ /CN0/RA4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 13       | VDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 14       | PGED3/AN17/ASDA1/ / /OC1E/CLCINA/CN27/RB5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 15       | PGEC3/AN18/ASCL1/ / /OC1F/CLCINB/CN24/RB6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 16       | AN19/U1TX/INT0/CN23/RB7 AN19/U1TX/ / /INT0/CN23/RB7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 17       | AN20/SCL1/U1CTS/C3OUT/OC1B/CTED10/CN22/RB8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 18       | AN21/SDA1/T1CK/U1RTS/U1BCLK/IC2/ /CLC10/CTED4/CN21/RB9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 19       | /IC1/ / /CTED3/CN9/RA7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 20       | /OC1A/CTED1/INT2/CN8/RA6 VCAP OR VDDCORE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 21<br>22 | PGED2/SDI1/ /OC1C/CTED11/CN16/RB10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 22<br>23 | PGEC2/SCK1/OC2A/CTED9/CN15/RB11           /AN12/HLVDIN/         /           /AN12/HLVDIN/         /           /B12         //                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 24       | / /AN11/SD01/OCFB/ /OC1D/CTPLS/CN13/RB13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 25       | /CVREF/ / /AN10/ / /C1OUT/OCFA/CTED5/INT1/CN12/RB14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 26       | / /AN9/ /REFO/SS1/TCKIA/CTED6/CN11/RB15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 27       | Vss/AVss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 28       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

Legend: Values in indicate pin function differences between PIC24F(V)XXKM202 and PIC24F(V)XXKM102 devices.

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

Microchip's Worldwide Web site; http://www.microchip.com

Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

#### TABLE 1-5: PIC24FV16KM204 FAMILY PINOUT DESCRIPTION

|          |                                  |                                  | F             |                        |                |                                  |                                  | FV            |                        |                |     |                   |                                   |

|----------|----------------------------------|----------------------------------|---------------|------------------------|----------------|----------------------------------|----------------------------------|---------------|------------------------|----------------|-----|-------------------|-----------------------------------|

|          |                                  |                                  | Pin Numb      | er                     |                | Pin Number                       |                                  |               |                        |                |     |                   |                                   |

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | I/O | Buffer            | Description                       |

| AN0      | 2                                | 2                                | 27            | 19                     | 21             | 2                                | 2                                | 27            | 19                     | 21             | I   | ANA               | A/D Analog Inputs                 |

| AN1      | 3                                | 3                                | 28            | 20                     | 22             | 3                                | 3                                | 28            | 20                     | 22             | I   | ANA               | A/D Analog Inputs                 |

| AN2      | 4                                | 4                                | 1             | 21                     | 23             | 4                                | 4                                | 1             | 21                     | 23             | I   | ANA               | A/D Analog Inputs                 |

| AN3      | 5                                | 5                                | 2             | 22                     | 24             | 5                                | 5                                | 2             | 22                     | 24             | Ι   | ANA               | A/D Analog Inputs                 |

| AN4      | 6                                | 6                                | 3             | 23                     | 25             | 6                                | 6                                | 3             | 23                     | 25             | I   | ANA               | A/D Analog Inputs                 |

| AN5      | _                                | 7                                | 4             | 24                     | 26             | —                                | 7                                | 4             | 24                     | 26             | I   | ANA               | A/D Analog Inputs                 |

| AN6      | _                                | —                                | —             | 25                     | 27             | —                                | —                                |               | 25                     | 27             | I   | ANA               | A/D Analog Inputs                 |

| AN7      | _                                | —                                | —             | 26                     | 28             | —                                | —                                |               | 26                     | 28             | I   | ANA               | A/D Analog Inputs                 |

| AN8      | _                                | —                                | —             | 27                     | 29             | —                                | —                                |               | 27                     | 29             | I   | ANA               | A/D Analog Inputs                 |

| AN9      | 18                               | 26                               | 23            | 15                     | 16             | 18                               | 26                               | 23            | 15                     | 16             | I   | ANA               | A/D Analog Inputs                 |

| AN10     | 17                               | 25                               | 22            | 14                     | 15             | 17                               | 25                               | 22            | 14                     | 15             | I   | ANA               | A/D Analog Inputs                 |

| AN11     | 16                               | 24                               | 21            | 11                     | 12             | 16                               | 24                               | 21            | 11                     | 12             | I   | ANA               | A/D Analog Inputs                 |

| AN12     | 15                               | 23                               | 20            | 10                     | 11             | 15                               | 23                               | 20            | 10                     | 11             | I   | ANA               | A/D Analog Inputs                 |

| AN13     | 7                                | 9                                | 6             | 30                     | 33             | 7                                | 9                                | 6             | 30                     | 33             | I   | ANA               | A/D Analog Inputs                 |

| AN14     | 8                                | 10                               | 7             | 31                     | 34             | 8                                | 10                               | 7             | 31                     | 34             | I   | ANA               | A/D Analog Inputs                 |

| AN15     | 9                                | 11                               | 8             | 33                     | 36             | 9                                | 11                               | 8             | 33                     | 36             | I   | ANA               | A/D Analog Inputs                 |

| AN16     | 10                               | 12                               | 9             | 34                     | 37             | 10                               | 12                               | 9             | 34                     | 37             | I   | ANA               | A/D Analog Inputs                 |

| AN17     | _                                | 14                               | 11            | 41                     | 45             | _                                | 14                               | 11            | 41                     | 45             | I   | ANA               | A/D Analog Inputs                 |

| AN18     | _                                | 15                               | 12            | 42                     | 46             | _                                | 15                               | 12            | 42                     | 46             | I   | ANA               | A/D Analog Inputs                 |

| AN19     | 11                               | 16                               | 13            | 43                     | 47             | 11                               | 16                               | 13            | 43                     | 47             | I   | ANA               | A/D Analog Inputs                 |

| AN20     | 12                               | 17                               | 14            | 44                     | 48             | 12                               | 17                               | 14            | 44                     | 48             | I   | ANA               | A/D Analog Inputs                 |

| AN21     | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | I   | ANA               | A/D Analog Inputs                 |

| ASCL1    | _                                | 15                               | 12            | 42                     | 46             | _                                | 15                               | 12            | 42                     | 46             | I/O | I <sup>2</sup> C™ | Alternate I2C1 Clock Input/Output |

| ASDA1    | _                                | 14                               | 11            | 41                     | 45             | _                                | 14                               | 11            | 41                     | 45             | I/O | l <sup>2</sup> C  | Alternate I2C1 Data Input/Output  |

| AVDD     | 20                               | 28                               | 25            | 17                     | 18             | 20                               | 28                               | 25            | 17                     | 18             | Р   |                   | A/D Supply Pins                   |

| AVss     | 19                               | 27                               | 24            | 16                     | 17             | 19                               | 27                               | 24            | 16                     | 17             | Р   |                   | A/D Supply Pins                   |

| C1INA    | 8                                | 7                                | 4             | 24                     | 26             | 8                                | 7                                | 4             | 24                     | 26             | Ι   | ANA               | Comparator 1 Input A (+)          |

| C1INB    | 7                                | 6                                | 3             | 23                     | 25             | 7                                | 6                                | 3             | 23                     | 25             | I   | ANA               | Comparator 1 Input B (-)          |

| C1INC    | 5                                | 5                                | 2             | 22                     | 24             | 5                                | 5                                | 2             | 22                     | 24             | Ι   | ANA               | Comparator 1 Input C (+)          |

| C1IND    | 4                                | 4                                | 1             | 21                     | 23             | 4                                | 4                                | 1             | 21                     | 23             | Ι   | ANA               | Comparator 1 Input D (-)          |

**Legend:** ANA = Analog level input/output, ST = Schmitt Trigger input buffer,  $I^2C^{TM} = I^2C/SMBus$  input buffer

DS30003030B-page 20

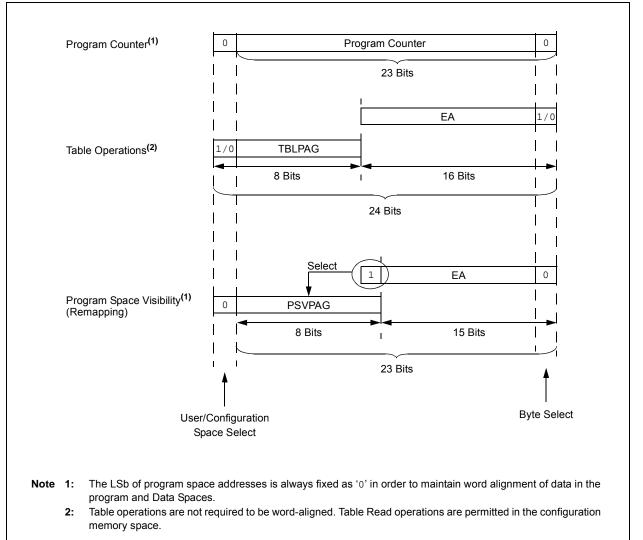

#### TABLE 4-35: PROGRAM SPACE ADDRESS CONSTRUCTION

|                          | Access                 | Program Space Address |              |                      |                         |        |  |  |

|--------------------------|------------------------|-----------------------|--------------|----------------------|-------------------------|--------|--|--|

| Access Type              | Space                  | Space <23> <2         |              | <15>                 | <14:1>                  | <0>    |  |  |

| Instruction Access       | Access User 0 PC<22:1> |                       |              |                      |                         | 0      |  |  |

| (Code Execution)         |                        |                       | 0xx xxxx x   | xxx xxxx xxxx xxx0   |                         |        |  |  |

| TBLRD/TBLWT              | User                   | TB                    | LPAG<7:0>    | Data EA<15:0>        |                         |        |  |  |

| (Byte/Word Read/Write)   |                        | 02                    | xxx xxxx     | XXXX XXXX XXXX XXXX  |                         |        |  |  |

|                          | Configuration          | TBLPAG<7:0>           |              | Data EA<15:0>        |                         |        |  |  |

|                          |                        | 1:                    | xxx xxxx     | XXXX XXXX XXXX XXXX  |                         | xxx    |  |  |

| Program Space Visibility | User                   | 0                     | 0 PSVPAG<7:0 |                      | 7:0>(2) Data EA<14:0>(1 |        |  |  |

| (Block Remap/Read)       |                        | 0                     | xxxx xxx     | xx xxx xxxx xxxx xxx |                         | x xxxx |  |  |

**Note 1:** Data EA<15> is always '1' in this case, but is not used in calculating the program space address. Bit 15 of the address is PSVPAG<0>.

2: PSVPAG can have only two values ('00' to access program memory and FF to access data EEPROM) on the PIC24F16KM family.

#### FIGURE 4-5: DATA ACCESS FROM PROGRAM SPACE ADDRESS GENERATION

## 5.2 RTSP Operation

The PIC24F Flash program memory array is organized into rows of 32 instructions or 96 bytes. RTSP allows the user to erase blocks of 1 row, 2 rows and 4 rows (32, 64 and 128 instructions) at a time, and to program one row at a time. It is also possible to program single words.

The 1-row (96 bytes), 2-row (192 bytes) and 4-row (384 bytes) erase blocks, and single row write block (96 bytes) are edge-aligned, from the beginning of program memory.

When data is written to program memory using TBLWT instructions, the data is not written directly to memory. Instead, data written using Table Writes is stored in holding latches until the programming sequence is executed.

Any number of TBLWT instructions can be executed and a write will be successfully performed. However, 32 TBLWT instructions are required to write the full row of memory.

The basic sequence for RTSP programming is to set up a Table Pointer, then do a series of TBLWT instructions to load the buffers. Programming is performed by setting the control bits in the NVMCON register.

Data can be loaded in any order and the holding registers can be written to multiple times before performing a write operation. Subsequent writes, however, will wipe out any previous writes.

| Note: | Writing | to a lo |      | location     | multiple | times, |

|-------|---------|---------|------|--------------|----------|--------|

|       | without | eras    | sing | it, is not i | recommer | nded.  |

All of the Table Write operations are single-word writes (two instruction cycles), because only the buffers are written. A programming cycle is required for programming each row.

## 5.3 Enhanced In-Circuit Serial Programming

Enhanced ICSP uses an on-board bootloader, known as the Program Executive (PE), to manage the programming process. Using an SPI data frame format, the Program Executive can erase, program and verify program memory. For more information on Enhanced ICSP, see the device programming specification.

### 5.4 Control Registers

There are two SFRs used to read and write the program Flash memory: NVMCON and NVMKEY.

The NVMCON register (Register 5-1) controls the blocks that need to be erased, which memory type is to be programmed and when the programming cycle starts.

NVMKEY is a write-only register that is used for write protection. To start a programming or erase sequence, the user must consecutively write 55h and AAh to the NVMKEY register. Refer to **Section 5.5 "Programming Operations"** for further details.

## 5.5 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. During a programming or erase operation, the processor stalls (waits) until the operation is finished. Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

#### EXAMPLE 5-5: INITIATING A PROGRAMMING SEQUENCE – ASSEMBLY LANGUAGE CODE

| DISI | #5          | ; | Block all interrupts<br>for next 5 instructions |

|------|-------------|---|-------------------------------------------------|

| MOV  | #0x55, W0   |   |                                                 |

| MOV  | W0, NVMKEY  | ; | Write the 55 key                                |

| MOV  | #0xAA, W1   | ; |                                                 |

| MOV  | W1, NVMKEY  | ; | Write the AA key                                |

| BSET | NVMCON, #WR | ; | Start the erase sequence                        |

| NOP  |             | ; | 2 NOPs required after setting WR                |

| NOP  |             | ; |                                                 |

| BTSC | NVMCON, #15 | ; | Wait for the sequence to be completed           |

| BRA  | \$-2        | ; |                                                 |

|      |             |   |                                                 |

#### EXAMPLE 5-6: INITIATING A PROGRAMMING SEQUENCE – 'C' LANGUAGE CODE

| // C example using MPLAB C30 |                                                 |

|------------------------------|-------------------------------------------------|

| asm("DISI #5");              | // Block all interrupts for next 5 instructions |

| builtin_write_NVM();         | // Perform unlock sequence and set WR           |

**REGISTER 7-1:**

RCON: RESET CONTROL REGISTER<sup>(1)</sup>

| R/W-0, H   | S R/W-0, HS                    | R/W-0                 | R/W-0                | U-0                  | U-0                                 | R/W-0             | R/W-0          |

|------------|--------------------------------|-----------------------|----------------------|----------------------|-------------------------------------|-------------------|----------------|

| TRAPR      |                                | SBOREN                | RETEN <sup>(3)</sup> | _                    | _                                   | СМ                | PMSLP          |

| bit 15     |                                |                       |                      |                      |                                     |                   | bit 8          |

|            |                                |                       |                      |                      |                                     |                   |                |

| R/W-0, H   | S R/W-0, HS                    | R/W-0, HS             | R/W-0, HS            | R/W-0, HS            | R/W-0, HS                           | R/W-1, HS         | R/W-1, HS      |

| EXTR       | SWR                            | SWDTEN <sup>(2)</sup> | WDTO                 | SLEEP                | IDLE                                | BOR               | POR            |

| bit 7      |                                |                       |                      |                      |                                     |                   | bit C          |

|            |                                |                       |                      |                      |                                     |                   |                |

| Legend:    |                                | HS = Hardwar          | e Settable bit       |                      |                                     |                   |                |

| R = Read   | able bit                       | W = Writable t        | pit                  | U = Unimplen         | nented bit, read                    | as '0'            |                |

| -n = Value | e at POR                       | '1' = Bit is set      |                      | '0' = Bit is cle     | ared                                | x = Bit is unkn   | own            |

|            |                                |                       |                      |                      |                                     |                   |                |

| bit 15     | -                              | Reset Flag bit        |                      |                      |                                     |                   |                |

|            | •                              | onflict Reset has     |                      |                      |                                     |                   |                |

| 1.11.4.4   |                                | onflict Reset has     |                      |                      | <b>E</b> 1                          |                   |                |

| bit 14     |                                | gal Opcode or l       |                      |                      | r Flag bit<br>or Uninitialized V    | / register used   | aa an Addraaa  |

|            |                                | aused a Reset         | on, an illegal a     | duress mode c        |                                     | v register used   | as an Address  |

|            |                                | opcode or Unir        | nitialized W Re      | set has not oc       | curred                              |                   |                |

| bit 13     | SBOREN: So                     | oftware Enable/D      | Disable of BOF       | R bit                |                                     |                   |                |

|            | 1 = BOR is tu                  | rned on in softw      | are                  |                      |                                     |                   |                |

|            |                                | rned off in softw     |                      |                      |                                     |                   |                |

| bit 12     |                                | ention Sleep Mo       |                      |                      |                                     |                   |                |

|            |                                |                       |                      |                      | Regulator (RETR<br>ge Regulator (VF |                   |                |

| bit 11-10  | -                              | ted: Read as '0       |                      |                      |                                     |                   |                |

| bit 9      | -                              | ation Word Misr       |                      | lag bit              |                                     |                   |                |

|            | -                              | ration Word Mis       |                      | -                    |                                     |                   |                |

|            | 0 = A Configu                  | ration Word Mis       | match Reset          | has not occurre      | ed                                  |                   |                |

| bit 8      | PMSLP: Prog                    | gram Memory Po        | ower During S        | leep bit             |                                     |                   |                |

|            |                                | memory bias vo        |                      |                      |                                     |                   |                |

|            | 0 = Program<br>Standby         |                       | oltage is pow        | ered down du         | iring Sleep and                     | the voltage re    | gulator enters |

| bit 7      | •                              | nal Reset (MCLF       | R) Pin hit           |                      |                                     |                   |                |

| bit i      |                                | Clear (pin) Rese      |                      | d                    |                                     |                   |                |

|            |                                | Clear (pin) Rese      |                      |                      |                                     |                   |                |

| bit 6      | SWR: Softwa                    | re reset (Instru      | uction) Flag bit     | t                    |                                     |                   |                |

|            |                                | instruction has t     |                      |                      |                                     |                   |                |

|            |                                | instruction has r     |                      |                      |                                     |                   |                |

| bit 5      |                                | oftware Enable/[      | Disable of WD        | l bit <sup>(2)</sup> |                                     |                   |                |

|            | 1 = WDT is ei<br>0 = WDT is di |                       |                      |                      |                                     |                   |                |

|            |                                |                       |                      |                      | <b>-</b>                            |                   |                |

| Note 1:    | All of the Reset               | •                     | be set or clear      | ed in software.      | Setting one of the                  | nese bits in soft | ware does not  |

| 2:         | If the FWDTEN                  |                       | tion bits are '1     | 1' (upprogram        | med) the WDT i                      | is alwavs enabl   | ed renardless  |

| <b>_</b> . | of the SWDTEN                  |                       |                      |                      |                                     | ie amayo chabi    |                |

| -          |                                |                       |                      |                      |                                     |                   |                |

#### 3: This is implemented on PIC24FV16KMXXX parts only; not used on PIC24F16KMXXX devices.

### REGISTER 8-7: IFS2: INTERRUPT FLAG STATUS REGISTER 2

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0, HS | U-0   |

|--------|-----|-----|-----|-----|-----|-----------|-------|

| —      | —   | —   | —   | —   | —   | CCT5IF    | —     |

| bit 15 |     |     |     |     |     |           | bit 8 |

|        |     |     |     |     |     |           |       |

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0       | U-0   |

|        |     | _   | _   |     | _   |           | _     |

| bit 7  |     |     |     |     |     |           | bit 0 |

| Legend:           | HS = Hardware Settable bit |                                    |                    |  |

|-------------------|----------------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 15-10 | Unimplemented: Read as '0'                                |

|-----------|-----------------------------------------------------------|

| bit 9     | CCT5IF: Capture/Compare 5 Timer Interrupt Flag Status bit |

|           | 1 = Interrupt request has occurred                        |

|           | 0 = Interrupt request has not occurred                    |

|           |                                                           |

bit 8-0 Unimplemented: Read as '0'

### REGISTER 8-8: IFS3: INTERRUPT FLAG STATUS REGISTER 3

| U-0    | R/W-0, HS | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----------|-----|-----|-----|-----|-----|-------|

| —      | RTCIF     | —   | —   | —   | —   | —   | —     |

| bit 15 |           |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0, HS | R/W-0, HS | U-0   |

|-------|-----|-----|-----|-----|-----------|-----------|-------|

| —     | —   | —   | —   | —   | BCL2IF    | SSP2IF    | —     |

| bit 7 |     |     |     |     |           |           | bit 0 |

| Legend:           | HS = Hardware Settable bit |                             |                    |

|-------------------|----------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15   | Unimplemented: Read as '0'                                                          |

|----------|-------------------------------------------------------------------------------------|

| bit 14   | RTCIF: Real-Time Clock and Calendar Interrupt Flag Status bit                       |

|          | 1 = Interrupt request has occurred                                                  |

|          | 0 = Interrupt request has not occurred                                              |

| bit 13-3 | Unimplemented: Read as '0'                                                          |

| bit 2    | BCL2IF: MSSP2 I <sup>2</sup> C <sup>™</sup> Bus Collision Interrupt Flag Status bit |

|          | 1 = Interrupt request has occurred                                                  |

|          | 0 = Interrupt request has not occurred                                              |

| bit 1    | SSP2IF: MSSP2 SPI/I <sup>2</sup> C Event Interrupt Flag Status bit                  |

|          | 1 = Interrupt request has occurred                                                  |

|          | 0 = Interrupt request has not occurred                                              |

| bit 0    | Unimplemented: Read as '0'                                                          |

|          |                                                                                     |

#### REGISTER 10-1: ULPWCON: ULPWU CONTROL REGISTER

| R/W-0         | U-0                                    | R/W-0            | U-0              | U-0               | U-0             | U-0             | R/W-0   |  |  |

|---------------|----------------------------------------|------------------|------------------|-------------------|-----------------|-----------------|---------|--|--|

| ULPEN         |                                        | ULPSIDL          | _                | —                 | _               | _               | ULPSINK |  |  |

| bit 15        |                                        |                  |                  |                   |                 |                 | bit 8   |  |  |

|               |                                        |                  |                  |                   |                 |                 |         |  |  |

| U-0           | U-0                                    | U-0              | U-0              | U-0               | U-0             | U-0             | U-0     |  |  |

| _             | _                                      | —                |                  | —                 | _               | _               | —       |  |  |

| bit 7         | ·                                      | · · ·            |                  |                   |                 |                 | bit 0   |  |  |

|               |                                        |                  |                  |                   |                 |                 |         |  |  |

| Legend:       |                                        |                  |                  |                   |                 |                 |         |  |  |

| R = Readabl   | le bit                                 | W = Writable b   | it               | U = Unimplen      | nented bit, rea | d as '0'        |         |  |  |

| -n = Value at | POR                                    | '1' = Bit is set |                  | '0' = Bit is clea | ared            | x = Bit is unkr | nown    |  |  |

|               |                                        |                  |                  |                   |                 |                 |         |  |  |

| bit 15        | ULPEN: ULF                             | PWU Module En    | able bit         |                   |                 |                 |         |  |  |

|               | 1 = Module i                           |                  |                  |                   |                 |                 |         |  |  |

|               | 0 = Module i                           | s disabled       |                  |                   |                 |                 |         |  |  |

| bit 14        | Unimpleme                              | nted: Read as '0 | ,                |                   |                 |                 |         |  |  |

| bit 13        | ULPSIDL: U                             | LPWU Stop in Ic  | lle Select bit   |                   |                 |                 |         |  |  |

|               |                                        | nues module ope  |                  |                   | Idle mode       |                 |         |  |  |

|               | 0 = Continue                           | es module operat | tion in Idle mod | e                 |                 |                 |         |  |  |

| bit 12-9      | Unimplemented: Read as '0'             |                  |                  |                   |                 |                 |         |  |  |

| bit 8         | ULPSINK: ULPWU Current Sink Enable bit |                  |                  |                   |                 |                 |         |  |  |

|               | 1 = Current sink is enabled            |                  |                  |                   |                 |                 |         |  |  |

|               | 0 = Current s                          | sink is disabled |                  |                   |                 |                 |         |  |  |

| bit 7-0       | Unimpleme                              | nted: Read as '0 | 3                |                   |                 |                 |         |  |  |

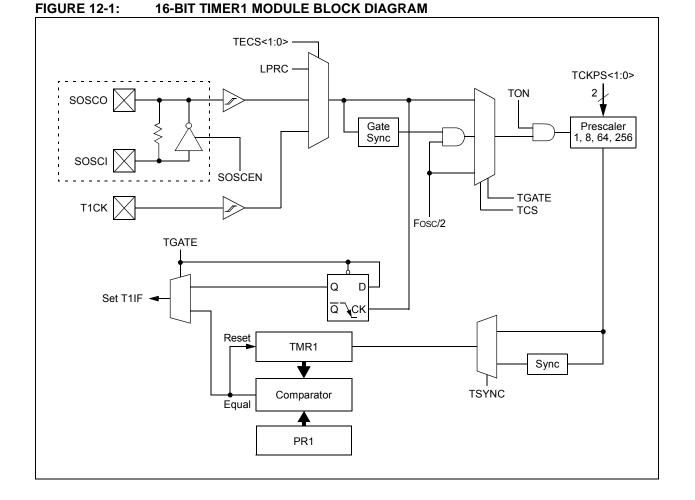

## 12.0 TIMER1

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on timers, refer to the "PIC24F Family Reference Manual", "Timers" (DS39704).

The Timer1 module is a 16-bit timer which can serve as the time counter for the Real-Time Clock (RTC) or operate as a free-running, interval timer/counter. Timer1 can operate in three modes:

- 16-Bit Timer

- 16-Bit Synchronous Counter

- 16-Bit Asynchronous Counter

Timer1 also supports these features:

- Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation During CPU Idle and Sleep modes

- Interrupt on 16-Bit Period Register Match or Falling Edge of External Gate Signal

Figure 12-1 illustrates a block diagram of the 16-bit Timer1 module.

To configure Timer1 for operation:

- 1. Set the TON bit (= 1).

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits.

- 4. Set or clear the TSYNC bit to configure synchronous or asynchronous operation.

- 5. Load the timer period value into the PR1 register.

- 6. If interrupts are required, set the Timer1 Interrupt Enable bit, T1IE. Use the Timer1 Interrupt Priority bits, T1IP<2:0>, to set the interrupt priority.

#### REGISTER 13-6: CCPxCON3H: CCPx CONTROL 3 HIGH REGISTERS

| R/W-0         | R/W-0                 | R/W-0                                  | R/W-0                                | U-0                 | R/W-0                | R/W-0                  | R/W-0                  |

|---------------|-----------------------|----------------------------------------|--------------------------------------|---------------------|----------------------|------------------------|------------------------|

| OETRIG        | OSCNT2                | OSCNT1                                 | OSCNT0                               | _                   | OUTM2 <sup>(1)</sup> | OUTM1 <sup>(1)</sup>   | OUTM0 <sup>(1)</sup>   |

| bit 15        |                       |                                        |                                      |                     |                      |                        | bit 8                  |

|               |                       |                                        |                                      |                     |                      |                        |                        |

| U-0           | U-0                   | R/W-0                                  | R/W-0                                | R/W-0               | R/W-0                | R/W-0                  | R/W-0                  |

|               |                       | POLACE                                 | POLBDF <sup>(1)</sup>                | PSSACE1             | PSSACE0              | PSSBDF1 <sup>(1)</sup> | PSSBDF0 <sup>(1)</sup> |

| bit 7         |                       |                                        |                                      |                     |                      |                        | bit C                  |

| Legend:       |                       |                                        |                                      |                     |                      |                        |                        |

| R = Readabl   | le bit                | W = Writable                           | bit                                  | U = Unimplen        | nented bit, read     | d as '0'               |                        |

| -n = Value at | POR                   | '1' = Bit is set                       |                                      | '0' = Bit is cle    |                      | x = Bit is unkn        | own                    |

|               |                       |                                        |                                      |                     |                      |                        | -                      |

| bit 15        | OETRIG: CC            | Px Dead-Time                           | Select bit                           |                     |                      |                        |                        |

|               | 1 = For Trigg         | ered mode (TF                          | RIGEN = 1): Mo                       | dule does not       | drive enabled o      | output pins until      | triggered              |

|               |                       | output pin opera                       |                                      |                     |                      |                        |                        |

| bit 14-12     | OSCNT<2:0>            | : One-Shot Ev                          | ent Count bits                       |                     |                      |                        |                        |

|               |                       |                                        | nt by 7 time ba                      |                     |                      |                        |                        |

|               |                       |                                        | nt by 6 time ba                      |                     |                      |                        |                        |

|               |                       |                                        | nt by 5 time bas<br>nt by 4 time bas |                     |                      |                        |                        |

|               |                       |                                        | nt by 3 time bas                     |                     |                      |                        |                        |

|               |                       |                                        | nt by 2 time ba                      |                     |                      |                        |                        |

|               |                       |                                        | nt by 1 time ba                      |                     |                      |                        |                        |

|               | 000 <b>= Do no</b>    | t extend one-sl                        | not Trigger ever                     | nt                  |                      |                        |                        |

| bit 11        | -                     | ted: Read as '                         |                                      |                     |                      |                        |                        |

| bit 10-8      | OUTM<2:0>:            | PWMx Output                            | Mode Control I                       | oits <sup>(1)</sup> |                      |                        |                        |

|               | 111 = Reserv          |                                        |                                      |                     |                      |                        |                        |

|               | 110 = Output          |                                        | 1. f                                 |                     |                      |                        |                        |

|               |                       | DC Output mod<br>DC Output mod         |                                      |                     |                      |                        |                        |

|               | 011 = Reserv          | •                                      |                                      |                     |                      |                        |                        |

|               | 010 = Half-Br         | idge Output me                         | ode                                  |                     |                      |                        |                        |

|               |                       | Pull Output mod                        |                                      |                     |                      |                        |                        |

|               | 000 <b>= Steera</b> l | ble Single Outp                        | out mode                             |                     |                      |                        |                        |

| bit 7-6       | -                     | ted: Read as '                         |                                      |                     |                      |                        |                        |

| bit 5         |                       | -                                      | s, OCxA, OCxC                        | and OCxE, P         | olarity Control      | bit                    |                        |

|               |                       | in polarity is ac<br>in polarity is ac |                                      |                     |                      |                        |                        |

| bit 4         |                       |                                        | s, OCxB, OCxE                        | and OCxF Po         | plarity Control b    | <sub>Dit</sub> (1)     |                        |

|               |                       | in polarity is ac                      |                                      |                     |                      |                        |                        |

|               |                       | in polarity is ac                      |                                      |                     |                      |                        |                        |

| bit 3-2       | PSSACE<1:0            | >: PWMx Outp                           | out Pins, OCxA                       | , OCxC and O        | CxE, Shutdowr        | State Control b        | oits                   |

|               | 11 = Pins are         | driven active v                        | vhen a shutdow                       | n event occur       | S                    |                        |                        |

|               |                       |                                        | when a shutdo                        |                     | urs                  |                        |                        |

|               |                       |                                        | n a shutdown e                       |                     |                      |                        | (4)                    |

| bit 1-0       |                       |                                        |                                      |                     |                      | State Control b        | oits <sup>(1)</sup>    |

|               |                       |                                        | vhen a shutdov                       |                     |                      |                        |                        |

|               |                       |                                        | when a shutdo                        |                     |                      |                        |                        |

|               | ux = Pins are         | па пуп-тпре                            | dance state wh                       | ien a shuluowi      | i eveni occurs       |                        |                        |

**Note 1:** These bits are implemented in MCCPx modules only.

| U-0           | R/W-x                                                                       | R/W-x            | R/W-x          | R/W-x                | R/W-x            | R/W-x              | R/W-x   |

|---------------|-----------------------------------------------------------------------------|------------------|----------------|----------------------|------------------|--------------------|---------|

| _             | MINTEN2                                                                     | MINTEN1          | MINTEN0        | MINONE3              | MINONE2          | MINONE1            | MINONE0 |

| bit 15        | -                                                                           |                  |                | -                    |                  |                    | bit 8   |

|               |                                                                             |                  |                |                      |                  |                    |         |

| U-0           | R/W-x                                                                       | R/W-x            | R/W-x          | R/W-x                | R/W-x            | R/W-x              | R/W-x   |

| —             | SECTEN2                                                                     | SECTEN1          | SECTEN0        | SECONE3              | SECONE2          | SECONE1            | SECONE0 |

| bit 7         | -                                                                           |                  |                |                      |                  |                    | bit 0   |

|               |                                                                             |                  |                |                      |                  |                    |         |

| Legend:       |                                                                             |                  |                |                      |                  |                    |         |

| R = Readable  | e bit                                                                       | W = Writable     | bit            | U = Unimplem         | nented bit, read | l as '0'           |         |

| -n = Value at | POR                                                                         | '1' = Bit is set |                | '0' = Bit is cleared |                  | x = Bit is unknown |         |

|               |                                                                             |                  |                |                      |                  |                    |         |

| bit 15        | Unimplement                                                                 | ted: Read as '0  | 3              |                      |                  |                    |         |

| bit 14-12     | MINTEN<2:0                                                                  | >: Binary Code   | d Decimal Valu | ue of Minute's T     | ens Digit bits   |                    |         |

|               | Contains a va                                                               | lue from 0 to 5  |                |                      |                  |                    |         |

| bit 11-8      | MINONE<3:0                                                                  | >: Binary Code   | ed Decimal Val | ue of Minute's (     | Ones Digit bits  |                    |         |

|               | Contains a va                                                               | lue from 0 to 9  |                |                      |                  |                    |         |

| bit 7         | Unimplemen                                                                  | ted: Read as '   | 0'             |                      |                  |                    |         |

| bit 6-4       | t 6-4 SECTEN<2:0>: Binary Coded Decimal Value of Second's Tens Digit bits   |                  |                |                      |                  |                    |         |

|               | Contains a value from 0 to 5.                                               |                  |                |                      |                  |                    |         |

| bit 3-0       | bit 3-0 SECONE<3:0>: Binary Coded Decimal Value of Second's Ones Digit bits |                  |                |                      |                  |                    |         |

|               | Contains a value from 0 to 9.                                               |                  |                |                      |                  |                    |         |

|               |                                                                             |                  |                |                      |                  |                    |         |

#### REGISTER 16-10: ALMINSEC: ALARM MINUTES AND SECONDS VALUE REGISTER

## 23.0 COMPARATOR VOLTAGE REFERENCE

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the Comparator Voltage Reference, refer to the "PIC24F Family Reference Manual", "Comparator Voltage Reference Module" (DS39709).

## 23.1 Configuring the Comparator Voltage Reference

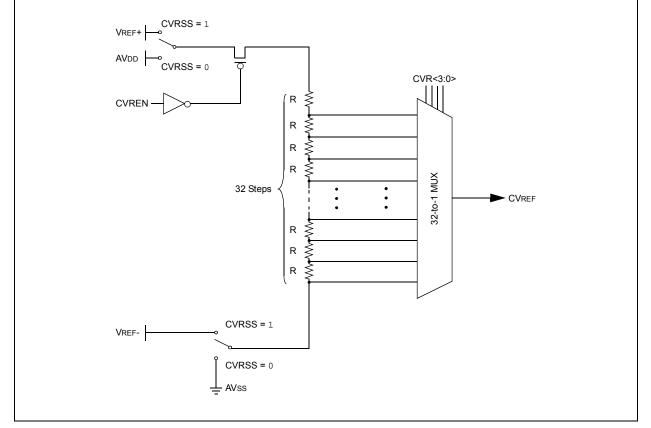

The comparator voltage reference module is controlled through the CVRCON register (Register 23-1). The comparator voltage reference provides a range of output voltages with 32 distinct levels.

The comparator voltage reference supply voltage can come from either VDD and VSS, or the external VREF+ and VREF-. The voltage source is selected by the CVRSS bit (CVRCON<5>).

The settling time of the comparator voltage reference must be considered when changing the CVREF output.

### TABLE 27-1: THERMAL OPERATING CONDITIONS

| Rating                                                                                                                                                                                                                                                                                                                        | Symbol | Min | Тур         | Max  | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|-------------|------|------|

| Operating Junction Temperature Range                                                                                                                                                                                                                                                                                          | TJ     | -40 | _           | +140 | °C   |

| Operating Ambient Temperature Range                                                                                                                                                                                                                                                                                           | TA     | -40 | _           | +125 | °C   |