Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0                |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                     |

| Number of I/O              | 37                                                                             |

| Program Memory Size        | 16KB (5.5K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | 512 x 8                                                                        |

| RAM Size                   | 2K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5V                                                                        |

| Data Converters            | A/D 22x10b/12b; D/A 2x8b                                                       |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

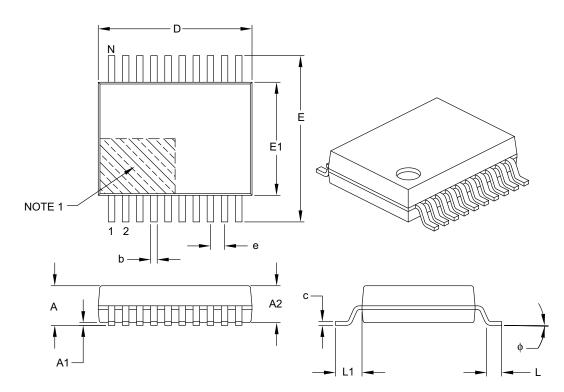

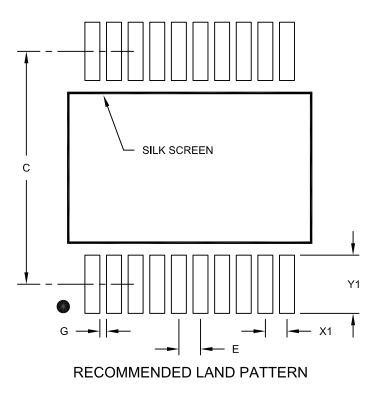

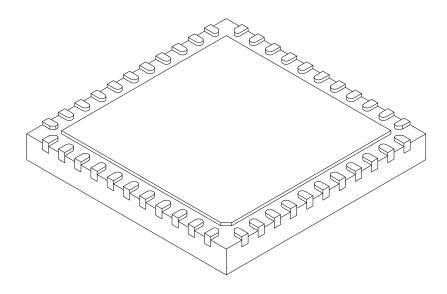

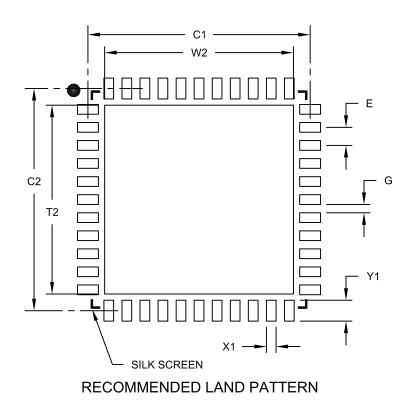

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 48-UFQFN Exposed Pad                                                           |

| Supplier Device Package    | 48-UQFN (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fv16km204t-i-mv |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Pin Diagrams (Continued)**

|          | 28-Pin QFN <sup>(1)</sup>                                                            | 22<br>21 RB13<br>20 RB12                         |

|----------|--------------------------------------------------------------------------------------|--------------------------------------------------|

|          | RB3 4<br>Vss 5<br>RA2 6<br>RA3 7<br><u>8 9 10 11 12 <b>13</b> 1</u>                  | 18 RB10<br>17 RA6 or VDDcore<br>16 RA7<br>15 RB9 |

|          | R 85<br>R 85<br>R 85<br>R 82<br>R 82<br>R 82<br>R 82<br>R 82<br>R 82<br>R 82<br>R 82 | 5<br>0<br>2<br>2                                 |

| Pin      | Pin Features                                                                         | Pin Features                                     |

|          | PIC24FXXKMX02                                                                        | PIC24FVXXKMX02                                   |

| 1        | PGED1/AN2/CTCMP/ULPWU/C1IND/ / / /CN4/I                                              | RB0                                              |

| 2        | PGEC1/ / /AN3/C1INC/ / /CTED12/CN                                                    | I5/RB1                                           |

| 3        | / /AN4/C1INB/ / /U1RX/TCKIB/CTED1                                                    | 13/CN6/RB2                                       |

| 4        | /AN5/C1INA/ / /CN7/RB3                                                               |                                                  |

| 5        | Vss                                                                                  |                                                  |

| 6        | OSCI/CLKI/AN13/CN30/RA2                                                              |                                                  |

| 7        | OSCO/CLKO/AN14/CN29/RA3                                                              |                                                  |

| 8        | SOSCI/AN15/ / /CN1/RB4                                                               |                                                  |

| 9        | SOSCO/SCLKI/AN16/PWRLCLK/ /CN0/RA4                                                   |                                                  |

| 10       |                                                                                      |                                                  |

| 11       | PGED3/AN17/ASDA1/ / /OC1E/CLCINA/CN27/RB5                                            |                                                  |

| 12       | PGEC3/AN18/ASCL1/ / /OC1F/CLCINB/CN24/RB6<br>AN19/U1TX/INT0/CN23/RB7                 | AN19/U1TX/ /OC1A/INT0/CN23/RB7                   |

| 13<br>14 | AN19/0112/IN10/CN23/RB7<br>AN20/SCL1/U1CTS/C3OUT/OC1B/CTED10/CN22/RB8                | AN 19/011X/ /OCTA/IN10/CN23/RB7                  |

| 14       | AN21/SDA1/T1CK/U1RTS/U1BCLK/IC2/ /CLC10/CTED4/CN                                     | 121/PB0                                          |

| 16       | /IC1/ / /CTED3/CN9/RA7                                                               | vz //KD9                                         |

| 17       | /OC1A/CTED1/INT2/CN8/RA6                                                             | VDDCORE/VCAP                                     |

| 18       | PGED2/SDI1/ /OC1C/CTED11/CN16/RB10                                                   |                                                  |

| 19       | PGEC2/SCK1/OC2A/CTED9/CN15/RB11                                                      | <u></u>                                          |

| 20       | /AN12/HLVDIN/ / / /CTED2/CN14/RB12                                                   | /AN12/HLVDIN/SS2/ / /CTED2/INT2/CN14/RB12        |

| 21       | / /AN11/SDO1/OCFB/OC3B/OC1D/CTPLS/CN13                                               | 3/RB13                                           |

| 22       | /CVREF/ / /AN10/ / /C1OUT                                                            | OCFA/CTED5/INT1/CN12/RB14                        |

| 23       | / /AN9/ /REFO/SS1/TCKIA/CTED6/CN                                                     | I11/RB15                                         |

| 24       | Vss                                                                                  |                                                  |

| 25       | Vdd                                                                                  |                                                  |

| 26       | MCLR/Vpp/RA5                                                                         |                                                  |

|          | CVREF+/VREF+/ /AN0/ /CN2/RA0                                                         | CVREF+/VREF+/ /AN0/ /CTED1/CN2/RA0               |

| 27       |                                                                                      |                                                  |

Legend:Values inindicate pin function differences between PIC24F(V)XXKM202 and PIC24F(V)XXKM102 devices.Note 1:Exposed pad on underside of device is connected to Vss.

#### TABLE 1-5: PIC24FV16KM204 FAMILY PINOUT DESCRIPTION (CONTINUED)

| TADLE 1-5. |                                  |                                  | F             |                        |                |                                  | ,                                | FV            | ,                      |                |     |        |                                             |

|------------|----------------------------------|----------------------------------|---------------|------------------------|----------------|----------------------------------|----------------------------------|---------------|------------------------|----------------|-----|--------|---------------------------------------------|

|            |                                  |                                  | Pin Numb      | er                     |                |                                  |                                  | Pin Numb      | er                     |                | -   |        |                                             |

| Function   | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | I/O | Buffer | Description                                 |

| CTED1      | 11                               | 20                               | 17            | 7                      | 7              | 11                               | 2                                | 27            | 19                     | 21             | Ι   | ST     | CTMU Trigger Edge Inputs                    |

| CTED2      | 15                               | 23                               | 20            | 10                     | 11             | 15                               | 23                               | 20            | 10                     | 11             | I   | ST     | CTMU Trigger Edge Inputs                    |

| CTED3      | _                                | 19                               | 16            | 6                      | 6              | _                                | 19                               | 16            | 6                      | 6              | I   | ST     | CTMU Trigger Edge Inputs                    |

| CTED4      | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | I   | ST     | CTMU Trigger Edge Inputs                    |

| CTED5      | 17                               | 25                               | 22            | 14                     | 15             | 17                               | 25                               | 22            | 14                     | 15             | I   | ST     | CTMU Trigger Edge Inputs                    |

| CTED6      | 18                               | 26                               | 23            | 15                     | 16             | 18                               | 26                               | 23            | 15                     | 16             | I   | ST     | CTMU Trigger Edge Inputs                    |

| CTED7      | _                                |                                  | _             | 5                      | 5              |                                  |                                  | _             | 5                      | 5              | I   | ST     | CTMU Trigger Edge Inputs                    |

| CTED8      | —                                |                                  | _             | 13                     | 14             |                                  |                                  | —             | 13                     | 14             | I   | ST     | CTMU Trigger Edge Inputs                    |

| CTED9      | _                                | 22                               | 19            | 9                      | 10             |                                  | 22                               | 19            | 9                      | 10             | I   | ST     | CTMU Trigger Edge Inputs                    |

| CTED10     | 12                               | 17                               | 14            | 44                     | 48             | 12                               | 17                               | 14            | 44                     | 48             | I   | ST     | CTMU Trigger Edge Inputs                    |

| CTED11     | —                                | 21                               | 18            | 8                      | 9              |                                  | 21                               | 18            | 8                      | 9              | I   | ST     | CTMU Trigger Edge Inputs                    |

| CTED12     | 5                                | 5                                | 2             | 22                     | 24             | 5                                | 5                                | 2             | 22                     | 24             | I   | ST     | CTMU Trigger Edge Inputs                    |

| CTED13     | 6                                | 6                                | 3             | 23                     | 25             | 6                                | 6                                | 3             | 23                     | 25             | I   | ST     | CTMU Trigger Edge Inputs                    |

| CTPLS      | 16                               | 24                               | 21            | 11                     | 12             | 16                               | 24                               | 21            | 11                     | 12             | 0   | _      | CTMU Pulse Output                           |

| CVREF      | 17                               | 25                               | 22            | 14                     | 15             | 17                               | 25                               | 22            | 14                     | 15             | 0   | ANA    | Comparator Voltage Reference Output         |

| CVREF+     | 2                                | 2                                | 27            | 19                     | 21             | 2                                | 2                                | 27            | 19                     | 21             | Ι   | ANA    | Comparator Voltage Reference Positive Input |

| CVREF-     | 3                                | 3                                | 28            | 20                     | 22             | 3                                | 3                                | 28            | 20                     | 22             | Ι   | ANA    | Comparator Voltage Reference Negative Input |

| DAC1OUT    | —                                | 23                               | 20            | 10                     | 11             |                                  | 23                               | 20            | 10                     | 11             | 0   | ANA    | DAC1 Output                                 |

| DAC1REF+   | _                                | 2                                | 27            | 19                     | 21             |                                  | 2                                | 27            | 19                     | 21             | I   | ANA    | DAC1 Positive Voltage Reference Input       |

| DAC2OUT    | _                                | 25                               | 22            | 14                     | 15             | _                                | 25                               | 22            | 14                     | 15             | 0   | ANA    | DAC2 Output                                 |

| DAC2REF+   | _                                | 26                               | 23            | 15                     | 16             | _                                | 26                               | 23            | 15                     | 16             | Ι   | ANA    | DAC2 Positive Voltage Reference Input       |

| HLVDIN     | 15                               | 23                               | 20            | 10                     | 11             | 15                               | 23                               | 20            | 10                     | 11             | Ι   | ANA    | External High/Low-Voltage Detect Input      |

| IC1        | 14                               | 19                               | 16            | 6                      | 6              | 11                               | 19                               | 16            | 6                      | 6              | Ι   | ST     | MCCP1 Input Capture Input                   |

| IC2        | 13                               | 18                               | 15            | 1                      | 1              | 13                               | 18                               | 15            | 1                      | 1              | Ι   | ST     | MCCP2 Input Capture Input                   |

| IC3        | _                                | 23                               | 20            | 13                     | 14             | _                                | 23                               | 20            | 13                     | 14             | Ι   | ST     | MCCP3 Input Capture Input                   |

| IC4        | _                                | 14                               | 11            | 5                      | 5              | _                                | 14                               | 11            | 5                      | 5              | I   | ST     | SCCP4 Input Capture Input                   |

| IC5        | _                                | 15                               | 12            | 12                     | 13             |                                  | 15                               | 12            | 12                     | 13             | Ι   | ST     | SCCP5 Input Capture Input                   |

| INT0       | 11                               | 16                               | 13            | 43                     | 47             | 11                               | 16                               | 13            | 43                     | 47             | Ι   | ST     | External Interrupt 0 Input                  |

| INT1       | 17                               | 25                               | 22            | 14                     | 15             | 17                               | 25                               | 22            | 14                     | 15             | Ι   | ST     | External Interrupt 1 Input                  |

| INT2       | 14                               | 20                               | 17            | 7                      | 7              | 15                               | 23                               | 20            | 10                     | 11             | I   | ST     | External Interrupt 2 Input                  |

**Legend:** ANA = Analog level input/output, ST = Schmitt Trigger input buffer,  $I^2C^{TM} = I^2C/SMBus$  input buffer

NOTES:

### 3.0 CPU

| Note: | This data sheet summarizes the features<br>of this group of PIC24F devices. It is not |

|-------|---------------------------------------------------------------------------------------|

|       | intended to be a comprehensive refer-                                                 |

|       | ence source. For more information on the                                              |

|       | CPU, refer to the "PIC24F Family                                                      |

|       | Reference Manual", "CPU" (DS39703).                                                   |

The PIC24F CPU has a 16-bit (data) modified Harvard architecture with an enhanced instruction set and a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M instructions of user program memory space. A single-cycle instruction prefetch mechanism is used to help maintain throughput and provides predictable execution. All instructions execute in a single cycle, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction and the table instructions. Overhead-free program loop constructs are supported using the REPEAT instructions, which are interruptible at any point.

PIC24F devices have sixteen, 16-bit working registers in the programmer's model. Each of the working registers can act as a data, address or address offset register. The 16<sup>th</sup> working register (W15) operates as a Software Stack Pointer (SSP) for interrupts and calls.

The upper 32 Kbytes of the Data Space (DS) memory map can optionally be mapped into program space at any 16K word boundary of either program memory or data EEPROM memory, defined by the 8-bit Program Space Visibility Page Address (PSVPAG) register. The program to Data Space mapping feature lets any instruction access program space as if it were Data Space.

The Instruction Set Architecture (ISA) has been significantly enhanced beyond that of the PIC18, but maintains an acceptable level of backward compatibility. All PIC18 instructions and addressing modes are supported, either directly, or through simple macros. Many of the ISA enhancements have been driven by compiler efficiency needs.

The core supports Inherent (no operand), Relative, Literal, Memory Direct and three groups of addressing modes. All modes support Register Direct and various Register Indirect modes. Each group offers up to seven addressing modes. Instructions are associated with predefined addressing modes depending upon their functional requirements. For most instructions, the core is capable of executing a data (or program data) memory read, a working register (data) read, a data memory write and a program (instruction) memory read per instruction cycle. As a result, three parameter instructions can be supported, allowing trinary operations (i.e., A + B = C) to be executed in a single cycle.

A high-speed, 17-bit by 17-bit multiplier has been included to significantly enhance the core arithmetic capability and throughput. The multiplier supports Signed, Unsigned and Mixed mode, 16-bit by 16-bit or 8-bit by 8-bit integer multiplication. All multiply instructions execute in a single cycle.

The 16-bit ALU has been enhanced with integer divide assist hardware that supports an iterative non-restoring divide algorithm. It operates in conjunction with the REPEAT instruction looping mechanism and a selection of iterative divide instructions to support 32-bit (or 16-bit), divided by 16-bit integer signed and unsigned division. All divide operations require 19 cycles to complete but are interruptible at any cycle boundary.

The PIC24F has a vectored exception scheme with up to eight sources of non-maskable traps and up to 118 interrupt sources. Each interrupt source can be assigned to one of seven priority levels.

A block diagram of the CPU is illustrated in Figure 3-1.

### 3.1 Programmer's Model

Figure 3-2 displays the programmer's model for the PIC24F. All registers in the programmer's model are memory mapped and can be manipulated directly by instructions.

Table 3-1 provides a description of each register. All registers associated with the programmer's model are memory mapped.

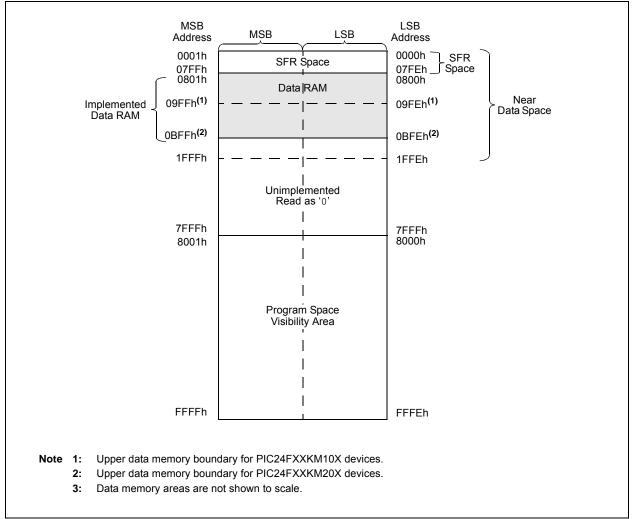

#### 4.2 **Data Address Space**

The PIC24F core has a separate, 16-bit-wide data memory space, addressable as a single linear range. The Data Space is accessed using two Address Generation Units (AGUs), one each for read and write operations. The Data Space memory map is displayed in Figure 4-3.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the Data Space. This gives a Data Space address range of 64 Kbytes or 32K words. The lower half of the data memory space (that is, when EA<15> = 0) is used for implemented memory addresses, while the upper half (EA<15> = 1) is reserved for the Program Space Visibility (PSV) area (see Section 4.3.3 "Reading Data From Program Memory Using Program Space Visibility").

Depending on the particular device, PIC24FV16KM family devices implement either 512 or 1024 words of data memory. Should an EA point to a location outside of this area, an all zero word or byte will be returned.

FIGURE 4-3:

#### 4.2.1 DATA SPACE WIDTH

The data organized memory space is in byte-addressable, 16-bit-wide blocks. Data is aligned in data memory and registers as 16-bit words, but all the Data Space EAs resolve to bytes. The Least Significant Bytes (LSBs) of each word have even addresses, while the Most Significant Bytes (MSBs) have odd addresses.

DATA SPACE MEMORY MAP FOR PIC24FXXXXX FAMILY DEVICES<sup>(3)</sup>

#### TABLE 4-31: CLOCK CONTROL REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7   | Bit 6 | Bit 5  | Bit 4 | Bit 3  | Bit 2   | Bit 1  | Bit 0  | All<br>Resets |

|-----------|-------|--------|--------|--------|--------|--------|--------|--------|--------|---------|-------|--------|-------|--------|---------|--------|--------|---------------|

| RCON      | 740h  | TRAPR  | IOPUWR | SBOREN | RETEN  |        |        | СМ     | PMSLP  | EXTR    | SWR   | SWDTEN | WDTO  | SLEEP  | IDLE    | BOR    | POR    | (Note 1)      |

| OSCCON    | 742h  | _      | COSC2  | COSC1  | COSC0  | _      | NOSC2  | NOSC1  | NOSC0  | CLKLOCK | _     | LOCK   | _     | CF     | SOSCDRV | SOSCEN | OSWEN  | (Note 2)      |

| CLKDIV    | 744h  | ROI    | DOZE2  | DOZE1  | DOZE0  | DOZEN  | RCDIV2 | RCDIV1 | RCDIV0 | _       | _     | _      | _     | _      | _       | _      | _      | 0100          |

| OSCTUN    | 748h  | _      | _      | _      | _      | _      | _      | _      | _      | _       | _     | TUN5   | TUN4  | TUN3   | TUN2    | TUN1   | TUN0   | 0000          |

| REFOCON   | 74Eh  | ROEN   | —      | ROSSLP | ROSEL  | RODIV3 | RODIV2 | RODIV1 | RODIV0 | _       | _     | _      | —     | —      | —       | _      | _      | 0000          |

| HLVDCON   | 756h  | HLVDEN | —      | HLSIDL | _      | _      | —      | _      | _      | VDIR    | BGVST | IRVST  | _     | HLVDL3 | HLVDL2  | HLVDL1 | HLVDL0 | 0000          |

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

Note 1: RCON register Reset values are dependent on the type of Reset.

2: OSCCON register Reset values are dependent on Configuration fuses and by type of Reset.

#### TABLE 4-32: NVM REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-----------|-------|--------|--------|--------|---------|--------|--------|-------|-------|---------|---------|---------|---------|---------|---------|---------|---------|---------------|

| NVMCON    | 760h  | WR     | WREN   | WRERR  | PGMONLY |        |        | _     |       | _       | ERASE   | NVMOP5  | NVMOP4  | NVMOP3  | NVMOP2  | NVMOP1  | NVMOP0  | 0000          |

| NVMKEY    | 766h  | —      |        |        | _       |        | _      |       |       | NVMKEY7 | NVMKEY6 | NVMKEY5 | NVMKEY4 | NVMKEY3 | NVMKEY2 | NVMKEY1 | NVMKEY0 | 0000          |

Legend: x = unknown, u = unchanged, - = unimplemented, q = value depends on condition, r = reserved.

#### TABLE 4-33: ULTRA LOW-POWER WAKE-UP REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|--------|--------|---------|--------|--------|--------|-------|---------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| ULPWCON   | 768h  | ULPEN  |        | ULPSIDL | _      | _      | _      | —     | ULPSINK | —     |       | —     | _     | _     | _     |       |       | 0000          |

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition, r = reserved.

#### TABLE 4-34: PMD REGISTER MAP

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8 | Bit 7  | Bit 6                 | Bit 5                 | Bit 4                 | Bit 3                 | Bit 2                 | Bit 1                 | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|-------|--------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|--------|---------------|

| PMD1         | 770h  | _      | _      |        | _      | T1MD   |        | _      | _     | SSP1MD | U2MD <sup>(1)</sup>   | U1MD                  | _                     | _                     | _                     | _                     | ADCMD  | 0000          |

| PMD2         | 772h  |        | _      |        | _      |        | _      | _      | _     | _      | -                     | _                     | CCP5MD <sup>(1)</sup> | CCP4MD <sup>(1)</sup> | CCP3MD <sup>(1)</sup> | CCP2MD                | CCP1MD | 0000          |

| PMD3         | 774h  |        | _      |        | _      |        | CMPMD  | RTCCMD | _     | _      | DAC1MD <sup>(1)</sup> | _                     | _                     | _                     | _                     | SSP2MD <sup>(1)</sup> | _      | 0000          |

| PMD4         | 776h  |        | _      |        | _      |        | _      | _      | _     | _      | ULPWUMD               | _                     | _                     | REFOMD                | CTMUMD                | HLVDMD                | _      | 0000          |

| PMD6         | 77Ah  |        | _      |        | _      |        | _      | _      | _     | _      | -                     | AMP1MD <sup>(1)</sup> | DAC2MD <sup>(1)</sup> | AMP2MD <sup>(1)</sup> | _                     | _                     | _      | 0000          |

| PMD8         | 77Eh  | _      | _      | —      | _      | _      | -      | _      | _     | _      | _                     | _                     | —                     | CLC2MD <sup>(1)</sup> | CLC1MD                | _                     | _      | 0000          |

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition, r = reserved.

Note 1: These bits are available only on PIC24F(V)16KM2XX devices.

| R/W-0         | R/W-0                                                                                                                     | R/W-0                                          | R/W-0             | R/W-0             | U-0              | U-0             | U-0    |  |  |  |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|-------------------|-------------------|------------------|-----------------|--------|--|--|--|--|--|--|

| U2TXIE        | U2RXIE                                                                                                                    | INT2IE                                         | CCT4IE            | CCT3IE            |                  | _               | _      |  |  |  |  |  |  |

| bit 15        |                                                                                                                           |                                                |                   |                   |                  |                 | bit 8  |  |  |  |  |  |  |

|               | DAMA                                                                                                                      |                                                | <b>D</b> 444 0    | DAVA              | DAMA             | DAMA            | DANO   |  |  |  |  |  |  |

| U-0           | R/W-0                                                                                                                     | U-0                                            | R/W-0             | R/W-0             | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |  |  |

|               | CCP5IE                                                                                                                    | —                                              | INT1IE            | CNIE              | CMIE             | BCL1IE          | SSP1IE |  |  |  |  |  |  |

| bit 7         |                                                                                                                           |                                                |                   |                   |                  |                 | bit    |  |  |  |  |  |  |

| Legend:       |                                                                                                                           |                                                |                   |                   |                  |                 |        |  |  |  |  |  |  |

| R = Readable  | e bit                                                                                                                     | W = Writable                                   | bit               | U = Unimplen      | nented bit, read | d as '0'        |        |  |  |  |  |  |  |

| -n = Value at | POR                                                                                                                       | '1' = Bit is set                               |                   | '0' = Bit is clea | ared             | x = Bit is unkr | nown   |  |  |  |  |  |  |

|               |                                                                                                                           |                                                |                   |                   |                  |                 |        |  |  |  |  |  |  |

| bit 15        | U2TXIE: UA                                                                                                                | RT2 Transmitte                                 | r Interrupt Enat  | ole bit           |                  |                 |        |  |  |  |  |  |  |

|               | 1 = Interrupt                                                                                                             | request is enab                                | led               |                   |                  |                 |        |  |  |  |  |  |  |

|               | 0 = Interrupt                                                                                                             | request is not e                               | enabled           |                   |                  |                 |        |  |  |  |  |  |  |

| bit 14        |                                                                                                                           | RT2 Receiver II                                | •                 | e bit             |                  |                 |        |  |  |  |  |  |  |

|               |                                                                                                                           | request is enab                                |                   |                   |                  |                 |        |  |  |  |  |  |  |

| L:1 10        | -                                                                                                                         | request is not e                               |                   |                   |                  |                 |        |  |  |  |  |  |  |

| bit 13        |                                                                                                                           | rnal Interrupt 2<br>request is enab            |                   |                   |                  |                 |        |  |  |  |  |  |  |

|               |                                                                                                                           | request is enabled                             |                   |                   |                  |                 |        |  |  |  |  |  |  |

| bit 12        | •                                                                                                                         | oture/Compare                                  |                   | pt Enable bit     |                  |                 |        |  |  |  |  |  |  |

|               | •                                                                                                                         | request is enab                                |                   |                   |                  |                 |        |  |  |  |  |  |  |

|               | 0 = Interrupt                                                                                                             | request is not e                               | enabled           |                   |                  |                 |        |  |  |  |  |  |  |

| bit 11        | CCT3IE: Cap                                                                                                               | oture/Compare                                  | 3 Timer Interru   | pt Enable bit     |                  |                 |        |  |  |  |  |  |  |

|               |                                                                                                                           | request is enab<br>request is not e            |                   |                   |                  |                 |        |  |  |  |  |  |  |

| bit 10-7      | Unimplemer                                                                                                                | nted: Read as '                                | 0'                |                   |                  |                 |        |  |  |  |  |  |  |

| bit 6         | CCP5IE: Cap                                                                                                               | oture/Compare                                  | 5 Event Interru   | pt Enable bit     |                  |                 |        |  |  |  |  |  |  |

|               | •                                                                                                                         | request is enab<br>request is not e            |                   |                   |                  |                 |        |  |  |  |  |  |  |

| bit 5         | Unimplemer                                                                                                                | nted: Read as '                                | 0'                |                   |                  |                 |        |  |  |  |  |  |  |

| bit 4         | INT1IE: Exte                                                                                                              | rnal Interrupt 1                               | Enable bit        |                   |                  |                 |        |  |  |  |  |  |  |

|               |                                                                                                                           | request is enab<br>request is not e            |                   |                   |                  |                 |        |  |  |  |  |  |  |

| bit 3         | CNIE: Input (                                                                                                             | Change Notifica                                | ation Interrupt E | Enable bit        |                  |                 |        |  |  |  |  |  |  |

|               | 1 = Interrupt                                                                                                             | request is enab                                | led               |                   |                  |                 |        |  |  |  |  |  |  |

| bit 2         | •                                                                                                                         | arator Interrupt                               |                   |                   |                  |                 |        |  |  |  |  |  |  |

|               | 1 = Interrupt                                                                                                             | request is enab<br>request is not e            | led               |                   |                  |                 |        |  |  |  |  |  |  |

| bit 1         |                                                                                                                           | SP1 I <sup>2</sup> C™ Bus                      |                   | unt Enable bit    |                  |                 |        |  |  |  |  |  |  |

|               |                                                                                                                           | request is enab                                |                   | טאנ בוומטוכ טונ   |                  |                 |        |  |  |  |  |  |  |

|               |                                                                                                                           |                                                |                   |                   |                  |                 |        |  |  |  |  |  |  |

|               | •                                                                                                                         |                                                |                   |                   |                  |                 |        |  |  |  |  |  |  |

| bit 0         | <ul> <li>Interrupt request is not enabled</li> <li>SSP1IE: MSSP1 SPI/I<sup>2</sup>C Event Interrupt Enable bit</li> </ul> |                                                |                   |                   |                  |                 |        |  |  |  |  |  |  |

| bit 0         |                                                                                                                           | SP1 SPI/I <sup>2</sup> C Ev<br>request is enab | •                 | nable bit         |                  |                 |        |  |  |  |  |  |  |

NOTES:

NOTES:

#### 19.1 A/D Control Registers

The 12-bit A/D Converter module uses up to 43 registers for its operation. All registers are mapped in the data memory space.

#### 19.1.1 CONTROL REGISTERS

Depending on the specific device, the module has up to eleven control and status registers:

- AD1CON1: A/D Control Register 1

- AD1CON2: A/D Control Register 2

- AD1CON3: A/D Control Register 3

- AD1CON5: A/D Control Register 5

- AD1CHS: A/D Sample Select Register

- AD1CHITH and AD1CHITL: A/D Scan Compare Hit Registers

- AD1CSSH and AD1CSSL: A/D Input Scan Select Registers

- AD1CTMENH and AD1CTMENL: CTMU Enable Registers

The AD1CON1, AD1CON2 and AD1CON3 registers (Register 19-1, Register 19-2 and Register 19-3) control the overall operation of the A/D module. This includes enabling the module, configuring the conversion clock and voltage reference sources, selecting the sampling and conversion Triggers, and manually controlling the sample/convert sequences. The AD1CON5 register (Register 19-4) specifically controls features of the Threshold Detect operation, including its function in power-saving modes.

The AD1CHS register (Register 19-5) selects the input channels to be connected to the S/H amplifier. It also allows the choice of input multiplexers and the selection of a reference source for differential sampling.

The AD1CHITH and AD1CHITL registers (Register 19-6 and Register 19-7) are semaphore registers used with Threshold Detect operations. The status of individual bits, or bit pairs in some cases, indicates if a match condition has occurred. AD1CHITL is always implemented, whereas AD1CHITH may not be implemented in devices with 16 or fewer channels.

The AD1CSSH/L registers (Register 19-8 and Register 19-9) select the channels to be included for sequential scanning.

The AD1CTMENH/L registers (Register 19-10 and Register 19-11) select the channel(s) to be used by the CTMU during conversions. Selecting a particular channel allows the A/D Converter to control the CTMU (particularly, its current source) and read its data through that channel. AD1CTMENL is always implemented, whereas AD1CTMENH may not be implemented in devices with 16 or fewer channels.

#### 19.1.2 A/D RESULT BUFFERS

The module incorporates a multi-word, dual port buffer, called ADC1BUFx. Each of the locations is mapped into the data memory space and is separately addressable. The buffer locations are referred to as ADC1BUF0 through ADC1BUFx (x = up to 17).

The A/D result buffers are both readable and writable. When the module is active (AD1CON<15> = 1), the buffers are read-only and store the results of A/D conversions. When the module is inactive (AD1CON<15> = 0), the buffers are both readable and writable. In this state, writing to a buffer location programs a conversion threshold for Threshold Detect operations.

Buffer contents are not cleared when the module is deactivated with the ADON bit (AD1CON1<15>). Conversion results and any programmed threshold values are maintained when ADON is set or cleared.

| R/W-0              | R/W-0                                                                                  | R/W-0                                                | U-0                 | R/W-0                                   | R/W-0           | U-0                 | U-0        |

|--------------------|----------------------------------------------------------------------------------------|------------------------------------------------------|---------------------|-----------------------------------------|-----------------|---------------------|------------|

| PVCFG              | 1 PVCFG0                                                                               | NVCFG0                                               | —                   | BUFREGEN                                | CSCNA           | —                   | —          |

| oit 15             |                                                                                        |                                                      |                     |                                         |                 |                     | bit        |

| R/W-0              | R/W-0                                                                                  | R/W-0                                                | R/W-0               | R/W-0                                   | R/W-0           | R/W-0               | R/W-0      |

| BUFS <sup>(1</sup> | ) SMPI4                                                                                | SMPI3                                                | SMPI2               | SMPI1                                   | SMPI0           | BUFM <sup>(1)</sup> | ALTS       |

| oit 7              |                                                                                        | · · · · · ·                                          |                     | · ·                                     |                 |                     | bit        |

| egend:             |                                                                                        |                                                      |                     |                                         |                 |                     |            |

| R = Reada          | able bit                                                                               | W = Writable b                                       | bit                 | U = Unimplem                            | ented bit, read | d as '0'            |            |

| n = Value          | at POR                                                                                 | '1' = Bit is set                                     |                     | '0' = Bit is clea                       | red             | x = Bit is unkno    | own        |

| bit 15-14          | <b>PVCFG&lt;1:0</b> ><br>11 = 4 * Inter<br>10 = 2 * Inter<br>01 = Externa<br>00 = AVDD | rnal V <sub>BG</sub> (2)<br>rnal V <sub>BG</sub> (3) | r Positive Vol      | age Reference C                         | Configuration I | bits                |            |

| bit 13             | <b>NVCFG0:</b> A/I<br>1 = External<br>0 = AVss                                         |                                                      | gative Voltage      | e Reference Cont                        | figuration bits |                     |            |

| oit 12             | Unimplemen                                                                             | ted: Read as '0                                      | ,                   |                                         |                 |                     |            |

| oit 11             | BUFREGEN:                                                                              | A/D Buffer Reg                                       | ister Enable        | bit                                     |                 |                     |            |

|                    | 1 = Conversi                                                                           | -                                                    | led into a buf      | er location deter                       | mined by the    | converted chanr     | nel        |

| oit 10             |                                                                                        |                                                      |                     | S/H Input for MU                        | X A Settina bi  | t                   |            |

|                    | 1 = Scans in<br>0 = Does no                                                            | puts                                                 |                     |                                         |                 |                     |            |

| oit 9-8            | Unimplemen                                                                             | ted: Read as '0                                      | ,                   |                                         |                 |                     |            |

| oit 7              | BUFS: A/D B                                                                            | uffer Fill Status                                    | bit <sup>(1)</sup>  |                                         |                 |                     |            |

|                    |                                                                                        | • • •                                                |                     | er; user should ad<br>r; user should ad |                 |                     |            |

| oit 6-2            |                                                                                        | Interrupt Sample                                     |                     |                                         |                 |                     |            |

|                    |                                                                                        | •                                                    |                     | e conversion for<br>e conversion for    |                 |                     |            |

|                    | 00000 = Inte                                                                           | errupts at the co                                    | mpletion of th      | e conversion for<br>e conversion for    |                 | ample               |            |

| bit 1              | 1 = Starts fill<br>interrupt<br>0 = Starts fil                                         | (Split Buffer mo                                     | address, ADC<br>de) | C1BUF0, on the fi                       | •               |                     |            |

| oit O              |                                                                                        | ate Input Sampl                                      | e Mode Seler        | rt bit                                  |                 |                     |            |

|                    | 1 = Uses cha                                                                           |                                                      | cts for Sample      | e A on the first sa                     | ample and Sa    | mple B on the n     | ext sample |

| Note 1:<br>2:      | This is only applied<br>used when BUFM<br>PIC24FV16KMX<br>Reference setting            | /I = 1.<br>XX devices only                           | . Reference s       | etting will not be                      | within specific | ·                   |            |

| R/W-0         | U-0               | R/W-0                                | R/W-0          | U-0               | U-0              | U-0             | U-0     |

|---------------|-------------------|--------------------------------------|----------------|-------------------|------------------|-----------------|---------|

| AMPEN         |                   | AMPSIDL                              | AMPSLP         |                   |                  |                 |         |

| bit 15        |                   |                                      | •              |                   |                  |                 | bit 8   |

|               |                   |                                      |                |                   |                  |                 |         |

| R/W-0         | U-0               | R/W-0                                | R/W-0          | R/W-0             | R/W-0            | R/W-0           | R/W-0   |

| SPDSEL        | —                 | NINSEL2                              | NINSEL1        | NINSEL0           | PINSEL2          | PINSEL1         | PINSEL0 |

| bit 7         |                   |                                      |                |                   |                  |                 | bit 0   |

| Legend:       |                   |                                      |                |                   |                  |                 |         |

| R = Readabl   | e bit             | W = Writable                         | bit            | U = Unimplen      | nented bit, read | 1 as '0'        |         |

| -n = Value at | POR               | '1' = Bit is set                     |                | '0' = Bit is clea |                  | x = Bit is unkr | nown    |

|               |                   |                                      |                |                   |                  |                 | -       |

| bit 15        | AMPEN: Op         | Amp x Control                        | Module Enable  | e bit             |                  |                 |         |

|               | 1 = Module        |                                      |                |                   |                  |                 |         |

|               | 0 = Module        |                                      |                |                   |                  |                 |         |

| bit 14        | -                 | nted: Read as '                      |                |                   |                  |                 |         |

| bit 13        |                   | Dp Amp x Periph                      |                |                   |                  |                 |         |

|               |                   | nues module op<br>es module opera    |                |                   | le mode          |                 |         |

| bit 12        |                   | p Amp x Periph                       |                |                   | it               |                 |         |

|               |                   | es module opera                      |                | -                 |                  |                 |         |

|               |                   | nues module op                       |                |                   | pinouo           |                 |         |

| bit 11-8      | Unimpleme         | nted: Read as '                      | כי             |                   |                  |                 |         |

| bit 7         | SPDSEL: Op        | p Amp x Power/                       | Speed Select b | bit               |                  |                 |         |

|               | • •               | ower and band                        | •              | • •               |                  |                 |         |

| bit 6         | -                 | ower and bandw                       | -              | sponse (me)       |                  |                 |         |

| bit 5-3       | -                 | nted: Read as '                      |                | oot hito          |                  |                 |         |

| DIL D-D       |                   | I>: Negative Op<br>rved; do not use  |                | eci biis          |                  |                 |         |

|               |                   | rved; do not use                     |                |                   |                  |                 |         |

|               |                   | np negative inpu                     |                | to the op amp     | output (voltage  | e follower)     |         |

|               |                   | rved; do not use                     |                |                   |                  |                 |         |

|               |                   | rved; do not use<br>np negative inpu |                | to the OAVING     | nin              |                 |         |

|               |                   | np negative inpl                     |                |                   |                  |                 |         |

|               |                   | np negative inpu                     |                |                   |                  |                 |         |

| bit 2-0       | PINSEL<2:0        | >: Positive Op /                     | Amp Input Sele | ect bits          |                  |                 |         |

|               | -                 | np positive inpu                     |                | to the output of  | the A/D input i  | multiplexer     |         |

|               |                   | rved; do not use                     |                | to the DAC1 of    | tout for OA1 /   |                 |         |

|               |                   | np positive inpu<br>rved; do not use |                |                   |                  |                 | i (JAZ) |

|               |                   | rved; do not use                     |                |                   |                  |                 |         |

|               |                   | np positive inpu                     |                |                   |                  |                 |         |

|               | •                 | np positive inpu                     |                |                   | pin              |                 |         |

|               | 000 = Op an       | np positive inpu                     | i is connected | IU AVSS           |                  |                 |         |

| Note 1: The   | nis register is a | vailable only on                     | PIC24F(V)16    | KM2XX devices     |                  |                 |         |

|               |                   |                                      |                |                   |                  |                 |         |

### REGISTER 21-1: AMPxCON: OP AMP x CONTROL REGISTER<sup>(1)</sup>

#### REGISTER 24-3: CTMUCON2L: CTMU CONTROL 2 LOW REGISTER

| U-0          | U-0                                                              | U-0                               | U-0              | U-0              | U-0          | U-0               | U-0         |

|--------------|------------------------------------------------------------------|-----------------------------------|------------------|------------------|--------------|-------------------|-------------|

| _            | —                                                                | —                                 | —                | —                | —            | —                 | —           |

| bit 15       |                                                                  |                                   |                  |                  |              |                   | bit 8       |

|              |                                                                  |                                   |                  |                  |              |                   |             |

| U-0          | U-0                                                              | U-0                               | R/W-0            | U-0              | R/W-0        | R/W-0             | R/W-0       |

|              | —                                                                | —                                 | IRSTEN           | —                | DISCHS2      | DISCHS1           | DISCHS0     |

| bit 7        |                                                                  |                                   |                  |                  |              |                   | bit 0       |

|              |                                                                  |                                   |                  |                  |              |                   |             |

| Legend:      |                                                                  |                                   |                  |                  |              |                   |             |

| R = Readab   | Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                                   |                  |                  |              |                   |             |

| -n = Value a | at POR                                                           | '1' = Bit is set                  |                  | '0' = Bit is cle | ared         | x = Bit is unkn   | own         |

|              |                                                                  |                                   |                  |                  |              |                   |             |

| bit 15-5     | Unimplement                                                      | ted: Read as '                    | 0'               |                  |              |                   |             |

| bit 4        | IRSTEN: CTM                                                      | IU Current Sou                    | urce Reset Ena   | able bit         |              |                   |             |

|              | detect log                                                       | gic                               |                  |                  | SSEN control | bit will reset th | e CTMU edge |

|              |                                                                  |                                   | c will not occur |                  |              |                   |             |

| bit 3        | Unimplement                                                      | ted: Read as '                    | 0'               |                  |              |                   |             |

| bit 2-0      | DISCHS<2:0>                                                      | Discharge S                       | ource Select bi  | its              |              |                   |             |

|              | 111 <b>= CLC2</b> c                                              |                                   |                  |                  |              |                   |             |

|              | 110 = CLC1 c                                                     |                                   |                  |                  |              |                   |             |

|              |                                                                  | ed; do not use<br>d of conversior |                  |                  |              |                   |             |

|              |                                                                  | 5 auxiliary outp                  | -                |                  |              |                   |             |

- 110 = MCCP2 auxiliary output 001 = MCCP1 auxiliary output

- 000 = No discharge source selected, use the IDISSEN bit

#### REGISTER 25-4: FOSC: OSCILLATOR CONFIGURATION REGISTER

| R/P-1  | R/P-1  | R/P-1   | R/P-1     | R/P-1     | R/P-1    | R/P-1   | R/P-1   |

|--------|--------|---------|-----------|-----------|----------|---------|---------|

| FCKSM1 | FCKSM0 | SOSCSEL | POSCFREQ1 | POSCFREQ0 | OSCIOFNC | POSCMD1 | POSCMD0 |

| bit 7  |        |         |           |           |          |         | bit 0   |

| Legend:           |                      |                            |                    |

|-------------------|----------------------|----------------------------|--------------------|

| R = Readable bit  | P = Programmable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared       | x = Bit is unknown |

| bit 7-6 | <b>FCKSM&lt;1:0&gt;:</b> Clock Switching and Fail-Safe Clock Monitor Selection Configuration bits<br>1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled<br>01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled<br>00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled                                            |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5   | <b>SOSCSEL:</b> Secondary Oscillator Power Selection Configuration bit<br>1 = Secondary Oscillator is configured for high-power operation<br>0 = Secondary Oscillator is configured for low-power operation                                                                                                                                                          |

| bit 4-3 | <b>POSCFREQ&lt;1:0&gt;:</b> Primary Oscillator Frequency Range Configuration bits<br>11 = Primary Oscillator/External Clock input frequency is greater than 8 MHz<br>10 = Primary Oscillator/External Clock input frequency is between 100 kHz and 8 MHz<br>01 = Primary Oscillator/External Clock input frequency is less than 100 kHz<br>00 = Reserved; do not use |

| bit 2   | <ul> <li>OSCIOFNC: CLKO Enable Configuration bit</li> <li>1 = CLKO output signal is active on the OSCO pin; Primary Oscillator must be disabled or configured for the External Clock (EC) mode for the CLKO to be active (POSCMD&lt;1:0&gt; = 11 or 00)</li> <li>0 = CLKO output is disabled</li> </ul>                                                              |

| bit 1-0 | POSCMD<1:0>: Primary Oscillator Configuration bits<br>11 = Primary Oscillator mode is disabled<br>10 = HS Oscillator mode is selected<br>01 = XT Oscillator mode is selected                                                                                                                                                                                         |

00 = External Clock mode is selected

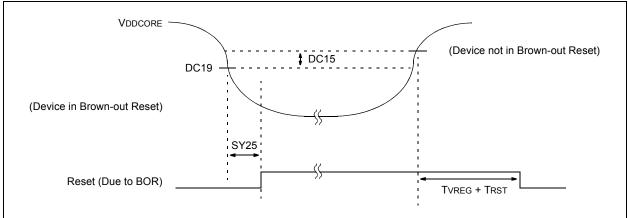

#### FIGURE 27-9: BROWN-OUT RESET CHARACTERISTICS

### TABLE 27-25:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER<br/>AND BROWN-OUT RESET TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                                                |      | rd Operating temp  | -    | ditions: 1.8V to 3.6V (PIC24F16KM204)<br>2.0V to 5.5V (PIC24FV16KM204)<br>$-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                                 |  |

|--------------------|--------|----------------------------------------------------------------|------|--------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--|

| Param<br>No.       | Symbol | Characteristic                                                 | Min. | Typ <sup>(1)</sup> | Max. | Units                                                                                                                                                                                   | Conditions                      |  |

| SY10               | TmcL   | MCLR Pulse Width (low)                                         | 2    | —                  | _    | μs                                                                                                                                                                                      |                                 |  |

| SY11               | TPWRT  | Power-up Timer Period                                          | 50   | 64                 | 90   | ms                                                                                                                                                                                      |                                 |  |

| SY12               | TPOR   | Power-on Reset Delay                                           | 1    | 5                  | 10   | μS                                                                                                                                                                                      |                                 |  |

| SY13               | Tioz   | I/O High-Impedance from<br>MCLR Low or Watchdog<br>Timer Reset | _    | —                  | 100  | ns                                                                                                                                                                                      |                                 |  |

| SY20               | TWDT   | Watchdog Timer Time-out                                        | 0.85 | 1.0                | 1.15 | ms                                                                                                                                                                                      | 1.32 prescaler                  |  |

|                    |        | Period                                                         | 3.4  | 4.0                | 4.6  | ms                                                                                                                                                                                      | 1:128 prescaler                 |  |

| SY25               | TBOR   | Brown-out Reset Pulse<br>Width                                 | 1    | —                  | —    | μS                                                                                                                                                                                      |                                 |  |

| SY35               | TFSCM  | Fail-Safe Clock Monitor<br>Delay                               | —    | 2.0                | 2.3  | μS                                                                                                                                                                                      |                                 |  |

| SY45               | TRST   | Internal State Reset Time                                      | —    | 5                  | _    | μS                                                                                                                                                                                      |                                 |  |

| SY50               | Tvreg  | On-Chip Voltage Regulator<br>Output Delay                      | —    | 10                 | _    | μS                                                                                                                                                                                      | (Note 2)                        |  |

| SY55               | TLOCK  | PLL Start-up Time                                              | _    | 100                |      | μs                                                                                                                                                                                      |                                 |  |

| SY65               | Tost   | Oscillator Start-up Time                                       | —    | 1024               | _    | Tosc                                                                                                                                                                                    |                                 |  |

| SY71               | Трм    | Program Memory Wake-up<br>Time                                 | —    | 1                  | _    | μS                                                                                                                                                                                      | Sleep wake-up with<br>PMSLP = 0 |  |

| SY72               | Tlvr   | Low-Voltage Regulator<br>Wake-up Time                          | —    | 250                | _    | μS                                                                                                                                                                                      |                                 |  |

Note 1: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

2: This applies to PIC24FV16KMXXX devices only.

| Param<br>No. | Symbol | Characteristic                                         | Min | Тур | Max | Units | Comments |

|--------------|--------|--------------------------------------------------------|-----|-----|-----|-------|----------|

| 300          | TRESP  | Response Time <sup>*(1)</sup>                          | _   | 150 | 400 | ns    |          |

| 301          | Тмс2о∨ | Comparator Mode Change to<br>Output Valid <sup>*</sup> | —   | —   | 10  | μs    |          |

#### TABLE 27-26: COMPARATOR TIMING REQUIREMENTS

Parameters are characterized but not tested.

\*

**Note 1:** Response time is measured with one comparator input at (VDD – 1.5)/2, while the other input transitions from Vss to VDD.

#### TABLE 27-27: COMPARATOR VOLTAGE REFERENCE SETTLING TIME SPECIFICATIONS

| Param<br>No. | Symbol | Characteristic               | Min | Тур | Max | Units | Comments |

|--------------|--------|------------------------------|-----|-----|-----|-------|----------|

| VR310        | TSET   | Settling Time <sup>(1)</sup> |     |     | 10  | μS    |          |

Note 1: Settling time is measured while CVRSS = 1 and the CVR<3:0> bits transition from '0000' to '1111'.

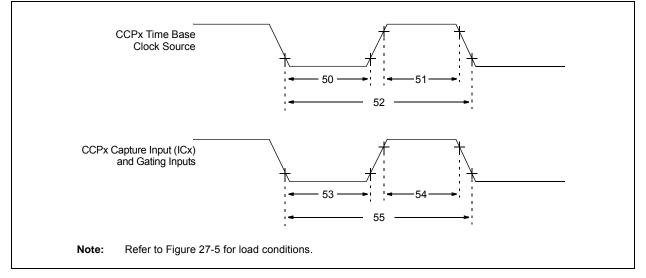

#### FIGURE 27-10: CAPTURE/COMPARE/PWM TIMINGS (MCCPx, SCCPx MODULES)

#### TABLE 27-28: CAPTURE/COMPARE/PWM REQUIREMENTS (MCCPx, SCCPx MODULES)

| Param<br>No. | Symbol | Characteristic                         | Min        | Max | Units | Conditions                         |

|--------------|--------|----------------------------------------|------------|-----|-------|------------------------------------|

| 50           | TCLKL  | CCPx Time Base Clock Source Low Time   | TCY/2      | _   | ns    |                                    |

| 51           | ТсікН  | CCPx Time Base Clock Source High Time  | Tcy/2      | _   | ns    |                                    |

| 52           | TCLK   | CCPx Time Base Clock Source Period     | Тсү        | -   | ns    |                                    |

| 53           | TccL   | CCPx Capture or Gating Input Low Time  | TCLK       | —   | ns    |                                    |

| 54           | ТссН   | CCPx Capture or Gating Input High Time | TCLK       | _   | ns    |                                    |

| 55           | TCCP   | CCPx Capture or Gating Input Period    | 2 * Tclk/N | —   | ns    | N = Prescale<br>Value (1, 4 or 16) |