Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Not For New Designs                                                              |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | C166SV2                                                                          |

| Core Size                  | 16/32-Bit                                                                        |

| Speed                      | 66MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI             |

| Peripherals                | I <sup>2</sup> S, POR, PWM, WDT                                                  |

| Number of I/O              | 75                                                                               |

| Program Memory Size        | 768KB (768K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 51K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                        |

| Data Converters            | A/D 16x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-LQFP Exposed Pad                                                             |

| Supplier Device Package    | PG-LQFP-100-3                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc2766x96f66lackxuma1 |

|                            |                                                                                  |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **General Device Information**

# 2 General Device Information

The XC2766X derivatives are high-performance members of the Infineon XC2000 Family of full-feature single-chip CMOS microcontrollers. These devices extend the functionality and performance of the C166 Family in terms of instructions (MAC unit), peripherals, and speed. They combine high CPU performance (up to 80 million instructions per second) with extended peripheral functionality and enhanced IO capabilities. Optimized peripherals can be adapted flexibly to meet the application requirements. These derivatives utilize clock generation via PLL and internal or external clock sources. On-chip memory modules include program Flash, program RAM, and data RAM.

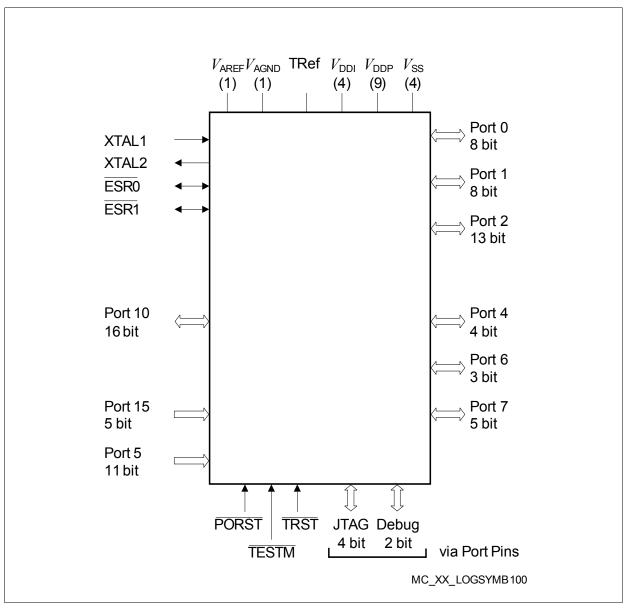

Figure 1 Logic Symbol

### **General Device Information**

| Table 4Pin Definitions and Functions (cont'd) |                  |        |      |                                                |  |  |  |

|-----------------------------------------------|------------------|--------|------|------------------------------------------------|--|--|--|

| Pin                                           | Symbol           | Ctrl.  | Туре | Function                                       |  |  |  |

| 58                                            | P0.2             | O0 / I | St/B | Bit 2 of Port 0, General Purpose Input/Output  |  |  |  |

|                                               | U1C0_<br>SCLKOUT | 01     | St/B | USIC1 Channel 0 Shift Clock Output             |  |  |  |

|                                               | TxDC0            | 02     | St/B | CAN Node 0 Transmit Data Output                |  |  |  |

|                                               | CCU61_<br>CC62   | O3 / I | St/B | CCU61 Channel 2 Input/Output                   |  |  |  |

|                                               | A2               | OH     | St/B | External Bus Interface Address Line 2          |  |  |  |

|                                               | U1C0_DX1B        | I      | St/B | USIC1 Channel 0 Shift Clock Input              |  |  |  |

| 59                                            | P10.0            | 00 / 1 | St/B | Bit 0 of Port 10, General Purpose Input/Output |  |  |  |

|                                               | U0C1_DOUT        | 01     | St/B | USIC0 Channel 1 Shift Data Output              |  |  |  |

|                                               | CCU60_<br>CC60   | O2 / I | St/B | CCU60 Channel 0 Input/Output                   |  |  |  |

|                                               | AD0              | OH/I   | St/B | External Bus Interface Address/Data Line 0     |  |  |  |

|                                               | ESR1_2           | I      | St/B | ESR1 Trigger Input 2                           |  |  |  |

|                                               | U0C0_DX0A        | I      | St/B | USIC0 Channel 0 Shift Data Input               |  |  |  |

|                                               | U0C1_DX0A        | I      | St/B | USIC0 Channel 1 Shift Data Input               |  |  |  |

| 60                                            | P10.1            | 00 / 1 | St/B | Bit 1 of Port 10, General Purpose Input/Output |  |  |  |

|                                               | U0C0_DOUT        | 01     | St/B | USIC0 Channel 0 Shift Data Output              |  |  |  |

|                                               | CCU60_<br>CC61   | O2 / I | St/B | CCU60 Channel 1 Input/Output                   |  |  |  |

|                                               | AD1              | OH/I   | St/B | External Bus Interface Address/Data Line 1     |  |  |  |

|                                               | U0C0_DX0B        | I      | St/B | USIC0 Channel 0 Shift Data Input               |  |  |  |

|                                               | U0C0_DX1A        | I      | St/B | USIC0 Channel 0 Shift Clock Input              |  |  |  |

### **General Device Information**

| Table 4Pin Definitions and Functions (cont'd) |                  |        |      |                                                                                                                                                                                                                                                                                                                                          |  |  |

|-----------------------------------------------|------------------|--------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin                                           | Symbol           | Ctrl.  | Туре | Function                                                                                                                                                                                                                                                                                                                                 |  |  |

| 93                                            | P1.6             | O0 / I | St/B | Bit 6 of Port 1, General Purpose Input/Output                                                                                                                                                                                                                                                                                            |  |  |

|                                               | CCU62_<br>CC61   | 01/1   | St/B | CCU62 Channel 1 Input/Output                                                                                                                                                                                                                                                                                                             |  |  |

|                                               | U1C1_<br>SELO2   | O2     | St/B | USIC1 Channel 1 Select/Control 2 Output                                                                                                                                                                                                                                                                                                  |  |  |

|                                               | U2C0_DOUT        | O3     | St/B | USIC2 Channel 0 Shift Data Output                                                                                                                                                                                                                                                                                                        |  |  |

|                                               | A14              | OH     | St/B | External Bus Interface Address Line 14                                                                                                                                                                                                                                                                                                   |  |  |

|                                               | U2C0_DX0D        | I      | St/B | USIC2 Channel 0 Shift Data Input                                                                                                                                                                                                                                                                                                         |  |  |

| 94                                            | P1.7             | O0 / I | St/B | Bit 7 of Port 1, General Purpose Input/Output                                                                                                                                                                                                                                                                                            |  |  |

|                                               | CCU62_<br>CC60   | 01/1   | St/B | CCU62 Channel 0 Input/Output                                                                                                                                                                                                                                                                                                             |  |  |

|                                               | U1C1_<br>MCLKOUT | O2     | St/B | USIC1 Channel 1 Master Clock Output                                                                                                                                                                                                                                                                                                      |  |  |

|                                               | U2C0_<br>SCLKOUT | O3     | St/B | USIC2 Channel 0 Shift Clock Output                                                                                                                                                                                                                                                                                                       |  |  |

|                                               | A15              | OH     | St/B | External Bus Interface Address Line 15                                                                                                                                                                                                                                                                                                   |  |  |

|                                               | U2C0_DX1C        | 1      | St/B | USIC2 Channel 0 Shift Clock Input                                                                                                                                                                                                                                                                                                        |  |  |

| 95                                            | XTAL2            | 0      | Sp/1 | Crystal Oscillator Amplifier Output                                                                                                                                                                                                                                                                                                      |  |  |

| 96                                            | XTAL1            | I      | Sp/1 | <b>Crystal Oscillator Amplifier Input</b><br>To clock the device from an external source, drive<br>XTAL1, while leaving XTAL2 unconnected.<br>Voltages on XTAL1 must comply to the core<br>supply voltage $V_{\text{DDI1}}$ .                                                                                                            |  |  |

| 97                                            | PORST            | 1      | In/B | Power On Reset Input<br>A low level at this pin resets the XC2766X<br>completely. A spike filter suppresses input pulses<br><10 ns. Input pulses >100 ns safely pass the filter.<br>The minimum duration for a safe recognition<br>should be 120 ns.<br>An internal pullup device will hold this pin high<br>when nothing is driving it. |  |  |

This common memory space consists of 16 Mbytes organized as 256 segments of 64 Kbytes; each segment contains four data pages of 16 Kbytes. The entire memory space can be accessed bytewise or wordwise. Portions of the on-chip DPRAM and the register spaces (ESFR/SFR) additionally are directly bit addressable.

The internal data memory areas and the Special Function Register areas (SFR and ESFR) are mapped into segment 0, the system segment.

The Program Management Unit (PMU) handles all code fetches and, therefore, controls access to the program memories such as Flash memory and PSRAM.

The Data Management Unit (DMU) handles all data transfers and, therefore, controls access to the DSRAM and the on-chip peripherals.

Both units (PMU and DMU) are connected to the high-speed system bus so that they can exchange data. This is required if operands are read from program memory, code or data is written to the PSRAM, code is fetched from external memory, or data is read from or written to external resources. These include peripherals on the LXBus such as USIC or MultiCAN. The system bus allows concurrent two-way communication for maximum transfer performance.

**32 Kbytes of on-chip Program SRAM (PSRAM)** are provided to store user code or data. The PSRAM is accessed via the PMU and is optimized for code fetches. A section of the PSRAM with programmable size can be write-protected.

**16 Kbytes of on-chip Data SRAM (DSRAM)** are used for storage of general user data. The DSRAM is accessed via a separate interface and is optimized for data access.

**2 Kbytes of on-chip Dual-Port RAM (DPRAM)** provide storage for user-defined variables, for the system stack, and for general purpose register banks. A register bank can consist of up to 16 word-wide (R0 to R15) and/or byte-wide (RL0, RH0, ..., RL7, RH7) General Purpose Registers (GPRs).

The upper 256 bytes of the DPRAM are directly bit addressable. When used by a GPR, any location in the DPRAM is bit addressable.

**1 Kbyte of on-chip Stand-By SRAM (SBRAM)** provides storage for system-relevant user data that must be preserved while the major part of the device is powered down. The SBRAM is accessed via a specific interface and is powered in domain M.

### Table 6XC2766X Interrupt Nodes (cont'd)

| Source of Interrupt or PEC<br>Service Request | Control<br>Register | Vector<br>Location <sup>1)</sup> | Trap<br>Number                    |

|-----------------------------------------------|---------------------|----------------------------------|-----------------------------------|

| GPT2 CAPREL Register                          | GPT12E_CRIC         | xx'0094 <sub>H</sub>             | 25 <sub>H</sub> / 37 <sub>D</sub> |

| CAPCOM Timer 7                                | CC2_T7IC            | xx'0098 <sub>H</sub>             | 26 <sub>H</sub> / 38 <sub>D</sub> |

| CAPCOM Timer 8                                | CC2_T8IC            | xx'009C <sub>H</sub>             | 27 <sub>H</sub> / 39 <sub>D</sub> |

| A/D Converter Request 0                       | ADC_0IC             | xx'00A0 <sub>H</sub>             | 28 <sub>H</sub> / 40 <sub>D</sub> |

| A/D Converter Request 1                       | ADC_1IC             | xx'00A4 <sub>H</sub>             | 29 <sub>H</sub> / 41 <sub>D</sub> |

| A/D Converter Request 2                       | ADC_2IC             | xx'00A8 <sub>H</sub>             | 2A <sub>H</sub> / 42 <sub>D</sub> |

| A/D Converter Request 3                       | ADC_3IC             | xx'00AC <sub>H</sub>             | 2B <sub>H</sub> / 43 <sub>D</sub> |

| A/D Converter Request 4                       | ADC_4IC             | xx'00B0 <sub>H</sub>             | 2C <sub>H</sub> / 44 <sub>D</sub> |

| A/D Converter Request 5                       | ADC_5IC             | xx'00B4 <sub>H</sub>             | 2D <sub>H</sub> / 45 <sub>D</sub> |

| A/D Converter Request 6                       | ADC_6IC             | xx'00B8 <sub>H</sub>             | 2E <sub>H</sub> / 46 <sub>D</sub> |

| A/D Converter Request 7                       | ADC_7IC             | xx'00BC <sub>H</sub>             | 2F <sub>H</sub> / 47 <sub>D</sub> |

| CCU60 Request 0                               | CCU60_0IC           | xx'00C0 <sub>H</sub>             | 30 <sub>H</sub> / 48 <sub>D</sub> |

| CCU60 Request 1                               | CCU60_1IC           | xx'00C4 <sub>H</sub>             | 31 <sub>H</sub> / 49 <sub>D</sub> |

| CCU60 Request 2                               | CCU60_2IC           | xx'00C8 <sub>H</sub>             | 32 <sub>H</sub> / 50 <sub>D</sub> |

| CCU60 Request 3                               | CCU60_3IC           | xx'00CC <sub>H</sub>             | 33 <sub>H</sub> / 51 <sub>D</sub> |

| CCU61 Request 0                               | CCU61_0IC           | xx'00D0 <sub>H</sub>             | 34 <sub>H</sub> / 52 <sub>D</sub> |

| CCU61 Request 1                               | CCU61_1IC           | xx'00D4 <sub>H</sub>             | 35 <sub>H</sub> / 53 <sub>D</sub> |

| CCU61 Request 2                               | CCU61_2IC           | xx'00D8 <sub>H</sub>             | 36 <sub>H</sub> / 54 <sub>D</sub> |

| CCU61 Request 3                               | CCU61_3IC           | xx'00DC <sub>H</sub>             | 37 <sub>H</sub> / 55 <sub>D</sub> |

| CCU62 Request 0                               | CCU62_0IC           | xx'00E0 <sub>H</sub>             | 38 <sub>H</sub> / 56 <sub>D</sub> |

| CCU62 Request 1                               | CCU62_1IC           | xx'00E4 <sub>H</sub>             | 39 <sub>H</sub> / 57 <sub>D</sub> |

| CCU62 Request 2                               | CCU62_2IC           | xx'00E8 <sub>H</sub>             | 3A <sub>H</sub> / 58 <sub>D</sub> |

| CCU62 Request 3                               | CCU62_3IC           | xx'00EC <sub>H</sub>             | 3B <sub>H</sub> / 59 <sub>D</sub> |

| CCU63 Request 0                               | CCU63_0IC           | xx'00F0 <sub>H</sub>             | 3C <sub>H</sub> / 60 <sub>D</sub> |

| CCU63 Request 1                               | CCU63_1IC           | xx'00F4 <sub>H</sub>             | 3D <sub>H</sub> / 61 <sub>D</sub> |

| CCU63 Request 2                               | CCU63_2IC           | xx'00F8 <sub>H</sub>             | 3E <sub>H</sub> / 62 <sub>D</sub> |

| CCU63 Request 3                               | CCU63_3IC           | xx'00FC <sub>H</sub>             | 3F <sub>H</sub> / 63 <sub>D</sub> |

| CAN Request 0                                 | CAN_0IC             | xx'0100 <sub>H</sub>             | 40 <sub>H</sub> / 64 <sub>D</sub> |

| CAN Request 1                                 | CAN_1IC             | xx'0104 <sub>H</sub>             | 41 <sub>H</sub> / 65 <sub>D</sub> |

| CAN Request 2                                 | CAN_2IC             | xx'0108 <sub>H</sub>             | 42 <sub>H</sub> / 66 <sub>D</sub> |

#### Table 6XC2766X Interrupt Nodes (cont'd)

| Source of Interrupt or PEC<br>Service Request | Control<br>Register | Vector<br>Location <sup>1)</sup> | Trap<br>Number                     |

|-----------------------------------------------|---------------------|----------------------------------|------------------------------------|

| Unassigned node                               | -                   | xx'0184 <sub>H</sub>             | 61 <sub>H</sub> / 97 <sub>D</sub>  |

| Unassigned node                               | -                   | xx'0188 <sub>H</sub>             | 62 <sub>H</sub> / 98 <sub>D</sub>  |

| Unassigned node                               | -                   | xx'018C <sub>H</sub>             | 63 <sub>H</sub> / 99 <sub>D</sub>  |

| Unassigned node                               | _                   | xx'0190 <sub>H</sub>             | 64 <sub>H</sub> / 100 <sub>D</sub> |

| Unassigned node                               | -                   | xx'0194 <sub>H</sub>             | 65 <sub>H</sub> / 101 <sub>D</sub> |

| Unassigned node                               | _                   | xx'0198 <sub>H</sub>             | 66 <sub>H</sub> / 102 <sub>D</sub> |

| Unassigned node                               | _                   | xx'019C <sub>H</sub>             | 67 <sub>H</sub> / 103 <sub>D</sub> |

| Unassigned node                               | _                   | xx'01A0 <sub>H</sub>             | 68 <sub>H</sub> / 104 <sub>D</sub> |

| Unassigned node                               | _                   | xx'01A4 <sub>H</sub>             | 69 <sub>H</sub> / 105 <sub>D</sub> |

| Unassigned node                               | _                   | xx'01A8 <sub>H</sub>             | 6A <sub>H</sub> / 106 <sub>D</sub> |

| SCU Request 1                                 | SCU_1IC             | xx'01AC <sub>H</sub>             | 6B <sub>H</sub> / 107 <sub>D</sub> |

| SCU Request 0                                 | SCU_0IC             | xx'01B0 <sub>H</sub>             | 6C <sub>H</sub> / 108 <sub>D</sub> |

| Program Flash Modules                         | PFM_IC              | xx'01B4 <sub>H</sub>             | 6D <sub>H</sub> / 109 <sub>D</sub> |

| RTC                                           | RTC_IC              | xx'01B8 <sub>H</sub>             | 6E <sub>H</sub> / 110 <sub>D</sub> |

| End of PEC Subchannel                         | EOPIC               | xx'01BC <sub>H</sub>             | 6F <sub>H</sub> / 111 <sub>D</sub> |

1) Register VECSEG defines the segment where the vector table is located.

Bitfield VECSC in register CPUCON1 defines the distance between two adjacent vectors. This table represents the default setting with a distance of 4 (two words) between two vectors.

# 3.5 On-Chip Debug Support (OCDS)

The On-Chip Debug Support system built into the XC2766X provides a broad range of debug and emulation features. User software running on the XC2766X can be debugged within the target system environment.

The OCDS is controlled by an external debugging device via the debug interface. This consists of the JTAG port conforming to IEEE-1149. The debug interface can be completed with an optional break interface.

The debugger controls the OCDS with a set of dedicated registers accessible via the debug interface (JTAG). In addition the OCDS system can be controlled by the CPU, e.g. by a monitor program. An injection interface allows the execution of OCDS-generated instructions by the CPU.

Multiple breakpoints can be triggered by on-chip hardware, by software, or by an external trigger input. Single stepping is supported, as is the injection of arbitrary instructions and read/write access to the complete internal address space. A breakpoint trigger can be answered with a CPU halt, a monitor call, a data transfer, or/and the activation of an external signal.

Tracing data can be obtained via the debug interface, or via the external bus interface for increased performance.

The JTAG interface uses four interface signals, to communicate with external circuitry. The debug interface can be amended with two optional break lines.

When a capture/compare register has been selected for capture mode, the current contents of the allocated timer will be latched ('captured') into the capture/compare register in response to an external event at the port pin associated with this register. In addition, a specific interrupt request for this capture/compare register is generated. Either a positive, a negative, or both a positive and a negative external signal transition at the pin can be selected as the triggering event.

The contents of all registers selected for one of the five compare modes are continuously compared with the contents of the allocated timers.

When a match occurs between the timer value and the value in a capture/compare register, specific actions will be taken based on the compare mode selected.

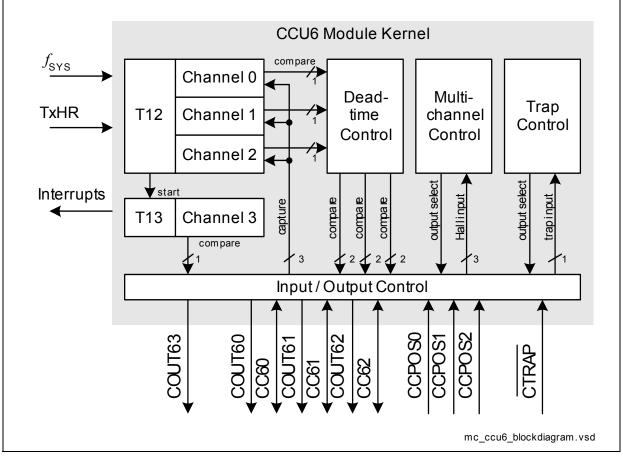

# 3.7 Capture/Compare Units CCU6x

The XC2766X features four CCU6 units (CCU60, CCU61, CCU62, CCU63).

The CCU6 is a high-resolution capture and compare unit with application-specific modes. It provides inputs to start the timers synchronously, an important feature in devices with several CCU6 modules.

The module provides two independent timers (T12, T13), that can be used for PWM generation, especially for AC motor control. Additionally, special control modes for block commutation and multi-phase machines are supported.

#### Timer 12 Features

- Three capture/compare channels, where each channel can be used either as a capture or as a compare channel.

- Supports generation of a three-phase PWM (six outputs, individual signals for highside and low-side switches)

- 16-bit resolution, maximum count frequency = peripheral clock

- Dead-time control for each channel to avoid short circuits in the power stage

- Concurrent update of the required T12/13 registers

- Center-aligned and edge-aligned PWM can be generated

- Single-shot mode supported

- Many interrupt request sources

- Hysteresis-like control mode

- Automatic start on a HW event (T12HR, for synchronization purposes)

#### Timer 13 Features

- One independent compare channel with one output

- 16-bit resolution, maximum count frequency = peripheral clock

- Can be synchronized to T12

- Interrupt generation at period match and compare match

- Single-shot mode supported

- Automatic start on a HW event (T13HR, for synchronization purposes)

#### Additional Features

- Block commutation for brushless DC drives implemented

- Position detection via Hall sensor pattern

- Automatic rotational speed measurement for block commutation

- Integrated error handling

- Fast emergency stop without CPU load via external signal (CTRAP)

- · Control modes for multi-channel AC drives

- Output levels can be selected and adapted to the power stage

# XC2766X XC2000 Family Derivatives

### **Functional Description**

#### Figure 6 CCU6 Block Diagram

Timer T12 can work in capture and/or compare mode for its three channels. The modes can also be combined. Timer T13 can work in compare mode only. The multi-channel control unit generates output patterns that can be modulated by timer T12 and/or timer T13. The modulation sources can be selected and combined for signal modulation.

# 4.2.1 DC Parameters for Upper Voltage Area

These parameters apply to the upper IO voltage range, 4.5 V  $\leq V_{\text{DDP}} \leq$  5.5 V.

#### Note / Parameter Symbol Values Unit **Test Condition** Min. Тур. Max. V Input low voltage $V_{\parallel}$ SR -0.3 $0.3 \times$ \_ \_ (all except XTAL1) $V_{\mathsf{DDP}}$ Input high voltage $V_{\rm IH}$ SR 0.7 × V $V_{\mathsf{DDP}}$ \_ \_ (all except XTAL1) + 0.3 $V_{\mathsf{DDP}}$ Input Hysteresis<sup>2)</sup> HYS CC 0.11 V $V_{\text{DDP}}$ in [V], \_ \_ Series $\times V_{\text{DDP}}$ resistance = $0 \Omega$ $I_{\rm OL} \leq I_{\rm OLmax}^{3)}$ $V_{OI}$ CC V Output low voltage 1.0 \_ \_ $I_{\rm OL} \leq I_{\rm OLnom}^{3)4)}$ V Output low voltage $V_{OI}$ CC 0.4 $I_{\text{OH}} \ge I_{\text{OHmax}}^{3)}$ Output high voltage<sup>5)</sup> $V_{OH}$ CC V $V_{\rm DDP}$ \_ - 1.0 $I_{\text{OH}} \ge I_{\text{OHnom}}^{3)4)}$ Output high voltage<sup>5)</sup> V $V_{OH}$ CC $V_{\mathsf{DDP}}$ \_ \_ - 0.4 $0 V < V_{IN} < V_{DDP}$ Input leakage current $I_{071}$ CC ±10 ±200 nA (Port 5, Port 15)<sup>6)</sup> $T_{.1} \le 110^{\circ}$ C, Input leakage current $I_{072} CC$ \_ $\pm 0.2$ ±5 μA $(all other)^{6)7}$ $0.45 V < V_{IN}$ $< V_{\rm DDP}$ $T_{1} \le 150^{\circ} C_{2}$ Input leakage current $I_{072} CC$ ±0.2 ±15 μA \_ (all other)<sup>6)7)</sup> $0.45 V < V_{IN}$ $< V_{\rm DDP}$ $V_{\text{PIN}} \ge V_{\text{IH}} (\text{up})^{8}$ Pull level keep current ±30 I<sub>PI K</sub> \_ \_ μA $V_{\mathsf{PIN}} \leq V_{\mathsf{IL}} (\mathsf{dn})$ $V_{\text{PIN}} \leq V_{\text{II}} \text{ (up)}^{8)}$ Pull level force current ±250 $I_{\mathsf{PIF}}$ μA $V_{\text{PIN}} \ge V_{\text{IH}} (\text{dn})$ Pin capacitance<sup>9)</sup> $C_{\rm IO}$ CC 10 pF \_ (digital inputs/outputs)

Table 14DC Characteristics for Upper Voltage Range<br/>(Operating Conditions apply)<sup>1)</sup>

1) Keeping signal levels within the limits specified in this table ensures operation without overload conditions. For signal levels outside these specifications, also refer to the specification of the overload current  $I_{OV}$ .

- Not subject to production test verified by design/characterization. Hysteresis is implemented to avoid metastable states and switching due to internal ground bounce. It cannot suppress switching due to external system noise under all conditions.

- The maximum deliverable output current of a port driver depends on the selected output driver mode, see Table 13, Current Limits for Port Output Drivers. The limit for pin groups must be respected.

- 4) As a rule, with decreasing output current the output levels approach the respective supply level ( $V_{OL} \rightarrow V_{SS}$ ,  $V_{OH} \rightarrow V_{DDP}$ ). However, only the levels for nominal output currents are verified.

- 5) This specification is not valid for outputs which are switched to open drain mode. In this case the respective output will float and the voltage is determined by the external circuit.

- 6) An additional error current (*I*<sub>INJ</sub>) will flow if an overload current flows through an adjacent pin. Please refer to the definition of the overload coupling factor *K*<sub>OV</sub>.

The leakage current value is not tested in the lower voltage range but only in the upper voltage range. This parameter is ensured by correlation.

- 7) The given values are worst-case values. In production test, this leakage current is only tested at 125°C; other values are ensured by correlation. For derating, please refer to the following descriptions:

Leakage derating depending on temperature ( $T_{J}$  = junction temperature [°C]):

$I_{OZ} = 0.03 \times e^{(1.35 + 0.028 \times TJ)}$  [µA]. For example, at a temperature of 130°C the resulting leakage current is 4.41 µA.

Leakage derating depending on voltage level (DV =  $V_{\text{DDP}}$  -  $V_{\text{PIN}}$  [V]):

$$I_{OZ} = I_{OZtempmax} - (1.3 \times DV) [\mu A]$$

This voltage derating formula is an approximation which applies for maximum temperature.

Because pin P2.8 is connected to two pads (standard pad and high-speed clock pad), it has twice the normal leakage.

8) Keep current: Limit the current through this pin to the indicated value so that the enabled pull device can keep the default pin level:  $V_{\text{PIN}} \ge V_{\text{IH}}$  for a pullup;  $V_{\text{PIN}} \le V_{\text{IL}}$  for a pulldown.

Force current: Drive the indicated minimum current through this pin to change the default pin level driven by the enabled pull device:  $V_{\text{PIN}} \leq V_{\text{IL}}$  for a pullup;  $V_{\text{PIN}} \geq V_{\text{IH}}$  for a pulldown.

These values apply to the fixed pull-devices in dedicated pins and to the user-selectable pull-devices in general purpose IO pins.

Not subject to production test - verified by design/characterization. Because pin P2.8 is connected to two pads (standard pad and high-speed clock pad), it has twice the normal capacitance.

# XC2766X XC2000 Family Derivatives

### **Electrical Parameters**

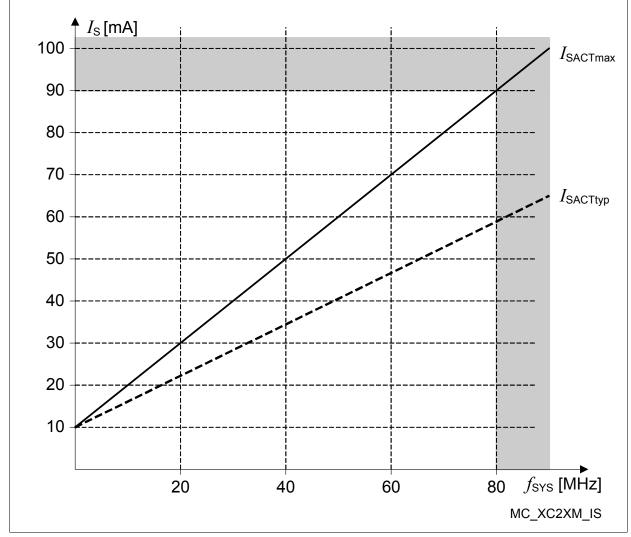

Figure 13 Supply Current in Active Mode as a Function of Frequency

# Table 17Leakage Power Consumption XC2766X<br/>(Operating Conditions apply)

| Parameter                                                                                                                         | Sym-          |      | Value | S    | Unit |                               |  |

|-----------------------------------------------------------------------------------------------------------------------------------|---------------|------|-------|------|------|-------------------------------|--|

|                                                                                                                                   | bol           | Min. | Тур.  | Max. |      | Test Condition <sup>1)</sup>  |  |

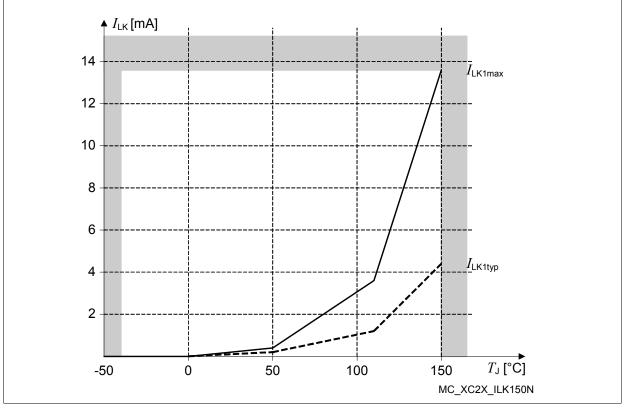

| Leakage supply current <sup>2)</sup>                                                                                              | $I_{\rm LK1}$ | _    | 0.03  | 0.05 | mA   | <i>T</i> <sub>J</sub> = 25°C  |  |

| Formula <sup>3)</sup> : 600,000 × $e^{-\alpha}$ ;<br>$\alpha$ = 5000 / (273 + B×T <sub>J</sub> );<br>Typ.: B = 1.0, Max.: B = 1.3 |               | _    | 0.5   | 1.3  | mA   | <i>T</i> <sub>J</sub> = 85°C  |  |

|                                                                                                                                   |               | _    | 2.1   | 6.2  | mA   | <i>T</i> <sub>J</sub> = 125°C |  |

|                                                                                                                                   |               | _    | 4.4   | 13.7 | mA   | <i>T</i> <sub>J</sub> = 150°C |  |

1) All inputs (including pins configured as inputs) are set at 0 V to 0.1 V or at  $V_{DDP}$  - 0.1 V to  $V_{DDP}$  and all outputs (including pins configured as outputs) are disconnected.

2) The supply current caused by leakage depends mainly on the junction temperature (see Figure 14) and the supply voltage. The temperature difference between the junction temperature  $T_J$  and the ambient temperature  $T_A$  must be taken into account. As this fraction of the supply current does not depend on device activity, it must be added to other power consumption values.

3) This formula is valid for temperatures above 0°C. For temperatures below 0°C a value of below 10  $\mu$ A can be assumed.

Figure 14 Leakage Supply Current as a Function of Temperature

## 4.3 Analog/Digital Converter Parameters

These parameters describe the conditions for optimum ADC performance.

# Table 18A/D Converter Characteristics<br/>(Operating Conditions apply)

| Parameter                                       | Symbol                  |    | Limit                         | Values                      | Unit | Test<br>Condition                   |  |

|-------------------------------------------------|-------------------------|----|-------------------------------|-----------------------------|------|-------------------------------------|--|

|                                                 |                         |    | Min.                          | Max.                        |      |                                     |  |

| Analog reference supply                         | V <sub>AREF</sub>       | SR | V <sub>AGND</sub><br>+ 1.0    | V <sub>DDPA</sub><br>+ 0.05 | V    | 1)                                  |  |

| Analog reference ground                         | V <sub>AGND</sub>       | SR | V <sub>SS</sub><br>- 0.05     | V <sub>AREF</sub><br>- 1.0  | V    | -                                   |  |

| Analog input voltage range                      | V <sub>AIN</sub>        | SR | V <sub>AGND</sub>             | V <sub>AREF</sub>           | V    | 2)                                  |  |

| Analog clock frequency                          | $f_{\rm ADCI}$          |    | 0.5                           | 20                          | MHz  | 3)                                  |  |

| Conversion time for 10-bit result <sup>4)</sup> | <i>t</i> <sub>C10</sub> | CC | (13 + STC)<br>+ 2 × $t_{SYS}$ | $) 	imes t_{ADCI}$          | -    | -                                   |  |

| Conversion time for 8-bit result <sup>4)</sup>  | t <sub>C8</sub>         | CC | (11 + STC)<br>+ 2 × $t_{SYS}$ | ) × $t_{ADCI}$              | -    | -                                   |  |

| Wakeup time from analog powerdown, fast mode    | t <sub>WAF</sub>        | СС | -                             | 1                           | μS   | -                                   |  |

| Wakeup time from analog powerdown, slow mode    | t <sub>WAS</sub>        | СС | -                             | 10                          | μS   | -                                   |  |

| Total unadjusted error <sup>5)</sup>            | TUE                     | CC | -                             | ±2                          | LSB  | $V_{\rm AREF} = 5.0 \ {\rm V}^{1)}$ |  |

| DNL error                                       | EA <sub>DNL</sub>       | CC | -                             | ±1                          | LSB  |                                     |  |

| INL error                                       | EA <sub>INL</sub>       | CC | -                             | ±1.2                        | LSB  |                                     |  |

| Gain error                                      | EA <sub>GAIN</sub>      | CC | -                             | ±0.8                        | LSB  |                                     |  |

| Offset error                                    | EA <sub>OFF</sub>       | CC | _                             | ±0.8                        | LSB  |                                     |  |

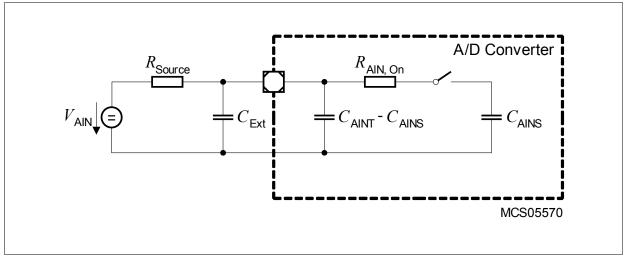

| Total capacitance of an analog input            | $C_{AINT}$              | CC | -                             | 10                          | pF   | 6)7)                                |  |

| Switched capacitance of an analog input         | $C_{AINS}$              | CC | -                             | 4                           | pF   | 6)7)                                |  |

| Resistance of the analog input path             | R <sub>AIN</sub>        | СС | -                             | 1.5                         | kΩ   | 6)7)                                |  |

| Total capacitance of the reference input        | $C_{AREFT}$             | СС | -                             | 15                          | pF   | 6)7)                                |  |

# Table 18A/D Converter Characteristics (cont'd)(Operating Conditions apply)

| Parameter                                   | Symbol            |    | Limi | t Values | Unit | Test      |  |

|---------------------------------------------|-------------------|----|------|----------|------|-----------|--|

|                                             |                   |    | Min. | Max.     |      | Condition |  |

| Switched capacitance of the reference input | $C_{AREFS}$       | CC | _    | 7        | pF   | 6)7)      |  |

| Resistance of the reference input path      | R <sub>AREF</sub> | CC | _    | 2        | kΩ   | 6)7)      |  |

1) TUE is tested at  $V_{AREFx} = V_{DDPA}$ ,  $V_{AGND} = 0$  V. It is verified by design for all other voltages within the defined voltage range.

The specified TUE is valid only if the absolute sum of input overload currents on Port 5 or Port 15 pins (see  $I_{OV}$  specification) does not exceed 10 mA, and if  $V_{AREF}$  and  $V_{AGND}$  remain stable during the measurement time.

- V<sub>AIN</sub> may exceed V<sub>AGND</sub> or V<sub>AREFx</sub> up to the absolute maximum ratings. However, the conversion result in these cases will be X000<sub>H</sub> or X3FF<sub>H</sub>, respectively.

- 3) The limit values for  $f_{ADCI}$  must not be exceeded when selecting the peripheral frequency and the prescaler setting.

- 4) This parameter includes the sample time (also the additional sample time specified by STC), the time to determine the digital result and the time to load the result register with the conversion result. Values for the basic clock t<sub>ADCI</sub> depend on programming and are found in Table 19.

- 5) The total unadjusted error TUE is the maximum deviation from the ideal ADC transfer curve, not the sum of individual errors.

All error specifications are based on measurement methods standardized by IEEE 1241.2000.

- 6) Not subject to production test verified by design/characterization.

- 7) These parameter values cover the complete operating range. Under relaxed operating conditions (temperature, supply voltage) typical values can be used for calculation. At room temperature and nominal supply voltage the following typical values can be used:

$C_{AINTtyp}$  = 12 pF,  $C_{AINStyp}$  = 5 pF,  $R_{AINtyp}$  = 1.0 k $\Omega$ ,  $C_{AREFTtyp}$  = 15 pF,  $C_{AREFStyp}$  = 10 pF,  $R_{AREFtyp}$  = 1.0 k $\Omega$ .

Figure 15 Equivalent Circuitry for Analog Inputs

# 4.6.3 External Clock Input Parameters

These parameters specify the external clock generation for the XC2766X. The clock can be generated in two ways:

- By connecting a **crystal or ceramic resonator** to pins XTAL1/XTAL2.

- By supplying an **external clock signal**. This clock signal can be supplied either to pin XTAL1 (core voltage domain) or to pin CLKIN1 (IO voltage domain).

If connected to CLKIN1, the input signal must reach the defined input levels  $V_{\rm IL}$  and  $V_{\rm IH}$ . In connected to XTAL1, a minimum amplitude  $V_{\rm AX1}$  (peak-to-peak voltage) is sufficient for the operation of the on-chip oscillator.

Note: The given clock timing parameters  $(t_1 \dots t_4)$  are only valid for an external clock input signal.

| Parameter                                      | Symbol             | L                          | imit Val | ues  | Unit | Note / Test                                            |  |

|------------------------------------------------|--------------------|----------------------------|----------|------|------|--------------------------------------------------------|--|

|                                                |                    | Min.                       | Тур.     | Max. |      | Condition                                              |  |

| Input voltage range limits for signal on XTAL1 | $V_{\rm IX1}$ SR   | -1.7 +<br>V <sub>DDI</sub> | -        | 1.7  | V    | 1)                                                     |  |

| Input voltage (amplitude)<br>on XTAL1          | $V_{AX1}SR$        | $0.3 \times V_{ m DDI}$    | -        | -    | V    | Peak-to-peak<br>voltage <sup>2)</sup>                  |  |

| XTAL1 input current                            | I <sub>IL</sub> CC | _                          | -        | ±20  | μA   | $0 \vee \langle V_{\rm IN} \langle V_{\rm DI} \rangle$ |  |

| Oscillator frequency                           | $f_{\rm OSC}$ CC   | 4                          | -        | 40   | MHz  | Clock signal                                           |  |

|                                                |                    | 4                          | -        | 16   | MHz  | Crystal or<br>Resonator                                |  |

| High time                                      | t <sub>1</sub> SR  | 6                          | -        | -    | ns   |                                                        |  |

| Low time                                       | $t_2$ SR           | 6                          | _        | -    | ns   |                                                        |  |

| Rise time                                      | t <sub>3</sub> SR  | _                          | 8        | 8    | ns   |                                                        |  |

| Fall time                                      | $t_4$ SR           | _                          | 8        | 8    | ns   |                                                        |  |

# Table 26External Clock Input Characteristics<br/>(Operating Conditions apply)

1) Overload conditions must not occur on pin XTAL1.

2) The amplitude voltage  $V_{AX1}$  refers to the offset voltage  $V_{OFF}$ . This offset voltage must be stable during the operation and the resulting voltage peaks must remain within the limits defined by  $V_{IX1}$ .

# Table 29External Bus Cycle Timing for Upper Voltage Range<br/>(Operating Conditions apply)

| Parameter                                                         | Symbol                    | Limits    |  |      | Unit | Note |

|-------------------------------------------------------------------|---------------------------|-----------|--|------|------|------|

|                                                                   |                           | Min. Typ. |  | Max. |      |      |

| Output valid delay for:<br>RD, WR(L/H)                            | <i>t</i> <sub>10</sub> CC | -         |  | 13   | ns   |      |

| Output valid delay for:<br>BHE, ALE                               | <i>t</i> <sub>11</sub> CC | -         |  | 13   | ns   |      |

| Output valid delay for:<br>A23 A16, A15 A0 (on P0/P1)             | <i>t</i> <sub>12</sub> CC | _         |  | 14   | ns   |      |

| Output valid delay for:<br>A15 A0 (on P2/P10)                     | <i>t</i> <sub>13</sub> CC | -         |  | 14   | ns   |      |

| Output valid delay for:<br>CS                                     | <i>t</i> <sub>14</sub> CC | -         |  | 13   | ns   |      |

| Output valid delay for:<br>D15 D0 (write data, MUX-mode)          | <i>t</i> <sub>15</sub> CC | -         |  | 14   | ns   |      |

| Output valid delay for:<br>D15 D0 (write data, DEMUX-<br>mode)    | <i>t</i> <sub>16</sub> CC | -         |  | 14   | ns   |      |

| Output hold time for:<br>RD, WR(L/H)                              | <i>t</i> <sub>20</sub> CC | 0         |  | 8    | ns   |      |

| Output hold time for:<br>BHE, ALE                                 | <i>t</i> <sub>21</sub> CC | 0         |  | 8    | ns   |      |

| Output hold time for:<br>A23 A16, A15 A0 (on P2/P10)              | <i>t</i> <sub>23</sub> CC | 0         |  | 8    | ns   |      |

| Output hold time for:<br>CS                                       | <i>t</i> <sub>24</sub> CC | 0         |  | 8    | ns   |      |

| Output hold time for:<br>D15 D0 (write data)                      | <i>t</i> <sub>25</sub> CC | 0         |  | 8    | ns   |      |

| Input setup time for:<br>READY, D15 … D0 (read data)              | <i>t</i> <sub>30</sub> SR | 18        |  | -    | ns   |      |

| Input hold time for:<br>READY, D15 … D0 (read data) <sup>1)</sup> | <i>t</i> <sub>31</sub> SR | -4        |  | -    | ns   |      |

Read data are latched with the same internal clock edge that triggers the address change and the rising edge of RD. Address changes before the end of RD have no impact on (demultiplexed) read cycles. Read data can change after the rising edge of RD.

# 4.6.5 Synchronous Serial Interface Timing

The following parameters are applicable for a USIC channel operated in SSC mode.

Note: These parameters are not subject to production test but verified by design and/or characterization.

# Table 31SSC Master/Slave Mode Timing for Upper Voltage Range<br/>(Operating Conditions apply), $C_L = 50 \text{ pF}$

| Parameter                                                         | Symbol                    | Values                   |      |      | Unit | Note /             |

|-------------------------------------------------------------------|---------------------------|--------------------------|------|------|------|--------------------|

|                                                                   |                           | Min.                     | Тур. | Max. |      | Test Co<br>ndition |

| Master Mode Timing                                                |                           |                          |      |      |      | 1                  |

| Slave select output SELO active to first SCLKOUT transmit edge    | t <sub>1</sub> CC         | 0                        | -    | 1)   | ns   | 2)                 |

| Slave select output SELO inactive after last SCLKOUT receive edge | t <sub>2</sub> CC         | $0.5 \times t_{\rm BIT}$ | -    | 3)   | ns   |                    |

| Transmit data output valid time                                   | t <sub>3</sub> CC         | -6                       | _    | 13   | ns   |                    |

| Receive data input setup time to SCLKOUT receive edge             | t <sub>4</sub> SR         | 31                       | -    | -    | ns   |                    |

| Data input DX0 hold time from SCLKOUT receive edge                | $t_5$ SR                  | -7                       | -    | -    | ns   |                    |

| Slave Mode Timing                                                 |                           |                          |      |      |      |                    |

| Select input DX2 setup to first clock input DX1 transmit edge     | <i>t</i> <sub>10</sub> SR | 7                        | -    | -    | ns   | 4)                 |

| Select input DX2 hold after last clock input DX1 receive edge     | <i>t</i> <sub>11</sub> SR | 5                        | -    | -    | ns   | 4)                 |

| Data input DX0 setup time to clock input DX1 receive edge         | <i>t</i> <sub>12</sub> SR | 7                        | -    | -    | ns   | 4)                 |

| Data input DX0 hold time from clock input DX1 receive edge        | <i>t</i> <sub>13</sub> SR | 5                        | -    | -    | ns   | 4)                 |

| Data output DOUT valid time                                       | <i>t</i> <sub>14</sub> CC | 8                        | _    | 29   | ns   | 4)                 |

1) The maximum value further depends on the settings for the slave select output leading delay.

2)  $t_{SYS} = 1/f_{SYS}$  (= 12.5 ns @ 80 MHz)

- The maximum value depends on the settings for the slave select output trailing delay and for the shift clock output delay.

- 4) These input timings are valid for asynchronous input signal handling of slave select input, shift clock input, and receive data input (bits DXnCR.DSEN = 0).

#### Package and Reliability

# 5 Package and Reliability

In addition to the electrical parameters, the following specifications ensure proper integration of the XC2766X into the target system.

### 5.1 Packaging

These parameters specify the packaging rather than the silicon.

| Table 34 | Package Parameters | (PG-LQFP-100-3) |

|----------|--------------------|-----------------|

|          |                    |                 |

| Parameter                              | Symbol             | Limit Values |           | Unit | Notes                         |

|----------------------------------------|--------------------|--------------|-----------|------|-------------------------------|

|                                        |                    | Min.         | Max.      |      |                               |

| Exposed Pad Dimension                  | $Ex \times Ey$     | _            | 6.2 × 6.2 | mm   | -                             |

| Power Dissipation                      | $P_{DISS}$         | -            | 1.0       | W    | -                             |

| Thermal resistance<br>Junction-Ambient | $R_{ m \Theta JA}$ | -            | 49        | K/W  | No thermal via <sup>1)</sup>  |

|                                        |                    |              | 37        | K/W  | 4-layer, no pad <sup>2)</sup> |

|                                        |                    |              | 22        | K/W  | 4-layer, pad <sup>3)</sup>    |

1) Device mounted on a 2-layer JEDEC board (according to JESD 51-3) or a 4-layer board without thermal vias; exposed pad not soldered.

2) Device mounted on a 4-layer JEDEC board (according to JESD 51-7) with thermal vias; exposed pad not soldered.

3) Device mounted on a 4-layer JEDEC board (according to JESD 51-7) with thermal vias; exposed pad soldered to the board.