Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | H8/300L                                                                      |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 4MHz                                                                         |

| Connectivity               | SCI                                                                          |

| Peripherals                | LCD, PWM, WDT                                                                |

| Number of I/O              | 39                                                                           |

| Program Memory Size        | 32KB (32K x 8)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                |                                                                              |

| RAM Size                   | 1K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                  |

| Data Converters            | A/D 4x10b                                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 64-LQFP                                                                      |

| Supplier Device Package    | 64-LFQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df38004fp4v |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Configuration of This Manual

This manual comprises the following items:

- 1. General Precautions in the Handling of MPU/MCU Products

- 2. Configuration of This Manual

- 3. Preface

- 4. Contents

- 5. Overview

- 6. Description of Functional Modules

- CPU and System-Control Modules

- On-Chip Peripheral Modules

The configuration of the functional description of each module differs according to the module. However, the generic style includes the following items:

- i) Feature

- ii) Input/Output Pin

- iii) Register Description

- iv) Operation

- v) Usage Note

When designing an application system that includes this LSI, take notes into account. Each section includes notes in relation to the descriptions given, and usage notes are given, as required, as the final part of each section.

- 7. List of Registers

- 8. Electrical Characteristics

- 9. Appendix

- 10. Main Revisions for This Edition (only for revised versions)

The list of revisions is a summary of points that have been revised or added to earlier versions. This does not include all of the revised contents. For details, see the actual locations in this manual.

11. Index

| Figure 6.3     | H8/3802 Memory Map in PROM Mode                                           | 136 |

|----------------|---------------------------------------------------------------------------|-----|

| Figure 6.4     | High-Speed, High-Reliability Programming Flowchart                        | 138 |

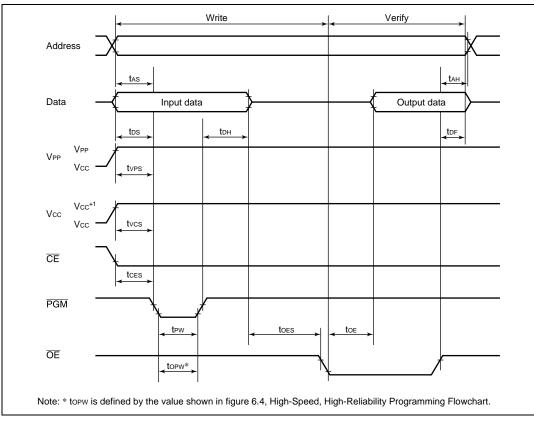

| Figure 6.5     | PROM Write/Verify Timing                                                  | 141 |

| Figure 6.6     | Recommended Screening Procedure                                           | 142 |

| Figure 6.7     | Block Diagram of Flash Memory                                             | 144 |

| Figure 6.8(1)  | Block Configuration of 32-kbyte Flash Memory                              | 145 |

| Figure 6.8(2)  | Block Configuration of 16-kbyte Flash Memory                              | 146 |

| Figure 6.9     | Programming/Erasing Flowchart Example in User Program Mode                | 154 |

| Figure 6.10    | Program/Program-Verify Flowchart                                          | 157 |

| Figure 6.11    | Erase/Erase-Verify Flowchart                                              | 160 |

| Figure 6.12(1) | Socket Adapter Pin Correspondence Diagram (H8/38004F, H8/38002F)          | 164 |

| Figure 6.12(2) | Socket Adapter Pin Correspondence Diagram (H8/38104F, H8/38102F)          | 165 |

| Figure 6.13    | Timing Waveforms for Memory Read after Command Write                      | 167 |

| Figure 6.14    | Timing Waveforms in Transition from Memory Read Mode to                   |     |

|                | Another Mode                                                              | 168 |

| Figure 6.15    | Timing Waveforms in $\overline{CE}$ and $\overline{OE}$ Enable State Read | 168 |

| Figure 6.16    | Timing Waveforms in $\overline{CE}$ and $\overline{OE}$ Clock System Read | 169 |

| Figure 6.17    | Timing Waveforms in Auto-Program Mode                                     | 170 |

| Figure 6.18    | Timing Waveforms in Auto-Erase Mode                                       | 172 |

| Figure 6.19    | Timing Waveforms in Status Read Mode                                      | 173 |

| Figure 6.20    | Oscillation Stabilization Time, Boot Program Transfer Time,               |     |

|                | and Power-Down Sequence                                                   | 175 |

| Section 7 RA   | Μ                                                                         |     |

| Figure 7.1     | Block Diagram of RAM (H8/3802)                                            | 178 |

| Section 8 I/O  | Ports                                                                     |     |

| Figure 8.1     | Port 3 Pin Configuration                                                  | 181 |

| Figure 8.2     | Port 4 Pin Configuration                                                  | 188 |

| Figure 8.3     | Input/Output Data Inversion Function                                      | 189 |

| Figure 8.4     | Port 5 Pin Configuration                                                  |     |

| Figure 8.5     | Port 6 Pin Configuration                                                  | 196 |

| U           | C                        |     |

|-------------|--------------------------|-----|

| Figure 8.5  | Port 6 Pin Configuration | 196 |

| Figure 8.6  | Port 7 Pin Configuration |     |

| Figure 8.7  | Port 8 Pin Configuration |     |

| Figure 8.8  | Port 9 Pin Configuration |     |

| Figure 8.9  | Port A Pin Configuration |     |

| Figure 8.10 | Port B Pin Configuration |     |

|             |                          |     |

#### Section 9 Timers

| Figure 9.1 | Block Diagram of Timer A | 218 |

|------------|--------------------------|-----|

| Figure 9.2 | Block Diagram of Timer F | 222 |

| Table 17.4  | Serial Interface (SCI3) Timing                             | 386 |

|-------------|------------------------------------------------------------|-----|

| Table 17.5  | A/D Converter Characteristics                              | 387 |

| Table 17.6  | LCD Characteristics                                        | 389 |

| Table 17.7  | Absolute Maximum Ratings                                   | 390 |

| Table 17.8  | DC Characteristics                                         | 395 |

| Table 17.9  | Control Signal Timing                                      | 403 |

| Table 17.10 | Serial Interface (SCI3) Timing                             | 407 |

| Table 17.11 | A/D Converter Characteristics                              | 408 |

| Table 17.12 | LCD Characteristics                                        | 410 |

| Table 17.13 | Flash Memory Characteristics                               | 411 |

| Table 17.14 | Power Supply Characteristics                               | 413 |

| Table 17.15 | Absolute Maximum Ratings                                   | 414 |

| Table 17.16 | DC Characteristics (1)                                     | 419 |

| Table 17.16 | DC Characteristics (2)                                     | 420 |

| Table 17.16 | DC Characteristics (3)                                     | 421 |

| Table 17.16 | DC Characteristics (4)                                     | 422 |

| Table 17.16 | DC Characteristics (5)                                     | 423 |

| Table 17.17 | Control Signal Timing                                      | 428 |

| Table 17.18 | Serial Interface (SCI3) Timing                             | 429 |

| Table 17.19 | A/D Converter Characteristics                              | 430 |

| Table 17.20 | LCD Characteristics                                        |     |

| Table 17.21 | Flash Memory Characteristics                               | 432 |

| Table 17.22 | Power Supply Voltage Detection Circuit Characteristics (1) | 434 |

| Table 17.23 | Power Supply Voltage Detection Circuit Characteristics (2) | 435 |

| Table 17.24 | Power Supply Voltage Detection Circuit Characteristics (3) | 435 |

| Table 17.25 | Power Supply Voltage Detection Circuit Characteristics (4) | 436 |

| Table 17.26 | Power Supply Voltage Detection Circuit Characteristics (5) | 437 |

| Table 17.27 | Power-On Reset Circuit Characteristics                     | 437 |

| Table 17.28 | Watchdog Timer Characteristics                             | 438 |

| Table 17.29 | Power Supply Characteristics                               | 438 |

## Appendices

| Table A.1 | Instruction Set                         |  |

|-----------|-----------------------------------------|--|

| Table A.2 | Operation Code Map                      |  |

| Table A.3 | Number of States Required for Execution |  |

| Table A.4 | Number of Cycles in Each Instruction    |  |

| Table C.1 | Port States                             |  |

| Table D.1 | Product Code Lineup of H8/3802 Group    |  |

| Table D.2 | Product Code Lineup of H8/38004 Group   |  |

| Table D.3 | Product Code Lineup of H8/38002S Group  |  |

| Table D.4 | Product Code Lineup of H8/38104 Group   |  |

|           |                                         |  |

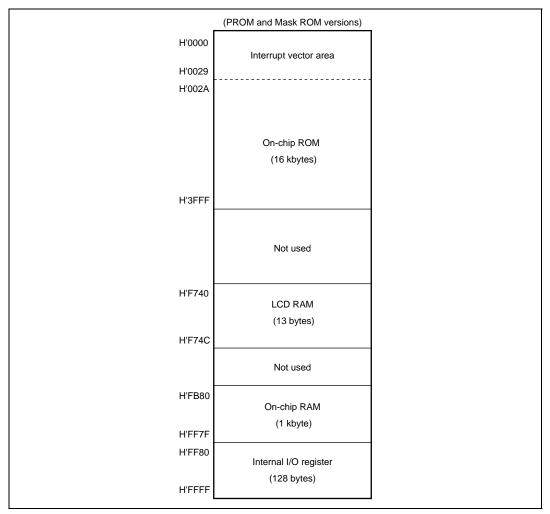

# 2.2 Address Space and Memory Map

The address space of this LSI is 64 kbytes, which includes the program area and the data area. Figures 2.1 show the memory map.

Figure 2.1(1) H8/3802 Memory Map

#### Immediate—#xx:8/#xx:16

The instruction contains an 8-bit operand (#xx:8) in its second byte, or a 16-bit operand (#xx:16) in its third and fourth bytes. Only MOV.W instructions can contain 16-bit immediate values.

The ADDS and SUBS instructions implicitly contain the value 1 or 2 as immediate data. Some bit manipulation instructions contain 3-bit immediate data in the second or fourth byte of the instruction, specifying a bit number.

#### Program-Counter Relative—@(d:8, PC)

This mode is used in the Bcc and BSR instructions. An 8-bit displacement in byte 2 of the instruction code is sign-extended to 16 bits and added to the program counter contents to generate a branch destination address. The possible branching range is -126 to +128 bytes (-63 to +64 words) from the current address. The displacement should be an even number.

#### Memory Indirect—@@aa:8

This mode can be used by the JMP and JSR instructions. The second byte of the instruction code specifies an 8-bit absolute address. The word located at this address contains the branch destination address. The upper 8 bits of the absolute address are assumed to be 0 (H'00), so the address range is from H'0000 to H'00FF (0 to 255). Note that with the H8/300L Series, the lower end of the address area is also used as a vector area. See section 3.1, Exception Sources and Vector Address, for details on the vector area.

If an odd address is specified as a branch destination or as the operand address of a MOV.W instruction, the least significant bit is regarded as 0, causing word access to be performed at the address preceding the specified address. See section 2.4.2, Memory Data Formats, for further information.

## Renesas

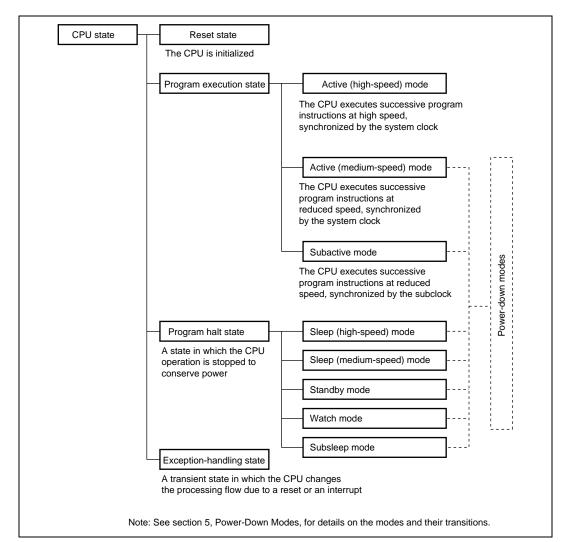

## 2.8 CPU States

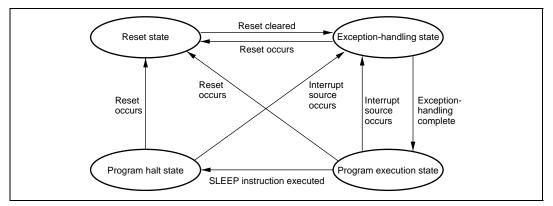

There are four CPU states: the reset state, program execution state, program halt state, and exception-handling state. The program execution state includes active (high-speed or medium-speed) mode and subactive mode. In the program halt state, there are a sleep (high-speed or medium-speed) mode, standby mode, watch mode, and sub-sleep mode.

These states are shown in figure 2.15. Figure 2.16 shows the state transitions.

### Figure 2.15 CPU Operation States

Figure 2.16 State Transitions

### 2.9 Usage Notes

#### 2.9.1 Notes on Data Access to Empty Areas

The address space of this LSI includes empty areas in addition to the ROM, RAM, and on-chip I/O registers areas available to the user. When data is transferred from CPU to empty areas, the transferred data will be lost. This action may also cause the CPU to malfunction. When data is transferred from an empty area to CPU, the contents of the data cannot be guaranteed.

### 2.9.2 Access to Internal I/O Registers

Internal data transfer to or from on-chip peripheral modules other than the on-chip ROM and RAM areas makes use of an 8-bit data width. If word access is attempted to these areas, the following results will occur.

Word access from CPU to I/O register area:

Upper byte: Will be written to I/O register.

Lower byte: Transferred data will be lost.

Word access from I/O register to CPU:

Upper byte: Will be written to upper part of CPU register.

Lower byte: Data which is written to lower part of CPU register is not guaranteed.

# Renesas

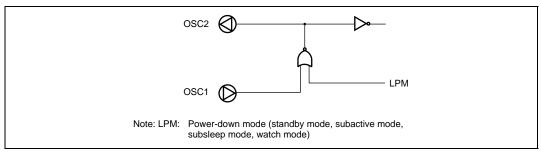

## 4.3 System Clock Generator

Clock pulses can be supplied to the system clock divider either by connecting a crystal or ceramic resonator, or by providing external clock input. Figure 4.3 shows a block diagram of the system clock generator.

As shown in figure 4.2, the H8/38104 Group supports selection between a system clock oscillator and an on-chip oscillator. See section 4.3.4, on-chip oscillator selection method, for information on selecting the on-chip oscillator.

Figure 4.3 Block Diagram of System Clock Generator

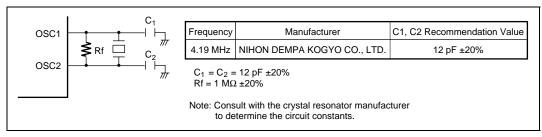

### 4.3.1 Connecting Crystal Resonator

Figure 4.4(1) shows a typical method of connecting a crystal oscillator to the H8/3802 Group, and figure 4.4(2) shows a typical method of connecting a crystal oscillator to the H8/38004, H8/38104 and H8/38002S Group. Figure 4.5 shows the equivalent circuit of a crystal resonator. A resonator having the characteristics given in table 4.1 should be used.

Figure 4.4(1) Typical Connection to Crystal Resonator (H8/3802 Group)

Figure 6.5 PROM Write/Verify Timing

#### 6.3.2 Programming Precautions

• Use the specified programming voltage and timing.

The programming voltage in PROM mode (Vpp) is 12.5 V. Use of a higher voltage can permanently damage the chip. Be especially careful with respect to PROM programmer overshoot.

Setting the PROM programmer to Renesas specifications for the HN27C101 will result in correct Vpp of 12.5 V.

- Make sure the index marks on the PROM programmer socket, socket adapter, and chip are properly aligned. If they are not, the chip may be destroyed by excessive current flow. Before programming, be sure that the chip is properly mounted in the PROM programmer.

- Avoid touching the socket adapter or chip while programming, since this may cause contact faults and write errors.

#### 6.5.3 Block Configuration

Figure 6.8 shows the block configuration of 32-kbyte flash memory. The thick lines indicate erasing units, the narrow lines indicate programming units, and the values are addresses. The 32-kbyte flash memory is divided into 1 kbyte  $\times$  4 blocks and 28 kbytes  $\times$  1 block. Erasing is performed in these units. The 16-kbyte flash memory is divided into 1 kbyte  $\times$  4 blocks and 12 kbytes  $\times$  1 block. Programming is performed in 128-byte units starting from an address with lower eight bits H'00 or H'80.

|            |        |        | , ,    |                                 |             |

|------------|--------|--------|--------|---------------------------------|-------------|

|            | H'0000 | H'0001 | H'0002 | ← Programming unit: 128 bytes → | H'007F      |

| Erase unit | H'0080 | H'0081 | H'0082 |                                 | H'00FF      |

| 1 kbyte    |        |        |        |                                 |             |

|            |        | 1      |        |                                 |             |

|            | H'0380 | H'0381 | H'0382 |                                 | H'03FF      |

|            | H'0400 | H'0401 | H'0402 | ← Programming unit: 128 bytes → | H'047F      |

| Erase unit | H'0480 | H'0481 | H'0482 |                                 | H'04FF      |

| 1 kbyte    |        |        |        |                                 |             |

|            | H'0780 | H'0781 | H'0782 |                                 |             |

|            |        |        | · · ·  |                                 | H'07FF      |

|            | H'0800 | H'0801 | H'0802 | ← Programming unit: 128 bytes → | H'087F      |

| Erase unit | H'0880 | H'0881 | H'0882 |                                 | H'08FF      |

| 1 kbyte    |        |        |        |                                 | 1           |

|            |        |        |        |                                 | 1<br>1<br>1 |

|            | H'0B80 | H'0B81 | H'0B82 |                                 | H'0BFF      |

|            | H'0C00 | H'0C01 | H'0C02 | ← Programming unit: 128 bytes → | H'0C7F      |

| Erase unit | H'0C80 | H'0C81 | H'0C82 |                                 | H'0CFF      |

| 1 kbyte    |        |        |        |                                 |             |

|            | H'0F80 | H'0F81 | H'0F82 |                                 | H'0FFF      |

|            | H'1000 | H'1001 | H'1002 | ← Programming unit: 128 bytes → | H'107F      |

| Erase unit | H'1080 | H'1081 | H'1082 |                                 | H'10FF      |

|            | П 1000 |        |        |                                 |             |

| 28 kbytes  |        |        |        |                                 |             |

|            |        |        |        |                                 |             |

|            | H'7F80 | H'7F81 | H'7F82 |                                 | H'7FFF      |

Figure 6.8(1) Block Configuration of 32-kbyte Flash Memory

#### 6.10.8 Programmer Mode Transition Time

Commands cannot be accepted during the oscillation stabilization period or the programmer mode setup period. After the programmer mode setup time, a transition is made to memory read mode.

| <b>Table 6.20</b> | Stipulated <b>T</b> | <b>Fransition</b> | Times to | Command | Wait State |

|-------------------|---------------------|-------------------|----------|---------|------------|

|-------------------|---------------------|-------------------|----------|---------|------------|

| Item                                               | Symbol            | Min | Max | Unit | Test Condition |

|----------------------------------------------------|-------------------|-----|-----|------|----------------|

| Oscillation stabilization time (crystal resonator) | t <sub>osc1</sub> | 10  | —   | ms   | Figure 6.20    |

| Oscillation stabilization time (ceramic resonator) | -                 | 5   | —   | ms   |                |

| Programmer mode setup time                         | t <sub>bmv</sub>  | 10  | —   | ms   |                |

| V <sub>cc</sub> hold time                          | t <sub>dwn</sub>  | 0   |     | ms   |                |

#### Figure 6.20 Oscillation Stabilization Time, Boot Program Transfer Time, and Power-Down Sequence

#### 6.10.9 Notes on Memory Programming

- 1. When performing programming using programmer mode on a chip that has been programmed/erased in on-board programming mode, auto-erasing is recommended before carrying out auto-programming.

- 2. The flash memory is initially in the erased state when the device is shipped by Renesas. For other chips for which the erasure history is unknown, it is recommended that auto-erasing be executed to check and supplement the initialization (erase) level.

### **10.7.6** Relation between Writing to TDR and Bit TDRE

Bit TDRE in the serial status register (SSR) is a status flag that indicates that data for serial transmission has not been prepared in TDR. When data is written to TDR, bit TDRE is cleared to 0 automatically. When the SCI3 transfers data from TDR to TSR, bit TDRE is set to 1.

Data can be written to TDR irrespective of the state of bit TDRE, but if new data is written to TDR while bit TDRE is cleared to 0, the data previously stored in TDR will be lost if it has not yet been transferred to TSR. Accordingly, to ensure that serial transmission is performed dependably, you should first check that bit TDRE is set to 1, then write the transmit data to TDR only once (not two or more times).

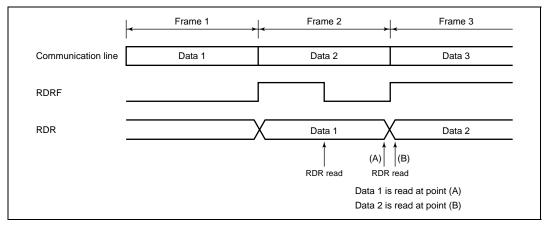

### 10.7.7 Relation between RDR Reading and bit RDRF

In a receive operation, the SCI3 continually checks the RDRF flag. If bit RDRF is cleared to 0 when reception of one frame ends, normal data reception is completed. If bit RDRF is set to 1, this indicates that an overrun error has occurred.

When the contents of RDR are read, bit RDRF is cleared to 0 automatically. Therefore, if RDR is read more than once, the second and subsequent read operations will be performed while bit RDRF is cleared to 0. Note that, when an RDR read is performed while bit RDRF is cleared to 0, if the read operation coincides with completion of reception of a frame, the next frame of data may be read. This is shown in figure 10.17.

Figure 10.17 Relation between RDR Read Timing and Data

In this case, only a single RDR read operation (not two or more) should be performed after first checking that bit RDRF is set to 1. If two or more reads are performed, the data read the first time

| Bit    | Bit Name | Initial<br>Value | R/W | Description                                                                             |

|--------|----------|------------------|-----|-----------------------------------------------------------------------------------------|

| 7 to 3 |          | All 1            | _   | Reserved                                                                                |

|        |          |                  |     | This bit is reserved. It is always read as 1 and cannot be written to.                  |

| 2      | PWCR2    | 0                | W   | Output Format Select                                                                    |

|        |          |                  |     | 0: 10-bit PWM                                                                           |

|        |          |                  |     | 1: Event counter PWM (PWM incorporating AEC)                                            |

| 1      | PWCR1    | 0                | W   | Clock Select 1, 0                                                                       |

| 0      | PWCR0    | 0                | W   | 00: The input clock is $\phi$ (t $\phi$ = 1/ $\phi$ )                                   |

|        |          |                  |     | — The conversion period is 512/ $\phi$ , with a minimum modulation width of 1/2 $\phi$  |

|        |          |                  |     | 01: The input clock is $\phi/2$ (t $\phi = 2/\phi$ )                                    |

|        |          |                  |     | — The conversion period is 1,024/ $\phi$ , with a minimum modulation width of 1/ $\phi$ |

|        |          |                  |     | 10: The input clock is $\phi/4$ (t $\phi = 4/\phi$ )                                    |

|        |          |                  |     | — The conversion period is 2,048/ $\phi$ , with a minimum modulation width of 2/ $\phi$ |

|        |          |                  |     | 11: The input clock is $\phi/8$ (t $\phi = 8/\phi$ )                                    |

|        |          |                  |     | — The conversion period is 4,096/ $\phi$ , with a minimum modulation width of 4/ $\phi$ |

Selects the PWCR output format and the conversion period on the H8/38104 Group.

Legend: to: Period of PWM clock input

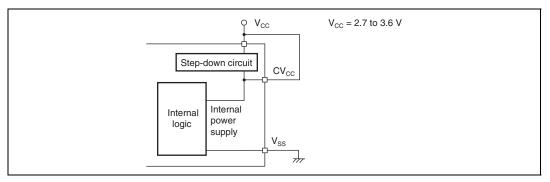

# 15.2 When Not Using Internal Power Supply Step-Down Circuit

When the internal power supply step-down circuit is not used, connect the external power supply to the  $CV_{cc}$  pin and  $V_{cc}$  pin, as shown in figure 15.2. The external power supply is then input directly to the internal power supply. The permissible range for the power supply voltage is 2.7 V to 3.6 V. Operation cannot be guaranteed if a voltage outside this range (less than 3.0 V or more than 3.6 V) is input.

Figure 15.2 Power Supply Connection when Internal Step-Down Circuit Is Not Used

#### Table 17.2DC Characteristics (4)

$V_{cc} = 1.8 \text{ V to } 5.5 \text{ V}, \text{AV}_{cc} = 1.8 \text{ V to } 5.5 \text{ V}, \text{V}_{ss} = \text{AV}_{ss} = 0.0 \text{ V}$ , unless otherwise specified (including subactive mode),  $T_a = -20^{\circ}\text{C}$  to  $+75^{\circ}\text{C}$  (product with regular specifications),  $T_a = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$  (product with wide-range temperature specifications),  $T_a = +75^{\circ}\text{C}$  (bare die product)

|                                     |                    |                                                                                   |                                                                             |      | Value | s     |      |                 |

|-------------------------------------|--------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------|------|-------|-------|------|-----------------|

| Item                                | Symbol             | Applicable Pins                                                                   | Test Condition                                                              | Min  | Тур   | Max   | Unit | Notes           |

| Pull-up<br>MOS                      | $-I_p$             | P31 to P37,<br>P50 to P57,                                                        | $V_{\rm CC} = 5.0 \text{ V},$<br>$V_{\rm IN} = 0.0 \text{ V}$               | 50.0 | —     | 300.0 | μA   |                 |

| current                             |                    | P60 to P67                                                                        | $V_{cc} = 2.7 V,$<br>$V_{iN} = 0.0 V$                                       | _    | 35.0  | _     |      | Reference value |

| Input<br>capaci-<br>tance           | C <sub>in</sub>    | All input pins<br>except power<br>supply, RES, P43,<br>IRQAEC, PB0 to<br>PB3 pins | f = 1  MHz,<br>$V_{IN} = 0.0 \text{ V},$<br>$T_a = 25^{\circ}\text{C}$      | _    | _     | 15.0  | pF   |                 |

|                                     |                    | IRQAEC                                                                            | -                                                                           | _    | _     | 30.0  |      |                 |

|                                     |                    | RES                                                                               | -                                                                           | _    | _     | 80.0  |      | *2              |

|                                     |                    |                                                                                   |                                                                             | _    | _     | 15.0  |      | *1              |

|                                     |                    | P43                                                                               | -                                                                           | _    | _     | 50.0  |      | *2              |

|                                     |                    |                                                                                   |                                                                             | _    | _     | 15.0  |      | *1              |

|                                     |                    | PB0 to PB3                                                                        | -                                                                           | _    | —     | 15.0  |      |                 |

| Active                              | I <sub>OPE1</sub>  | V <sub>cc</sub>                                                                   | Active (high-speed)                                                         | _    | 7.0   | 10.0  | mA   | *3              |

| mode<br>current<br>consump-         |                    |                                                                                   | mode<br>$V_{cc} = 5.0 V,$<br>$f_{osc} = 10 MHz$                             |      |       |       |      | *4              |

| tion                                | I <sub>OPE2</sub>  | V <sub>cc</sub>                                                                   | Active (medium-                                                             | _    | 2.2   | 3.0   | mA   | *3              |

|                                     |                    |                                                                                   | speed) mode<br>$V_{cc} = 5.0 V,$<br>$f_{osc} = 10 MHz,$<br>$\phi_{osc}/128$ |      |       |       |      | *4              |

| Sleep                               | I <sub>SLEEP</sub> | V <sub>cc</sub>                                                                   | V <sub>cc</sub> = 5.0 V,                                                    | _    | 3.8   | 5.0   | mA   | *3              |

| mode<br>current<br>consump-<br>tion |                    |                                                                                   | $f_{OSC} = 10 \text{ MHz}$                                                  |      |       |       |      | *4              |

# 17.3 Absolute Maximum Ratings of H8/38004 Group (F-ZTAT Version, Mask ROM Version), H8/38002S Group (Mask ROM Version)

Table 17.7 lists the absolute maximum ratings.

| <b>Table 17.7</b> | Absolute | Maximum | Ratings |

|-------------------|----------|---------|---------|

|-------------------|----------|---------|---------|

| Item                        |                   | Symbol           | Value                                                                 | Unit | Note |

|-----------------------------|-------------------|------------------|-----------------------------------------------------------------------|------|------|

| Power supply voltage        |                   | V <sub>cc</sub>  | -0.3 to +4.3                                                          | V    | *1   |

| Analog power supply voltage |                   | $AV_{cc}$        | –0.3 to +4.3                                                          | V    |      |

| Input voltage               | Other than port B | V <sub>in</sub>  | –0.3 to V $_{\rm cc}$ +0.3                                            | V    |      |

|                             | Port B            | $AV_{in}$        | –0.3 to AV $_{\rm cc}$ +0.3                                           | V    |      |

| Port 9 pin voltage          |                   | V <sub>P9</sub>  | –0.3 to $V_{cc}$ +0.3                                                 | V    |      |

| Operating temperature       |                   | $T_{opr}$        | Regular specifications:<br>-20 to +75 <sup>*2</sup>                   | °C   | —    |

|                             |                   |                  | Wide-range temperature<br>specifications:<br>-40 to +85 <sup>*3</sup> | _    |      |

|                             |                   |                  | Bare die product: +75*4                                               | _    |      |

| Storage temperature         |                   | T <sub>stg</sub> | –55 to +125                                                           | °C   |      |

Notes: 1. Permanent damage may result if maximum ratings are exceeded. Normal operation should be under the conditions specified in Electrical Characteristics. Exceeding these values can result in incorrect operation and reduced reliability.

- 2. When the operating voltage is V<sub>cc</sub> = 2.7 to 3.6 V during flash memory reading, the operating temperature ranges from -20°C to +75°C when programming or erasing the flash memory. When the operating voltage is V<sub>cc</sub> = 2.2 to 3.6 V during flash memory reading, the operating temperature ranges from -20°C to +50°C when programming or erasing the flash memory.

- 3. The operating temperature ranges from –20°C to +75°C when programming or erasing the flash memory.

- 4. The current-carrying temperature ranges from -20°C to +75°C.

|              |                                                                                                                                                      |               | Test              |     | Values | i          |               |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------------|-----|--------|------------|---------------|

| Item         |                                                                                                                                                      | Symbol        | Conditions        | Min | Тур    | Max        | Unit          |

| Programming  | y Wait time after<br>SWE-bit clear <sup>*1</sup>                                                                                                     | θ             |                   | 100 | —      | —          | μs            |

|              | Maximum<br>programming<br>count <sup>*1*4*5</sup>                                                                                                    | N             |                   | _   | _      | 1000       | times         |

| Erase        | Wait time after<br>SWE-bit setting <sup>*1</sup>                                                                                                     | х             |                   | 1   | _      |            | μs            |

|              | Wait time after<br>ESU-bit setting <sup>*1</sup>                                                                                                     | У             |                   | 100 | _      |            | μs            |

|              | Wait time after<br>E-bit setting <sup>*1*6</sup>                                                                                                     | Z             |                   | 10  | _      | 100        | ms            |

|              | Wait time after<br>E-bit clear <sup>*1</sup>                                                                                                         | α             |                   | 10  | —      | _          | μs            |

|              | Wait time after<br>ESU-bit clear <sup>*1</sup>                                                                                                       | β             |                   | 10  | _      |            | μs            |

|              | Wait time after<br>EV-bit setting <sup>*1</sup>                                                                                                      | γ             |                   | 20  | —      | _          | μs            |

|              | Wait time after dummy write <sup>*1</sup>                                                                                                            | 3             |                   | 2   | _      |            | μs            |

|              | Wait time after<br>EV-bit clear <sup>*1</sup>                                                                                                        | η             |                   | 4   | _      |            | μs            |

|              | Wait time after<br>SWE-bit clear <sup>*1</sup>                                                                                                       | θ             |                   | 100 | —      | —          | μs            |

|              | Maximum erase count <sup>*1*6*7</sup>                                                                                                                | Ν             |                   | —   | —      | 120        | times         |

| lotes: 1. Se | et the times according to                                                                                                                            | o the progran | n/erase algorithm | IS. |        |            |               |

| do           | Programming time per 128 bytes (Shows the total period for which the P bit in FLMCR1 is set. It does not include the programming verification time.) |               |                   |     |        |            |               |

| the          | Block erase time (Shows the total period for which the E bit in FLMCR1 is set. It does not include the erase verification time.)                     |               |                   |     |        |            |               |

|              | aximum programming t                                                                                                                                 |               |                   |     |        |            |               |

| F '          | max) = Wait time after<br>the maximum number of                                                                                                      | 0             | · /               |     | • • •  | et value o | f z1, z2, and |

5. The maximum number of writes (N) should be set according to the actual set value of z1, z2, and z3 to allow programming within the maximum programming time (t<sub>p</sub> (max)).

The write is a first program in the programming time (t<sub>p</sub> (max)).

The wait time after P-bit setting (z1 and z2) should be alternated according to the number of writes (n) as follows:

$1 \le n \le 6$   $z1 = 30 \ \mu s$

$7 \le n \le 1000$   $z^2 = 200 \ \mu s$

6. Maximum erase time ( $t_{E}$  (max))

$t_{_{E}}$  (max) = Wait time after E-bit setting (z) • maximum erase count (N)

- 7. The maximum number of erases (N) should be set according to the actual set value of z to allow erasing within the maximum erase time ( $t_{\epsilon}$  (max)).

- 8. This minimum value guarantees all characteristics after reprogramming (the guaranteed range is from 1 to the minimum value).

# Renesas

| Instruction | Mnemonic         | Instruction<br>Fetch | Branch<br>Addr. Read<br>J | Stack<br>Operation<br>K | • | Word Data<br>Access<br>M | Internal<br>Operation<br>N |

|-------------|------------------|----------------------|---------------------------|-------------------------|---|--------------------------|----------------------------|

| ROTXR       | ROTXR.B Rd       | 1<br>1               | J                         | ĸ                       | L | IVI                      | N                          |

| -           |                  |                      |                           |                         |   |                          |                            |

| RTE         | RTE              | 2                    |                           | 2                       |   |                          | 2                          |

| RTS         | RTS              | 2                    |                           | 1                       |   |                          | 2                          |

| SHAL        | SHAL.B Rd        | 1                    |                           |                         |   |                          |                            |

| SHAR        | SHAR.B Rd        | 1                    |                           |                         |   |                          |                            |

| SHLL        | SHLL.B Rd        | 1                    |                           |                         |   |                          |                            |

| SHLR        | SHLR.B Rd        | 1                    |                           |                         |   |                          |                            |

| SLEEP       | SLEEP            | 1                    |                           |                         |   |                          |                            |

| STC         | STC CCR, Rd      | 1                    |                           |                         |   |                          |                            |

| SUB         | SUB.B Rs, Rd     | 1                    |                           |                         |   |                          |                            |

|             | SUB.W Rs, Rd     | 1                    |                           |                         |   |                          |                            |

| SUBS        | SUBS.W #1, Rd    | 1                    |                           |                         |   |                          |                            |

|             | SUBS.W #2, Rd    | 1                    |                           |                         |   |                          |                            |

| POP         | POP Rd           | 1                    |                           | 1                       |   |                          | 2                          |

| PUSH        | PUSH Rs          | 1                    |                           | 1                       |   |                          | 2                          |

| SUBX        | SUBX.B #xx:8, Rd | 1                    |                           |                         |   |                          |                            |

|             | SUBX.B Rs, Rd    | 1                    |                           |                         |   |                          |                            |

| XOR         | XOR.B #xx:8, Rd  | 1                    |                           |                         |   |                          |                            |

|             | XOR.B Rs, Rd     | 1                    |                           |                         |   |                          |                            |

| XORC        | XORC #xx:8, CCR  | 1                    |                           |                         |   |                          |                            |

Note: n: Specified value in R4L. The source and destination operands are accessed n+1 times respectively.

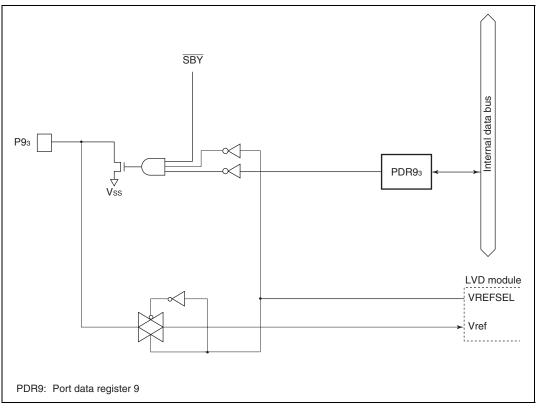

Figure B.7(c) Port 9 Block Diagram (Pin P93, H8/38104 Group Only)

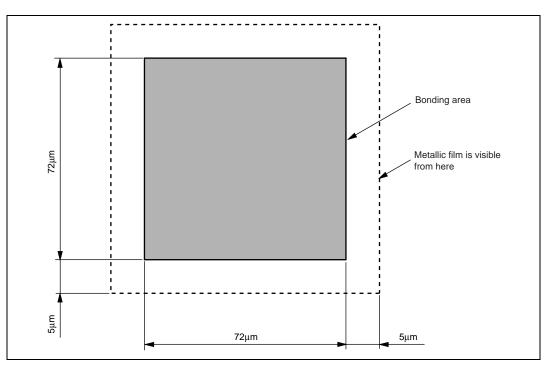

# Appendix G Bonding Pad Form

Figure G.1 Bonding Pad Form (HCD6433802, HCD6433801, HCD6433800, HCD64338004, HCD64338003, HCD64338002, HCD64338001, HCD64338000, HCD64F38004, and HCD64F38002)