#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | H8/300L                                                                    |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 10MHz                                                                      |

| Connectivity               | SCI                                                                        |

| Peripherals                | LCD, POR, PWM, WDT                                                         |

| Number of I/O              | 39                                                                         |

| Program Memory Size        | 32KB (32K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1K × 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                |

| Data Converters            | A/D 4x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-BQFP                                                                    |

| Supplier Device Package    | 64-QFP (14x14)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df38104hv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

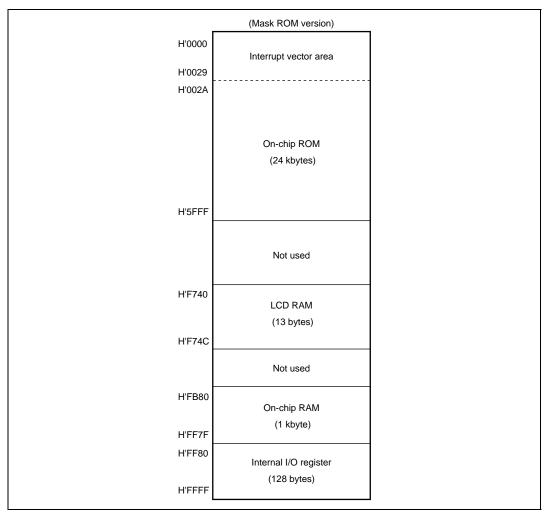

Figure 2.1(5) H8/38003, H8/38103 Memory Map

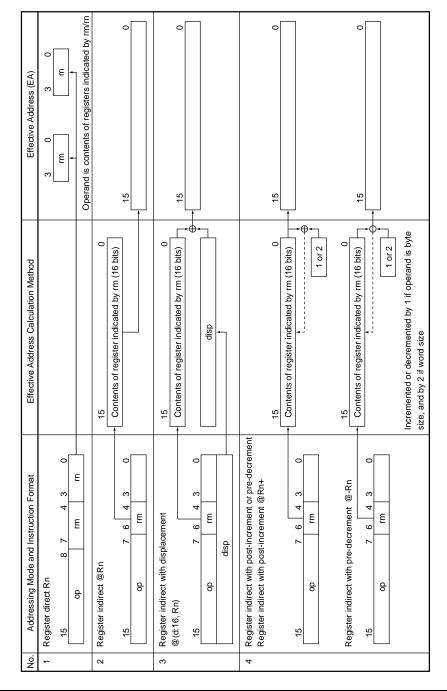

#### Table 2.12 Effective Address Calculation

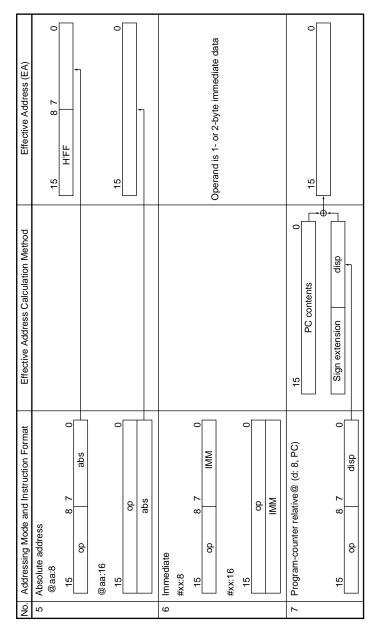

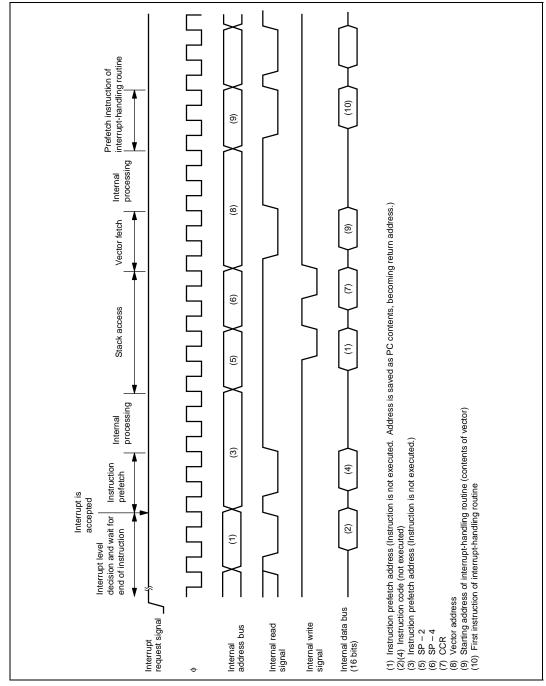

Figure 3.3 Interrupt Sequence

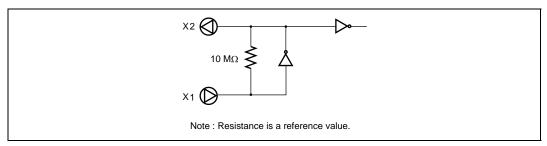

## 4.4 Subclock Generator

Figure 4.8 shows a block diagram of the subclock generator. Note that on the H8/38104 Group the subclock oscillator can be disabled by programs by setting the SUBSTP bit in the OSCCR register. The register setting to disable the subclock oscillator should be made in the active mode. When restoring operation of the subclock oscillator after it has been disabled using the OSCCR register, it is necessary to wait for the oscillation stabilization time (typ = 8s) to elapse before using the subclock.

Figure 4.8 Block Diagram of Subclock Generator

8. The maximum number of repetitions of the program/program-verify sequence of the same bit is 1,000.

#### 8.1.6 Pin Functions

The port 3 pin functions are shown below.

#### • P37/AEVL pin

The pin function depends on the combination of bit AEVL in PMR3 and bit PCR37 in PCR3.

| AEVL         | C             | 1              |                |

|--------------|---------------|----------------|----------------|

| PCR37        | 0             | 1              | *              |

| Pin Function | P37 input pin | P37 output pin | AEVL input pin |

Legend: \*: Don't care.

#### • P36/AEVH pin

The pin function depends on the combination of bit AEVH in PMR3 and bit PCR36 in PCR3.

| AEVH         | C             | 1              |                |

|--------------|---------------|----------------|----------------|

| PCR36        | 0             | *              |                |

| Pin Function | P36 input pin | P36 output pin | AEVH input pin |

Legend: \*: Don't care.

#### • P35 to P33 pins

The pin function depends on the corresponding bit in PCR3.

(n = 5 to 3)

| PCR3n        | 0             | 1              |

|--------------|---------------|----------------|

| Pin Function | P3n input pin | P3n output pin |

#### • P32/TMOFH pin

The pin function depends on the combination of bit TMOFH in PMR3 and bit PCR32 in PCR3.

| TMOFH        | C             | 1              |                  |

|--------------|---------------|----------------|------------------|

| PCR32        | 0             | *              |                  |

| Pin Function | P32 input pin | P32 output pin | TMOFH output pin |

Legend: \*: Don't care.

#### 8.5.2 Port Control Register 7 (PCR7)

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                   |

|-----|----------|------------------|-----|---------------------------------------------------------------------------------------------------------------|

| 7   | PCR77    | 0                | W   | Setting a PCR7 bit to 1 makes the corresponding pin an                                                        |

| 6   | PCR76    | 0                | W   | output pin, while clearing the bit to 0 makes the pin an                                                      |

| 5   | PCR75    | 0                | W   | input pin. The settings in PCR7 and in PDR7 are valid<br>only when the corresponding pin is designated by the |

| 4   | PCR74    | 0                | W   | SGS3 to SGS0 bits in LPCR as a general I/O pin.                                                               |

| 3   | PCR73    | 0                | W   | PCR7 is a write-only register. Bits 7 to 0 are always read                                                    |

| 2   | PCR72    | 0                | W   | as 1.                                                                                                         |

| 1   | PCR71    | 0                | W   |                                                                                                               |

| 0   | PCR70    | 0                | W   |                                                                                                               |

PCR7 controls whether each of the port 7 pins functions as an input pin or output pin.

#### 8.5.3 Pin Functions

The port 7 pin functions are shown below.

• P77/SEG24 to P74/SEG21 pins

The pin function depends on the combination of bit PCR7n in PCR7 and bits SGS3 to SGS0 in LPCR.

(n = 7 to 4)

|              |                       |                       | (                               |  |  |  |  |  |

|--------------|-----------------------|-----------------------|---------------------------------|--|--|--|--|--|

| SGS3 to      | Other than B'0110, B' | 0111, B'1000, B'1001, | B'0110, B'0111, B'1000, B'1001, |  |  |  |  |  |

| SGS0         | B'1010, B'1011,       | B'1100, B'1101        | B'1010, B'1011, B'1100, B'1101  |  |  |  |  |  |

| PCR7n        | 0                     | 1                     | *                               |  |  |  |  |  |

| Pin Function | P7n input pin         | P7n output pin        | SEGn+17 output pin              |  |  |  |  |  |

|              |                       |                       |                                 |  |  |  |  |  |

Legend: \*: Don't care.

## 8.10 Usage Notes

#### 8.10.1 How to Handle Unused Pin

If an I/O pin not used by the user system is floating, pull it up or down.

- If an unused pin is an input pin, handle it in one of the following ways:

- Pull it up to Vcc with an on-chip pull-up MOS.

- Pull it up to Vcc with an external resistor of approximately 100 k $\Omega$ .

- Pull it down to Vss with an external resistor of approximately 100 k $\Omega$ .

- For a pin also used by the A/D converter, pull it up to AVcc.

- If an unused pin is an output pin, handle it in one of the following ways:

- Set the output of the unused pin to high and pull it up to Vcc with an on-chip pull-up MOS.

- Set the output of the unused pin to high and pull it up to Vcc with an external resistor of approximately 100 k $\Omega$ .

- Set the output of the unused pin to low and pull it down to GND with an external resistor of approximately 100 k $\Omega$ .

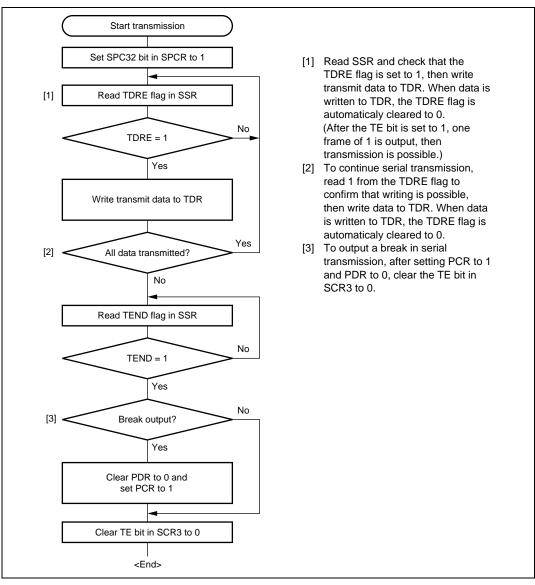

Figure 10.6 Sample Serial Transmission Flowchart (Asynchronous Mode)

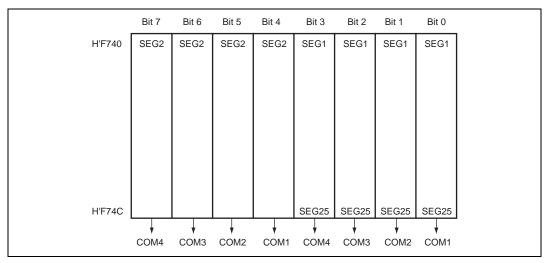

#### 13.4.2 Relationship between LCD RAM and Display

The relationship between the LCD RAM and the display segments differs according to the duty cycle. LCD RAM maps for the different duty cycles are shown in figures 13.3 to 13.6.

After setting the registers required for display, data is written to the part corresponding to the duty using the same kind of instruction as for ordinary RAM, and display is started automatically when turned on. Word- or byte-access instructions can be used for RAM setting.

Figure 13.3 LCD RAM Map (1/4 Duty)

## Renesas

# Section 14 Power-On Reset and Low-Voltage Detection Circuits (H8/38104 Group Only)

This LSI can include a power-on reset circuit.

The low-voltage detection circuit consists of two circuits: LVDI (interrupt by low voltage detect) and LVDR (reset by low voltage detect) circuits.

This circuit is used to prevent abnormal operation (runaway execution) from occurring due to the power supply voltage fall and to recreate the state before the power supply voltage fall when the power supply voltage rises again.

Even if the power supply voltage falls, the unstable state when the power supply voltage falls below the guaranteed operating voltage can be removed by entering standby mode\* when exceeding the guaranteed operating voltage and during normal operation. Thus, system stability can be improved. If the power supply voltage falls more, the reset state is automatically entered. If the power supply voltage rises again, the reset state is held for a specified period, then active mode is automatically entered.

Figure 14.1 is a block diagram of the power-on reset circuit and the low-voltage detection circuit.

Note: \* The voltage maintained in standby mode is the same as the RAM data maintenance voltage (V<sub>RAM</sub>). See section 17.6.2, DC Characteristics, for information on maintenance voltage electrical characteristics.

## 14.1 Features

• Power-on reset circuit

Uses an external capacitor to generate an internal reset signal when power is first supplied.

• Low-voltage detection circuit

LVDR: Monitors the power-supply voltage, and generates an internal reset signal when the voltage falls below a specified value.

LVDI: Monitors the power-supply voltage, and generates an interrupt when the voltage falls below or rises above respective specified values.

Two pairs of detection levels for reset generation voltage are available: when only the LVDR circuit is used, or when the LVDI and LVDR circuits are both used.

In addition, power supply rise/drop detection voltages and a detection voltage reference voltage may be input from an external source, allowing the detection level to be set freely by the user.

## Renesas

## 16.2 Register Bits

Register bit names of the on-chip peripheral modules are described below.

| Register<br>Abbreviatior | n Bit 7  | Bit 6    | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | Module<br>Name               |

|--------------------------|----------|----------|----------|----------|----------|----------|----------|----------|------------------------------|

| FLMCR1                   | _        | SWE      | ESU      | PSU      | EV       | PV       | E        | Р        | ROM                          |

| FLMCR2                   | FLER     | _        | _        | _        | _        | _        | _        | _        | -                            |

| FLPWCR                   | PDWND    | _        | _        | _        | _        | _        | _        | _        | -                            |

| EBR                      | _        | _        | _        | EB4      | EB3      | EB2      | EB1      | EB0      | -                            |

| FENR                     | FLSHE    | _        | _        | _        | _        | _        | _        | _        | -                            |

| LVDCR*4                  | LVDE     | _        | VINTDSEL | VINTUSEL | LVDSL    | LVDRE    | LVDDE    | LVDUE    | Low-                         |

| LVDSR*4                  | OVF      | _        | _        | _        | VREFSEL  | _        | LVDDF    | LVDUF    | voltage<br>detect<br>circuit |

| ECPWCRH                  | ECPWCRH  | ECPWCRH6 | ECPWCRH5 | ECPWCRH4 | ECPWCRH  | ECPWCRH2 | ECPWCRH1 | ECPWCRH0 | AEC <sup>*1</sup>            |

| ECPWCRL                  | ECPWCRL7 | ECPWCRL6 | ECPWCRL5 | ECPWCRL4 | ECPWCRL3 | ECPWCRL2 | ECPWCRL1 | ECPWCRL0 |                              |

| ECPWDRH                  | ECPWDRH7 | ECPWDRH6 | ECPWDRH5 | ECPWDRH4 | ECPWDRH  | ECPWDRH2 | ECPWDRH1 | ECPWDRH0 |                              |

| ECPWDRL                  | ECPWDRL7 | ECPWDRL6 | ECPWDRL5 | ECPWDRL4 | ECPWDRL3 | ECPWDRL2 | ECPWDRL1 | ECPWDRL0 | -                            |

| WEGR                     | WKEGS7   | WKEGS6   | WKEGS5   | WKEGS4   | WKEGS3   | WKEGS2   | WKEGS1   | WKEGS0   | Interrupts                   |

| SPCR                     | _        | _        | SPC32    | _        | SCINV3   | SCINV2   | _        | _        | SCI3                         |

| AEGSR                    | AHEGS1   | AHEGS0   | ALEGS1   | ALEGS0   | AIEGS1   | AIEGS0   | ECPWME   | _        | AEC <sup>*1</sup>            |

| ECCR                     | ACKH1    | ACKH0    | ACKL1    | ACKL0    | PWCK2    | PWCK1    | PWCK0    | _        |                              |

| ECCSR                    | OVH      | OVL      | _        | CH2      | CUEH     | CUEL     | CRCH     | CRCL     | -                            |

| ECH                      | ECH7     | ECH6     | ECH5     | ECH4     | ECH3     | ECH2     | ECH1     | ECH0     |                              |

| ECL                      | ECL7     | ECL6     | ECL5     | ECL4     | ECL3     | ECL2     | ECL1     | ECL0     | -                            |

| SMR                      | COM      | CHR      | PE       | PM       | STOP     | MP       | CKS1     | CKS0     | SCI3                         |

| BRR                      | BRR7     | BRR6     | BRR5     | BRR4     | BRR3     | BRR2     | BRR1     | BRR0     | -                            |

| SCR3                     | TIE      | RIE      | TE       | RE       | MPIE     | TEIE     | CKE1     | CKE0     | -                            |

| TDR                      | TDR7     | TDR6     | TDR5     | TDR4     | TDR3     | TDR2     | TDR1     | TDR0     | -                            |

| SSR                      | TDRE     | RDRF     | OER      | FER      | PER      | TEND     | MPBR     | MPBT     | -                            |

| RDR                      | RDR7     | RDR6     | RDR5     | RDR4     | RDR3     | RDR2     | RDR1     | RDR0     | ='                           |

| ТМА                      |          | _        | _        | _        | TMA3     | TMA2     | TMA1     | TMA0     | Timer A                      |

| TCA                      | TCA7     | TCA6     | TCA5     | TCA4     | TCA3     | TCA2     | TCA1     | TCA0     | -                            |

| TCSRW                    | B6WI     | TCWE     | B4WI     | TCSRWE   | B2WI     | WDON     | BOWI     | WRST     | WDT <sup>*2</sup>            |

| TCW                      | TCW7     | TCW6     | TCW5     | TCW4     | TCW3     | TCW2     | TCW1     | TCW0     | -                            |

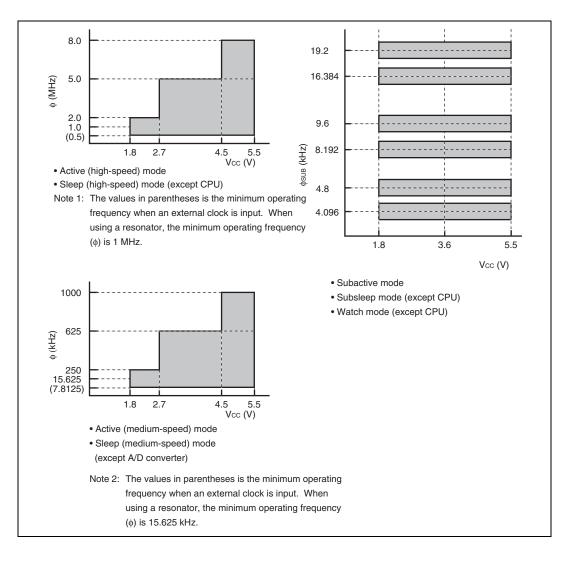

#### Power Supply Voltage and Operating Frequency Range

## Renesas

| Mode                                                | RES Pin                                | Internal State                      | Other Pins      | LCD Power<br>Supply | Oscillator Pins                    |  |

|-----------------------------------------------------|----------------------------------------|-------------------------------------|-----------------|---------------------|------------------------------------|--|

| Active (high-speed)<br>mode (I <sub>OPE1</sub> )    | eed) V <sub>cc</sub> Only CPU operates |                                     | V <sub>cc</sub> | Stops               | System clock:<br>crystal resonator |  |

| Active (medium-<br>speed) mode (I <sub>OPE2</sub> ) |                                        |                                     |                 |                     | Subclock:<br>Pin X1 = GND          |  |

| Sleep mode                                          | V <sub>cc</sub>                        | Only timers operate                 | V <sub>cc</sub> | Stops               | _                                  |  |

| Subactive mode                                      | V <sub>cc</sub>                        | Only CPU operates                   | V <sub>cc</sub> | Stops               | System clock:                      |  |

| Subsleep mode                                       | V <sub>cc</sub>                        | Only timers operate V <sub>cc</sub> |                 | Stops               | crystal resonator                  |  |

|                                                     |                                        | CPU stops                           |                 |                     | Subclock:<br>_ crystal resonator   |  |

| Watch mode                                          | V <sub>cc</sub>                        | Only clock time base operates       | V <sub>cc</sub> | Stops               |                                    |  |

|                                                     |                                        | CPU stops                           |                 |                     |                                    |  |

| Standby mode                                        | V <sub>cc</sub>                        | CPU and timers both stop            | V <sub>cc</sub> | Stops               | System clock:<br>crystal resonator |  |

|                                                     |                                        |                                     |                 |                     | Subclock:<br>Pin X1 = GND          |  |

Notes: 4. Except current which flows to the pull-up MOS or output buffer

5. When the PIOFF bit in the port mode register 9 is 0

6. When the PIOFF bit in the port mode register 9 is 1

#### **17.4.2 DC Characteristics**

Table 17.8 lists the DC characteristics.

#### Table 17.8 DC Characteristics

One of following conditions is applied unless otherwise specified.

| Condition A (F-ZTAT version): | $V_{cc} = 2.7 \text{ V to } 3.6 \text{ V}, \text{AV}_{cc} = 2.7 \text{ V to } 3.6 \text{ V},$<br>$V_{ss} = \text{AV}_{ss} = 0.0 \text{ V}$ |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Condition B (F-ZTAT version): | $V_{cc} = 2.2 \text{ V to } 3.6 \text{ V}, \text{AV}_{cc} = 2.2 \text{ V to } 3.6 \text{ V},$<br>$V_{ss} = \text{AV}_{ss} = 0.0 \text{ V}$ |

Condition C (Mask ROM version):  $V_{cc} = 1.8$  V to 3.6 V,  $AV_{cc} = 1.8$  V to 3.6 V,  $V_{ss} = AV_{ss} = 0.0$  V

|                       |                 |                                                                                               |                           |                     | Values | ;                         |      |       |

|-----------------------|-----------------|-----------------------------------------------------------------------------------------------|---------------------------|---------------------|--------|---------------------------|------|-------|

| Item                  | Symbol          | Applicable Pins                                                                               | Test Condition            | Min                 | Тур    | Max                       | Unit | Notes |

| Input high<br>voltage | V <sub>IH</sub> | RES,<br>WKP0 to WKP7,<br>IRQ0, AEVL,<br>AEVH, SCK32                                           |                           | $V_{cc} \times 0.9$ | _      | V <sub>cc</sub> +<br>0.3  | V    |       |

|                       |                 | IRQ1                                                                                          |                           | $V_{cc} 	imes 0.9$  | —      | AV <sub>cc</sub> +<br>0.3 | V    |       |

|                       |                 | RXD32                                                                                         |                           | $V_{cc} 	imes 0.8$  | —      | V <sub>cc</sub> +<br>0.3  | V    |       |

|                       |                 | OSC1                                                                                          |                           | $V_{cc} 	imes 0.9$  | —      | V <sub>cc</sub> +<br>0.3  | V    |       |

|                       |                 | X1                                                                                            | $V_{cc}$ = 1.8 V to 5.5 V | $V_{cc} \times 0.9$ |        | V <sub>cc</sub> +<br>0.3  | V    |       |

|                       |                 | P31 to P37,<br>P40 to P43,<br>P50 to P57,<br>P60 to P67,<br>P70 to P77,<br>P80,<br>PA0 to PA3 |                           | $V_{cc} \times 0.8$ | _      | V <sub>cc</sub> +<br>0.3  | V    |       |

|                       |                 | PB0 to PB3                                                                                    |                           | $V_{cc} \times 0.8$ | _      | AV <sub>cc</sub> +<br>0.3 | V    |       |

|                       |                 | IRQAEC, P95 <sup>*₅</sup>                                                                     |                           | $V_{cc} \times 0.9$ | _      | V <sub>cc</sub> + 0.3     | V    |       |

#### 17.6.5 LCD Characteristics

Table 17.20 shows the LCD characteristics.

#### Table 17.20 LCD Characteristics

$V_{cc} = 2.7 \text{ V}$  to 5.5 V,  $AV_{cc} = 2.7 \text{ V}$  to 5.5 V,  $V_{ss} = AV_{ss} = 0.0 \text{ V}$ , unless otherwise specified

|                                   |                  | Applicable                               |                                            |     | Value | s   |      | Reference |

|-----------------------------------|------------------|------------------------------------------|--------------------------------------------|-----|-------|-----|------|-----------|

| Item                              | Symbol           | Pins                                     | Test Condition                             | Min | Тур   | Max | Unit | Figure    |

| Segment driver step-down voltage  | V <sub>DS</sub>  | SEG <sub>1</sub> to<br>SEG <sub>25</sub> | $I_{D} = 2 \ \mu A$<br>V1 = 2.7 V to 5.5 V | _   | —     | 0.6 | V    | *1        |

| Common driver step-down voltage   | V <sub>DC</sub>  | COM₁ to<br>COM₄                          | $I_{D} = 2 \mu A$<br>V1 = 2.7 V to 5.5 V   | —   | _     | 0.3 | V    | *1        |

| LCD power supply split-resistance | $R_{\text{lcd}}$ |                                          | Between V1 and $V_{ss}$                    | 1.5 | 3.0   | 7.0 | MΩ   |           |

| Liquid crystal<br>display voltage | $V_{\rm LCD}$    | V <sub>1</sub>                           |                                            | 2.7 | —     | 5.5 | V    | *2        |

Notes: 1. The voltage step-down from power supply pins V1, V2, V3, and V<sub>ss</sub> to each segment pin or common pin.

2. When the liquid crystal display voltage is supplied from an external power supply, ensure that the following relationship is maintained:  $V_{cc} \ge V1 \ge V2 \ge V3 \ge V_{ss}$ .

| Number<br>of Execution<br>States            |             | 4       | 9          | 8          | 9       |        |           | 9       |        |         | 8          |        |          | 8          |        |          | 8      |         | 10                |         |        |         |

|---------------------------------------------|-------------|---------|------------|------------|---------|--------|-----------|---------|--------|---------|------------|--------|----------|------------|--------|----------|--------|---------|-------------------|---------|--------|---------|

| Condition Code                              | U           | Ι       | Ι          | Ι          | Ι       |        |           | Ι       |        |         | Ι          |        |          | Ι          |        |          | Ι      |         | ↔                 |         |        |         |

|                                             | >           | Ι       | Ι          | Ι          | Ι       |        |           | Ι       |        |         | Ι          |        |          |            |        |          | Ι      |         | ↔                 |         |        |         |

|                                             | Ν           | I       |            |            |         |        |           |         |        |         |            |        |          |            |        |          |        |         | ↔                 |         |        |         |

|                                             | z           | Ι       | Ι          | Ι          | Ι       |        |           | Ι       |        |         | Ι          |        |          |            |        |          | Ι      |         | ↔                 |         |        |         |

|                                             | т           |         | 1          |            |         |        |           |         |        |         |            |        |          |            |        |          |        |         | ↔                 |         |        |         |

|                                             | -           | Ι       | Ι          | Ι          |         |        |           | Ι       |        |         | Ι          |        |          | Ι          |        |          | Ι      |         | $\leftrightarrow$ |         |        |         |

| Operation                                   |             | PC←Rn16 | PC← aa:16  | PC←@aa:8   | SP-2→SP | PC→@SP | PC←PC+d:8 | SP-2→SP | PC→@SP | PC←Rn16 | SP-2→SP    | PC→@SP | PC←aa:16 | SP-2→SP    | PC→@SP | PC←@aa:8 | PC←@SP | SP+2→SP | CCR←@SP           | SP+2→SP | PC←@SP | SP+2→SP |

|                                             | Ι           |         |            |            |         |        |           |         |        |         |            |        |          |            |        |          | 2      |         | 2                 |         |        |         |

|                                             | @ @ aa      |         |            | 2          |         |        |           |         |        |         |            |        |          | 2          |        |          |        |         |                   |         |        |         |

| Addressing Modes/Instruction Length (bytes) | @(d:8, PC)  |         |            |            | 2       |        |           |         |        |         |            |        |          |            |        |          |        |         |                   |         |        |         |

|                                             | @aa:8/16    |         | 4          |            |         |        |           |         |        |         | 4          |        |          |            |        |          |        |         |                   |         |        |         |

|                                             | @-Rn/@Rn+   |         |            |            |         |        |           |         |        |         |            |        |          |            |        |          |        |         |                   |         |        |         |

| ddressing Mo                                | @(d:16, Rn) |         |            |            |         |        |           |         |        |         |            |        |          |            |        |          |        |         |                   |         |        |         |

| A                                           | @Rn         | 2       |            |            |         |        |           | 2       |        |         |            |        |          |            |        |          |        |         |                   |         |        |         |

|                                             | Rn          |         |            |            |         |        |           |         |        |         |            |        |          |            |        |          |        |         |                   |         |        |         |

|                                             | #xx:8/16    |         |            |            |         |        |           |         |        |         |            |        |          |            |        |          |        |         |                   |         |        |         |

| Size<br>Size                                | 10          | Ι       |            |            |         |        |           | Ι       |        |         |            |        |          |            |        |          |        |         | Ι                 |         |        |         |

| Mnemonic                                    |             | JMP @Rn | JMP @aa:16 | JMP @@aa:8 | BSR d:8 |        |           | JSR @Rn |        |         | JSR @aa:16 |        |          | JSR @@aa:8 |        |          | RTS .  |         | RTE .             |         |        |         |

|                                             |             | AML     |            |            | BSR     |        |           | JSR     |        |         |            |        |          |            |        |          | RTS    |         | RTE               |         |        |         |

## Appendix A Instruction Set

| Product Typ | be       |                                             | Part No.       | Model Marking  | Package<br>(Package Code) |  |  |  |  |

|-------------|----------|---------------------------------------------|----------------|----------------|---------------------------|--|--|--|--|

| H8/38002S   | Mask ROM | Regular                                     | HD64338002SH   | 38002 (***) H  | 64-pin QFP (FP-64A)       |  |  |  |  |

|             | version  | product                                     | HD64338002SFZ  | 38002 (***)    | 64-pin LQFP (FP-64K)      |  |  |  |  |

|             |          |                                             | HD64338002SFT  | 38002 (***) FT | 64-pin QFP (TNP-64B)      |  |  |  |  |

|             |          | Product with                                | HD64338002SHW  | 38002 (***) H  | 64-pin QFP (FP-64A)       |  |  |  |  |

|             |          | wide-range<br>temperature<br>specifications | HD64338002SFZW | 38002 (***)    | 64-pin LQFP (FP-64K)      |  |  |  |  |

|             |          |                                             | HD64338002SFTW | 38002 (***) FT | 64-pin QFP (TNP-64B)      |  |  |  |  |

| H8/38001S   | Mask ROM | Regular                                     | HD64338001SH   | 38001 (***) H  | 64-pin QFP (FP-64A)       |  |  |  |  |

|             | version  | product                                     | HD64338001SFZ  | 38001 (***)    | 64-pin LQFP (FP-64K)      |  |  |  |  |

|             |          |                                             | HD64338001SFT  | 38001 (***) FT | 64-pin QFP (TNP-64B)      |  |  |  |  |

|             |          | Product with                                | HD64338001SHW  | 38001 (***) H  | 64-pin QFP (FP-64A)       |  |  |  |  |

|             |          | wide-range<br>temperature                   | HD64338001SFZW | 38001 (***)    | 64-pin LQFP (FP-64K)      |  |  |  |  |

|             |          | specifications                              | HD64338001SFTW | 38001 (***) FT | 64-pin QFP (TNP-64B)      |  |  |  |  |

| H8/38000S   | Mask ROM | Regular                                     | HD64338000SH   | 38000 (***) H  | 64-pin QFP (FP-64A)       |  |  |  |  |

|             | version  | product                                     | HD64338000SFZ  | 38000 (***)    | 64-pin LQFP (FP-64K)      |  |  |  |  |

|             |          |                                             | HD64338000SFT  | 38000 (***) FT | 64-pin QFP (TNP-64B)      |  |  |  |  |

|             |          | Product with                                | HD64338000SHW  | 38000 (***) H  | 64-pin QFP (FP-64A)       |  |  |  |  |

|             |          | wide-range<br>temperature                   | HD64338000SFZW | 38000 (***)    | 64-pin LQFP (FP-64K)      |  |  |  |  |

|             |          | specifications                              | HD64338000SFTW | 38000 (***) FT | 64-pin QFP (TNP-64B)      |  |  |  |  |

### Table D.3 Product Code Lineup of H8/38002S Group

Legend:

(\*\*\*): ROM code