Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                |

| Core Processor             | AVR                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 8MHz                                                                    |

| Connectivity               | SPI, UART/USART                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 20                                                                      |

| Program Memory Size        | 4KB (2K × 16)                                                           |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 256 x 8                                                                 |

| RAM Size                   | 128 × 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                 |

| Data Converters            | A/D 6x10b                                                               |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 85°C                                                            |

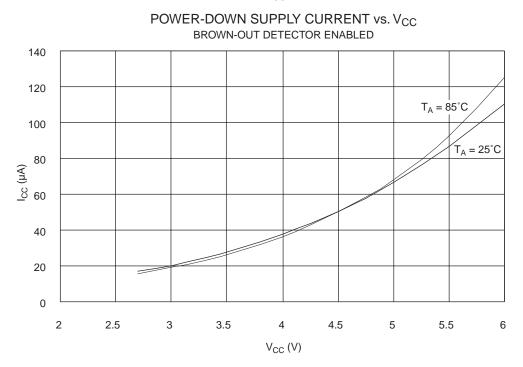

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                 |

| Supplier Device Package    | 28-PDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at90s4433-8pi |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

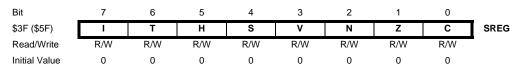

#### Status Register – SREG

The AVR Status Register (SREG) at I/O space location \$3F (\$5F) is defined as:

#### • Bit 7 – I: Global Interrupt Enable

The Global Interrupt Enable bit must be set (one) for the interrupts to be enabled. The individual interrupt enable control is then performed in separate control registers. If the Global Interrupt Enable Register is cleared (zero), none of the interrupts are enabled independent of the individual interrupt enable settings. The I-bit is cleared by hardware after an interrupt has occurred and is set by the RETI instruction to enable subsequent interrupts.

#### • Bit 6 – T: Bit Copy Storage

The Bit Copy Instructions BLD (Bit LoaD) and BST (Bit STore) use the T-bit as source and destination for the operated bit. A bit from a register in the Register File can be copied into T by the BST instruction, and a bit in T can be copied into a bit in a register in the Register File by the BLD instruction.

#### • Bit 5 – H: Half Carry Flag

The Half Carry Flag H indicates a Half Carry in some arithmetical operations. See the Instruction Set description for detailed information.

#### • Bit 4 – S: Sign Bit, S = N ⊕ V

The S-bit is always an exclusive or between the Negative Flag N and the Two's Complement Overflow Flag V. See the Instruction Set description for detailed information.

#### • Bit 3 – V: Two's Complement Overflow Flag

The Two's Complement Overflow Flag V supports two's complement arithmetics. See the Instruction Set description for detailed information.

#### • Bit 2 – N: Negative Flag

The Negative Flag N indicates a negative result from an arithmetical or logical operation. See the Instruction Set description for detailed information.

#### • Bit 1 – Z: Zero Flag

The Zero Flag Z indicates a zero result from an arithmetical or logical operation. See the Instruction Set description for detailed information.

#### • Bit 0 – C: Carry Flag

The Carry Flag C indicates a carry in an arithmetical or logical operation. See the Instruction Set description for detailed information.

Note that the Status Register is not automatically stored when entering an interrupt routine and restored when returning from an interrupt routine. This must be handled by software.

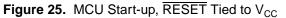

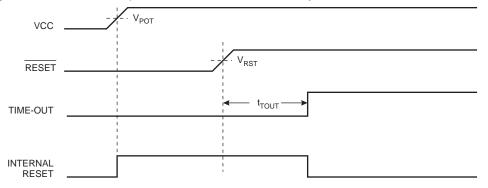

#### Figure 26. MCU Start-up, RESET Controlled Externally

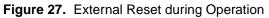

#### **External Reset**

An External Reset is generated by a low level on the RESET pin. Reset pulses longer than 50 ns will generate a Reset, even if the clock is not running. Shorter pulses are not guaranteed to generate a Reset. When the applied signal reaches the Reset Threshold Voltage ( $V_{RST}$ ) on its positive edge, the delay timer starts the MCU after the Time-out period ( $t_{TOUT}$ ) has expired.

| Idle Mode       | When the SM bit is cleared (zero), the SLEEP instruction forces the MCU into the Idle mode stopping the CPU but allowing Timer/Counters, Watchdog and the interrupt system to continue operating. This enables the MCU to wake up from external triggered interrupts as well as internal ones like Timer Overflow interrupt and Watchdog Reset. If wake-up from the Analog Comparator interrupt is not required, the Analog Comparator can be powered down by setting the ACD bit in the Analog Comparator Control and Status Register (ACSR). This will reduce power consumption in Idle mode.                                                                                                                           |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

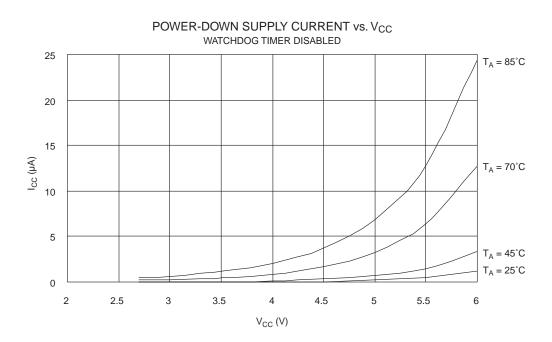

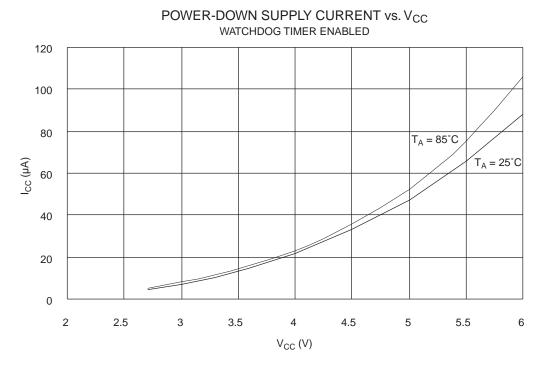

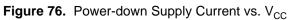

| Power-down Mode | When the SM bit is set (one), the SLEEP instruction forces the MCU into the Power-<br>down mode. In this mode, the External Oscillator is stopped while the external interrupts<br>and the Watchdog (if enabled) continue operating. Only an External Reset, a Watchdog<br>Reset (if enabled) or an external level interrupt can wake up the MCU.                                                                                                                                                                                                                                                                                                                                                                         |

|                 | Note that if a level-triggered interrupt is used for wake-up from Power-down mode, the changed level must be held for a time to wake up the MCU. This makes the MCU less sensitive to noise. The Wake-up period is equal to the clock-counting part of the Reset period (see Table 5). The MCU will wake up from Power-down if the input has the required level for two Watchdog Oscillator cycles. If the wake-up period is shorter than two Watchdog Oscillator cycles, the MCU will wake up if the input has the required level for the Wake-up period. If the wake-up condition disappears before the wake-up period has expired, the MCU will wake up from Power-down without executing the corresponding interrupt. |

|                 | The period of the Watchdog Oscillator is 2.7 $\mu$ s (nominal) at 3.0V and 25°C. The fre-<br>quency of the Watchdog Oscillator is voltage dependent as shown in the Electrical<br>Characteristics section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                 | When waking up from Power-down mode, a delay from the wake-up condition occurs<br>until the wake-up becomes effective. This allows the clock to restart and become stable<br>after having been stopped. The wake-up period is defined by the same CKSEL Fuses<br>that define the Reset Time-out period.                                                                                                                                                                                                                                                                                                                                                                                                                   |

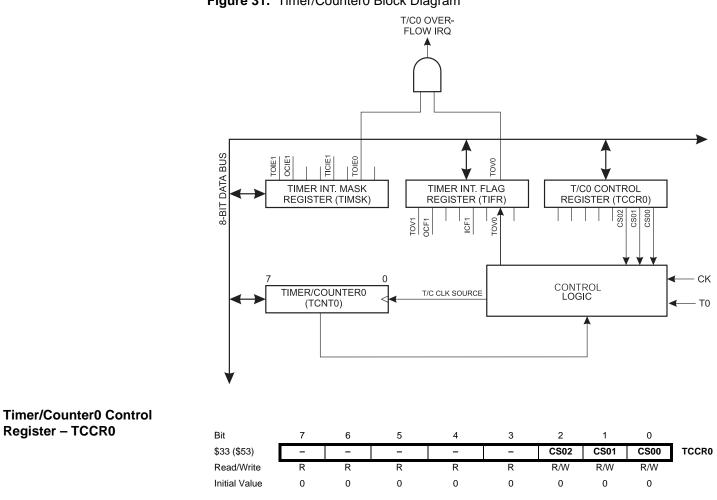

#### • Bits 7 - 3 - Res: Reserved Bits

These bits are reserved bits in the AT90S4433 and always read as zero.

#### • Bits 2, 1, 0 - CS02, CS01, CS00: Clock Select0, Bits 2, 1, and 0

The Clock Select0 bits 2, 1, and 0 define the prescaling source of Timer/Counter0.

| Table 9. | Clock 0 | Prescale | Select |

|----------|---------|----------|--------|

|----------|---------|----------|--------|

| CS02 | CS01 | CS00 | Description                      |

|------|------|------|----------------------------------|

| 0    | 0    | 0    | Stop, Timer/Counter0 is stopped. |

| 0    | 0    | 1    | СК                               |

| 0    | 1    | 0    | СК/8                             |

| 0    | 1    | 1    | CK/64                            |

| 1    | 0    | 0    | CK/256                           |

| 1    | 0    | 1    | CK/1024                          |

| 1    | 1    | 0    | External Pin T0, falling edge    |

| 1    | 1    | 1    | External Pin T0, rising edge     |

Register – TCCR0

# AT90S/LS4433

#### Timer/Counter1 Control Register A – TCCR1A

| Bit           | 7     | 6     | 5 | 4 | 3 | 2 | 1     | 0     |        |

|---------------|-------|-------|---|---|---|---|-------|-------|--------|

| \$2F (\$4F)   | COM11 | COM10 | - | - | - | - | PWM11 | PWM10 | TCCR1A |

| Read/Write    | R/W   | R/W   | R | R | R | R | R/W   | R/W   |        |

| Initial Value | 0     | 0     | 0 | 0 | 0 | 0 | 0     | 0     |        |

## • Bits 7, 6 – COM11, COM10: Compare Output Mode1, Bits 1, and 0

The COM11 and COM10 control bits determine any output pin action following a Compare Match in Timer/Counter1. Any output pin actions affect pin OC1 (Output Compare pin 1). This is an alternative function to an I/O port, and the corresponding direction control bit must be set (one) to control an output pin. The control configuration is shown in Table 10.

### Table 10. Compare 1 Mode Select

| COM11 | COM10 | Description                                     |  |  |  |

|-------|-------|-------------------------------------------------|--|--|--|

| 0     | 0     | Timer/Counter1 disconnected from output pin OC1 |  |  |  |

| 0     | 1     | Toggle the OC1 output line.                     |  |  |  |

| 1     | 0     | Clear the OC1 output line (to zero).            |  |  |  |

| 1     | 1     | Set the OC1 output line (to one).               |  |  |  |

In PWM mode, these bits have a different function. Refer to Table 11 for a detailed description.

## • Bits 5..2 - Res: Reserved Bits

These bits are reserved bits in the AT90S4433 and always read as zero.

## • Bits 1, 0 – PWM11, PWM10: Pulse Width Modulator Select Bits

These bits select PWM operation of Timer/Counter1 as specified in Table 11. This mode is described on page 41.

Table 11.

PWM Mode Select

| PWM11 | PWM10 | Description                                 |

|-------|-------|---------------------------------------------|

| 0     | 0     | PWM operation of Timer/Counter1 is disabled |

| 0     | 1     | Timer/Counter1 is an 8-bit PWM              |

| 1     | 0     | Timer/Counter1 is a 9-bit PWM               |

| 1     | 1     | Timer/Counter1 is a 10-bit PWM              |

#### • Bit 3 – TXEN: Transmitter Enable

This bit enables the UART Transmitter when set (one). When disabling the Transmitter while transmitting a character, the Transmitter is not disabled before the character in the Shift Register plus any following character in UDR has been completely transmitted.

#### • Bit 2 – CHR9: 9-bit Characters

When this bit is set (one), transmitted and received characters are nine bits long, plus start and stop bits. The ninth bit is read and written by using the RXB8 and TXB8 bits in UCSRB, respectively. The ninth data bit can be used as an extra stop bit or a parity bit.

#### • Bit 1 – RXB8: Receive Data Bit 8

When CHR9 is set (one), RXB8 is the ninth data bit of the received character.

#### • Bit 0 – TXB8: Transmit Data Bit 8

When CHR9 is set (one), TXB8 is the ninth data bit in the character to be transmitted.

**Baud Rate Generator** The Baud Rate Generator is a frequency divider, which generates baud rates according to the following equation:

$$\mathsf{BAUD} = \frac{f_{\mathsf{CK}}}{16(\mathsf{UBR}+1)}$$

- BAUD = Baud Rate

- f<sub>CK</sub>= Crystal Clock frequency

- UBR = Contents of the UBRRHI and UBRR Registers, (0 4095)

For standard crystal frequencies, the most commonly used baud rates can be generated by using the UBR settings in Table 19. UBR values that yield an actual baud rate differing less than 2% from the target baud rate are boldface in the table. However, using baud rates that have more than 1% error is not recommended. High error ratings give less noise resistance.

#### ADC Multiplexer Select Register – ADMUX

| Bit           | 7 | 6     | 5 | 4 | 3 | 2    | 1    | 0    | _     |

|---------------|---|-------|---|---|---|------|------|------|-------|

| \$07 (\$27)   | - | ADCBG | - | - | - | MUX2 | MUX1 | MUX0 | ADMUX |

| Read/Write    | R | R/W   | R | R | R | R/W  | R/W  | R/W  | •     |

| Initial Value | 0 | 0     | 0 | 0 | 0 | 0    | 0    | 0    |       |

#### • Bit 7 – Res: Reserved Bit

This bit is a reserved bit in the AT90S4433, and should be written to zero if accessed.

#### • Bit 6 – ADCBG: ADC Bandgap Select

When this bit is set and the BOD is enabled (BODEN Fuse is programmed), a fixed bandgap voltage of  $1.22V \pm 0.1V$  replaces the normal input to the ADC. When this bit is cleared, the normal input pin (as selected by MUX2..MUX0) is applied to the ADC.

#### • Bits 5..3 - Res: Reserved Bits

These bits are reserved bits in the AT90S4433, and should be written to zero if accessed.

#### • Bits 2..0 – MUX2..MUX0: Analog Channel Select Bits 2 - 0

The value of these three bits selects which analog input 5 - 0 is connected to the ADC.

#### ADC Control and Status Register – ADCSR

| Bit           | 7    | 6    | 5    | 4    | 3    | 2     | 1     | 0     |       |

|---------------|------|------|------|------|------|-------|-------|-------|-------|

| \$06 (\$26)   | ADEN | ADSC | ADFR | ADIF | ADIE | ADPS2 | ADPS1 | ADPS0 | ADCSR |

| Read/Write    | R/W  | R/W  | R/W  | R/W  | R/W  | R/W   | R/W   | R/W   |       |

| Initial Value | 0    | 0    | 0    | 0    | 0    | 0     | 0     | 0     |       |

#### • Bit 7 – ADEN: ADC Enable

Writing a logical "1" to this bit enables the ADC. By clearing this bit to zero, the ADC is turned off. Turning the ADC off while a conversion is in progress will terminate this conversion.

#### • Bit 6 – ADSC: ADC Start Conversion

In Single Conversion mode, a logical "1" must be written to this bit to start each conversion. In Free Run mode, a logical "1" must be written to this bit to start the first conversion. The first time ADSC has been written after the ADC has been enabled, or if ADSC is written at the same time as the ADC is enabled, a dummy conversion will precede the initiated conversion. This dummy conversion performs initialization of the ADC.

ADSC remains high during the conversion. ADSC goes low after the conversion is complete, but before the result is written to the ADC Data Registers. This allows a new conversion to be initiated before the current conversion is complete. The new conversion will then start immediately after the current conversion completes. When a dummy conversion precedes a real conversion, ADSC will stay high until the real conversion completes.

Writing a "0" to this bit has no effect.

# **AMEL**

# Scanning Multiple Channels

Since change of analog channel always is delayed until a conversion is finished, the Free Run mode can be used to scan multiple channels without interrupting the converter. Typically, the ADC Conversion Complete interrupt will be used to perform the channel shift. However, the user should take the following fact into consideration: The interrupt triggers once the result is ready to be read. In Free Run mode, the next conversion will start immediately when the interrupt triggers. If ADMUX is changed after the interrupt triggers, the next conversion has already started and the old setting is used.

# ADC Noise Canceling Techniques

Digital circuitry inside and outside the AT90S4433 generates EMI, which might affect the accuracy of analog measurements. If conversion accuracy is critical, the noise level can be reduced by applying the following techniques:

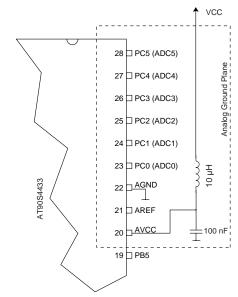

- 1. The analog part of the AT90S4433 and all analog components in the application should have a separate analog ground plane on the PCB. This ground plane is connected to the digital ground plane via a single point on the PCB.

- 2. Keep analog signal paths as short as possible. Make sure analog tracks run over the analog ground plane and keep them well away from high-speed switching digital tracks.

- 3. The AVCC pin on the AT90S4433 should be connected to the digital  $V_{CC}$  supply voltage via an LC network as shown in Figure 49.

- 4. Use the ADC Noise Canceler function to reduce induced noise from the CPU.

- 5. If some Port C pins are used as digital outputs, it is essential that these do not switch while a conversion is in progress.

Figure 49. ADC Power Connections

Note that since AVCC feeds the Port C output drivers, the RC network shown should not be employed if any Port C serve as outputs.

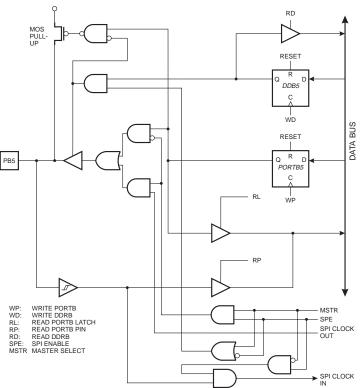

The Port B Input Pins address (PINB) is not a register; this address enables access to the physical value on each Port B pin. When reading PORTB, the Port B Data Latch is read, and when reading PINB, the logical values present on the pins are read.

**Port B as General Digital I/O** All six pins in Port B have equal functionality when used as digital I/O pins.

PBn, general I/O pin: The DDBn bit in the DDRB Register selects the direction of this pin. If DDBn is set (one), PBn is configured as an output pin. If DDBn is cleared (zero), PBn is configured as an input pin. If PORTBn is set (one) when the pin is configured as an input pin, the MOS pull-up resistor is activated. To switch the pull-up resistor off, the PORTBn has to be cleared (zero) or the pin has to be configured as an output pin. The port pins are tri-stated when a reset condition becomes active, even if the clock is not running.

| DDBn | PORTBn | I/O    | Pull-up | Comment                                     |

|------|--------|--------|---------|---------------------------------------------|

| 0    | 0      | Input  | No      | Tri-state (high-Z)                          |

| 0    | 1      | Input  | Yes     | PBn will source current if ext. pulled low. |

| 1    | 0      | Output | No      | Push-pull Zero Output                       |

| 1    | 1      | Output | No      | Push-pull One Output                        |

Table 24. DDBn Effects on Port B Pins<sup>(1)</sup>

Note: 1. n: 5..0, pin number.

Alternate Functions of Port B The alternate pin configuration is as follows:

#### • SCK – Port B, Bit 5

SCK: Master Clock output, Slave Clock input pin for SPI channel. When the SPI is enabled as a Slave, this pin is configured as an input, regardless of the setting of DDB5. When the SPI is enabled as a Master, the data direction of this pin is controlled by DDB5. When the pin is forced to be an input, the pull-up can still be controlled by the PORTB5 bit. See the description of the SPI port for further details.

#### • MISO - Port B, Bit 4

MISO: Master Data input, Slave Data output pin for SPI channel. When the SPI is enabled as a Master, this pin is configured as an input, regardless of the setting of DDB4. When the SPI is enabled as a Slave, the data direction of this pin is controlled by DDB4. When the pin is forced to be an input, the pull-up can still be controlled by the PORTB4 bit. See the description of the SPI port for further details.

#### • MOSI - Port B, Bit 3

MOSI: SPI Master Data output, Slave Data input for SPI channel. When the SPI is enabled as a Slave, this pin is configured as an input, regardless of the setting of DDB3. When the SPI is enabled as a Master, the data direction of this pin is controlled by DDB3. When the pin is forced to be an input, the pull-up can still be controlled by the PORTB3 bit. See the description of the SPI port for further details.

#### • SS – Port B, Bit 2

SS: Slave Port Select input. When the SPI is enabled as a Slave, this pin is configured as an input, regardless of the setting of DDB2. As a Slave, the SPI is activated when this pin is driven low. When the SPI is enabled as a Master, the data direction of this pin is

Port C

Port C is a 6-bit bi-directional I/O port.

Three I/O memory address locations are allocated for the Port C, one each for the Data Register – PORTC, \$15(\$35), Data Direction Register – DDRC, \$14(\$34), and the Port C Input Pins – PINC, \$13(\$33). The Port C Input Pins address is read only, while the Data Register and the Data Direction Register are read/write.

All port pins have individually selectable pull-up resistors. The Port C output buffers can sink 20 mA and thus drive LED displays directly. When pins PC0 to PC5 are used as inputs and are externally pulled low, they will source current if the internal pull-up resistors are activated.

Port C has an alternate function as analog inputs for the ADC. If some Port C pins are configured as outputs, it is essential that these do not switch when a conversion is in progress. This might corrupt the result of the conversion.

During Power-down mode, the Schmitt triggers of the digital inputs are disconnected. This allows an analog voltage close to  $V_{CC}/2$  to be present during Power-down without causing excessive power consumption.

#### Port C Data Register – PORTC

|                                | Bit                                      | 7          | 6        | 5         | 4          | 3       | 2         | 1           | 0         |       |

|--------------------------------|------------------------------------------|------------|----------|-----------|------------|---------|-----------|-------------|-----------|-------|

|                                | \$15 (\$35)                              | -          | -        | PORTC5    | PORTC4     | PORTC3  | PORTC2    | PORTC1      | PORTC0    | PORTC |

|                                | Read/Write                               | R          | R        | R/W       | R/W        | R/W     | R/W       | R/W         | R/W       |       |

|                                | Initial Value                            | 0          | 0        | 0         | 0          | 0       | 0         | 0           | 0         |       |

| Port C Data Direction Register |                                          |            |          |           |            |         |           |             |           |       |

| – DDRC                         | Bit                                      | 7          | 6        | 5         | 4          | 3       | 2         | 1           | 0         | _     |

|                                | \$14 (\$34)                              | -          | -        | DDC5      | DDC4       | DDC3    | DDC2      | DDC1        | DDC0      | DDRC  |

|                                | Read/Write                               | R          | R        | R/W       | R/W        | R/W     | R/W       | R/W         | R/W       | •     |

|                                | Initial Value                            | 0          | 0        | 0         | 0          | 0       | 0         | 0           | 0         |       |

| Port C Input Pins Address –    |                                          |            |          |           |            |         |           |             |           |       |

| PINC                           | Bit                                      | 7          | 6        | 5         | 4          | 3       | 2         | 1           | 0         |       |

|                                | \$13 (\$33)                              | -          | -        | PINC5     | PINC4      | PINC3   | PINC2     | PINC1       | PINC0     | PINC  |

|                                | Read/Write                               | R          | R        | R         | R          | R       | R         | R           | R         |       |

|                                | Initial Value                            | 0          | 0        | N/A       | N/A        | N/A     | N/A       | N/A         | N/A       |       |

|                                | The Port C<br>the physica<br>read, and w | il value o | on each  | Port C p  | in. When   | reading | PORTC     | , the Po    | rt C Data |       |

| Port C as General Digital I/O  | All six pins                             | in Port C  | C have e | qual fund | ctionality | when us | ed as dię | gital I/O p | pins.     |       |

PCn, general I/O pin: The DDCn bit in the DDRC Register selects the direction of this pin. If DDCn is set (one), PCn is configured as an output pin. If DDCn is cleared (zero), PCn is configured as an input pin. If PORTCn is set (one) when the pin is configured as an input pin, the MOS pull-up resistor is activated. To switch the pull-up resistor off, PORTCn has to be cleared (zero) or the pin has to be configured as an output pin. The port pins are tri-stated when a reset condition becomes active, even if the clock is not running.

| DDCn | PORTCn | I/O    | Pull-up | Comment                                     |

|------|--------|--------|---------|---------------------------------------------|

| 0    | 0      | Input  | No      | Tri-state (high-Z)                          |

| 0    | 1      | Input  | Yes     | PCn will source current if ext. pulled low. |

| 1    | 0      | Output | No      | Push-pull Zero Output                       |

| 1    | 1      | Output | No      | Push-pull One Output                        |

#### Table 25. DDCn Effects on Port C Pins<sup>(1)</sup>

Note: 1. n: 5..0, pin number

### Port D

Port D is an 8-bit bi-directional I/O port with internal pull-up resistors.

Three I/O memory address locations are allocated for Port D, one each for the Data Register – PORTD, \$12(\$32), Data Direction Register – DDRD, \$11(\$31), and the Port D Input Pins – PIND, \$10(\$30). The Port D Input Pins address is read only, while the Data Register and the Data Direction Register are read/write.

The Port D output buffers can sink 20 mA. As inputs, Port D pins that are externally pulled low will source current if the pull-up resistors are activated.

Some Port D pins have alternate functions as shown in Table 26.

| Port Pin | Alternate Function                             |  |  |  |  |  |

|----------|------------------------------------------------|--|--|--|--|--|

| PD0      | RXD (UART Input Line)                          |  |  |  |  |  |

| PD1      | TXD (UART Output Line)                         |  |  |  |  |  |

| PD2      | PD2 INT0 (External Interrupt 0 Input)          |  |  |  |  |  |

| PD3      | INT1 (External Interrupt 1 Input)              |  |  |  |  |  |

| PD4      | D4 T0 (Timer/Counter 0 External Counter Input) |  |  |  |  |  |

| PD5      | T1 (Timer/Counter 1 External Counter Input)    |  |  |  |  |  |

| PD6      | AIN0 (Analog Comparator Positive Input)        |  |  |  |  |  |

| PD7      | AIN1 (Analog Comparator Negative Input)        |  |  |  |  |  |

**Table 26.** Port D Pin Alternate Functions

#### Port D Data Register - PORTD

|                                | Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |       |

|--------------------------------|---------------|--------|--------|--------|--------|--------|--------|--------|--------|-------|

|                                | \$12 (\$32)   | PORTD7 | PORTD6 | PORTD5 | PORTD4 | PORTD3 | PORTD2 | PORTD1 | PORTD0 | PORTD |

|                                | Read/Write    | R/W    |       |

|                                | Initial Value | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |       |

| Port D Data Direction Register |               |        |        |        |        |        |        |        |        |       |

| – DDRD                         | Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |       |

|                                | \$11 (\$31)   | DDD7   | DDD6   | DDD5   | DDD4   | DDD3   | DDD2   | DDD1   | DDD0   | DDRD  |

|                                | Read/Write    | R/W    |       |

|                                | Initial Value | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |       |

| Port D Input Pins Address –    |               |        |        |        |        |        |        |        |        |       |

| PIND                           | Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |       |

|                                | \$10 (\$30)   | PIND7  | PIND6  | PIND5  | PIND4  | PIND3  | PIND2  | PIND1  | PIND0  | PIND  |

|                                | Read/Write    | R      | R      | R      | R      | R      | R      | R      | R      | 1     |

|                                | Initial Value | N/A    |       |

The Port D Input Pins address (PIND) is not a register; this address enables access to the physical value on each Port D pin. When reading PORTD, the Port D Data Latch is read, and when reading PIND, the logical values present on the pins are read.

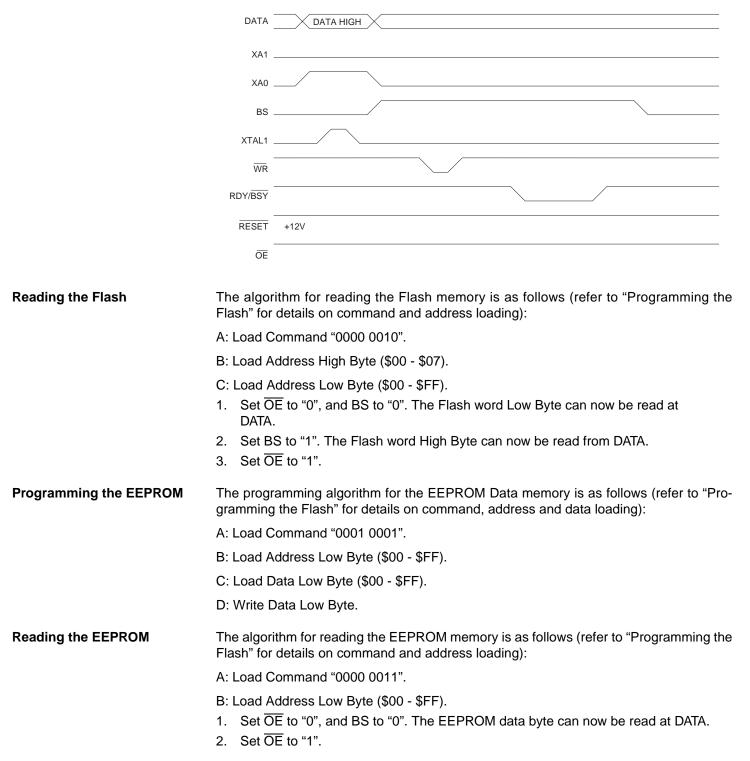

# External Clock Drive Waveforms

Figure 69. External Clock

#### Table 39. External Clock Drive

|                     |                      | V <sub>CC</sub> = 2.7V to 6.0V |     | V <sub>CC</sub> = 4.0V to 6.0V |     |       |

|---------------------|----------------------|--------------------------------|-----|--------------------------------|-----|-------|

| Symbol              | Parameter            | Min                            | Max | Min                            | Max | Units |

| 1/t <sub>CLCL</sub> | Oscillator Frequency | 0.0                            | 4.0 | 0.0                            | 8.0 | MHz   |

| t <sub>CLCL</sub>   | Clock Period         | 250.0                          |     | 125.0                          |     | ns    |

| t <sub>CHCX</sub>   | High Time            | 100.0                          |     | 50.0                           |     | ns    |

| t <sub>CLCX</sub>   | Low Time             | 100.0                          |     | 50.0                           |     | ns    |

| t <sub>CLCH</sub>   | Rise Time            |                                | 1.6 |                                | 0.5 | μs    |

| t <sub>CHCL</sub>   | Fall Time            |                                | 1.6 |                                | 0.5 | μs    |

# **Instruction Set Summary**

| Mnemonic       | Operands          | Description                            | Operation                                                                                | Flags          | # Clocks |

|----------------|-------------------|----------------------------------------|------------------------------------------------------------------------------------------|----------------|----------|

| ARITHMETIC AND | LOGIC INSTRUCTION | S                                      |                                                                                          |                |          |

| ADD            | Rd, Rr            | Add Two Registers                      | $Rd \leftarrow Rd + Rr$                                                                  | Z,C,N,V,H      | 1        |

| ADC            | Rd, Rr            | Add with Carry Two Registers           | $Rd \leftarrow Rd + Rr + C$                                                              | Z,C,N,V,H      | 1        |

| ADIW           | Rdl, K            | Add Immediate to Word                  | $Rdh:Rdl \leftarrow Rdh:Rdl + K$                                                         | Z,C,N,V,S      | 2        |

| SUB            | Rd, Rr            | Subtract Two Registers                 | $Rd \leftarrow Rd - Rr$                                                                  | Z,C,N,V,H      | 1        |

| SUBI           | Rd, K             | Subtract Constant from Register        | $Rd \leftarrow Rd - K$                                                                   | Z,C,N,V,H      | 1        |

| SBC            | Rd, Rr            | Subtract with Carry Two Registers      | $Rd \leftarrow Rd - Rr - C$                                                              | Z,C,N,V,H      | 1        |

| SBCI           | Rd, K             | Subtract with Carry Constant from Reg. | $Rd \leftarrow Rd - K - C$                                                               | Z,C,N,V,H      | 1        |

| SBIW           | Rdl, K            | Subtract Immediate from Word           | Rdh:Rdl ← Rdh:Rdl - K                                                                    | Z,C,N,V,S      | 2        |

| AND            | Rd, Rr            | Logical AND Registers                  | $Rd \leftarrow Rd \bullet Rr$                                                            | Z,N,V          | 1        |

| ANDI           | Rd, K             | Logical AND Register and Constant      | $Rd \leftarrow Rd \bullet K$                                                             | Z,N,V          | 1        |

| OR             | Rd, Rr            | Logical OR Registers                   | $Rd \leftarrow Rd v Rr$                                                                  | Z,N,V          | 1        |

| ORI            | Rd, K             | Logical OR Register and Constant       | $Rd \leftarrow Rd \vee K$                                                                | Z,N,V          | 1        |

| EOR            | Rd, Rr            | Exclusive OR Registers                 | $Rd \leftarrow Rd \oplus Rr$                                                             | Z,N,V          | 1        |

| COM            | Rd                | One's Complement                       | $Rd \leftarrow \$FF - Rd$                                                                | Z,C,N,V        | 1        |

| NEG            | Rd                | Two's Complement                       | Rd ← \$00 - Rd                                                                           | Z,C,N,V,H      | 1        |

| SBR            | Rd, K             | Set Bit(s) in Register                 | $Rd \leftarrow Rd \vee K$                                                                | Z,N,V          | 1        |

| CBR            | Rd, K             | Clear Bit(s) in Register               | $Rd \leftarrow Rd \bullet (\$FF - K)$                                                    | Z,N,V          | 1        |

| INC            | Rd                | Increment                              | $Rd \leftarrow Rd + 1$                                                                   | Z,N,V          | 1        |

| DEC            | Rd                | Decrement                              | $Rd \leftarrow Rd - 1$                                                                   | Z,N,V<br>Z,N,V | 1        |

| TST            | Rd                | Test for Zero or Minus                 | $Rd \leftarrow Rd \bullet Rd$                                                            | Z,N,V<br>Z,N,V | 1        |

| CLR            | Rd                | Clear Register                         | $Rd \leftarrow Rd \oplus Rd$                                                             | Z,N,V          | 1        |

| SER            | Rd                | Set Register                           | $Rd \leftarrow FF$                                                                       | None           | 1        |

| BRANCH INSTRU  |                   | Our register                           | i\u ← φi i                                                                               | NULLE          | I        |

|                |                   | Deletive lump                          |                                                                                          | Nana           | 2        |

| RJMP           | k                 | Relative Jump                          | $PC \leftarrow PC + k + 1$                                                               | None           | 2        |

| IJMP           |                   | Indirect Jump to (Z)                   | $PC \leftarrow Z$                                                                        | None           | 2        |

| RCALL          | k                 | Relative Subroutine Call               | $PC \leftarrow PC + k + 1$                                                               | None           | 3        |

| ICALL          |                   | Indirect Call to (Z)                   | PC ← Z                                                                                   | None           | 3        |

| RET            |                   | Subroutine Return                      | PC ← STACK                                                                               | None           | 4        |

| RETI           |                   | Interrupt Return                       | PC ← STACK                                                                               | 1              | 4        |

| CPSE           | Rd, Rr            | Compare, Skip if Equal                 | if (Rd = Rr) PC $\leftarrow$ PC + 2 or 3                                                 | None           | 1/2/3    |

| CP             | Rd, Rr            | Compare                                | Rd - Rr                                                                                  | Z,N,V,C,H      | 1        |

| CPC            | Rd, Rr            | Compare with Carry                     | Rd - Rr - C                                                                              | Z,N,V,C,H      | 1        |

| CPI            | Rd, K             | Compare Register with Immediate        | Rd - K                                                                                   | Z,N,V,C,H      | 1        |

| SBRC           | Rr, b             | Skip if Bit in Register Cleared        | if $(Rr(b) = 0) PC \leftarrow PC + 2 \text{ or } 3$                                      | None           | 1/2/3    |

| SBRS           | Rr, b             | Skip if Bit in Register is Set         | if $(Rr(b) = 1) PC \leftarrow PC + 2 \text{ or } 3$                                      | None           | 1/2/3    |

| SBIC           | P, b              | Skip if Bit in I/O Register Cleared    | if $(P(b) = 0) PC \leftarrow PC + 2 \text{ or } 3$                                       | None           | 1/2/3    |

| SBIS           | P, b              | Skip if Bit in I/O Register is Set     | if (P(b) = 1) PC ← PC + 2 or 3                                                           | None           | 1/2/3    |

| BRBS           | s, k              | Branch if Status Flag Set              | if (SREG(s) = 1) then PC $\leftarrow$ PC + k + 1                                         | None           | 1/2      |

| BRBC           | s, k              | Branch if Status Flag Cleared          | if (SREG(s) = 0) then PC $\leftarrow$ PC + k + 1                                         | None           | 1/2      |

| BREQ           | k                 | Branch if Equal                        | if (Z = 1) then PC $\leftarrow$ PC + k + 1                                               | None           | 1/2      |

| BRNE           | k                 | Branch if Not Equal                    | if (Z = 0) then PC $\leftarrow$ PC + k + 1                                               | None           | 1/2      |

| BRCS           | k                 | Branch if Carry Set                    | if (C = 1) then PC $\leftarrow$ PC + k + 1                                               | None           | 1/2      |

| BRCC           | k                 | Branch if Carry Cleared                | if (C = 0) then PC $\leftarrow$ PC + k + 1                                               | None           | 1/2      |

| BRSH           | k                 | Branch if Same or Higher               | if (C = 0) then PC $\leftarrow$ PC + k + 1<br>if (C = 0) then PC $\leftarrow$ PC + k + 1 | None           | 1/2      |

| BRLO           | k                 | Branch if Lower                        | if (C = 0) then PC $\leftarrow$ PC + k + 1                                               |                | 1/2      |

|                |                   |                                        |                                                                                          | None           |          |

| BRMI           | k                 | Branch if Minus                        | if (N = 1) then PC $\leftarrow$ PC + k + 1                                               | None           | 1/2      |

| BRPL           | k                 | Branch if Plus                         | if (N = 0) then PC $\leftarrow$ PC + k + 1                                               | None           | 1/2      |

| BRGE           | k                 | Branch if Greater or Equal, Signed     | if $(N \oplus V = 0)$ then PC $\leftarrow$ PC + k + 1                                    | None           | 1/2      |

| BRLT           | k                 | Branch if Less than Zero, Signed       | if $(N \oplus V = 1)$ then PC $\leftarrow$ PC + k + 1                                    | None           | 1/2      |

| BRHS           | k                 | Branch if Half-carry Flag Set          | if (H = 1) then PC $\leftarrow$ PC + k + 1                                               | None           | 1/2      |

| BRHC           | k                 | Branch if Half-carry Flag Cleared      | if (H = 0) then PC $\leftarrow$ PC + k + 1                                               | None           | 1/2      |

| BRTS           | k                 | Branch if T-flag Set                   | if (T = 1) then PC $\leftarrow$ PC + k + 1                                               | None           | 1/2      |

| BRTC           | k                 | Branch if T-flag Cleared               | if (T = 0) then PC $\leftarrow$ PC + k + 1                                               | None           | 1/2      |

| BRVS           | k                 | Branch if Overflow Flag is Set         | if (V = 1) then PC $\leftarrow$ PC + k + 1                                               | None           | 1/2      |

| BRVC           | k                 | Branch if Overflow Flag is Cleared     | if (V = 0) then PC $\leftarrow$ PC + k + 1                                               | None           | 1/2      |

| BRIE           | k                 | Branch if Interrupt Enabled            | if (I = 1) then PC $\leftarrow$ PC + k + 1                                               | None           | 1/2      |

| BRID           | k                 | Branch if Interrupt Disabled           | if (I = 0) then PC $\leftarrow$ PC + k + 1                                               | None           | 1/2      |

| DATA TRANSFER  | INSTRUCTIONS      |                                        |                                                                                          | ·              |          |

| MOV            | Rd, Rr            | Move between Registers                 | $Rd \leftarrow Rr$                                                                       | None           | 1        |

| LDI            | Rd, K             | Load Immediate                         | $Rd \leftarrow K$                                                                        | None           | 1        |

| LD             | Rd, X             | Load Indirect                          | $Rd \leftarrow (X)$                                                                      | None           | 2        |

|                |                   | Load Indirect and Post-inc.            | $Rd \leftarrow (X), X \leftarrow X + 1$                                                  | None           | 2        |

| LD             | Rd, X+            |                                        |                                                                                          |                |          |

# Errata for AT90S/LS4433 Rev. Rev. C/D/E/F

- · BOD Keeps the Device in Reset at Low Temperature

- Fuses and Programming Mode

- Incorrect Channel Change in Free Running Mode

- Bandgap Reference Stabilizing Time

- Brown-out Detection Level

- Serial Programming at Voltages below 2.9V

- UART Loses Synchronization if RXD Line is Low when UART Receive is Disabled

#### 7. BOD Keeps the Device in Reset at Low Temperature

When the device operates at low temperature (below 0°C) and the BOD is enabled, tha part may fail to start up. AT low temperature the BOD may never release the reset, and the part will not start the application. The problem will only occur during start-up and an already running application will not go into reset even if the temperature goes below 0°C.

Note that this also affects the described workaround for Errata no. 4.

#### **Problem Fix/Workaround**

If the device operates at low temperature and a BOD is required, an external BOD circuit must be used. Alternatively, ATmega8 can be used instead of AT90S/LS4433.

#### 6. Fuses and Programming Mode

After programming the Fuses in Serial Programming mode, it is not possible to program the Flash or EEPROM. If leaving Programming mode, it is not possible to reenter Programming mode.

#### **Problem Fix/Workaround**

Power the part down and backup again after programming the Fuses or leaving Programming mode.

#### 5. Incorrect Channel Change in Free Running Mode

If the ADC operates in Free Running mode and channels are changed by writing to ADMUX, shortly after the ADC Interrupt Flag (ADIF in ADCSR) is set, the new setting in ADMUX may affect the ongoing conversion.

#### **Problem Fix/Workaround**

Use Single Conversion mode when scanning channels, or avoid changing ADMUX util at least 0.5 ADC clock cycles after ADIF goes high.

#### 4. Bandgap Reference Stabilizing Time

The time for the internal voltage reference for the Analog Comparator to stabilize is longer than specified. The stabilizing period starts after the bandgap reference has been selected, and can go on for as much as 10 seconds.

#### **Problem Fix/Workaround**

The Bandgap reference will be stable immediately if the internal Brown-out Detector is enabled.

#### **Atmel Headquarters**

Corporate Headquarters 2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 487-2600

#### Europe

Atmel Sarl Route des Arsenaux 41 Case Postale 80 CH-1705 Fribourg Switzerland TEL (41) 26-426-5555 FAX (41) 26-426-5500

#### Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimhatsui East Kowloon Hong Kong TEL (852) 2721-9778 FAX (852) 2722-1369

#### Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan TEL (81) 3-3523-3551 FAX (81) 3-3523-7581

#### **Atmel Operations**

Memory

2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 436-4314

#### Microcontrollers

2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 436-4314

La Chantrerie BP 70602 44306 Nantes Cedex 3, France TEL (33) 2-40-18-18-18 FAX (33) 2-40-18-19-60

#### ASIC/ASSP/Smart Cards

Zone Industrielle 13106 Rousset Cedex, France TEL (33) 4-42-53-60-00 FAX (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL 1(719) 576-3300 FAX 1(719) 540-1759

Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland TEL (44) 1355-803-000 FAX (44) 1355-242-743

#### **RF**/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany TEL (49) 71-31-67-0 FAX (49) 71-31-67-2340

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL 1(719) 576-3300 FAX 1(719) 540-1759

# Biometrics/Imaging/Hi-Rel MPU/

High Speed Converters/RF Datacom Avenue de Rochepleine BP 123 38521 Saint-Egreve Cedex, France TEL (33) 4-76-58-30-00 FAX (33) 4-76-58-34-80

e-mail

literature@atmel.com

Web Site http://www.atmel.com

#### © Atmel Corporation 2002.

Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in Atmel's Terms and Conditions located on the Company's web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel's products are not authorized for use as critical components in life support devices or systems.

ATMEL® and AVR® are the registered trademarks of Atmel.

Other terms and product names may be the trademarks of others.

Printed on recycled paper.