Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | 80C51                                                                      |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB                                     |

| Peripherals                | LED, POR, PWM, WDT                                                         |

| Number of I/O              | 34                                                                         |

| Program Memory Size        | 32KB (32K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 4K x 8                                                                     |

| RAM Size                   | 1.25K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

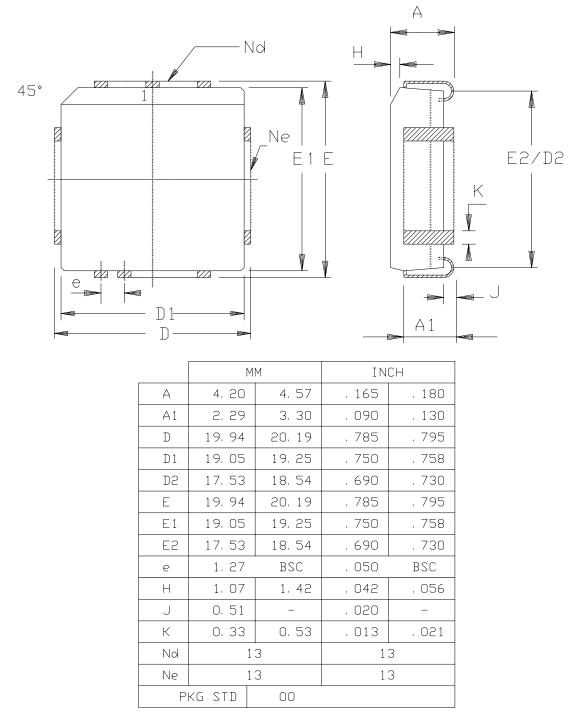

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-LQFP                                                                    |

| Supplier Device Package    | 64-LQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89c5131a-rdtil |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table 15.** CKCON1 (S:AFh)Clock Control Register 1

| 7          | 6               | 5                                | 4                                                                                                                                                                                                                                                | 3 | 2 | 1 | 0     |  |  |

|------------|-----------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|-------|--|--|

| -          | -               | -                                | -                                                                                                                                                                                                                                                | - | - | - | SPIX2 |  |  |

| Bit Number | Bit<br>Mnemonic | Description                      |                                                                                                                                                                                                                                                  |   |   |   |       |  |  |

| 7-1        | -               | Reserved<br>The value rea        | Reserved<br>The value read from this bit is always 0. Do not set this bit.                                                                                                                                                                       |   |   |   |       |  |  |

| 0          | SPIX2           | this bit has a<br>Clear to selee | SPI Clock<br>This control bit is validated when the CPU clock X2 is set. When X2 is low,<br>this bit has no effect.<br>Clear to select 6 clock periods per peripheral clock cycle.<br>Set to select 12 clock periods per peripheral clock cycle. |   |   |   |       |  |  |

Reset Value = 0000 0000b

# **Table 16.** PLLCON (S:A3h)PLL Control Register

| 7          | 6               | 5                                            | 4                                                                                                                                                                                                 | 3                              | 2     | 1     | 0     |  |  |

|------------|-----------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-------|-------|-------|--|--|

| -          | -               | -                                            | -                                                                                                                                                                                                 | -                              | EXT48 | PLLEN | PLOCK |  |  |

| Bit Number | Bit<br>Mnemonic | Description                                  | Description                                                                                                                                                                                       |                                |       |       |       |  |  |

| 7-3        | -               | Reserved<br>The value rea                    | Reserved<br>The value read from this bit is always 0. Do not set this bit.                                                                                                                        |                                |       |       |       |  |  |

| 2          | EXT48           | Set this bit to                              | External 48 MHz Enable Bit<br>Set this bit to bypass the PLL and disable the crystal oscillator.<br>Clear this bit to select the PLL output as USB clock and to enable the crystal<br>oscillator. |                                |       |       |       |  |  |

| 1          | PLLEN           | Set to enable                                | PLL Enable Bit<br>Set to enable the PLL.<br>Clear to disable the PLL.                                                                                                                             |                                |       |       |       |  |  |

| 0          | PLOCK           | PLL Lock In<br>Set by hardw<br>Clear by hard | are when PLI                                                                                                                                                                                      | _ is locked.<br>LL is unlocked | d.    |       |       |  |  |

Reset Value = 0000 0000b **Table 17.** PLLDIV (S:A4h) PLL Divider Register

| 7          | 6               | 5           | 4                  | 3  | 2  | 1  | 0  |  |

|------------|-----------------|-------------|--------------------|----|----|----|----|--|

| R3         | R2              | R1          | R0                 | N3 | N2 | N1 | N0 |  |

| Bit Number | Bit<br>Mnemonic | Description |                    |    |    |    |    |  |

| 7-4        | R3:0            | PLL R Divid | PLL R Divider Bits |    |    |    |    |  |

| 3-0        | N3:0            | PLL N Divid | er Bits            |    |    |    |    |  |

Reset Value = 0000 0000

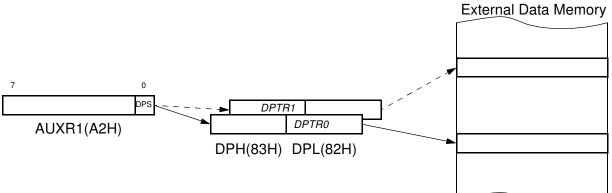

## Dual Data Pointer Register

The additional data pointer can be used to speed up code execution and reduce code size.

The dual DPTR structure is a way by which the chip will specify the address of an external data memory location. There are two 16-bit DPTR registers that address the external memory, and a single bit called DPS = AUXR1.0 (see Table 32) that allows the program code to switch between them (see Figure 12).

### Figure 12. Use of Dual Pointer

**Table 32.** AUXR1 RegisterAUXR1- Auxiliary Register 1(0A2h)

|                 |                                                                            | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|-----------------|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| -               | ENBOOT                                                                     | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | GF3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | DPS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| Bit<br>Mnemonic | Description                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| -               | Reserved<br>The value rea                                                  | d from this b                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | it is indetermir                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | nate. Do not se                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | et this bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| -               | <b>Reserved</b><br>The value rea                                           | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| ENBOOT          | Cleared to dis                                                             | able boot RC                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | h - 0FFFFh.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| -               | <b>Reserved</b><br>The value rea                                           | d from this b                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | it is indetermir                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | nate. Do not se                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | et this bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| GF3             | This bit is a g                                                            | eneral-purpos                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | se user flag.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 0               | Always cleare                                                              | ed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| -               | <b>Reserved</b><br>The value rea                                           | d from this b                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | it is indetermir                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | nate. Do not se                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | et this bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| DPS             | Cleared to se<br>Set to select I                                           | lect DPTR0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|                 | Bit<br>Mnemonic<br>-<br>-<br>ENBOOT<br>-<br>GF3<br>0<br>-<br>CF3<br>0<br>- | Bit<br>Mnemonic     Description       Reserved<br>The value real     Reserved<br>The value real       Reserved<br>The value real     Reserved<br>The value real       ENBOOT     Enable Boot<br>Cleared to dis<br>Set to map the<br>Set to map the<br>The value real       GF3     This bit is a get<br>The value real       0     Always cleared<br>The value real       0     Always cleared<br>The value real       DPS     Data Pointer<br>Cleared to sel<br>Set to select for | Bit<br>Mnemonic       Description         Bit<br>Mnemonic       Description         Reserved<br>The value read from this bit       Reserved<br>The value read from this bit         ENBOOT       Enable Boot Flash<br>Cleared to disable boot RO<br>Set to map the boot ROM         Bit       Reserved<br>The value read from this bit         GF3       This bit is a general-purpose         0       Always cleared.         Bit       Reserved<br>The value read from this bit         DPS       Data Pointer Selection<br>Cleared to select DPTR1. | Bit<br>Mnemonic       Description         -       Reserved<br>The value read from this bit is indetermin         -       Reserved<br>The value read from this bit is indetermin         -       Reserved<br>The value read from this bit is indetermin         ENBOOT       Enable Boot Flash<br>Cleared to disable boot ROM.<br>Set to map the boot ROM between F800         -       Reserved<br>The value read from this bit is indetermin         GF3       This bit is a general-purpose user flag.         0       Always cleared.         -       Reserved<br>The value read from this bit is indetermin         DPS       Data Pointer Selection<br>Cleared to select DPTR0.<br>Set to select DPTR1. | Bit<br>Mnemonic       Description         -       Reserved<br>The value read from this bit is indeterminate. Do not set<br>The value read from this bit is indeterminate. Do not set<br>The value read from this bit is indeterminate. Do not set<br>Enable Boot Flash<br>Cleared to disable boot ROM.<br>Set to map the boot ROM between F800h - 0FFFFh.         -       Reserved<br>The value read from this bit is indeterminate. Do not set<br>GF3         0       Always cleared.         -       Reserved<br>The value read from this bit is indeterminate. Do not set<br>O         0       Always cleared.         -       Reserved<br>The value read from this bit is indeterminate. Do not set<br>O         0       Always cleared.         -       Reserved<br>The value read from this bit is indeterminate. Do not set         DPS       Data Pointer Selection<br>Cleared to select DPTR0. | Bit<br>Mnemonic       Description         -       Reserved<br>The value read from this bit is indeterminate. Do not set this bit.         -       Reserved<br>The value read from this bit is indeterminate. Do not set this bit.         -       Reserved<br>The value read from this bit is indeterminate. Do not set this bit.         ENBOOT       Enable Boot Flash<br>Cleared to disable boot ROM.<br>Set to map the boot ROM between F800h - 0FFFFh.         -       Reserved<br>The value read from this bit is indeterminate. Do not set this bit.         GF3       This bit is a general-purpose user flag.         0       Always cleared.         -       Reserved<br>The value read from this bit is indeterminate. Do not set this bit.         DPS       Data Pointer Selection<br>Cleared to select DPTR0.<br>Set to select DPTR1. |  |

Reset Value = XX[BLJB]X X0X0b

Not bit addressable

a. Bit 2 stuck at 0; this allows to use INC AUXR1 to toggle DPS without changing GF3.

| Table 38. | Program | Lock bits |

|-----------|---------|-----------|

|-----------|---------|-----------|

|                | Program Loo | ck Bits |     |                                                                                                                                                                                                                                                                                                                                    |

|----------------|-------------|---------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Security level | LB0         | LB1     | LB2 | Protection Description                                                                                                                                                                                                                                                                                                             |

| 1              | U           | U       | U   | No program lock features enabled.                                                                                                                                                                                                                                                                                                  |

| 2              | Ρ           | U       | U   | MOVC instruction executed from external<br>program memory is disabled from fetching code<br>bytes from any internal memory, EA is sampled<br>and latched on reset, and further parallel<br>programming of the Flash and of the EEPROM<br>(boot and Xdata) is disabled. ISP and software<br>programming with API are still allowed. |

| 3              | х           | Ρ       | U   | Same as 2, also verify through parallel programming interface is disabled and serial programming ISP is still allowed.                                                                                                                                                                                                             |

| 4              | х           | х       | Р   | Same as 3, also external execution is disabled.                                                                                                                                                                                                                                                                                    |

Notes: 1. U: unprogrammed or "one" level.

2. P: programmed or "zero" level.

3. X: don't care

4. WARNING: Security level 2 and 3 should only be programmed after verification.

These security bits protect the code access through the parallel programming interface. They are set by default to level 4. The code access through the ISP is still possible and is controlled by the "software security bits" which are stored in the extra Flash memory accessed by the ISP firmware.

To load a new application with the parallel programmer, a chip erase must be done first. This will set the HSB in its inactive state and will erase the Flash memory. The part reference can always be read using Flash parallel programming modes.

The default value of the HSB provides parts ready to be programmed with ISP:

- BLJB: Cleared to force ISP operation.

- X2: Set to force X1 mode (Standard Mode)

- OSCON1-0: Set to start with 32 MHz oscillator configuration value.

- LB2-0: Security level four to protect the code from a parallel access with maximum security.

**Software Registers**

Default Values

Several registers are used, in factory and by parallel programmers, to make copies of hardware registers contents. These values are used by Atmel ISP (see Section "In-System Programming (ISP)").

These registers are in the "Extra Flash Memory" part of the Flash memory. This block is also called "XAF" or eXtra Array Flash. They are accessed in the following ways:

- Commands issued by the parallel memory programmer.

- Commands issued by the ISP software.

- Calls of API issued by the application software.

Several software registers are described in Table 39.

| Table 39. | Software | Registers |

|-----------|----------|-----------|

|-----------|----------|-----------|

| Address | Mnemonic | Description                              | Default value |                                      |

|---------|----------|------------------------------------------|---------------|--------------------------------------|

| 01      | SBV      | Software Boot Vector                     | FFh           | -                                    |

| 00      | BSB      | Boot Status Byte                         | 0FFh          | -                                    |

| 05      | SSB      | Software Security Byte                   | FFh           | -                                    |

| 30      | _        | Copy of the Manufacturer<br>Code         | 58h           | Atmel                                |

| 31      | -        | Copy of the Device ID #1:<br>Family Code | D7h           | C51 X2, Electrically<br>Erasable     |

| 60      | _        | Copy of the Device ID #2:<br>Memories    | F7h           | AT89C5131A-L 32 Kbyte                |

| 61      | _        | Copy of the Device ID #3:<br>Name        | DFh           | AT89C5131A-L 32 Kbyte,<br>revision 0 |

After programming the part by ISP, the BSB must be cleared (00h) in order to allow the application to boot at 0000h.

The content of the Software Security Byte (SSB) is described in Table 40 and Table 41.

To assure code protection from a parallel access, the HSB must also be at the required level.

| Table 10  | Softwara | Socurity | Buto |       |   |

|-----------|----------|----------|------|-------|---|

| Table 40. | Sollwale | Security | Dyte | (330) | 1 |

| 7             | 6               | 5                       | 4                                  | 3 | 2 | 1   | 0   |  |

|---------------|-----------------|-------------------------|------------------------------------|---|---|-----|-----|--|

| -             | -               | -                       | -                                  | - | - | LB1 | LB0 |  |

| Bit<br>Number | Bit<br>Mnemonic | Descriptio              | n                                  |   |   |     |     |  |

| 7             | -               | Reserved<br>Do not clea | ar this bit.                       |   |   |     |     |  |

| 6             | -               | Reserved<br>Do not clea | ar this bit.                       |   |   |     |     |  |

| 5             | -               | Reserved<br>Do not clea | ar this bit.                       |   |   |     |     |  |

| 4             | -               | Reserved<br>Do not clea | Reserved<br>Do not clear this bit. |   |   |     |     |  |

| 3             | -               | Reserved<br>Do not clea | Reserved<br>Do not clear this bit. |   |   |     |     |  |

| 2             | -               | Reserved<br>Do not clea | Reserved<br>Do not clear this bit. |   |   |     |     |  |

| 1-0           | LB1-0           | User Memo<br>See Table  | ory Lock Bits<br>41                |   |   |     |     |  |

The two lock bits provide different levels of protection for the on-chip code and data, when programmed as shown to Table 41.

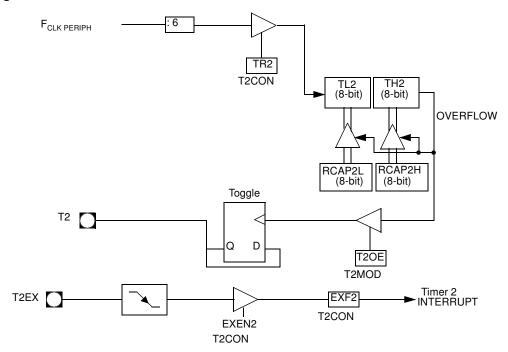

It is possible to use Timer 2 as a baud rate generator and a clock generator simultaneously. For this configuration, the baud rates and clock frequencies are not independent since both functions use the values in the RCAP2H and RCAP2L registers.

**Figure 27.** Clock-out Mode  $C/\overline{T2} = 0$

#### Table 55. CL Register

CL - PCA Counter Register Low (0E9h)

| 7             | 6               | 5                    | 4    | 3 | 2 | 1 | 0 |

|---------------|-----------------|----------------------|------|---|---|---|---|

| -             | -               | -                    | -    | - | - | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Descriptio           | n    |   |   |   |   |

| 7 - 0         | -               | PCA Cour<br>CL Value | iter |   |   |   |   |

Reset Value = 0000 0000b Not bit addressable

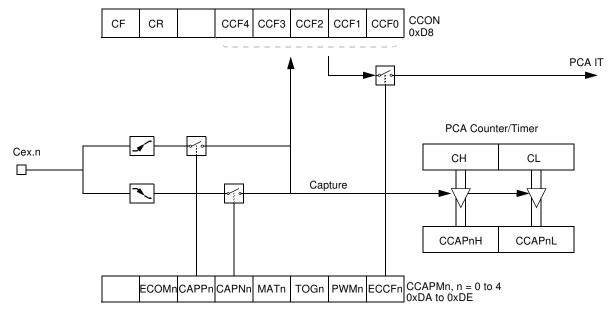

**PCA Capture Mode** To use one of the PCA modules in the capture mode either one or both of the CCAPM bits CAPN and CAPP for that module must be set. The external CEX input for the module (on port 1) is sampled for a transition. When a valid transition occurs the PCA hardware loads the value of the PCA counter registers (CH and CL) into the module's capture registers (CCAPnL and CCAPnH). If the CCFn bit for the module in the CCON SFR and the ECCFn bit in the CCAPMn SFR are set then an interrupt will be generated (see Figure 30).

#### Figure 30. PCA Capture Mode

### 16-bit Software Timer/Compare Mode

The PCA modules can be used as software timers by setting both the ECOM and MAT bits in the modules CCAPMn register. The PCA timer will be compared to the module's capture registers and when a match occurs an interrupt will occur if the CCFn (CCON SFR) and the ECCFn (CCAPMn SFR) bits for the module are both set (see Figure 31).

|                                  | Figure                     | 36. UART Timings in Mod                                                                                                                      | les 2 and 3                                                               |                                                                                                                                      |                     |

|----------------------------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|---------------------|

|                                  |                            |                                                                                                                                              | 1 <u> </u>                                                                | 5 X D6 X D7 X D8 X                                                                                                                   | -                   |

|                                  |                            | Start<br>Bit                                                                                                                                 | Data Byte                                                                 | Ninth Stop<br>Bit Bit                                                                                                                |                     |

|                                  | :                          | RI<br>MOD0 = 0                                                                                                                               |                                                                           |                                                                                                                                      |                     |

|                                  | :                          | RI<br>MOD0 = <del>1</del>                                                                                                                    |                                                                           |                                                                                                                                      |                     |

|                                  |                            | FE<br>MOD0 = 1                                                                                                                               |                                                                           | ·····                                                                                                                                |                     |

| Automatic Address<br>Recognition |                            | omatic address recognition<br>feature is enabled (SM2 b                                                                                      |                                                                           |                                                                                                                                      | commu-              |

|                                  | commi<br>incomi<br>receive | ented in hardware, automa<br>nication feature by allow<br>og command frame. Only<br>r sets RI bit in SCON regist<br>terrupted by command fra | ing the serial port to<br>when the serial port<br>ter to generate an inte | o examine the address of recognizes its own addre errupt. This ensures that the third set of the | of each<br>ess, the |

|                                  | configu                    | ed, you may enable the au<br>ration, the stop bit takes the<br>d command frame address<br>op bit.                                            | e place of the ninth d                                                    | ata bit. Bit RI is set only w                                                                                                        | hen the             |

|                                  | •                          | port automatic address rec<br>cast address.<br>The multiprocessor commun                                                                     | ication and automatic                                                     | address recognition features                                                                                                         | s cannot            |

|                                  |                            | be enabled in mode 0 (i.e., s                                                                                                                | etting SM2 bit in SCON                                                    | l register in mode 0 has no e                                                                                                        | ffect).             |

| Given Address                    | registe<br>device          | evice has an individual add<br>r is a mask byte that con<br>s given address. The don't<br>at a time. The following exa                       | tains don't care bits<br>care bits provide the                            | (defined by zeros) to for<br>flexibility to address one                                                                              | orm the<br>or more  |

|                                  | To add<br>1111b<br>For exa |                                                                                                                                              | dual address, the S                                                       | ADEN mask byte must b                                                                                                                | <b>e</b> 1111       |

|                                  |                            | owing is an example of how<br>e A:SADDR1111 0001b<br><u>SADEN1111 1010b</u><br>Given1111 0X0Xb                                               | w to use given addre                                                      | sses to address different s                                                                                                          | slaves:             |

|                                  | Sla                        | e B:SADDR1111 0011b<br><u>SADEN1111 1001b</u><br>Given1111 0XX1b                                                                             |                                                                           |                                                                                                                                      |                     |

|                                  | Sla                        | e C:SADDR1111 0011b<br><u>SADEN1111 1101b</u><br>Given1111 00X1b                                                                             |                                                                           |                                                                                                                                      |                     |

| Bit<br>Number | Bit Mnemonic | Description                                                                                                                                            |

|---------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2             | SPR1         | SPR2 SPR1 SPR0 Serial Peripheral Rate<br>000Reserved<br>00 1F <sub>CLK PERIPH</sub> /4                                                                 |

|               |              | 010 F <sub>CLK PERIPH/</sub> 8<br>011F <sub>CLK PERIPH/</sub> 16                                                                                       |

| 1             | SPR0         | 100F <sub>CLK PERIPH</sub> /10<br>100F <sub>CLK PERIPH</sub> /32<br>10 1F <sub>CLK PERIPH</sub> /64<br>110F <sub>CLK PERIPH</sub> /128<br>1 11Reserved |

Reset Value = 0001 0100b

Not bit addressable

Serial Peripheral Status Register (SPSTA)

- The Serial Peripheral Status Register contains flags to signal the following conditions:

- Data transfer complete

- Write collision

- Inconsistent logic level on SS pin (mode fault error)

Table 75 describes the SPSTA register and explains the use of every bit in the register.

### Table 75. SPSTA Register

SPSTA - Serial Peripheral Status and Control register (0C4H)

|               |                 |                           | Tab                                                                                                                                                                                                                                                                                                                     | le 1.                      | . ,                                |             |         |  |

|---------------|-----------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------------------------------|-------------|---------|--|

| 7             | 6               | 5                         | 4                                                                                                                                                                                                                                                                                                                       | 3                          | 2                                  | 1           | 0       |  |

| SPIF          | WCOL            | SSERR                     | MODF                                                                                                                                                                                                                                                                                                                    | -                          | -                                  | -           | -       |  |

| Bit<br>Number | Bit<br>Mnemonic | Description               |                                                                                                                                                                                                                                                                                                                         |                            |                                    |             |         |  |

| 7             | SPIF            | approved by               | ardware to inc<br>a clearing sec                                                                                                                                                                                                                                                                                        | licate data tra<br>quence. | nsfer is in prog<br>transfer has b |             |         |  |

| 6             | WCOL            | approved by               | ardware to inc<br>a clearing sec                                                                                                                                                                                                                                                                                        | quence.                    | collision has o<br>on has been de  |             | is been |  |

| 5             | SSERR           |                           | are when $\overline{SS}$ ore the end of                                                                                                                                                                                                                                                                                 | is de-<br>a received da    |                                    | CON).       |         |  |

| 4             | MODF            | has been app              | leared by disabling the SPI (clearing SPEN bit in SPCON).<br><b>Iode Fault</b><br>leared by hardware to indicate that the $\overline{SS}$ pin is at appropriate logic level, or<br>as been approved by a clearing sequence.<br>et by hardware to indicate that the $\overline{SS}$ pin is at inappropriate logic level. |                            |                                    |             |         |  |

| 3             | -               | Reserved<br>The value rea | ad from this bi                                                                                                                                                                                                                                                                                                         | t is indetermir            | nate. Do not se                    | et this bit |         |  |

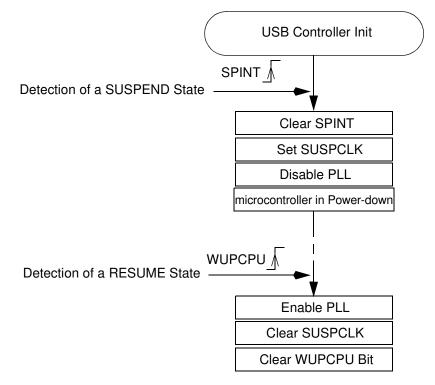

Figure 66. Example of a Suspend/Resume Management

Table 96.UEPNUM RegisterUEPNUM (S:C7h)USB Endpoint Number

| 7          | 6         | 5                                                                             | 4                                                                                                                                                                                                 | 3                                                                                                              | 2                                                                                                        | 1                                                                                                              | 0                                                                                             |