Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | 80C51                                                                      |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB                                     |

| Peripherals                | LED, POR, PWM, WDT                                                         |

| Number of I/O              | 18                                                                         |

| Program Memory Size        | 32KB (32K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 4K x 8                                                                     |

| RAM Size                   | 1.25К х 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89c5131a-tisil |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

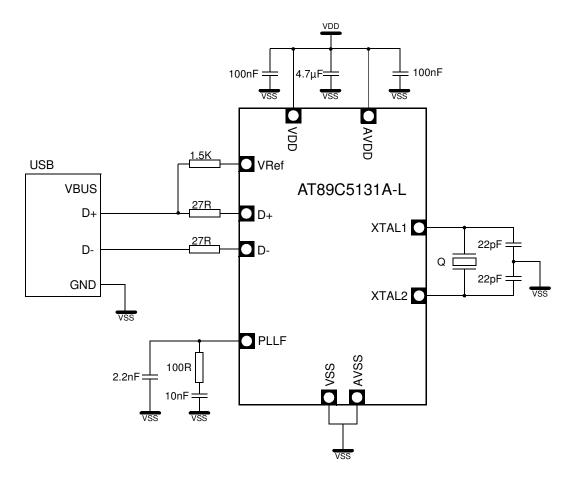

# **Typical Application**

# **Recommended External components**

All the external components described in the figure below must be implemented as close as possible from the microcontroller package.

The following figure represents the typical wiring schematic.

## Figure 4. Typical Application

# Table 21. Timer SFR's

| Mnemonic | Add | Name                                        | 7     | 6     | 5    | 4    | 3     | 2     | 1     | 0       |

|----------|-----|---------------------------------------------|-------|-------|------|------|-------|-------|-------|---------|

| TH0      | 8Ch | Timer/Counter 0 High byte                   |       |       |      |      |       |       |       |         |

| TL0      | 8Ah | Timer/Counter 0 Low byte                    |       |       |      |      |       |       |       |         |

| TH1      | 8Dh | Timer/Counter 1 High byte                   |       |       |      |      |       |       |       |         |

| TL1      | 8Bh | Timer/Counter 1 Low byte                    |       |       |      |      |       |       |       |         |

| TH2      | CDh | Timer/Counter 2 High byte                   |       |       |      |      |       |       |       |         |

| TL2      | CCh | Timer/Counter 2 Low byte                    |       |       |      |      |       |       |       |         |

| TCON     | 88h | Timer/Counter 0 and 1 control               | TF1   | TR1   | TF0  | TR0  | IE1   | IT1   | IE0   | IT0     |

| TMOD     | 89h | Timer/Counter 0 and 1<br>Modes              | GATE1 | C/T1# | M11  | M01  | GATE0 | C/T0# | M10   | M00     |

| T2CON    | C8h | Timer/Counter 2 control                     | TF2   | EXF2  | RCLK | TCLK | EXEN2 | TR2   | C/T2# | CP/RL2# |

| T2MOD    | C9h | Timer/Counter 2 Mode                        |       |       |      |      |       |       | T2OE  | DCEN    |

| RCAP2H   | CBh | Timer/Counter 2<br>Reload/Capture High byte |       |       |      |      |       |       |       |         |

| RCAP2L   | CAh | Timer/Counter 2<br>Reload/Capture Low byte  |       |       |      |      |       |       |       |         |

| WDTRST   | A6h | WatchDog Timer Reset                        |       |       |      |      |       |       |       |         |

| WDTPRG   | A7h | WatchDog Timer Program                      |       |       |      |      |       | S2    | S1    | S0      |

# Table 22. Serial I/O Port SFR's

| Mnemonic | Add | Name               | 7      | 6   | 5   | 4   | 3   | 2   | 1  | 0  |

|----------|-----|--------------------|--------|-----|-----|-----|-----|-----|----|----|

| SCON     | 98h | Serial Control     | FE/SM0 | SM1 | SM2 | REN | TB8 | RB8 | ТІ | RI |

| SBUF     | 99h | Serial Data Buffer |        |     |     |     |     |     |    |    |

| SADEN    | B9h | Slave Address Mask |        |     |     |     |     |     |    |    |

| SADDR    | A9h | Slave Address      |        |     |     |     |     |     |    |    |

# Table 23. Baud Rate Generator SFR's

| Mnemonic | Add | Name              | 7 | 6 | 5 | 4   | 3    | 2    | 1   | 0   |

|----------|-----|-------------------|---|---|---|-----|------|------|-----|-----|

| BRL      | 9Ah | Baud Rate Reload  |   |   |   |     |      |      |     |     |

| BDRCON   | 9Bh | Baud Rate Control |   |   |   | BRR | TBCK | RBCK | SPD | SRC |

#### Table 24. PCA SFR's

| Mnemo-<br>nic                                  | Add                             | Name                                                                                                                                                                   | 7                                                   | 6                                                   | 5                                                   | 4                                                   | 3                                                   | 2                                                   | 1                                                   | 0                                                   |

|------------------------------------------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------|

| CCON                                           | D8h                             | PCA Timer/Counter Control                                                                                                                                              | CF                                                  | CR                                                  |                                                     | CCF4                                                | CCF3                                                | CCF2                                                | CCF1                                                | CCF0                                                |

| CMOD                                           | D9h                             | PCA Timer/Counter Mode                                                                                                                                                 | CIDL                                                | WDTE                                                |                                                     |                                                     |                                                     | CPS1                                                | CPS0                                                | ECF                                                 |

| CL                                             | E9h                             | PCA Timer/Counter Low byte                                                                                                                                             |                                                     |                                                     |                                                     |                                                     |                                                     |                                                     |                                                     |                                                     |

| СН                                             | F9h                             | PCA Timer/Counter High byte                                                                                                                                            |                                                     |                                                     |                                                     |                                                     |                                                     |                                                     |                                                     |                                                     |

| CCAPM0<br>CCAPM1<br>CCAPM2<br>CCAPM3<br>CCAPM4 | DAh<br>DBh<br>DCh<br>DDh<br>DEh | PCA Timer/Counter Mode 0<br>PCA Timer/Counter Mode 1<br>PCA Timer/Counter Mode 2<br>PCA Timer/Counter Mode 3<br>PCA Timer/Counter Mode 4                               |                                                     | ECOM0<br>ECOM1<br>ECOM2<br>ECOM3<br>ECOM4           | CAPP0<br>CAPP1<br>CAPP2<br>CAPP3<br>CAPP4           | CAPN0<br>CAPN1<br>CAPN2<br>CAPN3<br>CAPN4           | MAT0<br>MAT1<br>MAT2<br>MAT3<br>MAT4                | TOG0<br>TOG1<br>TOG2<br>TOG3<br>TOG4                | PWM0<br>PWM1<br>PWM2<br>PWM3<br>PWM4                | ECCF0<br>ECCF1<br>ECCF2<br>ECCF3<br>ECCF4           |

| CCAP0H<br>CCAP1H<br>CCAP2H<br>CCAP3H<br>CCAP4H | FAh<br>FBh<br>FCh<br>FDh<br>FEh | PCA Compare Capture Module 0 H<br>PCA Compare Capture Module 1 H<br>PCA Compare Capture Module 2 H<br>PCA Compare Capture Module 3 H<br>PCA Compare Capture Module 4 H | CCAP0H7<br>CCAP1H7<br>CCAP2H7<br>CCAP3H7<br>CCAP4H7 | CCAP0H6<br>CCAP1H6<br>CCAP2H6<br>CCAP3H6<br>CCAP4H6 | CCAP0H5<br>CCAP1H5<br>CCAP2H5<br>CCAP3H5<br>CCAP4H5 | CCAP0H4<br>CCAP1H4<br>CCAP2H4<br>CCAP3H4<br>CCAP4H4 | CCAP0H3<br>CCAP1H3<br>CCAP2H3<br>CCAP3H3<br>CCAP4H3 | CCAP0H2<br>CCAP1H2<br>CCAP2H2<br>CCAP3H2<br>CCAP3H2 | CCAP0H1<br>CCAP1H1<br>CCAP2H1<br>CCAP3H1<br>CCAP3H1 | CCAP0H0<br>CCAP1H0<br>CCAP2H0<br>CCAP3H0<br>CCAP4H0 |

| CCAP0L<br>CCAP1L<br>CCAP2L<br>CCAP3L<br>CCAP4L | EAh<br>EBh<br>ECh<br>EDh<br>EEh | PCA Compare Capture Module 0 L<br>PCA Compare Capture Module 1 L<br>PCA Compare Capture Module 2 L<br>PCA Compare Capture Module 3 L<br>PCA Compare Capture Module 4 L | CCAP0L7<br>CCAP1L7<br>CCAP2L7<br>CCAP3L7<br>CCAP4L7 | CCAP0L6<br>CCAP1L6<br>CCAP2L6<br>CCAP3L6<br>CCAP4L6 | CCAP0L5<br>CCAP1L5<br>CCAP2L5<br>CCAP3L5<br>CCAP4L5 | CCAP0L4<br>CCAP1L4<br>CCAP2L4<br>CCAP3L4<br>CCAP4L4 | CCAP0L3<br>CCAP1L3<br>CCAP2L3<br>CCAP3L3<br>CCAP3L3 | CCAP0L2<br>CCAP1L2<br>CCAP2L2<br>CCAP3L2<br>CCAP3L2 | CCAP0L1<br>CCAP1L1<br>CCAP2L1<br>CCAP3L1<br>CCAP4L1 | CCAP0L0<br>CCAP1L0<br>CCAP2L0<br>CCAP3L0<br>CCAP4L0 |

#### Table 25. Interrupt SFR's

| Mnemo-<br>nic | Add | Name                              | 7  | 6     | 5    | 4   | 3    | 2     | 1     | 0    |

|---------------|-----|-----------------------------------|----|-------|------|-----|------|-------|-------|------|

| IEN0          | A8h | Interrupt Enable Control 0        | EA | EC    | ET2  | ES  | ET1  | EX1   | ET0   | EX0  |

| IEN1          | B1h | Interrupt Enable Control 1        |    | EUSB  |      |     |      | ESPI  | ETWI  | EKB  |

| IPL0          | B8h | Interrupt Priority Control Low 0  |    | PPCL  | PT2L | PSL | PT1L | PX1L  | PTOL  | PX0L |

| IPH0          | B7h | Interrupt Priority Control High 0 |    | PPCH  | PT2H | PSH | PT1H | PX1H  | PT0H  | PX0H |

| IPL1          | B2h | Interrupt Priority Control Low 1  |    | PUSBL |      |     |      | PSPIL | PTWIL | PKBL |

| IPH1          | B3h | Interrupt Priority Control High 1 |    | PUSBH |      |     |      | PSPIH | PTWIH | РКВН |

## Table 26. PLL SFRs

| Mnemonic | Add | Name        | 7  | 6  | 5  | 4  | 3  | 2     | 1     | 0     |

|----------|-----|-------------|----|----|----|----|----|-------|-------|-------|

| PLLCON   | A3h | PLL Control |    |    |    |    |    | EXT48 | PLLEN | PLOCK |

| PLLDIV   | A4h | PLL Divider | R3 | R2 | R1 | R0 | N3 | N2    | N1    | N0    |

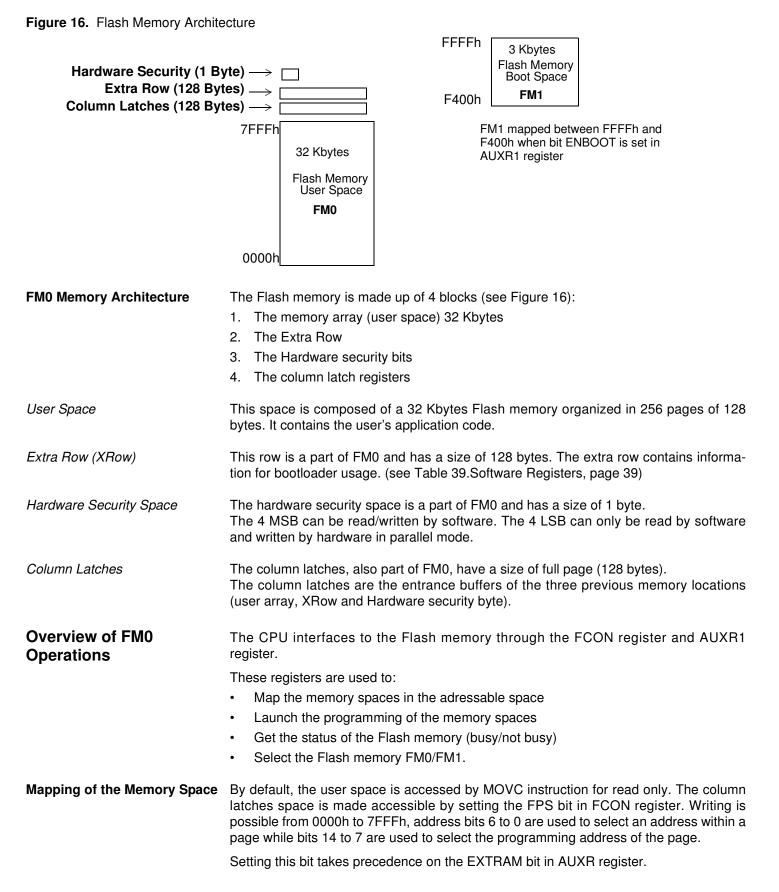

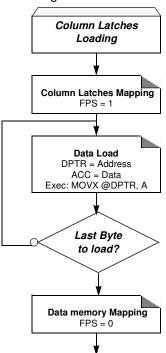

## Loading the Column Latches

Any number of data from 1 byte to 128 bytes can be loaded in the column latches. This provides the capability to program the whole memory by byte, by page or by any number of bytes in a page.

When programming is launched, an automatic erase of the locations loaded in the column latches is first performed, then programming is effectively done. Thus, no page or block erase is needed and only the loaded data are programmed in the corresponding page.

The following procedure is used to load the column latches and is summarized in Figure 17:

- Map the column latch space by setting FPS bit.

- · Load the DPTR with the address to load.

- Load Accumulator register with the data to load.

- Execute the MOVX @DPTR, A instruction.

- If needed loop the three last instructions until the page is completely loaded.

Figure 17. Column Latches Loading Procedure

#### **Programming the Flash Spaces**

User

The following procedure is used to program the User space and is summarized in Figure 18:

- Load data in the column latches from address 0000h to 7FFFh<sup>(1)</sup>.

- Disable the interrupts.

- Launch the programming by writing the data sequence 50h followed by A0h in FCON register.

The end of the programming indicated by the FBUSY flag cleared.

- Enable the interrupts.

- Note: 1. The last page address used when loading the column latch is the one used to select the page programming address.

# Registers

Table 36.FCON (S:D1h)Flash Control Register

| 7          | 6               | 5                          | 4                                                                                                                                | 3                                        | 2           | 1            | 0        |  |  |

|------------|-----------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-------------|--------------|----------|--|--|

| FPL3       | FPL2            | FPL1                       | FPL0                                                                                                                             | FPS                                      | FMOD1       | FMOD0        | FBUSY    |  |  |

| Bit Number | Bit<br>Mnemonic | Description                |                                                                                                                                  |                                          |             |              |          |  |  |

| 7-4        | FPL3:0          | •                          | lowed by AXh                                                                                                                     | ommand Bits<br>to launch the             | programming | according to | FMOD1:0. |  |  |

| 3          | FPS             | Set to map th              | Flash Map Program Space<br>Set to map the column latch space in the data memory space.<br>Clear to re-map the data memory space. |                                          |             |              |          |  |  |

| 2-1        | FMOD1:0         | Flash Mode<br>See Table 34 | or Table 35.                                                                                                                     |                                          |             |              |          |  |  |

| 0          | FBUSY           | Clear by hard              |                                                                                                                                  | gramming is in<br>rogramming is<br>ware. |             |              |          |  |  |

Reset Value = 0000 0000b

# Flash Registers and Memory Map

The AT89C5131A-L Flash memory uses several registers:

- Hardware register can be accessed with a parallel programmer. Some bits of the hardware register can be changed, also, by API (i.e. X2 and BLJB bits of Hardware security Byte) or ISP.

- Software registers are in a special page of the Flash memory which can be accessed through the API or with the parallel programming modes. This page, called "Extra Flash Memory", is not in the internal Flash program memory addressing space.

Hardware Registers The only hardware register of the AT89C5131A-L is called Hardware Security Byte (HSB).

| 7             | 6               | 5                           | 4                                                                                                                                                                           | 3                                                                     | 2                                                                  | 1        | 0           |  |  |  |

|---------------|-----------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------|----------|-------------|--|--|--|

| X2            | BLJB            | OSCON1                      | OSCON1 OSCON0 - LB2 LB1 LB0                                                                                                                                                 |                                                                       |                                                                    |          |             |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                 | Description                                                                                                                                                                 |                                                                       |                                                                    |          |             |  |  |  |

| 7             | X2              |                             | 2 Mode<br>Cleared to force X2 mode (6 clocks per instruction)<br>Set to force X1 mode, Standard Mode (Default).                                                             |                                                                       |                                                                    |          |             |  |  |  |

| 6             | BLJB            | Set this bit to             | Bootloader Jump Bit<br>Set this bit to start the user's application on next reset at address 0000h.<br>Cleared this bit to start the bootloader at address F400h (default). |                                                                       |                                                                    |          |             |  |  |  |

| 5-4           | OSCON1-0        | 1 0 The osc<br>0 1 The osc  | s are used to<br>CON0 Descri<br>illator is config<br>illator is config                                                                                                      | <b>ption</b><br>gured to run fr<br>gured to run fr<br>gured to run fr | cillator in orde<br>om 0 to 32 Mł<br>om 0 to 16 Mł<br>om 0 to 8 MH | Hz<br>Hz | insumption. |  |  |  |

| 3             | -               | Reserved                    |                                                                                                                                                                             |                                                                       |                                                                    |          |             |  |  |  |

| 2-0           | LB2-0           | User Memory<br>See Table 38 | / Lock Bits                                                                                                                                                                 |                                                                       |                                                                    |          |             |  |  |  |

Table 37. Hardware Security Byte (HSB)

Bootloader Jump Bit (BLJB)

One bit of the HSB, the BLJB bit, is used to force the boot address:

- When this bit is set the boot address is 0000h.

- When this bit is reset the boot address is F400h. By default, this bit is cleared and the ISP is enabled.

Flash Memory Lock Bits

The three lock bits provide different levels of protection for the on-chip code and data, when programmed as shown in Table 38.

| In-System<br>Programming (ISP)   | <ul> <li>With the implementation of the User Space (FM0) and the Boot Space (FM1) in Flash technology the AT89C5131 allows the system engineer the development of applications with a very high level of flexibility. This flexibility is based on the possibility to alter the customer program at any stages of a product's life:</li> <li>Before mounting the chip on the PCB, FM0 flash can be programmed with the application code. FM1 is always preprogrammed by Atmel with a USB bootloader.<sup>(1)</sup></li> <li>Once the chip is mounted on the PCB, it can be programmed by serial mode via the USB bus.</li> <li>Note: <ul> <li>The user can also program his own bootloader in FM1.</li> </ul> </li> <li>This ISP allows code modification over the total lifetime of the product.</li> <li>Besides the default Bootloaders Atmel provide customers all the needed Application-Programming-Interfaces (API) which are needed for the ISP. The API are located in the Boot memory.</li> </ul> <li>This allow the customer to have a full use of the 32-Kbyte user memory.</li> |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Flash Programming and<br>Erasure | <ul> <li>There are three methods for programming the Flash memory:</li> <li>The Atmel bootloader located in FM1 is activated by the application. Low level API routines (located in FM1)will be used to program FM0. The interface used for serial downloading to FM0 is the USB. API can be called also by user's bootloader located in FM0 at [SBV]00h.</li> <li>A further method exist in activating the Atmel boot loader by hardware activation. See the Section "Hardware Registers".</li> <li>The FM0 can be programmed also by the parallel mode using a programmer.</li> <li>Figure 22. Flash Memory Mapping</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                  | FFFFh<br>F400h FFFFh<br>F400h FFFFh<br>FM1 FFFFh<br>FM1 Mapped between F400h and FFFFh<br>When API Called                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Flash Memory

FM0

0000h

# On-chip Expanded RAM (ERAM)

The AT89C5131A-L provides additional Bytes of random access memory (RAM) space for increased data parameters handling and high level language usage.

AT89C5131A-L devices have an expanded RAM in the external data space; maximum size and location are described in Table 44.

#### Table 44. Description of Expanded RAM

|              |           | Add   | ress |

|--------------|-----------|-------|------|

| Part Number  | ERAM Size | Start | End  |

| AT89C5131A-L | 1024      | 00h   | 3FFh |

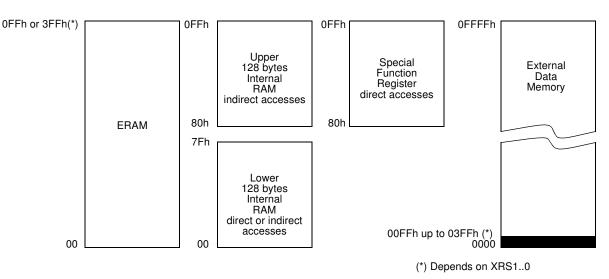

The AT89C5131A-L has on-chip data memory which is mapped into the following four separate segments.

- 1. The Lower 128 bytes of RAM (addresses 00h to 7Fh) are directly and indirectly addressable.

- 2. The Upper 128 bytes of RAM (addresses 80h to FFh) are indirectly addressable only.

- 3. The Special Function Registers, SFRs, (addresses 80h to FFh) are directly addressable only.

- 4. The expanded RAM bytes are indirectly accessed by MOVX instructions, and with the EXTRAM bit cleared in the AUXR register (see Table 44)

The lower 128 bytes can be accessed by either direct or indirect addressing. The Upper 128 bytes can be accessed by indirect addressing only. The Upper 128 bytes occupy the same address space as the SFR. That means they have the same address, but are physically separate from SFR space.

## Figure 25. Internal and External Data Memory Address

# Table 45. AUXR Register

AUXR - Auxiliary Register (8Eh)

| 7             | 6               | 5                                   | 4                                                                                                                                   | 3                                                  | 2             | 1              | 0  |  |  |  |  |

|---------------|-----------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|---------------|----------------|----|--|--|--|--|

| DPU           | -               | МО                                  | -                                                                                                                                   | XRS1                                               | XRS0          | EXTRAM         | AO |  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Descriptio                          | Description                                                                                                                         |                                                    |               |                |    |  |  |  |  |

| 7             | DPU             | Cleared to                          | <b>Disable Weak Pull Up</b><br>Cleared to enabled weak pull up on standard Ports.<br>Set to disable weak pull up on standard Ports. |                                                    |               |                |    |  |  |  |  |

| 6             | -               | <b>Reserved</b><br>The value        | read from this                                                                                                                      | s bit is indeterr                                  | minate. Do no | t set this bit |    |  |  |  |  |

| 5             | MO              | periods (de                         | stretch MOV                                                                                                                         | X control: the ntrol: the $\overline{\text{RD}}$ a |               |                |    |  |  |  |  |

| 4             | -               | <b>Reserved</b><br>The value        | read from this                                                                                                                      | s bit is indeterr                                  | minate. Do no | t set this bit |    |  |  |  |  |

| 3             | XRS1            | ERAM Siz                            | e                                                                                                                                   |                                                    |               |                |    |  |  |  |  |

| 2             | XRS0            | XRS1XRS<br>0 0<br>0 1<br>1 0<br>1 1 | 256 byte<br>512 byte<br>768 byte                                                                                                    | es<br>es                                           |               |                |    |  |  |  |  |

| 1             | EXTRAM          | Cleared to                          | <b>EXTRAM bit</b><br>Cleared to access internal ERAM using MOVX at $\overline{Ri}$ at DPTR.<br>Set to access external memory.       |                                                    |               |                |    |  |  |  |  |

| 0             | AO              | 1/3 if X2 m                         | LE is emitted<br>node is used)                                                                                                      | at a constant<br>(default).<br>vhen a MOVX         |               |                |    |  |  |  |  |

Reset Value = 0X0X 1100b Not bit addressable

the CAPP bit enables the positive edge. If both bits are set both edges will be enabled and a capture will occur for either transition.

• The last bit in the register ECOM (CCAPMn.6) when set enables the comparator function.

Table 51 shows the CCAPMn settings for the various PCA functions.

#### **Table 50.** CCAPMn Registers (n = 0-4)

CCAPM0 - PCA Module 0 Compare/Capture Control Register (0DAh) CCAPM1 - PCA Module 1 Compare/Capture Control Register (0DBh) CCAPM2 - PCA Module 2 Compare/Capture Control Register (0DCh) CCAPM3 - PCA Module 3 Compare/Capture Control Register (0DDh) CCAPM4 - PCA Module 4 Compare/Capture Control Register (0DEh)

| 7             | 6               | 5                     | 4                                                                                                                                                                                                     | 3                                                  | 2    | 1            | 0     |  |

|---------------|-----------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|------|--------------|-------|--|

| -             | ECOMn           | CAPPn                 | CAPNn                                                                                                                                                                                                 | MATn                                               | TOGn | PWMn         | ECCFn |  |

| Bit<br>Number | Bit<br>Mnemonic | Descriptio            | Description                                                                                                                                                                                           |                                                    |      |              |       |  |

| 7             | -               | Reserved<br>The value | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                       |                                                    |      |              |       |  |

| 6             | ECOMn           | Cleared to            | Enable Comparator<br>Cleared to disable the comparator function.<br>Set to enable the comparator function.                                                                                            |                                                    |      |              |       |  |

| 5             | CAPPn           | Cleared to            | Capture Positive<br>Cleared to disable positive edge capture.<br>Set to enable positive edge capture.                                                                                                 |                                                    |      |              |       |  |

| 4             | CAPNn           | Cleared to            | Capture Negative<br>Cleared to disable negative edge capture.<br>Set to enable negative edge capture.                                                                                                 |                                                    |      |              |       |  |

| 3             | MATn            | compare/ca            | apture registe                                                                                                                                                                                        | h of the PCA or<br>r causes the<br>set, flagging a |      | nis module's |       |  |

| 2             | TOGn            |                       | ,                                                                                                                                                                                                     | h of the PCA<br>r causes the (                     |      |              |       |  |

| 1             | PWMn            | Cleared to            | Pulse Width Modulation Mode<br>Cleared to disable the CEXn pin to be used as a pulse width modulated output.<br>Set to enable the CEXn pin to be used as a pulse width modulated output.              |                                                    |      |              |       |  |

| 0             | ECCFn           | Cleared to generate a | Enable CCF Interrupt<br>Cleared to disable compare/capture flag CCFn in the CCON register to<br>generate an interrupt.<br>Set to enable compare/capture flag CCFn in the CCON register to generate an |                                                    |      |              |       |  |

Reset Value = X000 0000b Not bit addressable

| BRL - Bau | BRL - Baud Rate Reload Register for the internal baud rate generator, UART (9Ah) |   |   |   |   |   |   |  |

|-----------|----------------------------------------------------------------------------------|---|---|---|---|---|---|--|

| 7         | 6                                                                                | 5 | 4 | 3 | 2 | 1 | 0 |  |

| -         |                                                                                  |   |   |   |   |   |   |  |

|           |                                                                                  |   |   |   |   |   |   |  |

Reset Value = 0000 0000b

# Table 57. T2CON Register

| T2CON - | Timer 2 Cor | trol Registe | er (C8h) |  |

|---------|-------------|--------------|----------|--|

| _       | -           | _            | -        |  |

| 7             | 6               | 5                                                                                                                                                                                                        | 4                                                                                                                                                                                                                                                                                                                                      | 3                              | 2                                                   | 1         | 0        |  |

|---------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-----------------------------------------------------|-----------|----------|--|

| TF2           | EXF2            | RCLK                                                                                                                                                                                                     | TCLK                                                                                                                                                                                                                                                                                                                                   | EXEN2                          | TR2                                                 | C/T2#     | CP/RL2#  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                        |                                |                                                     |           |          |  |

| 7             | TF2             |                                                                                                                                                                                                          | red by softwa                                                                                                                                                                                                                                                                                                                          |                                | RCLK = 0 and                                        | TCLK = 0. |          |  |

| 6             | EXF2            | Set when a c<br>EXEN2 = 1.<br>When set, ca<br>interrupt is e<br>Must be clear                                                                                                                            | Timer 2 External Flag<br>Set when a capture or a reload is caused by a negative transition on T2EX pin if<br>EXEN2 = 1.<br>When set, causes the CPU to vector to Timer 2 interrupt routine when Timer 2<br>interrupt is enabled.<br>Must be cleared by software. EXF2 doesn't cause an interrupt in Up/down<br>counter mode (DCEN = 1) |                                |                                                     |           |          |  |

| 5             | RCLK            | Receive Clock bit for UART<br>Cleared to use Timer 1 overflow as receive clock for serial port in mode 1 or 3.<br>Set to use Timer 2 overflow as receive clock for serial port in mode 1 or 3.           |                                                                                                                                                                                                                                                                                                                                        |                                |                                                     |           |          |  |

| 4             | TCLK            | <b>Transmit Clock bit for UART</b><br>Cleared to use Timer 1 overflow as transmit clock for serial port in mode 1 or 3.<br>Set to use Timer 2 overflow as transmit clock for serial port in mode 1 or 3. |                                                                                                                                                                                                                                                                                                                                        |                                |                                                     |           |          |  |

| 3             | EXEN2           | Cleared to ig<br>Set to cause                                                                                                                                                                            | a capture or i                                                                                                                                                                                                                                                                                                                         | n T2EX pin fo<br>reload when a | r Timer 2 oper<br>negative trans<br>he serial port. |           | K pin is |  |

| 2             | TR2             | Timer 2 Rur<br>Cleared to tu<br>Set to turn o                                                                                                                                                            | Irn off Timer 2                                                                                                                                                                                                                                                                                                                        |                                |                                                     |           |          |  |

| 1             | C/T2#           | Cleared for t<br>Set for count                                                                                                                                                                           | <b>Timer/Counter 2 select bit</b><br>Cleared for timer operation (input from internal clock system: F <sub>CLK PERIPH</sub> ).<br>Set for counter operation (input from T2 input pin, falling edge trigger). Must be 0<br>for clock out mode.                                                                                          |                                |                                                     |           |          |  |

| 0             | CP/RL2#         | If RCLK = 1<br>on Timer 2 o<br>Cleared to A<br>if EXEN2 = 1                                                                                                                                              | Timer 2 Capture/Reload bit<br>If RCLK = 1 or TCLK = 1, CP/RL2# is ignored and timer is forced to Auto-reload<br>on Timer 2 overflow.<br>Cleared to Auto-reload on Timer 2 overflows or negative transitions on T2EX pin<br>if EXEN2 = 1.<br>Set to capture on negative transitions on T2EX pin if EXEN2 = 1.                           |                                |                                                     |           |          |  |

Reset Value = 0000 0000b Bit addressable

# Interrupt Sources and Vector Addresses

## Table 67. Vector Table

| Number | Polling<br>Priority | Interrupt<br>Source | Interrupt<br>Request | Vector<br>Address |

|--------|---------------------|---------------------|----------------------|-------------------|

| 0      | 0                   | Reset               |                      | 0000h             |

| 1      | 1                   | INT0                | IE0                  | 0003h             |

| 2      | 2                   | Timer 0             | TF0                  | 000Bh             |

| 3      | 3                   | INT1                | IE1                  | 0013h             |

| 4      | 4                   | Timer 1             | IF1                  | 001Bh             |

| 5      | 6                   | UART                | RI+TI                | 0023h             |

| 6      | 7                   | Timer 2             | TF2+EXF2             | 002Bh             |

| 7      | 5                   | PCA                 | CF + CCFn (n = 0-4)  | 0033h             |

| 8      | 8                   | Keyboard            | KBDIT                | 003Bh             |

| 9      | 9                   | TWI                 | TWIIT                | 0043h             |

| 10     | 10                  | SPI                 | SPIIT                | 004Bh             |

| 11     | 11                  |                     |                      | 0053h             |

| 12     | 12                  |                     |                      | 005Bh             |

| 13     | 13                  |                     |                      | 0063h             |

| 14     | 14                  | USB                 | UEPINT + USBINT      | 006Bh             |

| 15     | 15                  |                     |                      | 0073h             |

# Registers

# Table 86. SSCON Register

# SSCON - Synchronous Serial Control Register (93h)

| 7             | 6               | 5                                                                                                                                                                                                                                                                                                                                                                                                                        | 4                                                                                        | 3  | 2  | 1   | 0                                  |  |  |  |

|---------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|----|----|-----|------------------------------------|--|--|--|

| CR2           | SSIE            | STA                                                                                                                                                                                                                                                                                                                                                                                                                      | STO                                                                                      | SI | AA | CR1 | CR0                                |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                          |    |    |     |                                    |  |  |  |

| 7             | CR2             | Control Rate<br>See .                                                                                                                                                                                                                                                                                                                                                                                                    | e bit 2                                                                                  |    |    |     |                                    |  |  |  |

| 6             | SSIE            | Clear to disa                                                                                                                                                                                                                                                                                                                                                                                                            | Synchronous Serial Interface Enable bit<br>Clear to disable SSLC.<br>Set to enable SSLC. |    |    |     |                                    |  |  |  |

| 5             | STA             | Start flag<br>Set to send a                                                                                                                                                                                                                                                                                                                                                                                              | Start flag<br>Set to send a START condition on the bus.                                  |    |    |     |                                    |  |  |  |

| 4             | ST0             | Stop flag<br>Set to send a STOP condition on the bus.                                                                                                                                                                                                                                                                                                                                                                    |                                                                                          |    |    |     |                                    |  |  |  |

| 3             | SI              | Synchronous Serial Interrupt flag<br>Set by hardware when a serial interrupt is requested.<br>Must be cleared by software to acknowledge interrupt.                                                                                                                                                                                                                                                                      |                                                                                          |    |    |     |                                    |  |  |  |

| 2             | AA              | Assert Acknowledge flag<br>Clear in master and slave receiver modes, to force a not acknowledge (high level<br>on SDA).<br>Clear to disable SLA or GCA recognition.<br>Set to recognise SLA or GCA (if GC set) for entering slave receiver or transmitter<br>modes.<br>Set in master and slave receiver modes, to force an acknowledge (low level on<br>SDA).<br>This bit has no effect when in master transmitter mode. |                                                                                          |    |    |     |                                    |  |  |  |

| 1             | CR1             | Control Rate bit 1<br>See Table 80                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                          |    |    |     |                                    |  |  |  |

| 0             | CR0             |                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                          |    |    |     | Control Rate bit 0<br>See Table 80 |  |  |  |

# Table 87. SSDAT (095h) - Synchronous Serial Data Register (read/write)

| SD7           | SD6             | SD5                          | SD4                          | SD3 | SD2 | SD1 | SD0 |

|---------------|-----------------|------------------------------|------------------------------|-----|-----|-----|-----|

| 7             | 6               | 5                            | 4                            | 3   | 2   | 1   | 0   |

| Bit<br>Number | Bit<br>Mnemonic | Description                  |                              |     |     |     |     |

| 7             | SD7             | Address bit 7                | Address bit 7 or Data bit 7. |     |     |     |     |

| 6             | SD6             | Address bit 6                | Address bit 6 or Data bit 6. |     |     |     |     |

| 5             | SD5             | Address bit 5                | Address bit 5 or Data bit 5. |     |     |     |     |

| 4             | SD4             | Address bit 4 or Data bit 4. |                              |     |     |     |     |

| 3             | SD3             | Address bit 3 or Data bit 3. |                              |     |     |     |     |

| 2             | SD2             | Address bit 2                | Address bit 2 or Data bit 2. |     |     |     |     |

Endpoint enable

.

Before using an endpoint, this one will be enabled by setting the EPEN bit in the UEPCONX register.

An endpoint which is not enabled won't answer to any USB request. The Default Control Endpoint (Endpoint 0) will always be enabled in order to answer to USB standard requests.

Endpoint type configuration

All Standard Endpoints can be configured in Control, Bulk, Interrupt or Isochronous mode. The Ping-pong Endpoints can be configured in Bulk, Interrupt or Isochronous mode. The configuration of an endpoint is performed by setting the field EPTYPE with the following values:

- Control:EPTYPE = 00b

- Isochronous:EPTYPE = 01b

- Bulk:EPTYPE = 10b

- Interrupt:EPTYPE = 11b

The Endpoint 0 is the Default Control Endpoint and will always be configured in Control type.

Endpoint direction configuration

For Bulk, Interrupt and Isochronous endpoints, the direction is defined with the EPDIR bit of the UEPCONX register with the following values:

- IN:EPDIR = 1b

- OUT:EPDIR = 0b

For Control endpoints, the EPDIR bit has no effect.

• Summary of Endpoint Configuration:

Do not forget to select the correct endpoint number in the UEPNUM register before accessing to endpoint specific registers.

| Endpoint Configuration | EPEN | EPDIR | EPTYPE | UEPCONX   |

|------------------------|------|-------|--------|-----------|

| Disabled               | 0b   | Xb    | XXb    | 0XXX XXXb |

| Control                | 1b   | Xb    | 00b    | 80h       |

| Bulk-in                | 1b   | 1b    | 10b    | 86h       |

| Bulk-out               | 1b   | 0b    | 10b    | 82h       |

| Interrupt-In           | 1b   | 1b    | 11b    | 87h       |

| Interrupt-Out          | 1b   | 0b    | 11b    | 83h       |

| Isochronous-In         | 1b   | 1b    | 01b    | 85h       |

| Isochronous-Out        | 1b   | 0b    | 01b    | 81h       |

Table 90. Summary of Endpoint Configuration

| 7          | 6 IEPSTAX       | 5.CEII) (                                                                           | 5 5 5 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | X Status Regis<br>4                                             | 3                    | 2                                            | 1                                                                   | 0            |  |  |

|------------|-----------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|----------------------|----------------------------------------------|---------------------------------------------------------------------|--------------|--|--|

| DIR        | RXOU            | TB1                                                                                 | STALLRQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | TXRDY                                                           | STL/CRC              | RXSETUP                                      | RXOUTB0                                                             | ТХСМР        |  |  |

| Bit Number | Bit<br>Mnemonic | Descrip                                                                             | tion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                 |                      |                                              |                                                                     |              |  |  |

| 7          | DIR             | This bit i<br>USB En<br>This bit<br>The dev                                         | ntrol Endpoint Direction<br>s bit is used only if the endpoint is configured in the control type (seeSection "UEPCONX Register UEPCONX (S:D4h)<br>B Endpoint X Control Register").<br>s bit determines the Control data and status direction.<br>e device firmware will set this bit ONLY for the IN data stage, before any other USB operation. Otherwise, the device<br>nware will clear this bit.                                                                                                                                                                                                                                                                                                                                                                    |                                                                 |                      |                                              |                                                                     |              |  |  |

| 6          | RXOUTB1         | This bit i<br>Then, th<br>Interrupt<br>bit has b                                    | ceived OUT Data Bank 1 for Endpoints 4, 5 and 6 (Ping-pong mode)<br>is bit is set by hardware after a new packet has been stored in the endpoint FIFO data bank 1 (only in Ping-pong mode).<br>en, the endpoint interrupt is triggered if enabled (see"UEPINT Register UEPINT (S:F8h read-only) USB Endpoint<br>errupt Register" on page 145) and all the following OUT packets to the endpoint bank 1 are rejected (NAK'ed) until this<br>has been cleared, excepted for Isochronous Endpoints.<br>s bit will be cleared by the device firmware after reading the OUT data from the endpoint FIFO.                                                                                                                                                                     |                                                                 |                      |                                              |                                                                     |              |  |  |

| 5          | STALLRQ         | Set this                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | FALL answer to the                                              | host for the next ha |                                              |                                                                     |              |  |  |

| 4          | TXRDY           | Set this<br>endpoin<br>Length I<br>This bit<br>acknowl                              | X Packet Ready<br>et this bit after a packet has been written into the endpoint FIFO for IN data transfers. Data will be written into the<br>ndpoint FIFO only after this bit has been cleared. Set this bit without writing data to the endpoint FIFO to send a Zero<br>ength Packet.<br>his bit is cleared by hardware, as soon as the packet has been sent for Isochronous endpoints, or after the host has<br>cknowledged the packet for Control, Bulk and Interrupt endpoints. When this bit is cleared, the endpoint interrupt is<br>iggered if enabled (see"UEPINT Register UEPINT (S:F8h read-only) USB Endpoint Interrupt Register" on page 145).                                                                                                              |                                                                 |                      |                                              |                                                                     |              |  |  |

| 3          | STLCRC          | - For Co<br>This bit<br>interrupt<br>page 14<br>It will be<br>- For Isc<br>This bit | Stall Sent/CRC error flag<br>For Control, Bulk and Interrupt Endpoints:<br>This bit is set by hardware after a STALL handshake has been sent as requested by STALLRQ. Then, the endpoint<br>interrupt is triggered if enabled (see"UEPINT Register UEPINT (S:F8h read-only) USB Endpoint Interrupt Register" on<br>page 145)<br>t will be cleared by the device firmware.<br>For Isochronous Endpoints ( <b>Read-Only</b> ):<br>This bit is set by hardware if the last received data is corrupted (CRC error on data).<br>This bit is updated by hardware when a new data is received.                                                                                                                                                                                 |                                                                 |                      |                                              |                                                                     |              |  |  |

| 2          | RXSETUP         | This bit<br>register<br>read-on                                                     | Received SETUP<br>This bit is set by hardware when a valid SETUP packet has been received from the host. Then, all the other bits of the<br>register are cleared by hardware and the endpoint interrupt is triggered if enabled (see"UEPINT Register UEPINT (S:F<br>read-only) USB Endpoint Interrupt Register" on page 145).<br>It will be cleared by the device firmware after reading the SETUP data from the endpoint FIFO.                                                                                                                                                                                                                                                                                                                                         |                                                                 |                      |                                              |                                                                     |              |  |  |

| 1          | RXOUTB0         | This bit<br>interrupt<br>page 14<br>excepte<br>content                              | Received OUT Data Bank 0 (see also RXOUTB1 bit for Ping-pong Endpoints)<br>This bit is set by hardware after a new packet has been stored in the endpoint FIFO data bank 0. Then, the endpoint<br>nterrupt is triggered if enabled (see"UEPINT Register UEPINT (S:F8h read-only) USB Endpoint Interrupt Register" on<br>page 145) and all the following OUT packets to the endpoint bank 0 are rejected (NAK'ed) until this bit has been cleared,<br>excepted for Isochronous Endpoints. However, for control endpoints, an early SETUP transaction may overwrite the<br>content of the endpoint FIFO, even if its Data packet is received while this bit is set.<br>This bit will be cleared by the device firmware after reading the OUT data from the endpoint FIFO. |                                                                 |                      |                                              |                                                                     |              |  |  |

| 0          | TXCMPL          | This bit<br>accepte<br>enabled                                                      | d (ACK'ed) by the<br>(see"UEPINT Re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | after an IN packet<br>host for Control, B<br>gister UEPINT (S:F | ulk and Interrupt en | dpoints. Then, the e<br>Endpoint Interrupt I | endpoints and after<br>endpoint interrupt is<br>Register" on page 1 | triggered if |  |  |

Table 98. UEPSTAX (S:CEh) USB Endpoint X Status Registe

Reset Value = 00h

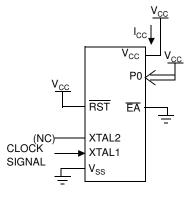

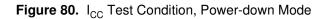

Figure 79.  $I_{\text{CC}}$  Test Condition, Idle Mode

All other pins are disconnected.

All other pins are disconnected.

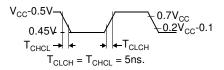

Figure 81. Clock Signal Waveform for  $\mathrm{I}_{\mathrm{CC}}$  Tests in Active and Idle Modes

## LED's

Table 113. LED Outputs DC Parameters

| Symb            | ool F                                                       | Parameter | Min | Тур | Max | Unit               | Test Conditions     |

|-----------------|-------------------------------------------------------------|-----------|-----|-----|-----|--------------------|---------------------|

|                 |                                                             |           | 1   | 2   | 4   | mA                 | 2 mA configuration  |

| I <sub>OL</sub> | I <sub>OL</sub> Output Low Current, P3.6 and P3.7 LED modes | 2         | 4   | 8   | mA  | 4 mA configuration |                     |

|                 |                                                             |           | 5   | 10  | 20  | mA                 | 10 mA configuration |

Note: 1. (Ta = -20°C to +50°C, V<sub>CC</sub> - V<sub>OL</sub> = 2 V  $\pm$  20%)

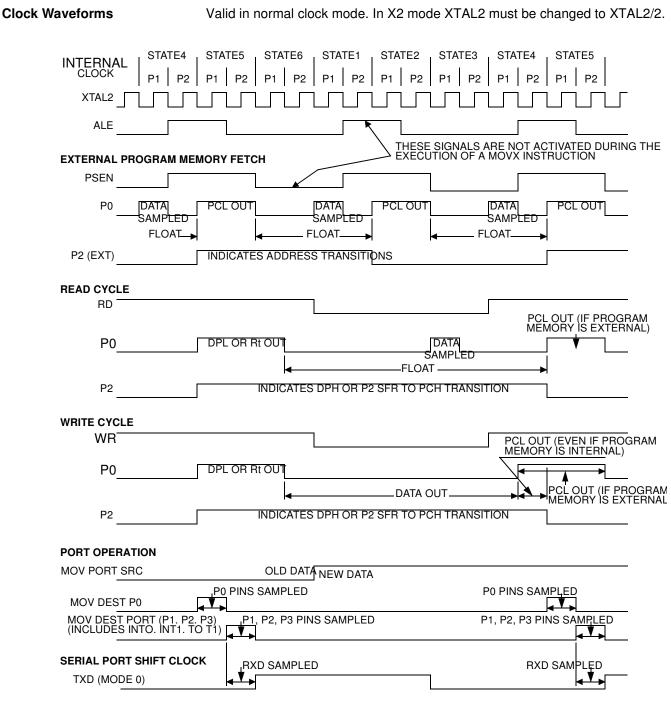

This diagram indicates when signals are clocked internally. The time it takes the signals to propagate to the pins, however, ranges from 25 to 125 ns. This propagation delay is dependent on variables such as temperature and pin loading. Propagation also varies from output to output and component. Typically though ( $T_A = 25^{\circ}C$  fully loaded) RD and WR propagation delays are approximately 50 ns. The other signals are typically 85 ns. Propagation delays are incorporated in the AC specifications.

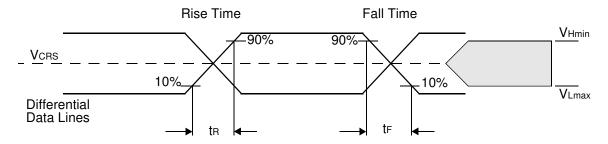

# **USB AC Parameters**

### Table 126. USB AC Parameters

| Symbol              | Parameter                                      | Min     | Тур | Max     | Unit | Test Conditions |

|---------------------|------------------------------------------------|---------|-----|---------|------|-----------------|

| t <sub>R</sub>      | Rise Time                                      | 4       |     | 20      | ns   |                 |

| t <sub>F</sub>      | Fall Time                                      | 4       |     | 20      | ns   |                 |

| t <sub>FDRATE</sub> | Full-speed Data Rate                           | 11.9700 |     | 12.0300 | Mb/s |                 |

| $V_{CRS}$           | Crossover Voltage                              | 1.3     |     | 2.0     | V    |                 |

| t <sub>DJ1</sub>    | Source Jitter Total to Next<br>Transaction     | -3.5    |     | 3.5     | ns   |                 |

| t <sub>DJ2</sub>    | Source Jitter Total for Paired<br>Transactions | -4      |     | 4       | ns   |                 |

| t <sub>JR1</sub>    | Receiver Jitter to Next<br>Transaction         | -18.5   |     | 18.5    | ns   |                 |

| t <sub>JR2</sub>    | Receiver Jitter for Paired<br>Transactions     | -9      |     | 9       | ns   |                 |

## **SPI Interface AC Parameters**

Definition of Symbols

# Table 127. SPI Interface Timing Symbol Definitions

| Signals |          |  |  |  |

|---------|----------|--|--|--|

| С       | Clock    |  |  |  |

| 1       | Data In  |  |  |  |

| 0       | Data Out |  |  |  |

| Conditions |                 |  |  |  |

|------------|-----------------|--|--|--|

| н          | High            |  |  |  |

| L          | Low             |  |  |  |

| V          | Valid           |  |  |  |

| Х          | No Longer Valid |  |  |  |

| Z          | Floating        |  |  |  |

# **Ordering Information**

# Table 129. Possible Order Entries

| Part Number      | Memory Size (Kbytes) | Supply Voltage | Temperature Range  | Package | Packing |

|------------------|----------------------|----------------|--------------------|---------|---------|

| AT89C5131A-RDTIL | 32                   | 3.0 to 3.6V    | Industrial         | VQFP64  | Tray    |

| AT89C5131A-S3SIL | 32                   | 3.0 to 3.6V    | Industrial         | PLCC52  | Stick   |

| AT89C5131A-TISIL | 32                   | 3.0 to 3.6V    | Industrial         | SO28    | Stick   |

|                  |                      |                |                    |         |         |

| AT89C5131A-RDTUL | 32                   | 3.0 to 3.6V    | Industrial & Green | VQFP64  | Tray    |

| AT89C5131A-S3SUL | 32                   | 3.0 to 3.6V    | Industrial & Green | PLCC52  | Stick   |

| AT89C5131A-TISUL | 32                   | 3.0 to 3.6V    | Industrial & Green | SO28    | Stick   |

1. Optional Packing and Package options (please consult Atmel sales representative): Note:

-Tape and Reel

-Dry Pack -Known good dice