Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

⊡XFI

| Detalls                    |                                                                                        |

|----------------------------|----------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                 |

| Core Processor             | 8051                                                                                   |

| Core Size                  | 8-Bit                                                                                  |

| Speed                      | 40MHz                                                                                  |

| Connectivity               | EBI/EMI, SPI, UART/USART                                                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                             |

| Number of I/O              | 40                                                                                     |

| Program Memory Size        | 16KB (16K x 8)                                                                         |

| Program Memory Type        | FLASH                                                                                  |

| EEPROM Size                | -                                                                                      |

| RAM Size                   | 1.25K x 8                                                                              |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 5.5V                                                                            |

| Data Converters            | -                                                                                      |

| Oscillator Type            | Internal                                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                      |

| Mounting Type              | Surface Mount                                                                          |

| Package / Case             | 48-LQFP                                                                                |

| Supplier Device Package    | -                                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/nuvoton-technology-corporation-america/n78e055alg |

|                            |                                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Table 4–1. Pin Description

|     | Pin n | umber |      | Symbol | Alternate | • Function | Type <sup>[1]</sup> | Description                                                                                                     |  |  |  |

|-----|-------|-------|------|--------|-----------|------------|---------------------|-----------------------------------------------------------------------------------------------------------------|--|--|--|

| DIP | PLCC  | PQFP  | LQFP | Symbol | 1         | 2          | i ype               | Description                                                                                                     |  |  |  |

|     |       |       |      |        |           |            |                     | an external capacitor to V <sub>DD</sub> .                                                                      |  |  |  |

| 39  | 43    | 37    | 40   | P0.0   |           | AD0        | D, I/O              | <b>PORT0:</b> Port 0 is an 8-bit open-drain port by default.                                                    |  |  |  |

| 38  | 42    | 36    | 39   | P0.1   |           | AD1        | D, I/O              | Via setting P0UP (P0OR.0), P0 will switch as weakly pulled up internally.                                       |  |  |  |

| 37  | 41    | 35    | 38   | P0.2   |           | AD2        | D, I/O              | P0 has an alternative function as AD[7:0] while ex-<br>ternal memory accessing. During the external             |  |  |  |

| 36  | 40    | 34    | 37   | P0.3   |           | AD3        | D, I/O              | memory access, P0 will output high will be internal strong pulled-up rather than weak pull-up in order to       |  |  |  |

| 35  | 39    | 33    | 35   | P0.4   |           | AD4        | D, I/O              | drive out high byte address for external devices.                                                               |  |  |  |

| 34  | 38    | 32    | 34   | P0.5   |           | AD5        | D, I/O              |                                                                                                                 |  |  |  |

| 33  | 37    | 31    | 33   | P0.6   |           | AD6        | D, I/O              |                                                                                                                 |  |  |  |

| 32  | 36    | 30    | 32   | P0.7   |           | AD7        | D, I/O              | 015                                                                                                             |  |  |  |

| 1   | 2     | 40    | 43   | P1.0   | T2        |            | I/O                 | <b>PORT1:</b> Port 1 is an 8-bit quasi bi-directional I/O port. Its multifunction pins are for T2, T2EX,        |  |  |  |

| 2   | 3     | 41    | 44   | P1.1   | T2EX      |            | I/O                 | $PWM0{\sim}PWM4, \ \overline{SS}, \ MOSI, \ MISO, \ and \ SPCLK.$                                               |  |  |  |

| 3   | 4     | 42    | 45   | P1.2   |           |            | I/O                 |                                                                                                                 |  |  |  |

| 4   | 5     | 43    | 46   | P1.3   | PWM0      |            | I/O                 |                                                                                                                 |  |  |  |

| 5   | 6     | 44    | 47   | P1.4   | PWM1      | SS         | I/O                 |                                                                                                                 |  |  |  |

| 6   | 7     | 1     | 1    | P1.5   | PWM2      | MOSI       | I/O                 |                                                                                                                 |  |  |  |

| 7   | 8     | 2     | 2    | P1.6   | PWM3      | MISO       | I/O                 |                                                                                                                 |  |  |  |

| 8   | 9     | 3     | 3    | P1.7   | PWM4      | SPCLK      | I/O                 |                                                                                                                 |  |  |  |

| 21  | 24    | 18    | 19   | P2.0   |           | A8         | I/O                 | <b>PORT2:</b> Port 2 is an 8-bit quasi bi-directional I/O port. It has an alternative function as A[15:8] while |  |  |  |

| 22  | 25    | 19    | 20   | P2.1   |           | A9         | I/O                 | external memory accessing. During the external memory access, P2 will output high will be internal              |  |  |  |

| 23  | 26    | 20    | 21   | P2.2   |           | A10        | I/O                 | strong pulled-up rather than weak pull-up in order to<br>drive out high byte address for external devices.      |  |  |  |

| 24  | 27    | 21    | 22   | P2.3   |           | A11        | I/O                 | anve out high byte address for external devices.                                                                |  |  |  |

| 25  | 28    | 22    | 23   | P2.4   |           | A12        | I/O                 |                                                                                                                 |  |  |  |

| 26  | 29    | 23    | 25   | P2.5   | 20        | A13        | I/O                 |                                                                                                                 |  |  |  |

| 27  | 30    | 24    | 26   | P2.6   | RC        | A14        | I/O                 |                                                                                                                 |  |  |  |

| 28  | 31    | 25    | 27   | P2.7   | 10        | A15        | I/O                 | 1                                                                                                               |  |  |  |

## 5.3 Internal Data Memory

Figure 5–3 shows the internal and external Data Memory spaces available on N78E059A/N78E055A. Internal Data Memory can be divided into three blocks. They are the lower 128 bytes of RAM, the upper 128 bytes of RAM, and the 128 bytes of SFR space. Internal Data Memory addresses are always 8-bit wide, which implies an address space of only 256 bytes. Direct addressing higher than 7FH will access the special function registers (SFRs) space and indirect addressing higher than 7FH will access the upper 128 bytes of RAM. Although the SFR space and the upper 128 bytes of RAM share the same logic address, 80H through FFH, actually they are physically separate entities. Direct addressing to distinguish with the higher 128 bytes of RAM can only access these SFRs. Sixteen addresses in SFR space are both byte and bit-addressable. The bit-addressable SFRs are those whose addresses end in 0H or 8H.

The lower 128 bytes of internal RAM are present in all 8051 devices. The lowest 32 bytes are grouped into 4 banks of 8 registers. Program instructions call these registers as R0 through R7. Two bits RS0 and RS1 in the Program Status Word (PSW[3:4]) select which Register Bank is used. This benefits more efficiency of code space, since register instructions are shorter than instructions that use direct addressing. The next 16 bytes above the Register Banks (byte-address 20H through 2FH) form a block of bit-addressable memory space (bitaddress 00H through 7FH). The 8051 instruction set includes a wide selection of single-bit instructions, and the 128 bits in this area can be directly addressed by these instructions. The bit addresses in this area are 00H through 7FH.

All bytes in the lower 128-byte space can be accessed by either direct or indirect addressing. Indirect addressing can only access the upper 128.

Another application implemented with the whole block of internal 256-byte RAM is for the stack. This area is selected by the Stack Pointer (SP), which stores the address of the top of the stack. Whenever a JMP, CALL or interrupt is invoked, the return address is placed on the stack. There is no restriction as to where the stack can begin in the RAM. By default however, the Stack Pointer contains 07H at reset. The user can then change this to any value desired. The SP will point to the last used value. Therefore, the SP will be incremented and then address saved onto the stack. Conversely, while popping from the stack the contents will be read first, , decre and then the SP is decreased.

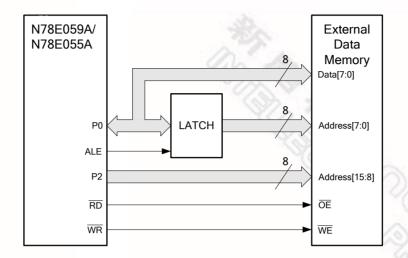

Figure 5–5. Data Memory Interface

## 5.6 On-chip Non-volatile Data Flash

N78E059A/N78E055A additionally has Data Flash. The Data Flash is non-volatile so that it remains its content even after the power is off. Therefore, in general application the user can write or read data which rules as parameters or constants. Be aware of Data Flash writing endurance of 10,000 cycles. By the software path, the Data Flash can be accessed only through ISP mode. Note that the erasing or writing of Data Flash should not operates under V<sub>DD</sub> 3.0V for ISP limitation. For Data Flash accessing with ISP, please see <u>Section 18. "IN</u> <u>SYSTEM PROGRAMMING (ISP)" on page 91</u> for details. For the design for security, ISP is invalid while external Program Memory executes. The Data Flash, therefore, cannot be accessed with external memory code. Of course the Data Flash can be accessed via hardware with parallel Programmer/Writer.

The Data Flash size is fixed as 4k-byte size on N78E059A/N78E055A.

### Table 6–2. N78E059A/N78E055A SFR Descriptions and Reset Values

| Symbol                | Definition                             | Address    | MSB         |             |             |               |                    |              |             | LSB <sup>[1]</sup> | Reset                                            | Value              |

|-----------------------|----------------------------------------|------------|-------------|-------------|-------------|---------------|--------------------|--------------|-------------|--------------------|--------------------------------------------------|--------------------|

| SPDR                  | SPI data                               | F5H        |             |             |             | 100           |                    |              |             |                    | 0000                                             |                    |

| SPSR                  | SPI status                             | F4H        | SPIF        | WCOL        | SPIOVF      | MODF          | DISMODF            | -            | -           | -                  | 0000                                             | 000                |

| SPCR                  | SPI control                            | F3H        | SSOE        | SPIEN       | LSBFE       | MSTR          | CPOL               | CPHA         | SPR1        | SPR0               | 0000                                             |                    |

| B                     | B register                             | F0H        | (F7)        | (F6)        | (F5)        | (F4)          | (F3)               | (F2)         | (F1)        | (F0)               | 0000                                             |                    |

| ACC                   | Accumulator                            | E0H        | (E7)        | (E6)        | (E5)        | (E4)          | (E3)               | (E2)         | (E1)        | (E0)               | 0000                                             |                    |

| PWM3                  | PWM3 duty                              | DEH        | (= / )      | (20)        | (20)        | (= 1)         | (20)               | (==)         | (= !)       | (20)               | 0000                                             |                    |

| PWM2                  | PWM2 duty                              | DDH        | -           |             |             | 1             | 0 1                | 132          |             |                    | 0000                                             |                    |

|                       |                                        | DCH        | PW/M3OF     | PW/M2OF     | PW/M3EN     | PW/M2EN       | PWM10E             | PW/MOOF      | PWM1EN      | PW/MOEN            |                                                  |                    |

| PWM1                  | PWM1 duty                              | DBH        | TWINGOL     | TWIMEOL     | TWINGEN     |               | TWINTOL            | TWINOOL      | TVINILLI    | TWINGEN            | 0000                                             |                    |

| PWM0                  | PWM0 duty                              | DAH        |             |             |             |               |                    | 1            |             |                    | 0000                                             |                    |

| PWMP                  | PWM period                             | DAH<br>D9H |             |             |             |               | - MC               |              |             |                    | 0000                                             |                    |

|                       |                                        | Dau        | (DF)        | (DE)        | (DD)        | (DC)          | (DB)               |              | (D9)        | (D8)               | 0000                                             | 000                |

| P4                    | Port 4                                 | D8H        | (DF)        | (DE)        | (00)        | (DC)          | INT2               | (DA)<br>INT3 | (D9)        | (D0)               | 1111                                             | 11                 |

| PSW                   | Program status word                    | D0H        | (D7)<br>CY  | (D6)<br>AC  | (D5)<br>F0  | (D4)<br>RS1   | (D3)<br>RS0        | (D2)<br>OV   | (D1)<br>F1  | (D0)<br>P          | 0000                                             | 000                |

| PWM4                  | PWM4 duty                              | CFH        |             |             |             |               |                    |              | 2           | 1 ling             | 0000                                             | 00                 |

| PWMCON1               | PWM control 1                          | CEH        | -           | -           | -           | -             | -                  | PWM4OE       | 6.20        | PWM4EN             |                                                  |                    |

| TH2                   | Timer 2 high byte                      | CDH        |             |             |             |               | 1                  |              | 7.0         | 0. (6              | 0000                                             |                    |

| TL2                   | Timer 2 low byte                       | CCH        |             |             |             |               |                    |              | 11          |                    | 0000                                             |                    |

| RCAP2H                | Timer 2 reload/capture<br>high byte    | СВН        |             |             |             |               |                    |              | 1           | 20                 | 0000                                             |                    |

| RCAP2L                | Timer 2 reload/capture<br>low byte     | CAH        |             |             |             |               |                    |              |             | - 73               | 0000                                             | 00                 |

| T2MOD                 | Timer 2 mode                           | C9H        | -           | -           | -           | -             | -                  | -            | T2OE        |                    | 0000                                             | 000                |

|                       |                                        | 2.5.1.     | (CF)        | (CE)        | (CD)        | (CC)          | (CB)               | (CA)         | (C9)        | (C8)               |                                                  |                    |

| T2CON                 | Timer 2 control                        | C8H        | TF2         | EXF2        | RCLK        | TCLK          | EXEN2              | TR2          | C/T2        | CP/RL2             | 0000                                             |                    |

| ТА                    | Timed access protection                | C7H        |             |             |             |               |                    |              |             |                    | 0000                                             | 000                |

| XICON                 | External interrupt control             | СОН        | (C7)<br>PX3 | (C6)<br>EX3 | (C4)<br>IE3 | (C4)<br>IT3   | (C3)<br>PX2        | (C2)<br>EX2  | (C1)<br>IE2 | (C0)<br>1IT2       | 0000                                             | 000                |

| EIE                   | Extensive interrupt ena-<br>ble        | BDH        | -           | -           | -           | -             | -                  | EBOD         | EPDT        | ESPI               | 0000                                             | 000                |

| EIP                   | Extensive interrupt priori-<br>ty      | BCH        | -           | -           | -           | -             | -                  | PBOV         | PPDT        | PSPI               | 0000                                             | 000                |

| EIPH                  | Extensive interrupt priori-<br>ty high | BBH        | -           | -           | -           | -             | -                  | PBODH        | PPDTH       | PSPIH              | 0000                                             |                    |

| IPH                   | Interrupt priority high                | BAH        | PX3H        | PX2H        | PT2H        | PSH           | PT1H               | PX1H         | PT0H        | PX0H               | 0000                                             | 000                |

| IP                    | Interrupt priority                     | B8H        | (BF)<br>-   | (BE)<br>-   | (BD)<br>PT2 | (BC)<br>PS    | (BB)<br>PT1        | (BA)<br>PX1  | (B9)<br>PT0 | (B8)<br>PX0        | 0000                                             | 00(                |

| P3                    | Port 3                                 | B0H        | (B7)        | (B6)        | (B5)        | (B4)          | (B3)               | (B2)         | (B1)        | (B0)               | 1111                                             | 11                 |

|                       |                                        |            | RD          | WR          | T1          | Т0            | INT1               | INT0         | TXD         | RXD                |                                                  |                    |

| ISPCN                 | ISP flash control                      | AFH        | ISPA17      | ISPA16      | FOEN        | FCEN          | FCTRL3             | FCTRL2       | FCTRL1      | FCTRL0             | 0000                                             | 00                 |

| ISPFD                 | ISP flash data                         | AEH        |             |             |             |               |                    |              |             |                    | 0000                                             | 00                 |

| PMC <sup>[3]</sup>    | Power monitoring control               | ACH        | BODEN       | -           | -           | BORST         | BOF <sup>[4]</sup> | LPBOD        | -           | BOS <sup>[5]</sup> | Power<br>XXXX<br>Brown<br>XXXX<br>Others<br>XXXX | X0<br>-out,<br>10  |

| PDCON                 | Power Down waking-up<br>timer control  | ABH        | PDTEN       | PDTCK       | PDTF        | -             | -                  | PPS2         | PPS1        | PPS0               | 0000                                             |                    |

| WDCON <sup>[3]</sup>  | Watchdog Timer control                 | ААН        | WDTEN       | WDCLR       | -           | WIDPD         | WDTRF              | WPS2         | WPS1        | WPS0               | Power<br>X000<br>Watch<br>X00U<br>Others<br>X00U | 000<br>dog,<br>1UU |

| IE                    | Interrupt enable                       | A8H        | (AF)<br>EA  | (AE)<br>-   | (AD)<br>ET2 | (AC)<br>ES    | (AB)<br>ET1        | (AA)<br>EX1  | (A9)<br>ET0 | (A8)<br>EX0        | 0000                                             |                    |

| ISPAH                 | ISP address high byte                  | A7H        | Sec. 1      |             |             |               |                    |              |             |                    | 0000                                             |                    |

| ISPAL                 | ISP address low byte                   | A6H        | No          |             |             |               |                    |              |             |                    | 0000                                             | 00                 |

| ISPTRG <sup>[3]</sup> | ISP trigger                            | A4H        | 2.          | -           | -           | -             | -                  | -            | -           | ISPGO              | 0000                                             | 00                 |

| XRAMAH                | Auxiliary RAM address                  | A1H        | 46          | s           | -           | -             | -                  | -            |             | XRAMAH.0           | 1                                                |                    |

|                       |                                        | ~~~        | (A7)        | (AG)        | (A5)        | $(\Lambda A)$ | (A3)               | (A2)         | (A1)        | (A0)               |                                                  |                    |

| P2                    | Port 2                                 | A0H        | (A7)<br>A15 | (A6)<br>A14 | (A5)<br>A13 | (A4)<br>A12   | (43)               | (A2)<br>A10  | (A1)        | (AU)               | 1111                                             | 1 1                |

### PCON – Power Control

| 7            | 6                                                                                           | 5 | 4   | 3   | 2   | 1   | 0   |  |  |

|--------------|---------------------------------------------------------------------------------------------|---|-----|-----|-----|-----|-----|--|--|

| SMOD         | -                                                                                           | - | POF | GF1 | GF0 | PD  | IDL |  |  |

| r/w          | -                                                                                           | - | r/w | r/w | r/w | r/w | r/w |  |  |

| Address: 87H | Address: 87H reset value: see Table 6-2 N78E059A/N78E055A SER Descriptions and Reset Values |   |     |     |     |     |     |  |  |

Address: 87H

reset value: see <u>Table 6–2. N78E059A/N78E055A SFR Descriptions and Reset Values</u>

| Bit | Name | Description                                                                                 |

|-----|------|---------------------------------------------------------------------------------------------|

| 3   | GF1  | General purpose flag 1.<br>The general purpose flag that can be set or cleared by the user. |

| 2   | GF0  | General purpose flag 0.<br>The general purpose flag that can be set or cleared by the user. |

## 8. AUXILIARY RAM (XRAM)

N78E059A/N78E055A provides additional on-chip 1k-byte RAM called XRAM to enlarge the RAM space. It occupies the address space from 000H through 3FFH. The XRAM is enabled after all resets. The 1024 bytes of XRAM are indirectly accessed by move external instruction MOVX @DPTR or MOVX @Ri along with XRAMAH. (If XRAM is enabled, MOVX @Ri cannot be used to access external RAM anymore.) This block of XRAM shares the same logic address of 000H through 3FFH with the external RAM. A DPTR value given larger than 03FFH will map to the external RAM no matter of the value of bit XRAMEN (CHPCON.4). If the user would like to access contents within 000H to 3FFH address of the off-chip external XRAM, the XRAMEN bit should be cleared as logic 0. (Note that CHPCON is a TA writing protected SFR.) When the XRAM is accessed, the address fetching signal will not emit via P0, P2, WR, and RD. Note that the stack pointer cannot locate in any part of XRAM.

### CHPCON – Chip Control (TA protected)

|              |                                                                                             |       | 1      |   |   |     |       |

|--------------|---------------------------------------------------------------------------------------------|-------|--------|---|---|-----|-------|

| 7            | 6                                                                                           | 5     | 4      | 3 | 2 | 1   | 0     |

| SWRST        | ISPF                                                                                        | LDUEN | XRAMEN | - | - | BS  | ISPEN |

| W            | r/w                                                                                         | r/w   | r/w    | - | - | r/w | r/w   |

| Address: QFH | Address: 9EH reset value: see Table 6-2 N78E0594/N78E0554 SER Descriptions and Reset Values |       |        |   |   |     |       |

Address: 9FH reset value: see <u>Table 6–2. N78E059A/N78E055A SFR Descriptions and Reset Values</u>

| Bit | Name   | Description                                                   |

|-----|--------|---------------------------------------------------------------|

| 4   | XRAMEN | XRAM enable.                                                  |

|     |        | 0 = Disable on-chip XRAM.                                     |

|     |        | 1 - Enable on chin XRAM (The default value after all resets ) |

1 = Enable on-chip XRAM. (The default value after all resets.)

### XRAMAH – XRAM Address High Byte

|   | 7 | 6 | 5 | 4 | 3 | 2 | 1        | 0        |

|---|---|---|---|---|---|---|----------|----------|

| 3 | - | - | - | - | - | - | XRAMAH.1 | XRAMAH.0 |

| 7 | - | - | - | - | - | - | r/w      | r/w      |

|   |   |   |   |   |   |   |          |          |

Address: A1H

MOV

R0,#23H

reset value: 0000 0000b

|      | Bit                       | Name                                      | Description                                                                                                                                           |

|------|---------------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | 7:2                       | 25                                        | Reserved.                                                                                                                                             |

|      | 1:0                       | XRAMAH[1:0]                               | XRAM address high byte.<br>To set the XRAM high byte address. This setting works along with MOV @Ri<br>instructions. The demo codes are listed below. |

| XRAM | l demo c                  | ode:                                      |                                                                                                                                                       |

|      | MOV<br>MOV<br>MOV<br>MOVX | XRAMAH,#01H<br>R0,#23H<br>A,#5AH<br>@R0,A | ;write #5AH to XRAM with address @0123H.                                                                                                              |

|      | MOV                       | XRAMAH,#01H                               | ;read from XRAM with address @0123H.                                                                                                                  |

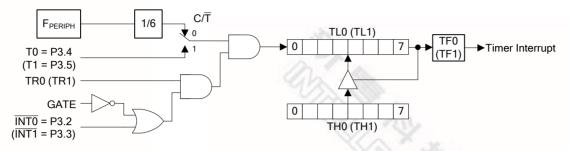

Figure 10-3. Timer/Counter 0 and 1 in Mode 2

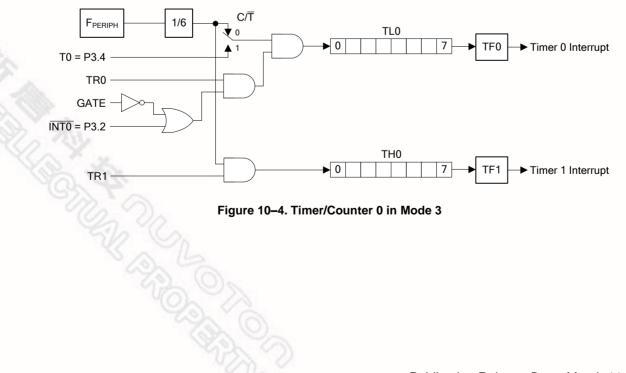

## 10.1.4 Mode 3 (Two Separate 8-bit Timers)

Mode 3 has different operating methods for the two Timer/Counters. For Timer/Counter 1, Mode 3 simply freezes the counter. Timer/Counter 0, however, configures TL0 and TH0 as two separate 8 bit count registers in this mode. TL0 uses the Timer/Counter 0 control bits  $C/\overline{T}$ , GATE, TR0,  $\overline{INT0}$ , and TF0. The TL0 also can be used as a 1-to-0 transition counter on pin T0 as determined by  $C/\overline{T}$  (TMOD.2). TH0 is forced as a clock cycle counter and takes over the usage of TR1 and TF1 from Timer/Counter 1. Mode 3 is used in case which an extra 8 bit timer is needed. If Timer/Counter 0 is configured in Mode 3, Timer/Counter 1 can be turned on or off by switching it out of or into its own Mode 3. It can still be used in Modes 0, 1 and 2 although its flexibility is restricted. It no longer has control over its overflow flag TF1 and the enable bit TR1. However Timer 1 can still be used as a Timer/Counter and retains the use of GATE and  $\overline{INT1}$  pin. It can be used as a baud rate generator for the serial port or other application not requiring an interrupt.

| Timer 2 Mode                  | RCLK (T2CON.5)<br>or<br>TCLK (T2CON.4) | CP/RL2 (T2CON.0) | T2OE (T2MOD.1) |

|-------------------------------|----------------------------------------|------------------|----------------|

| 16-bit capture <sup>[1]</sup> | 0                                      | 1                | x              |

| 16-bit auto-reload            | 0                                      | 0                | 0              |

| Baud rate generator           | 1                                      | Х                | 0              |

| Clock-out <sup>[2]</sup>      | Х                                      | 0                | GA T           |

[1] The capture is valid while EXEN2 (T2CON.3) is a 1. Or Timer/Counter 2 behaves just like a 16-bit timer/counter. [2]  $C/\overline{T2}$  (T2CON.1) must be 0.

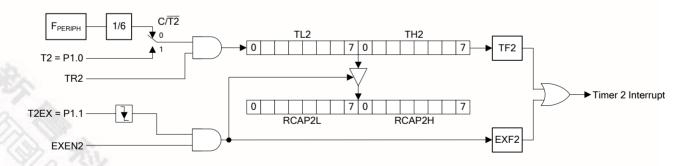

### 10.2.1 Capture Mode

The capture mode is enabled by setting the CP/RL2 bit in the T2CON register to 1. In the capture mode, Timer/Counter 2 serves as a 16 bit up counter. When the counter rolls over from FFFFH to 0000H, the TF2 bit is set, which will generate an Timer 2 interrupt request. If the EXEN2 bit is set, then a negative transition of T2EX pin (alternative function of P1.1) will cause the value in the TL2 and TH2 register to be captured by the RCAP2L and RCAP2H registers. The TH2 and TL2 keeps on counting while this capture event occurs. This capture action also causes the EXF2 (T2CON.6) bit set, which will also generate an Timer 2 interrupt. If Timer 2 interrupt enabled, both TF2 and EXF2 flags will generate interrupt vectoring to the same location. The user should check which one triggers the Timer 2 interrupt in the interrupt service routine.

Figure 10–5. Timer/Counter 2 in Capture Mode

### 10.2.2 Auto-reload Mode

The auto-reload mode is enabled by clearing the CP/RL2 bit in the T2CON register. In this mode, Timer/Counter 2 is a 16 bit up counter. When the counter rolls over from FFFFH, TF2 (T2CON.7) is set as 1 and a reload is generated that causes the contents of the RCAP2L and RCAP2H registers to be reloaded into the TL2 and TH2 registers respectively. If the EXEN2 bit is set, then a negative transition on T2EX pin will also cause a reload. This action also sets the EXF2 bit in T2CON.

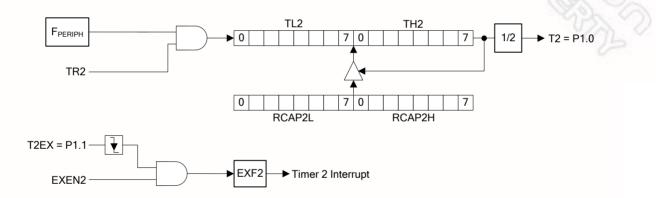

## 10.2.4 Clock-out Mode

Timer 2 is equipped with a clock-out feature, which outputs a 50% duty cycle clock on P1.0. It can be invoked as a programmable clock generator. To configure Timer 2 with clock-out mode, software must initiate it by setting bit T2OE (TMOD.1) = 1, C/T2 = 0 and CP/RL2 = 0. Setting bit TR2 will start the clock output. This mode is similar to the baud rate generator mode which does not generate an interrupt while Timer 2 overflow. Similar with the baud rate generator mode, T2EX can also be configured as a simple external interrupt.

The clock-out frequency follows the equation  $\frac{F_{OSC}}{2 \times 2^{EN6T} \times (65536 - (RCAP2H, RCAP2L))}.$

In this formula, EN6T is bit 6 of CONFIG3. While EN6T = 0, the clock system runs under 6T mode and the clock-out frequency will be double of that in 12T mode. (RCAP2H,RCAP2L) in the formula means  $256 \times RCAP2H + RCAP2L$ .

### Figure 10–8. Timer/Counter 2 in Clock-out Mode

| WPS2 | WPS1 | WPS0 | Clock Divider<br>Scale | Typical Watchdog Time-out<br>Interval (F <sub>ILRC</sub> ~= 10kHz) |

|------|------|------|------------------------|--------------------------------------------------------------------|

| 0    | 0    | 0    | 1/1                    | 6.40ms                                                             |

| 0    | 0    | 1    | 1/2                    | 12.80ms                                                            |

| 0    | 1    | 0    | 1/8                    | 51.20ms                                                            |

| 0    | 1    | 1    | 1/16                   | 102.40ms                                                           |

| 1    | 0    | 0    | 1/32                   | 204.80ms                                                           |

| 1    | 0    | 1    | 1/64                   | 409.60ms                                                           |

| 1    | 1    | 0    | 1/128                  | 819.20ms                                                           |

| 1    | 1    | 1    | 1/256                  | 1.638s                                                             |

Table 11–1. Watchdog Timer-Out Interval under different pre-scalars

## **11.2 Applications of Watchdog Timer**

The main application of the Watchdog Timer is for the system monitor. This is important in real-time control applications. In case of some power glitches or electro-magnetic interference, the processor may begin to execute erroneous codes and operate in an unpredictable state. If this is left unchecked the entire system may crash. Using the Watchdog Timer during software development will require the user to select ideal watchdog reset locations for inserting instructions to reset the Watchdog Timer. By inserting the instruction setting WDCLR, it will allow the code to run without any Watchdog Timer reset. However If any erroneous code executes by any power of other interference, the instructions to clear the Watchdog Timer counter will not be executed at the required instants. Thus the Watchdog Timer reset will occur to reset the system start from an erroneously executing condition. The user should remember that WDCON requires a timed access writing.

| Bit | Name | Description                                                                                                                                               |

|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5   | PDTF | <b>Power Down waking-up timer Interrupt Flag.</b><br>This bit will be set via hardware when PDT counter overflows. This bit must be cleared via software. |

| 4:3 | -    | Reserved.                                                                                                                                                 |

| 2   | PPS2 | Power Down waking-up timer clock pre-scalar select.                                                                                                       |

| 1   | PPS1 | These bits determine the scale of the clock divider for PDT counter. The scale is from 1/1 through 1/1024. See Table 12–1.                                |

| 0   | PPS0 |                                                                                                                                                           |

The Power Down waking-up time-out interval is determined by the formula  $\frac{1}{F_{LOSC} \times clock \, dividers calar} \times 64$

where F<sub>ILRC</sub> is the frequency of internal 10kHz RC. The following table shows an example of the Power Down waking-up time-out interval under different pre-scalars.

| PPS2 | PPS1 | PPS0 | Clock Divider<br>Scale | Typical Power Down Waking-up<br>Time-out Interval (F <sub>ILRC</sub> ~= 10kHz) |

|------|------|------|------------------------|--------------------------------------------------------------------------------|

| 0    | 0    | 0    | 1/1                    | 6.40ms                                                                         |

| 0    | 0    | 1    | 1/4                    | 25.60ms                                                                        |

| 0    | 1    | 0    | 1/8                    | 51.20ms                                                                        |

| 0    | 1    | 1    | 1/32                   | 204.80ms                                                                       |

| 1    | 0    | 0    | 1/64                   | 409.60ms                                                                       |

| 1    | 0    | 1    | 1/256                  | 1.638s                                                                         |

| 1    | 1    | 0    | 1/512                  | 3.277s                                                                         |

| 1    | 1    | 1    | 1/1024                 | 6.554s                                                                         |

Table 12–1. Power Down Waking-up Timer-Out Interval under different pre-scalars

## 12.2 Applications of Power Down Waking-up Timer

The main application of the Power Down waking-up timer is a simple timer. The PDTF flag will be set while the Power Down waking-up timer completes the selected time interval. The software polls the PDTF flag to detect a time-out and the PDCLR allows software to restart the timer. The Power Down waking-up timer can also be used as a very long timer. Every time the time-out occurs, an interrupt will occur if the individual interrupt EPDT (EIE.1) and global interrupt enable EA is set.

In some application of low power consumption, the CPU usually stays in Idle mode when nothing needs to be served to save power consumption. After a while the CPU will be woken up to check if anything needs to be served at an interval of programmed period implemented by Timer 0, 1 or 2. However, the current consumption

of Idle mode still keeps at a "mA" level. To further reducing the current consumption to "µA" level, the CPU should stay in Power Down mode when nothing needs to be served, and has the ability of waking up at a programmable interval. N78E059A/N78E055A is equipped with this useful function. It provides a very low power internal RC 10kHz. Along with the low power consumption application, the Power Down Waking-up timer needs to count under Idle and Power Down mode and wake CPU up from Idle or Power Down mode. The demo code to accomplish this feature is shown below.

The demo code of Power Down waking-up timer waking up CPU from Power Down.

ORG 0000H LJMP START 004BH ORG PDT ISR LJMP ORG 0100H PDT ISR: PDCON, #0100000B ;Clear Power Down Waking-up timer counter ORL ANL PDCON,#11011111B ;Clear Power Down Waking-up timer interrupt flag RETI START: ORL PDCON, #00000111B ;Choose interval length ORL EIE,#00000010B ;Enable Power Down Waking-up timer interrupt SETB ΕA ORL PDCON, #1000000B ;Enable Power Down Waking-up timer to run ;Enter into Power Down mode ;\*\*\* LOOP: ORL PCON, #02H LJMP LOOP

high, the SPI is forced into idle state. If the  $\overline{SS}$  is force to high at the middle of transmission, the transmission will be aborted and the rest bits of the receiving shifter buffer will be high and goes into idle state.

In Slave mode, data flows from the Master to the Slave on MOSI pin and flows from the Slave to the Master on MISO pin. The data enters the shift register under the control of the SPCLK from the Master device. After one byte is received in the shift register, it is immediately moved into the read data buffer and the SPIF bit is set. A read of the SPDR is actually a read of the read data buffer. To prevent an overrun and the loss of the byte that caused by the overrun, the Slave must read SPDR out and the first SPIF must be cleared before a second transfer of data from the Master device comes in the read data buffer.

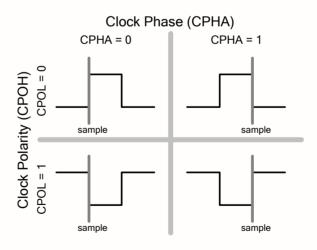

### 14.5 Clock Formats and Data Transfer

To accommodate a wide variety of synchronous serial peripherals, the SPI has a clock polarity bit CPOL (SPCR.3) and a clock phase bit CPHA (SPCR.2). Figure 14–4. SPI Clock Formats shows that CPOL and CPHA compose four different clock formats. The CPOL bit denotes the SPCLK line level in SPI idle state. The CPHA bit defines the edge on which the MOSI and MISO lines are sampled. The CPOL and CPHA should be identical for the Master and Slave devices on the same system. To Communicate in different data formats with one another will result undetermined result.

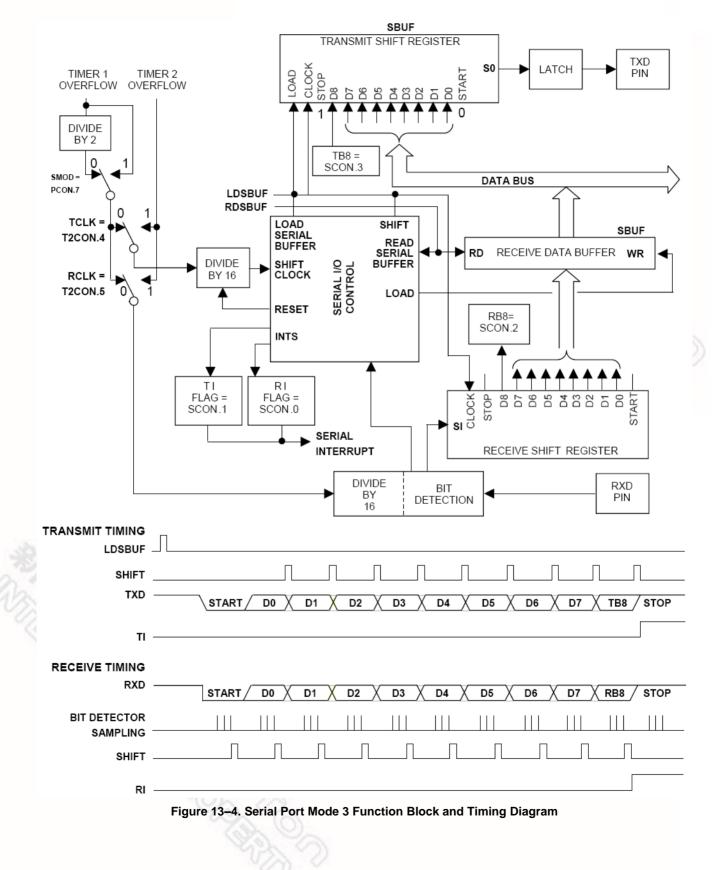

Figure 14–4. SPI Clock Formats

In SPI, a Master device always initiates the transfer. If SPI is selected as Master mode (MSTR = 1) and enabled (SPIEN = 1), writing to the SPI data register (SPDR) by the Master device starts the SPI clock and data transfer. After shifting one byte out and receiving one byte in, the SPI clock stops and SPIF (SPSR.7) in both Master and Slave are set. If SPI interrupt enable bit ESPI (EIE.0) is set 1 and global interrupt is enabled (EA = 1), the interrupt service routine (ISR) of SPI will be executed.

## **15. PULSE WIDTH MODULATOR (PWM)**

N78E059A/N78E055A provides five pulse width modulated (PWM) output channels to generate pulses of programmable length and interval. Five PWM channels, PWM0~4, shares the same pins with P1.3~P1.7. The PWM period is defined by an 8-bit pre-scalar PWMP, which supplies the clock of the PWM counter. The prescalar is common for all PWM channels. The duty of each PWM channel is determined by the value of five registers, PWM0, PWM1, PWM2, PWM3, and PWM4. If the contents of these registers are equal to or less than the 8-bit counter value, the output will be 0. Else the output will be 1 if these registers value are larger than the counter. Set PWMxEN (in PWMCON0[0,1,4,5] and PWMCON1.0) will enable to run or disable to stop each PWM channel respectively. In addition, the PWMxOM (in PWMCON0[2,3,6,7] and PWMCON1.2) must set 1 to output the internal PWM signal to port pins. Without setting PWMxOM, the pins which share with alternative PWM function will be normal general purpose I/O of P1.3~P1.7 even though PWM is enabled. The following registers relate to PWM function.

### **PWMCON0 – PWM Control 0**

|        | 11.743 77 |        |        |        |        |        | 1 ( ( ) ) ( |

|--------|-----------|--------|--------|--------|--------|--------|-------------|

| 7      | 6         | 5      | 4      | 3      | 2      | 1      | 0           |

| PWM3OE | PWM2OE    | PWM3EN | PWM2EN | PWM10E | PWM0OE | PWM1EN | PWM0EN      |

| r/w    | r/w       | r/w    | r/w    | r/w    | r/w    | r/w    | r/w         |

|        |           |        |        |        |        |        |             |

reset value: 0000 0000b

| Bit | Name   | Description                                                                                                            |

|-----|--------|------------------------------------------------------------------------------------------------------------------------|

| 7   | PWM3OE | <b>PWM3 output enable.</b><br>0 = P1.6 serves as general purpose I/O.<br>1 = P1.6 serves as output pin of PWM3 signal. |

| 6   | PWM2OE | <b>PWM2 output enable.</b><br>0 = P1.5 serves as general purpose I/O.<br>1 = P1.5 serves as output pin of PWM2 signal. |

| 5   | PWM3EN | <ul> <li>PWM3 enable.</li> <li>0 = PWM3 is disabled and stops.</li> <li>1 = PWM3 is enabled and runs.</li> </ul>       |

| 4   | PWM2EN | <ul> <li>PWM2 enable.</li> <li>0 = PWM2 is disabled and stops.</li> <li>1 = PWM2 is enabled and runs.</li> </ul>       |

| °G) | PWM1OE | <b>PWM1 output enable.</b><br>0 = P1.4 serves as general purpose I/O.<br>1 = P1.4 serves as output pin of PWM1 signal. |

| 2   | PWM0OE | <b>PWM0 output enable.</b><br>0 = P1.3 serves as general purpose I/O.<br>1 = P1.3 serves as output pin of PWM0 signal. |

| 1   | PWM1EN | <ul> <li>PWM1 enable.</li> <li>0 = PWM1 is disabled and stops.</li> <li>1 = PWM1 is enabled and runs.</li> </ul>       |

## PWM1 – PWM1 Duty

|                 |                                                                                            | 6                       | 5                                                                                          | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3                                                  | 2             | 1                | 0        |

|-----------------|--------------------------------------------------------------------------------------------|-------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|---------------|------------------|----------|

|                 |                                                                                            |                         |                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 11[7:0]                                            |               |                  |          |

| Addre           | ess: DBH                                                                                   |                         |                                                                                            | r                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | /w                                                 |               | reactivalue      |          |

| Addre           | 355. DDN                                                                                   |                         |                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                    |               | reset value      | . 0000 0 |

|                 | Bit                                                                                        | Name                    |                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Descrip                                            | tion          |                  |          |

|                 | 7:0                                                                                        | PWM1[7:0]               | PWM1 duty<br>This byte co                                                                  | ntrols the duty                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | of the PWM1 o                                      | utput.        | 1                |          |

| PWM             | 2 – PWM2                                                                                   |                         |                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                    | "UN           | 0                |          |

|                 | 7                                                                                          | 6                       | 5                                                                                          | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3                                                  | 2             | 1                | 0        |

|                 |                                                                                            |                         |                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 12[7:0]<br>/w                                      | - 4           | Sal L            | ~        |

| Addre           | ess: DDH                                                                                   |                         |                                                                                            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | / vv                                               |               | reset value      | · 0000 0 |

| huurt           |                                                                                            |                         |                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                    |               | reset value      | . 0000 0 |