Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Last Time Buy                                                                          |

|----------------------------|----------------------------------------------------------------------------------------|

| Core Processor             | 8051                                                                                   |

| Core Size                  | 8-Bit                                                                                  |

| Speed                      | 40MHz                                                                                  |

| Connectivity               | EBI/EMI, SPI, UART/USART                                                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                             |

| Number of I/O              | 32                                                                                     |

| Program Memory Size        | 32KB (32K x 8)                                                                         |

| Program Memory Type        | FLASH                                                                                  |

| EEPROM Size                | -                                                                                      |

| RAM Size                   | 1.25К х 8                                                                              |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 5.5V                                                                            |

| Data Converters            | -                                                                                      |

| Oscillator Type            | Internal                                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                      |

| Mounting Type              | Through Hole                                                                           |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                               |

| Supplier Device Package    | -                                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/nuvoton-technology-corporation-america/n78e059adg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

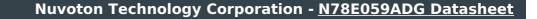

### 5.2 External Program Memory

N78E059A/N78E055A is a 16-bit address-width CPU. It can address 64k-byte program code. Besides the internal Program Memory, the external additional Program Memory is also can be used. The external program addressing will be executed under cases below,

1. The PC (Program Counter) value is beyond the boundary size address of APROM or LDROM while  $\overline{EA}$  pin is pulled high during power on. The CPU will continue to fetch the external Program Memory.

2. While  $\overline{EA}$  pin is pulled low during power on period, The CPU will run totally 64k-byte code externally.

While the external mode is running, the P0 and P2 will produce address and data signals to fetching external Program Memory. In this case, P0 and P2 cannot be general purpose I/O anymore. PSEN will also toggle out to strobe the external Program Memory. For the hardware circuit for external program execution, see Figure 5–2. Program Memory Interface.

For security  $\overline{EA}$  pin state will be locked after power on. The user cannot switch the program running internally or externally by  $\overline{EA}$  after power on. The other design for data security is MOVC lock enable (MOVCL, CONFIG0.2). While this bit is set 0, The external Program Memory code is inhibited to read internal APROM or LDROM contents through MOVC instruction.

### 5.3 Internal Data Memory

Figure 5–3 shows the internal and external Data Memory spaces available on N78E059A/N78E055A. Internal Data Memory can be divided into three blocks. They are the lower 128 bytes of RAM, the upper 128 bytes of RAM, and the 128 bytes of SFR space. Internal Data Memory addresses are always 8-bit wide, which implies an address space of only 256 bytes. Direct addressing higher than 7FH will access the special function registers (SFRs) space and indirect addressing higher than 7FH will access the upper 128 bytes of RAM. Although the SFR space and the upper 128 bytes of RAM share the same logic address, 80H through FFH, actually they are physically separate entities. Direct addressing to distinguish with the higher 128 bytes of RAM can only access these SFRs. Sixteen addresses in SFR space are both byte and bit-addressable. The bit-addressable SFRs are those whose addresses end in 0H or 8H.

The lower 128 bytes of internal RAM are present in all 8051 devices. The lowest 32 bytes are grouped into 4 banks of 8 registers. Program instructions call these registers as R0 through R7. Two bits RS0 and RS1 in the Program Status Word (PSW[3:4]) select which Register Bank is used. This benefits more efficiency of code space, since register instructions are shorter than instructions that use direct addressing. The next 16 bytes above the Register Banks (byte-address 20H through 2FH) form a block of bit-addressable memory space (bitaddress 00H through 7FH). The 8051 instruction set includes a wide selection of single-bit instructions, and the 128 bits in this area can be directly addressed by these instructions. The bit addresses in this area are 00H through 7FH.

All bytes in the lower 128-byte space can be accessed by either direct or indirect addressing. Indirect addressing can only access the upper 128.

Another application implemented with the whole block of internal 256-byte RAM is for the stack. This area is selected by the Stack Pointer (SP), which stores the address of the top of the stack. Whenever a JMP, CALL or interrupt is invoked, the return address is placed on the stack. There is no restriction as to where the stack can begin in the RAM. By default however, the Stack Pointer contains 07H at reset. The user can then change this to any value desired. The SP will point to the last used value. Therefore, the SP will be incremented and then address saved onto the stack. Conversely, while popping from the stack the contents will be read first, , decre and then the SP is decreased.

#### Table 6–2. N78E059A/N78E055A SFR Descriptions and Reset Values

| Symbol                | Definition                             | Address    | MSB         |             |              |               |                    |              |             | LSB <sup>[1]</sup> | Reset                                            | Value              |

|-----------------------|----------------------------------------|------------|-------------|-------------|--------------|---------------|--------------------|--------------|-------------|--------------------|--------------------------------------------------|--------------------|

| SPDR                  | SPI data                               | F5H        |             |             |              | 100           |                    |              |             |                    | 0000                                             |                    |

| SPSR                  | SPI status                             | F4H        | SPIF        | WCOL        | SPIOVF       | MODF          | DISMODF            | -            | -           | -                  | 0000                                             | 000                |

| SPCR                  | SPI control                            | F3H        | SSOE        | SPIEN       | LSBFE        | MSTR          | CPOL               | CPHA         | SPR1        | SPR0               | 0000                                             |                    |

| B                     | B register                             | F0H        | (F7)        | (F6)        | (F5)         | (F4)          | (F3)               | (F2)         | (F1)        | (F0)               | 0000                                             |                    |

| ACC                   | Accumulator                            | E0H        | (E7)        | (E6)        | (E5)         | (E4)          | (E3)               | (E2)         | (E1)        | (E0)               | 0000                                             |                    |

| PWM3                  | PWM3 duty                              | DEH        | (= / )      | (20)        | (20)         | (= 1)         | (20)               | (==)         | (= !)       | (20)               | 0000                                             |                    |

| PWM2                  | PWM2 duty                              | DDH        | -           |             |              | 1             | 0 1                | 132          |             |                    | 0000                                             |                    |

|                       |                                        | DCH        | PW/M3OF     | PW/M2OF     | PW/M3EN      | PW/M2EN       | PWM10E             | PW/MOOF      | PWM1EN      | PW/MOEN            |                                                  |                    |

| PWM1                  | PWM1 duty                              | DBH        | TWINGOL     | TWIMEOL     | TWINGEN      |               | TWINTOL            | TWINOOL      | TVINILLI    | TWINGEN            | 0000                                             |                    |

| PWM0                  | PWM0 duty                              | DAH        |             |             |              |               |                    | 1            |             |                    | 0000                                             |                    |

| PWMP                  | PWM period                             | DAH<br>D9H |             |             |              |               | - MC               |              |             |                    | 0000                                             |                    |

|                       |                                        | Dau        | (DF)        | (DE)        | (DD)         | (DC)          | (DB)               |              | (D9)        | (D8)               | 0000                                             | 000                |

| P4                    | Port 4                                 | D8H        | (DF)        | (DE)        | (00)         | (DC)          | INT2               | (DA)<br>INT3 | (D9)        | (D0)               | 1111                                             | 11                 |

| PSW                   | Program status word                    | D0H        | (D7)<br>CY  | (D6)<br>AC  | (D5)<br>F0   | (D4)<br>RS1   | (D3)<br>RS0        | (D2)<br>OV   | (D1)<br>F1  | (D0)<br>P          | 0000                                             | 000                |

| PWM4                  | PWM4 duty                              | CFH        |             |             |              |               |                    |              | 2           | 1 ling             | 0000                                             | 00                 |

| PWMCON1               | PWM control 1                          | CEH        | -           | -           | -            | -             | -                  | PWM4OE       | 6.20        | PWM4EN             |                                                  |                    |

| TH2                   | Timer 2 high byte                      | CDH        |             |             |              |               | 1                  |              | 7.0         | 0. (6              | 0000                                             |                    |

| TL2                   | Timer 2 low byte                       | CCH        |             |             |              |               |                    |              | 11          |                    | 0000                                             |                    |

| RCAP2H                | Timer 2 reload/capture<br>high byte    | СВН        |             |             |              |               |                    |              | 1           | 20                 | 0000                                             |                    |

| RCAP2L                | Timer 2 reload/capture<br>low byte     | CAH        |             |             |              |               |                    |              |             | - 73               | 0000                                             | 00                 |

| T2MOD                 | Timer 2 mode                           | C9H        | -           | -           | -            | -             | -                  | -            | T2OE        |                    | 0000                                             | 000                |

|                       |                                        | 2.5.1.     | (CF)        | (CE)        | (CD)         | (CC)          | (CB)               | (CA)         | (C9)        | (C8)               |                                                  |                    |

| T2CON                 | Timer 2 control                        | C8H        | TF2         | EXF2        | (CD)<br>RCLK | TCLK          | EXEN2              | TR2          | C/T2        | CP/RL2             | 0000                                             |                    |

| ТА                    | Timed access protection                | C7H        |             |             |              |               |                    |              |             |                    | 0000                                             | 000                |

| XICON                 | External interrupt control             | СОН        | (C7)<br>PX3 | (C6)<br>EX3 | (C4)<br>IE3  | (C4)<br>IT3   | (C3)<br>PX2        | (C2)<br>EX2  | (C1)<br>IE2 | (C0)<br>1IT2       | 0000                                             | 000                |

| EIE                   | Extensive interrupt ena-<br>ble        | BDH        | -           | -           | -            | -             | -                  | EBOD         | EPDT        | ESPI               | 0000                                             | 000                |

| EIP                   | Extensive interrupt priori-<br>ty      | BCH        | -           | -           | -            | -             | -                  | PBOV         | PPDT        | PSPI               | 0000                                             | 000                |

| EIPH                  | Extensive interrupt priori-<br>ty high | BBH        | -           | -           | -            | -             | -                  | PBODH        | PPDTH       | PSPIH              | 0000                                             |                    |

| IPH                   | Interrupt priority high                | BAH        | PX3H        | PX2H        | PT2H         | PSH           | PT1H               | PX1H         | PT0H        | PX0H               | 0000                                             | 000                |

| IP                    | Interrupt priority                     | B8H        | (BF)<br>-   | (BE)<br>-   | (BD)<br>PT2  | (BC)<br>PS    | (BB)<br>PT1        | (BA)<br>PX1  | (B9)<br>PT0 | (B8)<br>PX0        | 0000                                             | 00(                |

| P3                    | Port 3                                 | B0H        | (B7)        | (B6)        | (B5)         | (B4)          | (B3)               | (B2)         | (B1)        | (B0)               | 1111                                             | 11                 |

|                       |                                        |            | RD          | WR          | T1           | Т0            | INT1               | INT0         | TXD         | RXD                |                                                  |                    |

| ISPCN                 | ISP flash control                      | AFH        | ISPA17      | ISPA16      | FOEN         | FCEN          | FCTRL3             | FCTRL2       | FCTRL1      | FCTRL0             | 0000                                             | 00                 |

| ISPFD                 | ISP flash data                         | AEH        |             |             |              |               |                    |              |             |                    | 0000                                             | 00                 |

| PMC <sup>[3]</sup>    | Power monitoring control               | ACH        | BODEN       | -           | -            | BORST         | BOF <sup>[4]</sup> | LPBOD        | -           | BOS <sup>[5]</sup> | Power<br>XXXX<br>Brown<br>XXXX<br>Others<br>XXXX | X0<br>-out,<br>10  |

| PDCON                 | Power Down waking-up<br>timer control  | ABH        | PDTEN       | PDTCK       | PDTF         | -             | -                  | PPS2         | PPS1        | PPS0               | 0000                                             |                    |

| WDCON <sup>[3]</sup>  | Watchdog Timer control                 | ААН        | WDTEN       | WDCLR       | -            | WIDPD         | WDTRF              | WPS2         | WPS1        | WPS0               | Power<br>X000<br>Watch<br>X00U<br>Others<br>X00U | 000<br>dog,<br>1UU |

| IE                    | Interrupt enable                       | A8H        | (AF)<br>EA  | (AE)<br>-   | (AD)<br>ET2  | (AC)<br>ES    | (AB)<br>ET1        | (AA)<br>EX1  | (A9)<br>ET0 | (A8)<br>EX0        | 0000                                             |                    |

| ISPAH                 | ISP address high byte                  | A7H        | Sec. 1      |             |              |               |                    |              |             |                    | 0000                                             |                    |

| ISPAL                 | ISP address low byte                   | A6H        | No          |             |              |               |                    |              |             |                    | 0000                                             | 00                 |

| ISPTRG <sup>[3]</sup> | ISP trigger                            | A4H        | 2.          | -           | -            | -             | -                  | -            | -           | ISPGO              | 0000                                             | 00                 |

| XRAMAH                | Auxiliary RAM address                  | A1H        | 46          | s           | -            | -             | -                  | -            |             | XRAMAH.0           | 1                                                |                    |

|                       |                                        | ~~~        | (A7)        | (AG)        | (A5)         | $(\Lambda A)$ | (A3)               | (A2)         | (A1)        | (A0)               |                                                  |                    |

| P2                    | Port 2                                 | A0H        | (A7)<br>A15 | (A6)<br>A14 | (A5)<br>A13  | (A4)<br>A12   | (43)               | (A2)<br>A10  | (A1)        | (AU)               | 1111                                             | 1 1                |

#### **DPH – Data Pointer High Byte**

| 7            | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|--------------|---|---|---|---|---|---|---|--|--|--|

| DPH[7:0]     |   |   |   |   |   |   |   |  |  |  |

| r/w          |   |   |   |   |   |   |   |  |  |  |

| Address: 83H |   |   |   |   |   |   |   |  |  |  |

| Bit | Name     | Description                                                                                                                                                                                                      |

|-----|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | DPH[7:0] | <b>Data pointer high byte.</b><br>This is the high byte of the standard 8051 16-bit data pointer. DPH combined with DPL serve as a 16-bit data pointer DPTR to address non-scratch-pad memory or Program Memory. |

#### PSW – Program Status Word (bit-addressable)

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0    |

|-----|-----|-----|-----|-----|-----|-----|------|

| CY  | AC  | F0  | RS1 | RS0 | OV  | F1  | P    |

| r/w | Dec. |

Address: D0H

reset value: 0000 0000b

| Bit | Name                                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

|-----|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 7   | CY                                       | <b>Carry flag.</b><br>For a adding or subtracting operation, CY will be set when the previous operation resulted in a carry-out from or a borrow-in to the Most Significant bit, otherwise cleared.<br>If the previous operation is MUL or DIV, CY is always 0.<br>CY is affected by DA A instruction which indicates that if the original BCD sum is greater than 100.<br>For a CJNE branch, CY will be set if the first unsigned integer value is less than the second one. Otherwise, CY will be cleared. |  |  |  |  |  |  |  |

| 6   | AC                                       | <b>Auxiliary carry.</b><br>Set when the previous operation resulted in a carry-out from or a borrow-in to the 4 <sup>th</sup> bit of the low order nibble, otherwise cleared.                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| 5   | F0                                       | Jser flag 0.<br>The general purpose flag that can be set or cleared by the user.                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| 4   | RS1                                      | Register Bank selecting bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| 3   | RS0                                      | These two bits select one of four banks in which R0~R7 locate.<br><u>RS1 RS0 Register Bank RAM Address</u>                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

|     | 1 (1) (1) (1) (1) (1) (1) (1) (1) (1) (1 | 0 0 0 00-07H<br>0 1 1 08-0FH<br>1 0 2 10-17H<br>1 1 3 18-1FH                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

|     |                                          | Publication Release Date: March 11, 20<br>- 26 - Revision: V                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| WPS2 | WPS1 | WPS0 | Clock Divider<br>Scale | Typical Watchdog Time-out<br>Interval (F <sub>ILRC</sub> ~= 10kHz) |

|------|------|------|------------------------|--------------------------------------------------------------------|

| 0    | 0    | 0    | 1/1                    | 6.40ms                                                             |

| 0    | 0    | 1    | 1/2                    | 12.80ms                                                            |

| 0    | 1    | 0    | 1/8                    | 51.20ms                                                            |

| 0    | 1    | 1    | 1/16                   | 102.40ms                                                           |

| 1    | 0    | 0    | 1/32                   | 204.80ms                                                           |

| 1    | 0    | 1    | 1/64                   | 409.60ms                                                           |

| 1    | 1    | 0    | 1/128                  | 819.20ms                                                           |

| 1    | 1    | 1    | 1/256                  | 1.638s                                                             |

Table 11–1. Watchdog Timer-Out Interval under different pre-scalars

### **11.2 Applications of Watchdog Timer**

The main application of the Watchdog Timer is for the system monitor. This is important in real-time control applications. In case of some power glitches or electro-magnetic interference, the processor may begin to execute erroneous codes and operate in an unpredictable state. If this is left unchecked the entire system may crash. Using the Watchdog Timer during software development will require the user to select ideal watchdog reset locations for inserting instructions to reset the Watchdog Timer. By inserting the instruction setting WDCLR, it will allow the code to run without any Watchdog Timer reset. However If any erroneous code executes by any power of other interference, the instructions to clear the Watchdog Timer counter will not be executed at the required instants. Thus the Watchdog Timer reset will occur to reset the system start from an erroneously executing condition. The user should remember that WDCON requires a timed access writing.

# 13. SERIAL PORT

N78E059A/N78E055A includes one enhanced full duplex serial port. The serial port supports three modes of full duplex UART (Universal Asynchronous Receiver and Transmitter) in Mode 1, 2, and 3. This means it can transmit and receive simultaneously. The serial port is also receive-buffered, meaning it can commence reception of a second byte before a previously received byte has been read from the register. The serial port receive and transmit registers are both accessed at SBUF. Writing to SBUF loads the transmit register, and reading SBUF accesses a physically separate receive register. There are four operation modes in serial port. In all four modes, transmission initiates by any instruction that uses SBUF as a destination register. Note that before serial port function works, the port latch bits of P3.0 and P3.1 (for RXT and TXD pins) have to be set to 1.

#### SCON – Serial Port Control (bit-addressable)

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0           |

|-----|-----|-----|-----|-----|-----|-----|-------------|

| SM0 | SM1 | SM2 | REN | TB8 | RB8 | T   | RI          |

| r/w         |

|     |     |     |     |     |     |     | 100 100 100 |

Address: 98H

reset value: 0000 0000b

| Bit | Name | Description                                                                                                                                                                                                                                                                                                                                                                              |

|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | SM0  | Serial port mode select.                                                                                                                                                                                                                                                                                                                                                                 |

| 6   | SM1  | See <u>Table 13–1. Serial Port Mode Description</u> for details.                                                                                                                                                                                                                                                                                                                         |

| 5   | SM2  | Multiprocessor communication mode enable.<br>The function of this bit is dependent on the serial port mode.                                                                                                                                                                                                                                                                              |

|     |      | <u>Mode 0:</u><br>This bit has no effect.                                                                                                                                                                                                                                                                                                                                                |

|     |      | Mode 1:This bit checks valid stop bit.0 = Reception is always valid no matter the logic level of stop bit.1 = Reception is ignored if the received stop bit is not logic 1.                                                                                                                                                                                                              |

|     |      | $\begin{array}{l} \underline{\text{Mode 2 or 3:}} \\ \hline \text{For multiprocessor communication.} \\ 0 = \text{Reception is always valid no matter the logic level of the 9^{th} bit.} \\ 1 = \text{Reception is ignored if the received 9}^{th} bit is not logic 1.} \end{array}$                                                                                                    |

| 4   | REN  | <ul> <li>Receive enable.</li> <li>0 = Disable serial port reception.</li> <li>1 = Enable serial port reception in Mode 1,2, and 3. In Mode 0, clearing and then setting REN initiates one-byte reception. After reception is complete, this bit will not be cleared via hardware. The user should clear and set REN again via software to triggering the next byte reception.</li> </ul> |

| 3   | TB8  | <b>9<sup>th</sup> transmit bit.</b><br>This bit defines the state of the 9 <sup>th</sup> transmission bit in serial port Mode 2 and 3. It is not used in Mode0 and 1.                                                                                                                                                                                                                    |

|     |      | Publication Release Date: March 11, 2<br>- 52 -                                                                                                                                                                                                                                                                                                                                          |

Transmission is initiated by any writing instructions to SBUF. Transmission takes place on TXD pin. First the start bit comes out, the 8-bit data and bit TB8 (SCON.3) follows to be shifted out and then ends with a stop bit. After the stop bit appears, TI will be set to indicate the transmission complete.

While REN is set, the reception is allowed at any time. A falling edge of a start bit on RXD will initiate the reception progress. Data will be sampled and shifted in at the selected baud rate. In the midst of the 9<sup>th</sup> bit, certain conditions must be met to load SBUF with the received data:

1. RI (SCON.0) = 0, and

2. Either SM2(SCON.5) = 0, or the received  $9^{th}$  bit = 1 while SM2 = 1.

If these conditions are met, then the SBUF will be loaded with the received data, the RB8(SCON.2) with TB8 bit and RI will be set. If these conditions fail, there will be no data loaded and RI will remain 0. After above receiving progress, the serial control will look forward another 1-0 transition on RXD pin in order to start next data reception.

### 13.4 Mode 3

Mode 3 has the same operation as Mode 2, except its baud rate clock source. As shown is Figure 13–4, Mode 3 uses Timer 1 or Timer 2 overflow as its baud rate clock.

| TH4 relead welve | Oscillator Frequency (MHz) |     |        |         |        |  |  |  |

|------------------|----------------------------|-----|--------|---------|--------|--|--|--|

| TH1 reload value | 11.0592 14.7456            |     | 18.432 | 22.1184 | 36.864 |  |  |  |

| Baud Rate        |                            |     |        |         |        |  |  |  |

| 9600             | FDh                        | FCh | FBh    | FAh     | F6h    |  |  |  |

| 4800             | FAh                        | F8h | F6h    | F4h     | ECh    |  |  |  |

| 2400             | F4h                        | F0h | ECh    | E8h     | D8h    |  |  |  |

| 1200             | E8h                        | E0h | D8h    | D0h     | B0h    |  |  |  |

| 300              | A0h                        | 80h | 60h    | 40h     |        |  |  |  |

#### Table 13–4. Timer 2 Generated Commonly Used Baud Rates

| RCAP2H, RCAP2L | Oscillator Frequency (MHz) |          |          |          |          |  |  |  |

|----------------|----------------------------|----------|----------|----------|----------|--|--|--|

| reload value   | 11.0592                    | 14.7456  | 18.432   | 22.1184  | 36.864   |  |  |  |

| Baud Rate      |                            |          |          |          |          |  |  |  |

| 115200         | FFh, FDh                   | FFh, FCh | FFh, FBh | FFh, FAh | FFh, F6h |  |  |  |

| 57600          | FFh, FAh                   | FFh, F8h | FFh, F6h | FFh, F4h | FFh, ECh |  |  |  |

| 38400          | FFh, F7h                   | FFh, F4h | FFh, F1h | FFh, EEh | FFh, E2h |  |  |  |

| 19200          | FFh, EEh                   | FFh, E8h | FFh, E2h | FFh, DCh | FFh, C4h |  |  |  |

| 9600           | FFh, DCh                   | FFh, D0h | FFh, C4h | FFh, B8h | FFh, 88h |  |  |  |

| 4800           | FFh, B8h                   | FFh, A0h | FFh, 88h | FFh, 70h | FFh, 10h |  |  |  |

| 2400           | FFh, 70h                   | FFh, 40h | FFh, 10h | FEh, E0h | FEh, 20h |  |  |  |

| 1200           | FEh, E0h                   | FEh, 80h | FEh, 20h | FDh, C0h | FCh, 40h |  |  |  |

| 300            | FBh, 80h                   | FAh, 00h | F8h, 80h | F7h, 00h | F1h, 00h |  |  |  |

### **13.6 Multiprocessor Communication**

N78E059A/N78E055A multiprocessor communication feature of UART lets a Master device send a multiple frame serial message to a Slave device in a multi-slave configuration. It does this without interrupting other slave devices that may be on the same serial line. This feature can be used only in UART mode 2 or 3 mode. After 9 data bits are received. The 9<sup>th</sup> bit value is written to RB8 (SCON.2). The user can enable this function by setting SM2 (SCON.5) as a logic 1 so that when the stop bit is received, the serial interrupt will be generated only if RB8 is 1. When the SM2 bit is 1, serial data frames that are received with the 9<sup>th</sup> bit as 0 do not generate an interrupt. In this case, the 9<sup>th</sup> bit simply separates the address from the serial data.

When the Master device wants to transmit a block of data to one of several slaves on a serial line, it first sends out an address byte to identify the target slave. Note that in this case, an address byte differs from a data byte: In an address byte, the 9<sup>th</sup> bit is 1 and in a data byte, it is 0. The address byte interrupts all slaves so that each slave can examine the received byte and see if it is being addressed. The addressed slave then clears its SM2

# nuvoton

Most of interrupt flags must be cleared by writing it as a logic 0 via software. Without clearing the flag, the ISR of corresponding interrupt source will execute again and again non-stopped.

## **17.1 Priority Level Structure**

There are four priority levels for the interrupts, highest, high, low, and lowest. The interrupt sources can be individually set to one of four priority levels by setting their own priority bits. <u>Table 17–2</u> lists four priority setting. Naturally, a low priority interrupt can itself be interrupted by a high priority interrupt, but not by another same level interrupt or lower level. A highest priority can't be interrupted by any other interrupt source. In addition, there exists a pre-defined hierarchy among the interrupts themselves. This hierarchy comes into play when the interrupt controller has to resolve simultaneous requests having the same priority level. This hierarchy is defined as shown on <u>Table 17–3</u>. It also summarizes the interrupt sources, flag bits, vector addresses, enable bits, priority bits, natural priority and the permission to wake up the CPU from Power Down mode. For details of waking CPU up from Power Down mode, please see <u>Section 19.2 "Power Down Mode" on page 100</u>.

#### Table 17–2. Interrupt Priority Level Setting

| Interrupt Priori | Interrupt Priority Level |                   |

|------------------|--------------------------|-------------------|

| IPH / EIPH       | IP / EIP / XICON[7,3]    |                   |

| 0                | 0                        | Level 0 (lowest)  |

| 0                | 1                        | Level 1           |

| 1                | 0                        | Level 2           |

| 1                | 1                        | Level 3 (highest) |

#### Table 17–3. Characteristics of Each Interrupt Source

| Source                                   | Vector<br>Address | Flag                      | Enable Bit | Natural<br>Priority | Priority Control Bits | Power Down<br>Waking up |

|------------------------------------------|-------------------|---------------------------|------------|---------------------|-----------------------|-------------------------|

| External interrupt 0                     | 0003H             | IE0 <sup>[1]</sup>        | EX0        | 1                   | PX0, PX0H             | Yes                     |

| Timer 0 overflow                         | 000BH             | TF0 <sup>[2]</sup>        | ET0        | 2                   | PT0, PT0H             | No                      |

| External interrupt 1                     | 0013H             | IE1 <sup>[1]</sup>        | EX1        | 3                   | PX1, PX1H             | Yes                     |

| Timer 1 overflow                         | 001BH             | TF1 <sup>[2]</sup>        | ET1        | 4                   | PT1, PT1H             | No                      |

| Serial port (UART)                       | 0023H             | RI + TI                   | ES         | 5                   | PS, PSH               | No                      |

| Timer 2 overflow / cap-<br>ture / reload | 002BH             | TF2 <sup>[2]</sup> + EXF2 | ET2        | 6                   | PT2, PT2H             | No                      |

| External interrupt 2                     | 0033H             | IE2 <sup>[1]</sup>        | EX2        | 7                   | PX2, PX2H             | Yes                     |

| External interrupt 3                     | 003BH             | IE3 <sup>[1]</sup>        | EX3        | 8                   | РХЗ, РХЗН             | Yes                     |

## **18. IN SYSTEM PROGRAMMING (ISP)**

The internal Program Memory and on-chip Data Flash support both hardware programming and in system programming (ISP). Hardware programming mode uses gang-writers to reduce programming costs and time to market while the products enter into the mass production state. However, if the product is just under development or the end product needs firmware updating in the hand of an end user, the hardware programming mode will make repeated programming difficult and inconvenient. ISP method makes it easy and possible. N78E059A/N78E055A supports ISP mode allowing a device to be reprogrammed under software control. Furthermore, the capability to update the application firmware makes wide range of applications possible.

ISP is performed without removing the microcontroller from the system. The most common method to perform ISP is via UART along with the firmware in LDROM. General speaking, PC transfers the new APROM code through serial port. Then LDROM firmware receives it and re-programs into APROM through ISP commands. Nuvoton provides ISP firmware, USB ISP writer and PC application program for N78E059A/N78E055A. It makes users quite easy perform ISP through Nuvoton standard ISP tool. Please explore Nuvoton 8-bit Micro-controller website: Nuvoton 80C51 Microcontroller Development Tool.

### **18.1 ISP Procedure**

Unlike RAM's real-time operation, to update flash data often takes long time. Furthermore, it is a quite complex timing procedure to erase, program, or read flash data. Fortunately, N78E059A/N78E055A carried out the flash operation with convenient mechanism to help the user update the flash content. After ISP enabled by setting ISPEN (CHPCON.0 with TA protected), the user can easily fill the 16-bit target address in ISPAH and ISPAL, data in ISPFD and command in ISPCN. Then the ISP is ready to begin by setting a triggering bit ISPGO (ISPTRG.0). Note that ISPTRG is also TA protected. At this moment, the CPU holds the Program Counter and the built-in ISP automation takes over to control the internal charge-pump for high voltage and the detail signal timing. After ISP action completed, the Program Counter continues to run the following instructions. The ISPGO bit will be automatically cleared. The user may repeat steps above for next ISP action if necessary. Through this progress, the user can easily erase, program, and verify the embedded flash by just taking care of the pure software.

The following registers relate to ISP processing.

### CHPCON – Chip Control (TA protected)

| 7            | 6    | 5               | 4            | 3           | 2            | 1              | 0            |

|--------------|------|-----------------|--------------|-------------|--------------|----------------|--------------|

| SWRST        | ISPF | LDUEN           | XRAMEN       | 7EA         | -            | BS             | ISPEN        |

| w            | r/w  | r/w             | r/w          | n           | - 0          | r/w            | r/w          |

| Address: 9FH | rese | et value: see T | able 6-2 N78 | RE0594/N78E | 155A SER Des | scriptions and | Reset Values |

Address: 9FH

<u>Descriptions and Reset Values</u> -2. IN/O :039A/11/00

| Bit | Name  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6   | ISPF  | <ul> <li>ISP fault flag.</li> <li>The hardware will set this bit when any of the following condition is met: <ol> <li>The accessing area is illegal, such as,</li> <li>Erasing or programming APROM itself when APROM code runs.</li> <li>Erasing or programming LDROM when APROM code runs but LDUEN is 0.</li> <li>Erasing or programming, or reading CONFIG bytes when APROM code runs.</li> <li>Erasing or programming LDROM itself when LDROM code runs.</li> <li>Erasing or programming LDROM itself when LDROM code runs.</li> </ol> </li> <li>Erasing or programming LDROM itself when LDROM code runs.</li> <li>Erasing or programming LDROM itself when LDROM code runs.</li> <li>Erasing or programming LDROM itself when LDROM code runs.</li> <li>Erasing or programming runs from internal Program Memory into external one.</li> <li>This bit should be cleared via software.</li> </ul> |

| 5   | LDUEN | <ul> <li>Updating LDROM enable.</li> <li>0 = The LDROM is inhibited to be erased or programmed when APROM code runs. LDROM remains read-only.</li> <li>1 = The LDROM is allowed to be fully accessed when APROM code runs.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 0   | ISPEN | <ul> <li>ISP enable.</li> <li>0 = Enable ISP function.</li> <li>1 = Disable ISP function.</li> <li>To enable ISP function will start the internal 22.1184MHz RC oscillator for timing control. To clear ISPEN should always be the last instruction after ISP operation in order to stop internal RC for reducing power consumption.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

### **ISPCN – ISP Control**

| 7       | 6       | 5    | 4    | 3       | 2       | 1       | 0       |

|---------|---------|------|------|---------|---------|---------|---------|

| ISPA.17 | ISPA.16 | FOEN | FCEN | FCTRL.3 | FCTRL.2 | FCTRL.1 | FCTRL.0 |

| r/w     | r/w     | r/w  | r/w  | r/w     | r/w     | r/w     | r/w     |

Address: AFH

reset value: 0000 0000b

|         | Name      | Description                                                                                                                                        |

|---------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 ISF | PA[17:16] | ISP control.                                                                                                                                       |

| 5       | FOEN      | This byte is for ISP controlling command to decide ISP destinations and actions. For details, see <u>Table 18–1. ISP Modes and Command Codes</u> . |

| 4       | FCEN      |                                                                                                                                                    |

| 3:0 FC  | CTRL[3:0] |                                                                                                                                                    |

## **18.2 ISP Commands**

N78E059A/N78E055A provides a wide application to perform ISP to APROM, LDROM or on-chip Data Flash. The ISP action mode and the destination of the flash block are defined by ISP control register ISPCN.

| ISP Mode                           |                     | ISPC | N    | X          | ISPAH, ISPAL                                               |            |  |

|------------------------------------|---------------------|------|------|------------|------------------------------------------------------------|------------|--|

| ISP Mode                           | ISPA.17, ISPA.16    | FOEN | FCEN | FCTRL[3:0] | ISPA[15:0]                                                 | ISPFD[7:0] |  |

| Standby                            | X, X <sup>[1]</sup> | 1    | 1    | Х          | X                                                          | Х          |  |

| APROM and Data Flash<br>Page Erase | 0, 0                | 1    | 0    | 0010       | Address in <sup>[2]</sup>                                  | x          |  |

| LDROM Page Erase                   | 0, 1                | 1    | 0    | 0010       | Address in <sup>[2]</sup>                                  | X          |  |

| APROM and Data Flash<br>Program    | 0, 0                | 1    | 0    | 0001       | Address in                                                 | Data in    |  |

| LDROM Program                      | 0, 1                | 1    | 0    | 0001       | Address in                                                 | Data in    |  |

| APROM and Data Flash<br>Read       | 0, 0                | 0    | 0    | 0000       | Address in                                                 | Data out   |  |

| LDROM Read                         | 0, 1                | 0    | 0    | 0000       | Address in                                                 | Data out   |  |

| All CONFIG bytes Erase             | 1, 1                | 1    | 0    | 0010       | 00XXH                                                      | Х          |  |

| CONFIG Program                     | 1, 1                | 1    | 0    | 0001       | CONFIG0: 0000H Data ir<br>CONFIG2: 0002H<br>CONFIG3: 0003H |            |  |

| CONFIG Read                        | 1, 1                | 0    | 0    | 0000       | CONFIG0: 0000H<br>CONFIG2: 0002H<br>CONFIG3: 0003H         | Data out   |  |

| Table 18- | 1. ISP | Modes | and | Comma | and | Codes |

|-----------|--------|-------|-----|-------|-----|-------|

|           |        |       |     |       |     |       |

[1] "x" means "don't care".

[2] Each page is 256-byte size. Therefore, the address for Page Erase should be 0000H, 0100H, 0200H, 0300H, etc., which is incremented by one of high byte address.

## 18.3 User Guide of ISP

ISP facilitates the updating flash contents in a convenient way; however, the user should follow some restricted laws in order that the ISP operates correctly. Without noticing warnings will possible cause undetermined results even serious damages of devices. Be attention of these notices. Furthermore, this paragraph will also support useful suggestions during ISP procedures.

(1) If no more ISP operation needs, the user must clear ISPEN (CHPCON.0) to zero. It will make the system void to trigger ISP unaware. Furthermore, ISP requires internal 22.1184MHZ RC oscillator running. If the external clock source is chosen, disabling ISP will stop internal 22.1184MHz RC for saving power consumption. Note that a write to ISPEN is TA protected.

## **19. POWER SAVING MODES**

N78E059A/N78E055A has several features that help the user to control the power consumption of the device. The power saved features have the Power Down mode and the Idle mode of operation. For a stable current consumption, states of P0 pins should be taken care of. P0 should be set as 0 if floating or external pull-downs exist. Or P0 should be set as 1 if external pull-ups exist or internal pull-ups are enabled by P0UP (P0OR.0).

In system power saving modes, the Watchdog Timer should be specially taken care. The hardware will clear WDT counter automatically after entering into or being woken-up from Idle or Power Down mode. It prevents unconscious system reset.

#### **PCON – Power Control**

| 7            | 6    | 5              | 4            | 3   | 2   | 1             | 0            |

|--------------|------|----------------|--------------|-----|-----|---------------|--------------|

| SMOD         | -    | -              | POF          | GF1 | GF0 | PD            | IDL          |

| r/w          | -    | -              | r/w          | r/w | r/w | r/w           | r/w          |

| Address: 87H | roco | t value: see T | abla 6 2 N78 |     |     | criptions and | Rosot Values |

| Address: 87H | reset value: see | Table 6–2. N78E059A/N78E055A SFR Descri | ptions and Reset Values |

|--------------|------------------|-----------------------------------------|-------------------------|

|              |                  |                                         |                         |

| Bit | Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | PD   | <b>Power Down mode.</b><br>Setting this bit puts MCU into Power Down mode. Under this mode, both CPU and peripheral clocks stop and Program Counter (PC) suspends. It provides the lowest power consumption. After CPU is woken up from Power Down, this bit will be automatically cleared via hardware and the program continue executing the interrupt service routine (ISR) of the very interrupt source that woke the system up before. After return from the ISR, the device continues execution at the instruction which follows the instruction that put the system into Power Down mode.<br>Note that If IDL bit and PD bit are set simultaneously, the MCU will enter into Power Down mode. Then it does not go to Idle mode after exiting Power Down. |

| 0   | IDL  | Idle mode.<br>Setting this bit puts MCU into Idle mode. Under this mode, the CPU clock stops<br>and Program Counter (PC) suspends. After CPU is woken up from Idle, this bit<br>will be automatically cleared via hardware and the program continue executing the<br>ISR of the very interrupt source that woke the system up before. After return from<br>the ISR, the device continues execution at the instruction which follows the in-<br>struction that put the system into Idle mode.                                                                                                                                                                                                                                                                    |

### 19.1 Idle Mode

Idle mode suspends CPU processing by holding the Program Counter. No program code are fetched and run in Idle mode. This forces the CPU state to be frozen. The Program Counter (PC), the Stack Pointer (SP), the Program Status Word (PSW), the Accumulator (ACC), and the other registers hold their contents during Idle mode. The port pins hold the logical states they had at the time Idle was activated. Generally, it saves considerable power of typical half of the full operating power.

# nuvoton

nal. The reset circuitry then synchronously applies the internal reset signal. Thus the reset is a synchronous operation and requires the clock to be running to cause an external reset.

Once the device is in reset condition, it will remain so as long as RST pin is 1. After the RST high is removed, the CPU will exit the reset state with in two machine-cycles and begin code executing from address 0000H. There is no flag associated with the RST pin reset condition. However since the other reset sources have flags, the external reset can be considered as the default reset if those reset flags are cleared.

If a RST pin reset applies while CPU is in Power Down mode, the way to trigger a hardware reset is slightly different. Since the Power Down mode stops system clock, the reset signal will asynchronously cause the system clock resuming. After the system clock is stable, CPU will enter into the reset state.

### 22.4 Watchdog Timer Reset

The Watchdog Timer is a free running timer with programmable time-out intervals. The user can clear the Watchdog Timer at any time, causing it to restart the count. When the selected time-out occurs, the Watchdog Timer will reset the system directly. The reset condition is maintained via hardware for two machine-cycles. After the reset is removed, the device will begin execution from 0000H.

Once a reset due to Watchdog Timer occurs the Watchdog Timer reset flag WDTRF (WDCON.3) will be set. This bit keeps unchanged after any reset other than a power-on reset. The user may clear WDTRF via software.

### 22.5 Software Reset

N78E059A/N78E055A is enhanced with a software reset. This allows the program code to reset the whole system in software approach. It is quite useful in the end of an ISP progress. For example, if an LDROM updating APROM ISP finishes and the code in APROM is correctly updated, a software reset can be asserted to reboot CPU from the APROM in order to check the result of the updated APROM program code immediately. Writing 1 to SWRST (CHPCON.7) will trigger a software reset. Note that this bit is timed access protection. See demo code below. After a software reset the SWRF (RSR.0) will be automatically set via hardware. This bit will be preserved its value after all resets except power-on reset. SWRF can also be cleared via software. ah

is forced to 0000H and held as long as the reset condition is applied. Note that the Stack Pointer is also reset to 07H, therefore the stack contents may be effectively lost during the reset event even though the RAM contents are not altered.

After a reset, interrupts and Timers are disabled. The I/O port SFRs have FFH written into them which puts the port pins in a high state.

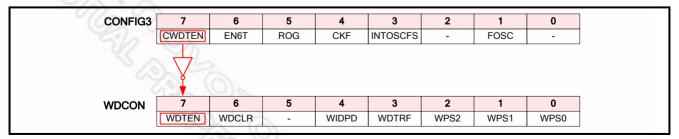

#### **CONFIG3**

| 7      | 6    | 5   | 4   | 3        | 2   | 1    | 0 |

|--------|------|-----|-----|----------|-----|------|---|

| CWDTEN | EN6T | ROG | CKF | INTOSCFS | -   | FOSC | - |

| r/w    | r/w  | r/w | r/w | r/w      | 8 - | r/w  | - |

unprogrammed value: 1111 1111b

|   | Bit   | Name     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---|-------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 7     | CWDTEN   | <b>CONFIG Watchdog Timer enable.</b><br>1 = Disable Watchdog Timer after all resets.<br>0 = Enable Watchdog Timer after all resets.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   | 6     | EN6T     | <ul> <li>Enable 6T mode.</li> <li>This bit switches MCU between 12T and 6T mode. See Figure 20–1. Clock System Block Diagram for definitions in details.</li> <li>1 = MCU runs at 12T mode. Each machine-cycle is equal to 12 clocks of system oscillator. The operating mode is the same as a standard 8051 MCU. (F<sub>CPU</sub> and F<sub>PERIPH</sub> is a half of F<sub>OSC</sub>.)</li> <li>0 = MCU runs at 6T mode. Each machine-cycle is equal to 6 clocks of system oscillator. This mode doubles the whole chip operation compared with the standard 8051. (F<sub>CPU</sub> and F<sub>PERIPH</sub> is equal to F<sub>OSC</sub>.)</li> </ul> |

|   | 5     | ROG      | <ul> <li>Reducing oscillator gain.</li> <li>1 = Use normal gain for crystal oscillating. The frequency can be up to 40MHz.</li> <li>0 = Use reduced gain for crystal oscillating. The frequency should be lower than 24MHz. In reduced gain mode, it will also help to decrease EMI.</li> </ul>                                                                                                                                                                                                                                                                                                                                                       |

|   | 4     | CKF      | Clock filter enable.<br>1 = Enable clock filter. It increases noise immunity and EMC capacity.<br>0 = Disable clock filter.<br>Note that the clock filter should be always disabled if the crystal frequency is<br>above 24MHz.                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   | 3     | INTOSCFS | <ul> <li>Internal RC oscillator frequency select.</li> <li>1 = Select 22.1184MHz as the system clock if internal RC oscillator mode is used.<br/>It bypasses the divided-by-2 path of internal oscillator to select 22.1184MHz<br/>output as the system clock source.</li> <li>0 = Select 11.0592MHz as the system clock if internal RC oscillator mode is used.<br/>The internal RC divided-by-2 path is selected. The internal oscillator is equivalent to 11.0592MHz output used as the system clock.</li> </ul>                                                                                                                                   |

|   | 2     | -        | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   | 1 the | FOSC     | Oscillator selection bit.<br>This bit selects the source of the system clock.<br>1 = Crystal, resonator, or external clock input.<br>0 = Internal RC oscillator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| X | 0     | Sk -     | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

#### Figure 24–3. CONFIG3 Reset Reloading

## **25. INSTRUCTION SET**

N78E059A/N78E055A executes all the instructions of the standard 8051 family. All instructions are coded within an 8-bit field called an OPCODE. This single byte must be fetched from Program Memory. The OPCODE is decoded by the CPU. It determines what action the microcontroller will take and whether more operation data is needed from memory. If no other data is needed, then only one byte was required. Thus the instruction is called a one byte instruction. In some cases, more data is needed. These will be two or three byte instructions.

Table 25–1 lists all instructions in details. Note of the instruction set and addressing modes are shown below.

| Rn (n = 0~7)   | Register R0~R7 of the currently selected Register Bank.                                                                                                                    |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| direct         | 8-bit internal data location's address. This could be an internal data RAM location (0~ 127) or a SFR (e.g., I/O port, control register, status register, etc. (128~255)). |

| @Ri (i = 0, 1) | 8-bit internal data RAM location (0~255) addressed indirectly through register R0 or R1.                                                                                   |

| #data          | 8-bit constant included in the instruction.                                                                                                                                |

| #data16        | 16-bit constant included in the instruction.                                                                                                                               |

| addr16         | 16-bit destination address. Used by LCALL and LJMP. A branch can be anywhere within the 64k-byte Program Memory address space.                                             |

| addr11         | 11-bit destination address. Used by ACALL and AJMP. The branch will be within the same 2k-byte page of Program Memory as the first byte of the following instruction.      |

| rel            | Signed (2's complement) 8-bit offset byte. Used by SJMP and all conditional branches.<br>Range is -128 to +127 bytes relative to first byte of the following instruction.  |

| bit            | Direct addressed bit in internal data RAM or SFR.                                                                                                                          |

#### Table 25-1. Instruction Set for N78E059A/N78E055A

| Instruction    | OPCODE | Bytes | Clock Cycles<br>in 12T Mode | Clock Cycles<br>in 6T Mode |

|----------------|--------|-------|-----------------------------|----------------------------|

| NOP            | 00     | 1     | 12                          | 6                          |

| ADD A, Rn      | 28~2F  | 1     | 12                          | 6                          |

| ADD A, @Ri     | 26, 27 | 1     | 12                          | 6                          |

| ADD A, direct  | 25     | 2     | 12                          | 6                          |

| ADD A, #data   | 24     | 2     | 12                          | 6                          |

| ADDC A, Rn     | 38~3F  | 1     | 12                          | 6                          |

| ADDC A, @Ri    | 36, 37 | 1     | 12                          | 6                          |

| ADDC A, direct | 35     | 2     | 12                          | 6                          |

| ADDC A, #data  | 34     | 2     | 12                          | 6                          |

| SUBB A, Rn     | 98~9F  | 1     | 12                          | 6                          |

| SUBB A, @Ri    | 96, 97 | 1     | 12                          | 6                          |

| SUBB A, direct | 95     | 2     | 12                          | 6                          |

| SUBB A, #data  | 94     | 2     | 12                          | 6                          |

# **26. ELECTRICAL CHARACTERISTICS**

## 26.1 Absolute Maximum Ratings

| Parameter                            | Rating                         | Unit |

|--------------------------------------|--------------------------------|------|

| Operating temperature under bias     | -40 to +85                     | °C   |

| Storage temperature range            | -55 to +150                    | °C   |

| Voltage on VDD pin to $V_{SS}$       | -0.3 to +6.5                   | V    |

| Voltage on any other pin to $V_{SS}$ | -0.3 to (V <sub>DD</sub> +0.3) | V    |

Stresses at or above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

### **26.2 DC Electrical Characteristics**

Temperature =  $-40^{\circ}$ C  $\sim 85^{\circ}$ C; V<sub>SS</sub> = 0V;

V<sub>DD</sub> = 4.5V to 5.5V @ F = 0 to 40MHz (12T mode), F = 0 to 33MHz (6T mode)

$V_{DD}$  = 2.4V to 5.5V @ F = 0 to 27MHz (12T mode), F = 0 to 20MHz (6T mode)

$V_{DD}$  = 3.0V to 5.5V for ISP erasing or programming.

#### Table 26–1. DC Characteristics

| Symbol           | Parameter                                                                        | Condition                                                                                             | Min.                     | Тур. | Max.                   | Unit |

|------------------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--------------------------|------|------------------------|------|

| VIL              | Input low voltage                                                                |                                                                                                       |                          |      | $0.2V_{\text{DD}}-0.1$ | V    |

| Vih              | Input high voltage (Ports 0 ~ 4, $\overline{EA}$ )                               |                                                                                                       | 0.2V <sub>DD</sub> + 0.9 |      |                        | V    |

| V <sub>IH1</sub> | Input high voltage<br>(RST, XTAL1)                                               |                                                                                                       | $0.7V_{DD}$              |      |                        | V    |

| V <sub>OL</sub>  | Output low voltage <sup>[1]</sup>                                                | $V_{DD} = 4.5V, I_{OL} = 8.2mA$<br>$V_{DD} = 3.0V, I_{OL} = 5.8mA$<br>$V_{DD} = 2.4V, I_{OL} = 4.4mA$ |                          |      | 0.4                    | V    |

| V <sub>OH</sub>  | Output high voltage<br>(Ports 1 ~ 4 and Port 0 with<br>internal pull-up enabled) |                                                                                                       | 2.4<br>2.4<br>2.0        |      |                        | V    |

| V <sub>OH1</sub> | Output high voltage<br>(Ports 0 and 2 in external bus<br>mode, ALE, PSEN)        |                                                                                                       | 2.4<br>2.4<br>2.0        |      |                        | V    |

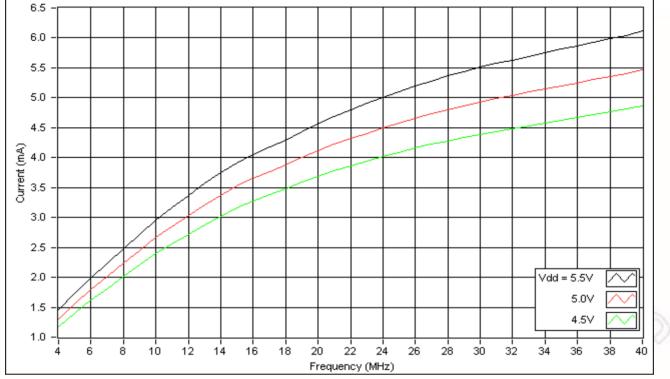

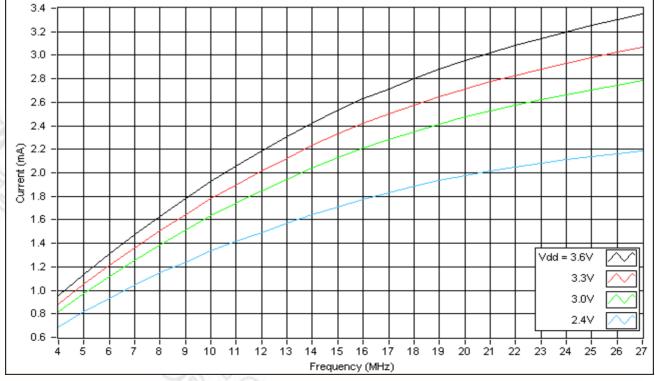

Figure 26–5. Idle Mode Current Under 12T Mode, External Clock (1)

## **26.3 AC Electrical Characteristics**

#### Table 26–2. AC Characteristics

| Symbol               | Parameter -                        | 12T                     | 12T mode                |                           | 6T mode                   |        |