Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                        |

|----------------------------|----------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                 |

| Core Processor             | 8051                                                                                   |

| Core Size                  | 8-Bit                                                                                  |

| Speed                      | 40MHz                                                                                  |

| Connectivity               | EBI/EMI, SPI, UART/USART                                                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                             |

| Number of I/O              | 36                                                                                     |

| Program Memory Size        | 32KB (32K x 8)                                                                         |

| Program Memory Type        | FLASH                                                                                  |

| EEPROM Size                | -                                                                                      |

| RAM Size                   | 1.25K x 8                                                                              |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 5.5V                                                                            |

| Data Converters            | -                                                                                      |

| Oscillator Type            | Internal                                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                      |

| Mounting Type              | Surface Mount                                                                          |

| Package / Case             | 44-BQFP                                                                                |

| Supplier Device Package    | -                                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/nuvoton-technology-corporation-america/n78e059afg |

|                            |                                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 14.8 Write Collision Error         |                                          |

|------------------------------------|------------------------------------------|

| 14.9 Overrun Error                 |                                          |

| 14.10 SPI Interrupts               |                                          |

| 15. PULSE WIDTH MODULATOR (PWM)    |                                          |

|                                    |                                          |

|                                    |                                          |

|                                    |                                          |

|                                    |                                          |

|                                    |                                          |

|                                    |                                          |

|                                    |                                          |

|                                    |                                          |

| 18.4 ISP Demo Code                 |                                          |

|                                    |                                          |

|                                    |                                          |

|                                    |                                          |

|                                    |                                          |

|                                    |                                          |

|                                    |                                          |

|                                    |                                          |

| •                                  |                                          |

|                                    |                                          |

|                                    |                                          |

|                                    |                                          |

|                                    |                                          |

|                                    |                                          |

|                                    |                                          |

|                                    |                                          |

|                                    |                                          |

|                                    |                                          |

|                                    |                                          |

|                                    |                                          |

|                                    |                                          |

|                                    |                                          |

|                                    |                                          |

| 26. ELECTRICAL CHARACTERISTICS     |                                          |

| 26.1 Absolute Maximum Ratings      |                                          |

| 26.2 DC Electrical Characteristics |                                          |

| 26.3 AC Electrical Characteristics |                                          |

| 27. PACKAGES                       |                                          |

| 28. DOCUMENT REVISION HISTORY      |                                          |

|                                    |                                          |

|                                    |                                          |

|                                    |                                          |

|                                    |                                          |

|                                    |                                          |

|                                    |                                          |

|                                    |                                          |

|                                    |                                          |

|                                    |                                          |

|                                    | Publication Release Date: March 11, 2010 |

|                                    | - 3 - Revision: V2.0                     |

|                                    |                                          |

|                                    |                                          |

#### Table 4–1. Pin Description

|     | Pin n | umber |      | 0      |      | • Function | Type <sup>[1]</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----|-------|-------|------|--------|------|------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIP | PLCC  | PQFP  | LQFP | Symbol | 1    | 2          | i ype               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 19  | 21    | 15    | 16   | XTAL1  |      |            | l<br>(ST)           | <b>CRYSTAL1:</b> This is the input pin to the internal invert-<br>ing amplifier. The system clock is from external crys-<br>tal or resonator when FOSC (CONFIG3.1) is logic 1<br>by default.<br><i>A 0.1µF capacitor is recommended to be added on</i><br><i>XTAL1 pin to gain the more precise frequency of</i><br><i>the internal RC oscillator frequency if it is selected</i><br><i>as the system clock source.</i>                                                                                                                                                                                                                                                                                                            |

| 18  | 20    | 14    | 15   | XTAL2  |      |            | 0                   | <b>CRYSTAL2:</b> This is the output pin from the internal inverting amplifier. It emits the inverted signal of XTAL1. While on-chip RC oscillator is used, float XTAL2 pin always.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 40  | 44    | 38    | 41   | VDD    |      |            | Р                   | <b>POWER SUPPLY:</b> Supply voltage $V_{DD}$ for operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 20  | 22    | 16    | 17   | VSS    |      |            | Р                   | GROUND: Ground potential.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 31  | 35    | 29    | 31   | ĒĀ     |      |            | Ι                   | <ul> <li>EXTERNAL ACCESS ENABLE: To force EA low will make the CPU execute the external Program Memory. The address and data will be presented on the bus P0 and P2. If the EA pin is high, CPU will fetch internal code unless the Program Counter addresses the area out of the internal Program Memory. This will make CPU run external Program Memory continuously.</li> <li>EA possesses reset lock. After all reset, the EA state will be latched and any state change of this pin after reset will not switch between internal and external Program Memory execution.</li> <li>The user should take care of this pin from floating but connecting to V<sub>DD</sub> directly if internal Program Memory is used.</li> </ul> |

| 30  | 33    | 27    | 29   | ALE    |      |            | 0                   | ADDRESS LATCH ENABLE: ALE is used to enable<br>the address latch that separates the address from the<br>data on Port 0. ALE runs at 1/6 of the Fosc <sup>[2]</sup> . An ALE<br>pulse is omitted always.<br>The user can turn ALE off by setting ALEOFF<br>(AUXR.0) to reduce EMI. Setting ALEOFF will just<br>make ALE activating only during external memory<br>access through a MOVC or MOVX instruction. ALE<br>will stay high in other conditions.                                                                                                                                                                                                                                                                             |

| 29  | 32    | 26    | 28   | PSEN   |      |            | 0                   | <b>PROGRAM STORE ENABLE:</b> PSEN strobes the external Program Memory. When internal Program Memory access is performed, there will be no PSEN strobe signal output from this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 9   | 10    | 4     | 4    | RST    | A CO |            | l<br>(ST)           | <b>RESET:</b> RST pin is a Schmitt trigger input pin for<br>hardware device reset. A high on this pin for two ma-<br>chine-cycles while the system clock is running will<br>reset the device. RST pin has an internal pull-down<br>resistor allowing power-on reset by simply connecting                                                                                                                                                                                                                                                                                                                                                                                                                                           |

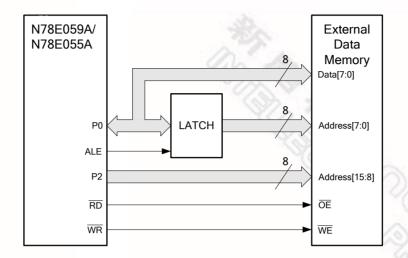

Figure 5–5. Data Memory Interface

### 5.6 On-chip Non-volatile Data Flash

N78E059A/N78E055A additionally has Data Flash. The Data Flash is non-volatile so that it remains its content even after the power is off. Therefore, in general application the user can write or read data which rules as parameters or constants. Be aware of Data Flash writing endurance of 10,000 cycles. By the software path, the Data Flash can be accessed only through ISP mode. Note that the erasing or writing of Data Flash should not operates under V<sub>DD</sub> 3.0V for ISP limitation. For Data Flash accessing with ISP, please see <u>Section 18. "IN</u> <u>SYSTEM PROGRAMMING (ISP)" on page 91</u> for details. For the design for security, ISP is invalid while external Program Memory executes. The Data Flash, therefore, cannot be accessed with external memory code. Of course the Data Flash can be accessed via hardware with parallel Programmer/Writer.

The Data Flash size is fixed as 4k-byte size on N78E059A/N78E055A.

#### Table 6–2. N78E059A/N78E055A SFR Descriptions and Reset Values

| Symbol                | Definition                             | Address    | MSB         |             |              |               |                    |              |             | LSB <sup>[1]</sup> | Reset                                            | Value              |

|-----------------------|----------------------------------------|------------|-------------|-------------|--------------|---------------|--------------------|--------------|-------------|--------------------|--------------------------------------------------|--------------------|

| SPDR                  | SPI data                               | F5H        |             |             |              | 100           |                    |              |             |                    | 0000                                             |                    |

| SPSR                  | SPI status                             | F4H        | SPIF        | WCOL        | SPIOVF       | MODF          | DISMODF            | -            | -           | -                  | 0000                                             | 000                |

| SPCR                  | SPI control                            | F3H        | SSOE        | SPIEN       | LSBFE        | MSTR          | CPOL               | CPHA         | SPR1        | SPR0               | 0000                                             |                    |

| B                     | B register                             | F0H        | (F7)        | (F6)        | (F5)         | (F4)          | (F3)               | (F2)         | (F1)        | (F0)               | 0000                                             |                    |

| ACC                   | Accumulator                            | E0H        | (E7)        | (E6)        | (E5)         | (E4)          | (E3)               | (E2)         | (E1)        | (E0)               | 0000                                             |                    |

| PWM3                  | PWM3 duty                              | DEH        | (= / )      | (20)        | (20)         | (= 1)         | (20)               | (==)         | (= !)       | (20)               | 0000                                             |                    |

| PWM2                  | PWM2 duty                              | DDH        | -           |             |              | 1             | 0 10               | 132          |             |                    | 0000                                             |                    |

|                       |                                        | DCH        | PW/M3OF     | PW/M2OF     | PW/M3EN      | PW/M2EN       | PWM10E             | PW/MOOF      | PWM1EN      | PW/MOEN            |                                                  |                    |

| PWM1                  | PWM1 duty                              | DBH        | TWINGOL     | TWIMEOL     | TWINGEN      |               | TWINTOL            | TWINOOL      | TVINIEN     | TWINGEN            | 0000                                             |                    |

| PWM0                  | PWM0 duty                              | DAH        |             |             |              |               |                    | 1            |             |                    | 0000                                             |                    |

| PWMP                  | PWM period                             | DAH<br>D9H |             |             |              |               | - 10               |              |             |                    | 0000                                             |                    |

|                       |                                        | Dau        | (DF)        | (DE)        | (DD)         | (DC)          | (DB)               |              | (D9)        | (D8)               | 0000                                             | 000                |

| P4                    | Port 4                                 | D8H        | (DF)        | (DE)        | (00)         | (DC)          | INT2               | (DA)<br>INT3 | (D9)        | (D0)               | 1111                                             | 11                 |

| PSW                   | Program status word                    | D0H        | (D7)<br>CY  | (D6)<br>AC  | (D5)<br>F0   | (D4)<br>RS1   | (D3)<br>RS0        | (D2)<br>OV   | (D1)<br>F1  | (D0)<br>P          | 0000                                             | 000                |

| PWM4                  | PWM4 duty                              | CFH        |             |             |              |               |                    |              | 2           | 1 ling             | 0000                                             | 00                 |

| PWMCON1               | PWM control 1                          | CEH        | -           | -           | -            | -             | -                  | PWM4OE       | 6.20        | PWM4EN             |                                                  |                    |

| TH2                   | Timer 2 high byte                      | CDH        |             |             |              |               | 1                  |              | 7.0         | 0. (6              | 0000                                             |                    |

| TL2                   | Timer 2 low byte                       | CCH        |             |             |              |               |                    |              | 11          |                    | 0000                                             |                    |

| RCAP2H                | Timer 2 reload/capture<br>high byte    | СВН        |             |             |              |               |                    |              | 1           | 20                 | 0000                                             |                    |

| RCAP2L                | Timer 2 reload/capture<br>low byte     | CAH        |             |             |              |               |                    |              |             | - 73               | 0000                                             | 00                 |

| T2MOD                 | Timer 2 mode                           | C9H        | -           | -           | -            | -             | -                  | -            | T2OE        |                    | 0000                                             | 000                |

|                       |                                        | 2.5.1.     | (CF)        | (CE)        | (CD)         | (CC)          | (CB)               | (CA)         | (C9)        | (C8)               |                                                  |                    |

| T2CON                 | Timer 2 control                        | C8H        | TF2         | EXF2        | (CD)<br>RCLK | TCLK          | EXEN2              | TR2          | C/T2        | CP/RL2             | 0000                                             |                    |

| ТА                    | Timed access protection                | C7H        |             |             |              |               |                    |              |             |                    | 0000                                             | 000                |

| XICON                 | External interrupt control             | СОН        | (C7)<br>PX3 | (C6)<br>EX3 | (C4)<br>IE3  | (C4)<br>IT3   | (C3)<br>PX2        | (C2)<br>EX2  | (C1)<br>IE2 | (C0)<br>1IT2       | 0000                                             | 000                |

| EIE                   | Extensive interrupt ena-<br>ble        | BDH        | -           | -           | -            | -             | -                  | EBOD         | EPDT        | ESPI               | 0000                                             | 000                |

| EIP                   | Extensive interrupt priori-<br>ty      | BCH        | -           | -           | -            | -             | -                  | PBOV         | PPDT        | PSPI               | 0000                                             | 000                |

| EIPH                  | Extensive interrupt priori-<br>ty high | BBH        | -           | -           | -            | -             | -                  | PBODH        | PPDTH       | PSPIH              | 0000                                             |                    |

| IPH                   | Interrupt priority high                | BAH        | PX3H        | PX2H        | PT2H         | PSH           | PT1H               | PX1H         | PT0H        | PX0H               | 0000                                             | 000                |

| IP                    | Interrupt priority                     | B8H        | (BF)<br>-   | (BE)<br>-   | (BD)<br>PT2  | (BC)<br>PS    | (BB)<br>PT1        | (BA)<br>PX1  | (B9)<br>PT0 | (B8)<br>PX0        | 0000                                             | 00(                |

| P3                    | Port 3                                 | B0H        | (B7)        | (B6)        | (B5)         | (B4)          | (B3)               | (B2)         | (B1)        | (B0)               | 1111                                             | 11                 |

|                       |                                        |            | RD          | WR          | T1           | Т0            | INT1               | INT0         | TXD         | RXD                |                                                  |                    |

| ISPCN                 | ISP flash control                      | AFH        | ISPA17      | ISPA16      | FOEN         | FCEN          | FCTRL3             | FCTRL2       | FCTRL1      | FCTRL0             | 0000                                             | 00                 |

| ISPFD                 | ISP flash data                         | AEH        |             |             |              |               |                    |              |             |                    | 0000                                             | 00                 |

| PMC <sup>[3]</sup>    | Power monitoring control               | ACH        | BODEN       | -           | -            | BORST         | BOF <sup>[4]</sup> | LPBOD        | -           | BOS <sup>[5]</sup> | Power<br>XXXX<br>Brown<br>XXXX<br>Others<br>XXXX | X0<br>-out,<br>10  |

| PDCON                 | Power Down waking-up<br>timer control  | ABH        | PDTEN       | PDTCK       | PDTF         | -             | -                  | PPS2         | PPS1        | PPS0               | 0000                                             |                    |

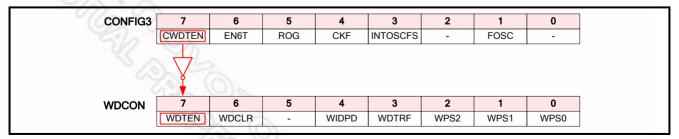

| WDCON <sup>[3]</sup>  | Watchdog Timer control                 | ААН        | WDTEN       | WDCLR       | -            | WIDPD         | WDTRF              | WPS2         | WPS1        | WPS0               | Power<br>X000<br>Watch<br>X00U<br>Others<br>X00U | 000<br>dog,<br>1UU |

| IE                    | Interrupt enable                       | A8H        | (AF)<br>EA  | (AE)<br>-   | (AD)<br>ET2  | (AC)<br>ES    | (AB)<br>ET1        | (AA)<br>EX1  | (A9)<br>ET0 | (A8)<br>EX0        | 0000                                             |                    |

| ISPAH                 | ISP address high byte                  | A7H        | Sec. 1      |             |              |               |                    |              |             |                    | 0000                                             |                    |

| ISPAL                 | ISP address low byte                   | A6H        | No          |             |              |               |                    |              |             |                    | 0000                                             | 00                 |

| ISPTRG <sup>[3]</sup> | ISP trigger                            | A4H        | 2.          | -           | -            | -             | -                  | -            | -           | ISPGO              | 0000                                             | 00                 |

| XRAMAH                | Auxiliary RAM address                  | A1H        | 46          | s           | -            | -             | -                  | -            |             | XRAMAH.0           | 1                                                |                    |

|                       |                                        | ~~~        | (A7)        | (AG)        | (A5)         | $(\Lambda A)$ | (A3)               | (A2)         | (A1)        | (A0)               |                                                  |                    |

| P2                    | Port 2                                 | A0H        | (A7)<br>A15 | (A6)<br>A14 | (A5)<br>A13  | (A4)<br>A12   | (43)               | (A2)<br>A10  | (A1)        | (AU)               | 1111                                             | 1 1                |

| Symbol | Definition             | Address | MSB                   |                      |                      | -                          |              |             |              | LSB <sup>[1]</sup> | Reset Value <sup>[2</sup>                                                                               |

|--------|------------------------|---------|-----------------------|----------------------|----------------------|----------------------------|--------------|-------------|--------------|--------------------|---------------------------------------------------------------------------------------------------------|

|        | Chip control           | 9FH     | SWRST                 | ISPF                 | LDUEN                | XRAMEN                     | <u>.</u>     | -           | BS           | ISPEN              | Software <sup>[6]</sup> ,<br>0001 00U0<br>Others,<br>0001 00X0                                          |

| SBUF   | Serial buffer          | 99H     |                       |                      |                      | ~/~                        | N            |             |              |                    | 0000 0000                                                                                               |

| SCON   | Serial control         | 98H     | (9F)<br>SM0           | (9E)<br>SM1          | (9D)<br>SM2          | (9C)<br>REN                | (9B)<br>TB8  | (9A)<br>RB8 | (99)<br>TI   | (98)<br>RI         | 0000 0000                                                                                               |

| RSR    | Reset status register  | 96H     | -                     | -                    | -                    | -                          | 30           | BORF        | 200          | SWRF               | Power-on,<br>0000 00001<br>Brown-out,<br>0000 01001<br>Software,<br>0000 00011<br>Others,<br>0000 00001 |

| P1     | Port 1                 | 90H     | (97)<br>PWM4<br>SPCLK | (96)<br>PWM3<br>MISO | (95)<br>PWM2<br>MOSI | (94)<br>PWM1<br><u>S</u> S | (93)<br>PWM0 | (92)        | (91)<br>T2EX | (90)<br>T2         | 1111 1111                                                                                               |

| AUXR   | Auxiliary register     | 8EH     | -                     | -                    | -                    | -                          | -            | -           | - 211        | ALEOFF             | 0000 0000                                                                                               |

| TH1    | Timer 1 high byte      | 8DH     |                       |                      |                      |                            |              |             | 4            | Oh                 | 0000 0000                                                                                               |

| TH0    | Timer 0 high byte      | 8CH     |                       |                      |                      |                            |              |             |              | 7.01               | 0000 0000                                                                                               |

| TL1    | Timer 1 low byte       | 8BH     |                       |                      |                      |                            |              |             |              | - 70               | 0000 0000                                                                                               |

| TL0    | Timer 0 low byte       | 8AH     |                       |                      |                      |                            |              |             |              | 0                  | 0000 0000                                                                                               |

| TMOD   | Timer 0 and 1 mode     | 89H     | GATE                  | C/T                  | M1                   | MO                         | GATE         | C/T         | M1           | MO                 | 0000 0000                                                                                               |

| TCON   | Timer 0 and 1control   | 88H     | (8F)<br>TF1           | (8E)<br>TR1          | (8D)<br>TF0          | (8C)<br>TR0                | (8B)<br>IE1  | (8A)<br>IT1 | (89)<br>IE0  | (88)<br>IT0        | 0000 0000                                                                                               |

| PCON   | Power control          | 87H     | SMOD                  | -                    | -                    | POF                        | GF1          | GF0         | PD           | IDL                | Power-on,<br>0001 00001<br>Others,<br>000U 00001                                                        |

| P00R   | P0 option register     | 86H     | -                     | -                    | -                    | -                          |              | -           | -            | POUP               | 0000 0000                                                                                               |

| DPH    | Data pointer high byte | 83H     |                       |                      |                      |                            |              |             |              |                    | 0000 0000                                                                                               |

| DPL    | Data pointer low byte  | 82H     |                       |                      |                      |                            |              |             |              |                    | 0000 0000                                                                                               |

| SP     | Stack pointer          | 81H     |                       |                      | 1                    |                            |              |             |              |                    | 0000 01111                                                                                              |

| P0     | Port 0                 | 80H     | (87)<br>A7            | (86)<br>A6           | (85)<br>A5           | (84)<br>A4                 | (83)<br>A3   | (82)<br>A2  | (81)<br>A1   | (80)<br>A0         | 1111 1111                                                                                               |

#### Table 6–2. N78E059A/N78E055A SFR Descriptions and Reset Values

[3] These SFRs have TA protected writing.

[4] BOF has different power-on reset value according to CBODEN (CONFIG2.7) and CBORST (CONFIG2.4). See Table 21-1. BOF Reset Value

[5] BOS is a read-only flag decided by V<sub>DD</sub> level while Brown-out detection is enabled.

[6] These SFRs have bits which are initialized after specified reset by loading certain bits in CONFIG bytes. See Section 24. "CONFIG BYTES" on page 116 for details.

Note that bits marked in "-" must be kept in their own initial states. Users should never change their values.

### nuvoton

P0UP (P0OR.0) P0 will switch on its weak pull-up internally and behave the same as the quasi bi-directional I/O pins.

P0 and P2 also serve as address/data bus when external memory is running or is accessed by MOVC or MOVX instruction. In these cases, it has strong pull-up and pull-down. In this application, there is no need of any external pull-up resistor. While external mode execution, P0 and P2 cannot be used as general purpose I/O anymore.

In standard 8051 instruction set, one kind of instructions, read-modify-write instructions, should be specially taken care of. Instead of the normal instructions, the read-modify-write instructions read the internal port latch (Px in SFRs) rather than the external port pin state. This kind of instructions read the port SFR value, modify it and write back to the port SFR. Read-modify-write instructions are listed as follows.

| Instruction | n      | Description                                        |

|-------------|--------|----------------------------------------------------|

| ANL         |        | Logical AND. (ANL Px,A and ANL Px,direct)          |

| ORL         |        | Logical OR. (ORL Px,A and ORL Px,direct)           |

| XRL         |        | Logical exclusive OR. (XRL Px,A and XRL Px,direct) |

| JBC         |        | Jump if bit = 1 and clear it. (JBC Px.y,LABEL)     |

| CPL         |        | Complement bit. (CPL Px.y)                         |

| INC         |        | Increment. (INC Px)                                |

| DEC         |        | Decrement. (DEC Px)                                |

| DJNZ        |        | Decrement and jump if not zero. (DJNZ Px,LABEL)    |

| MOV         | Px.y,C | Move carry bit to Px.y.                            |

| CLR         | Px.y   | Clear bit Px.y.                                    |

| SETB        | Px.y   | Set bit Px.y.                                      |

The last three seems not obviously read-modify-write instructions but actually they are. They read the entire port latch value, modify the changed bit, then write the new value back to the port latch.

### **10. TIMERS/COUNTERS**

N78E059A/N78E055A has three 16-bit programmable timers/counters.

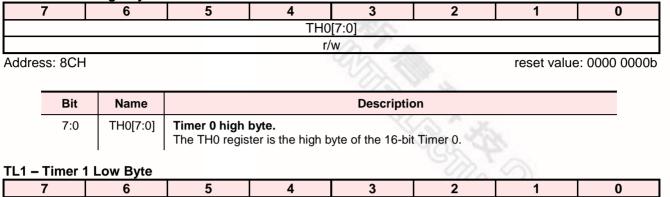

### 10.1 Timer/Counters 0 and 1

Timer/Counter 0 and 1 on N78E059A/N78E055A are two 16-bit Timer/Counters. Each of them has two 8 bit registers which form the 16 bit counting register. For Timer/Counter 0 they are TH0, the upper 8 bits register, and TL0, the lower 8 bit register. Similarly Timer/Counter 1 has two 8 bit registers, TH1 and TL1. TCON and TMOD can configure modes of Timer/Counter 0 and 1.

The Timer or Counter function is selected by the  $C/\overline{T}$  bit in TMOD. Each Timer/Counter has its own selection bit. TMOD.2 selects the function for Timer/Counter 0 and TMOD.6 selects the function for Timer/Counter 1

When configured as a "Timer", the timer counts clock cycles. The timer clock is 1/6 of the peripheral clock ( $F_{PERIPH}$ ). In the "Counter" mode, the register increases on the falling edge of the external input pins T0 for Timer 0 and T1 for Timer 1. If the sampled value is high in one machine-cycle and low in the next, a valid 1 to 0 transition on the pin is recognized and the count register increases.

In addition, each Timer/Counter can be set to operate in any one of four possible modes. Bits M0 and M1 in TMOD do the mode selection.

|   |      |     | ue  |     |      |     |     |     |

|---|------|-----|-----|-----|------|-----|-----|-----|

|   | 7    | 6   | 5   | 4   | 3    | 2   | 1   | 0   |

| R | GATE | C/T | M1  | M0  | GATE | C/T | M1  | MO  |

| 2 | r/w  | r/w | r/w | r/w | r/w  | r/w | r/w | r/w |

#### TMOD – Timer 0 and 1 Mode

Address: 89H

reset value: 0000 0000b

| Bit       | Name | Description                                                                                                                                                                                                                    |  |  |  |  |  |  |

|-----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| TX<br>COL | GATE | <b>Timer 1 gate control.</b><br>$0 = \text{Timer 1}$ will clock when TR1 = 1 regardless of $\overline{\text{INT1}}$ logic level.<br>$1 = \text{Timer 1}$ will clock only when TR1 = 1 and $\overline{\text{INT1}}$ is logic 1. |  |  |  |  |  |  |

| 6         | с/т  | Timer 1 Counter/Timer select.0 = Timer 1 is incremented by internal peripheral clocks.1 = Timer 1 is incremented by the falling edge of the external pin T1.                                                                   |  |  |  |  |  |  |

| 5         | M1   | Timer 1 mode select.                                                                                                                                                                                                           |  |  |  |  |  |  |

| 4         | MO   | M1M0Timer 1 Mode00Mode 0: 8-bit Timer/Counter with 5-bit pre-scalar (TL1[4:0])01Mode 1: 16-bit Timer/Counter10Mode 2: 8-bit Timer/Counter with auto-reload from TH111Mode 3: Timer 1 halted                                    |  |  |  |  |  |  |

#### TH0 – Timer 0 High Byte

| 7   | 6 | 5 | 4   | 3     | 2 | 1    | 0         |

|-----|---|---|-----|-------|---|------|-----------|

|     |   |   | TL1 | [7:0] | Z | 2.00 |           |

| r/w |   |   |     |       |   |      |           |

|     | l |   |     |       |   | A.A  | 0000 0000 |

Address: 8BH

reset value: 0000 0000b

| Bit | Name     | Description                                                                  | à  |

|-----|----------|------------------------------------------------------------------------------|----|

| 7:0 | TL1[7:0] | Timer 1 low byte.<br>The TL1 register is the low byte of the 16-bit Timer 1. | 20 |

#### TH1 – Timer 1 High Byte

|   | <u> </u> |   |     |       |   |   |   |

|---|----------|---|-----|-------|---|---|---|

| 7 | 6        | 5 | 4   | 3     | 2 | 1 | 0 |

|   |          |   | TH1 | [7:0] |   |   |   |

|   |          |   | r/  | w     |   |   |   |

|   |          |   |     |       |   |   |   |

Address: 8DH

reset value: 0000 0000b

| Bit | Name     | Description                                                                           |

|-----|----------|---------------------------------------------------------------------------------------|

| 7:0 | TH1[7:0] | <b>Timer 1 high byte.</b><br>The TH1 register is the high byte of the 16-bit Timer 1. |

### 10.1.1 Mode 0 (13-bit Timer)

In Mode 0, the Timer/Counter is a 13-bit counter. The 13-bit counter consists of THx and the five lower bits of TLx. The upper three bits of TLx are ignored. The Timer/Counter is enabled when TRx is set and either GATE is 0 or  $\overline{INTx}$  is 1. Gate = 1 allows the Timer to calculate the pulse width on external input pin  $\overline{INTx}$ . When the 13-bit value moves from 1FFFH to 0000H, the Timer overflow flag TFx is set and an interrupt occurs if enabled. Note that the peripheral clock is  $F_{OSC}/2$  in 12T mode and is  $F_{OSC}$  in 6T mode. See <u>Section 20. "CLOCK</u> <u>SYSTEM" on page 102</u>.

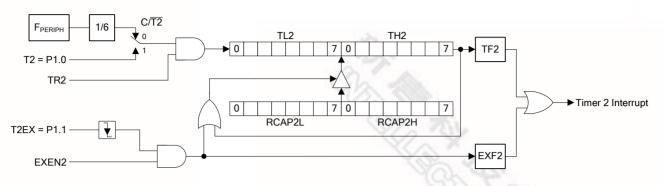

Figure 10-6. Timer/Counter 2 in Auto-reload Mode

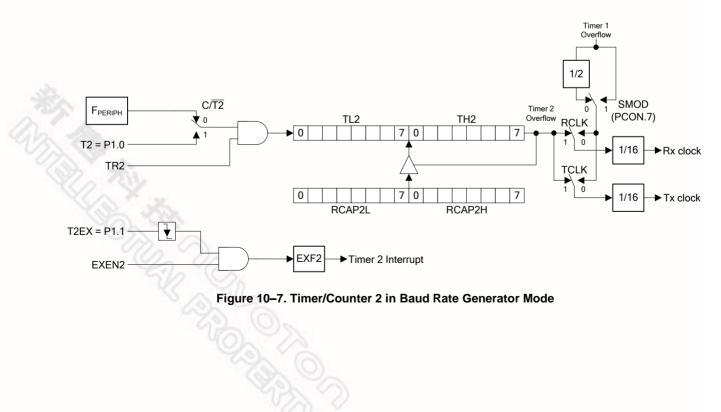

### 10.2.3 Baud Rate Generator Mode

The Timer 2 can generate the baud rate for UART in its Mode 1 and 3. The baud rate generator mode is enabled by setting either the RCLK or TCLK bits in T2CON register. While in the baud rate generator mode, Timer/Counter 2 is a 16 bit counter with auto-reload when the count rolls over from FFFFH. However, rolling over is used to generate the shift clock for UART data rather than to set the TF2 bit. If EXEN2 bit is set, then a negative transition of the T2EX pin will set EXF2 bit in the T2CON register and cause an interrupt request. It simply provides a external interrupt. Note that TCLK and RCLK are selected individually, the serial port transmit rate can be different from the receive rate. For example the transmit clock can be generated from Timer 2 by setting TCLK and the receive clock from Timer 1 by clearing RCLK.

- 44 -

| Bit | Name | Description                                                                                                                                               |

|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5   | PDTF | <b>Power Down waking-up timer Interrupt Flag.</b><br>This bit will be set via hardware when PDT counter overflows. This bit must be cleared via software. |

| 4:3 | -    | Reserved.                                                                                                                                                 |

| 2   | PPS2 | Power Down waking-up timer clock pre-scalar select.                                                                                                       |

| 1   | PPS1 | These bits determine the scale of the clock divider for PDT counter. The scale is from 1/1 through 1/1024. See Table 12–1.                                |

| 0   | PPS0 |                                                                                                                                                           |

The Power Down waking-up time-out interval is determined by the formula  $\frac{1}{F_{LOSC} \times clock \, dividers calar} \times 64$

where F<sub>ILRC</sub> is the frequency of internal 10kHz RC. The following table shows an example of the Power Down waking-up time-out interval under different pre-scalars.

| PPS2 | PPS1 | PPS0 | Clock Divider<br>Scale | Typical Power Down Waking-up<br>Time-out Interval (F <sub>ILRC</sub> ~= 10kHz) |

|------|------|------|------------------------|--------------------------------------------------------------------------------|

| 0    | 0    | 0    | 1/1                    | 6.40ms                                                                         |

| 0    | 0    | 1    | 1/4                    | 25.60ms                                                                        |

| 0    | 1    | 0    | 1/8                    | 51.20ms                                                                        |

| 0    | 1    | 1    | 1/32                   | 204.80ms                                                                       |

| 1    | 0    | 0    | 1/64                   | 409.60ms                                                                       |

| 1    | 0    | 1    | 1/256                  | 1.638s                                                                         |

| 1    | 1    | 0    | 1/512                  | 3.277s                                                                         |

| 1    | 1    | 1    | 1/1024                 | 6.554s                                                                         |

Table 12–1. Power Down Waking-up Timer-Out Interval under different pre-scalars

### 12.2 Applications of Power Down Waking-up Timer

The main application of the Power Down waking-up timer is a simple timer. The PDTF flag will be set while the Power Down waking-up timer completes the selected time interval. The software polls the PDTF flag to detect a time-out and the PDCLR allows software to restart the timer. The Power Down waking-up timer can also be used as a very long timer. Every time the time-out occurs, an interrupt will occur if the individual interrupt EPDT (EIE.1) and global interrupt enable EA is set.

In some application of low power consumption, the CPU usually stays in Idle mode when nothing needs to be served to save power consumption. After a while the CPU will be woken up to check if anything needs to be served at an interval of programmed period implemented by Timer 0, 1 or 2. However, the current consumption

| Name   | Description                                                      |  |  |  |  |

|--------|------------------------------------------------------------------|--|--|--|--|

| PWM0EN | PWM0 enable.                                                     |  |  |  |  |

|        | 0 = PWM0 is disabled and stops.<br>1 = PWM0 is enabled and runs. |  |  |  |  |

|        |                                                                  |  |  |  |  |

#### PWMCON1 – PWM Control 1

| 7 | 6 | 5 | 4 | 3   | 2      | 1 | 0      |  |

|---|---|---|---|-----|--------|---|--------|--|

| - | - | - | - |     | PWM4OE | - | PWM4EN |  |

| - | - | - | - | - 7 | r/w    | - | r/w    |  |

|   |   |   |   |     |        |   |        |  |

Address: CEH

reset value: 0000 0000b

| Bit | Name   | Description                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|--------|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:3 | -      | Reserved.                                                                                                              | S.M.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2   | PWM4OE | <b>PWM4 output enable.</b><br>0 = P1.7 serves as general purpose I/O.<br>1 = P1.7 serves as output pin of PWM4 signal. | NON CON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1   | -      | Reserved.                                                                                                              | 2.97 (62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 0   | PWM4EN | <b>PWM0 enable.</b><br>0 = PWM4 is disabled and stops.<br>1 = PWM4 is enabled and runs.                                | - Alexandress - Alexandres |

#### **PWMP – PWM Period**

| 7         | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-----------|---|---|---|---|---|---|---|--|

| PWMP[7:0] |   |   |   |   |   |   |   |  |

| r/w       |   |   |   |   |   |   |   |  |

Address: D9H

reset value: 0000 0000b

| Bit | Name      | Description                                                                                  |

|-----|-----------|----------------------------------------------------------------------------------------------|

| 7:0 | PWMP[7:0] | <b>PWM period.</b><br>This byte controls the period of the PWM output of PWM0~PWM4 channels. |

#### PWM0 – PWM0 Duty

| 7         | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-----------|---|---|---|---|---|---|---|--|--|

| PWM0[7:0] |   |   |   |   |   |   |   |  |  |

| r/w       |   |   |   |   |   |   |   |  |  |

|           |   |   |   |   |   |   |   |  |  |

Address: DAH

reset value: 0000 0000b

| Bit | Name      | Description                                                          |

|-----|-----------|----------------------------------------------------------------------|

| 7:0 | PWM0[7:0] | <b>PWM0 duty.</b><br>This byte controls the duty of the PWM0 output. |

|     | R ~       | m.                                                                   |

|     |           |                                                                      |

|     |           |                                                                      |

|     |           |                                                                      |

|     |           |                                                                      |

### CHPCON – Chip Control (TA protected)

| 7                                                                                           | 6    | 5     | 4      | 3   | 2   | 1   | 0     |

|---------------------------------------------------------------------------------------------|------|-------|--------|-----|-----|-----|-------|

| SWRST                                                                                       | ISPF | LDUEN | XRAMEN | 7EA | -   | BS  | ISPEN |

| w                                                                                           | r/w  | r/w   | r/w    | n   | - 0 | r/w | r/w   |

| Address: 9EH reset value: see Table 6–2 N78E059A/N78E055A SER Descriptions and Reset Values |      |       |        |     |     |     |       |

Address: 9FH

Jescriptions and Reset values -2. IN/O :039A/11/00

| Bit | Name  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6   | ISPF  | <ul> <li>ISP fault flag.</li> <li>The hardware will set this bit when any of the following condition is met: <ol> <li>The accessing area is illegal, such as,</li> <li>Erasing or programming APROM itself when APROM code runs.</li> <li>Erasing or programming LDROM when APROM code runs but LDUEN is 0.</li> <li>Erasing, programming, or reading CONFIG bytes when APROM code runs.</li> <li>Erasing or programming LDROM itself when LDROM code runs.</li> <li>Erasing or programming LDROM itself when LDROM code runs.</li> <li>Erasing or programming LDROM itself when LDROM code runs.</li> <li>Erasing or programming LDROM itself when LDROM code runs.</li> <li>Erasing or programming LDROM itself when LDROM code runs.</li> <li>Erasing or programming LDROM itself when LDROM code runs.</li> <li>Erasing or programming LDROM itself when LDROM code runs.</li> </ol> </li> <li>Erasing or programming LDROM itself when LDROM code runs.</li> <li>Erasing or programming LDROM itself when LDROM code runs.</li> <li>Erasing or programming LDROM itself when LDROM code runs.</li> <li>Erasing or programming runs from internal Program Memory into external one.</li> <li>This bit should be cleared via software.</li> </ul> |

| 5   | LDUEN | <ul> <li>Updating LDROM enable.</li> <li>0 = The LDROM is inhibited to be erased or programmed when APROM code runs. LDROM remains read-only.</li> <li>1 = The LDROM is allowed to be fully accessed when APROM code runs.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0   | ISPEN | <ul> <li>ISP enable.</li> <li>0 = Enable ISP function.</li> <li>1 = Disable ISP function.</li> <li>To enable ISP function will start the internal 22.1184MHz RC oscillator for timing control. To clear ISPEN should always be the last instruction after ISP operation in order to stop internal RC for reducing power consumption.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

#### **ISPCN – ISP Control**

| 7       | 6       | 5    | 4    | 3       | 2       | 1       | 0       |

|---------|---------|------|------|---------|---------|---------|---------|

| ISPA.17 | ISPA.16 | FOEN | FCEN | FCTRL.3 | FCTRL.2 | FCTRL.1 | FCTRL.0 |

| r/w     | r/w     | r/w  | r/w  | r/w     | r/w     | r/w     | r/w     |

Address: AFH

reset value: 0000 0000b

| 7:6       ISPA[17:16]       ISP control.         5       FOEN       This byte is for ISP controlling command to decide ISP destinations and tions. For details, see Table 18–1. ISP Modes and Command Codes. |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5 FOEN tions. For details, see <u>Table 18–1. ISP Modes and Command Codes</u> .                                                                                                                              |

|                                                                                                                                                                                                              |

| 4 FCEN                                                                                                                                                                                                       |

| 3:0 FCTRL[3:0]                                                                                                                                                                                               |

#### CONFIG2

| 7      | 6     | 5     | 4      | 3    | 2   | 1 | 0 |

|--------|-------|-------|--------|------|-----|---|---|

| CBODEN | CBOV1 | CBOV0 | CBORST |      | -   | - | - |

| r/w    | r/w   | r/w   | r/w    | nº a | 9 - | - | - |

|        |       |       |        |      |     |   |   |

unprogrammed value: 1111 1111b

| Bit | Name   | Description                                                                                                                                                                                                                                                |

|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ЫІ  | Name   | Description                                                                                                                                                                                                                                                |

| 7   | CBODEN | CONFIG Brown-out detect enable.<br>1 = Enable Brown-out detection.<br>0 = Disable Brown-out detection.                                                                                                                                                     |

| 6   | CBOV1  | CONFIG Brown-out voltage select.                                                                                                                                                                                                                           |

| 5   | CBOV0  | These two bits select one of four Brown-out voltage level.         CBOV1       CBOV0       Brown-out Voltage         1       1       2.2V         1       0       2.7V         0       1       3.8V         0       0       4.5V                           |

| 4   | CBORST | <b>CONFIG Brown-out reset enable.</b><br>This bit decides if a Brown-out reset is caused after a Brown-out event.<br>1 = Enable Brown-out reset when $V_{DD}$ drops below $V_{BOD}$ .<br>0 = Disable Brown-out reset when $V_{DD}$ drops below $V_{BOD}$ . |

#### PMC – Power Monitoring Control (TA protected)

| 7                    | 6 | 5 | 4                    | 3   | 2     | 1 | 0   |

|----------------------|---|---|----------------------|-----|-------|---|-----|

| BODEN <sup>[1]</sup> | - | - | BORST <sup>[1]</sup> | BOF | LPBOD | - | BOS |

| r/w                  | - | - | r/w                  | r/w | r/w   | - | r   |

Address: ACH reset value: see Table 6–2. N78E059A/N78E055A SFR Descriptions and Reset Values

| Bit | Name  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | BODEN | Brown-out detect enable.<br>0 = Disable Brown-out detection.<br>1 = Enable Brown-out detection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6:5 | -     | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4   | BORST | <b>Brown-out reset enable.</b><br>This bit decides if a Brown-out reset is caused after a Brown-out event.<br>$0 = D$ is able Brown-out reset when $V_{DD}$ drops below $V_{BOD}$ .<br>$1 = E$ nable Brown-out reset when $V_{DD}$ drops below $V_{BOD}$ .                                                                                                                                                                                                                                                                                                                                                                        |

| 3   | BOF   | <b>Brown-out flag.</b><br>This flag will be set as a logic 1 via hardware after a $V_{DD}$ dropping below or rising above $V_{BOD}$ event occurs. If both EBOD (EIE.2) and EA (IE.7) are set, a Brown-out interrupt requirement will be generated. This bit must be cleared via software.                                                                                                                                                                                                                                                                                                                                         |

| 3   | LPBOD | <ul> <li>Low power Brown-out detection enable.</li> <li>This bit switches the Brown-out detection into a power saving mode. This bit is only effective while BODEN = 1.</li> <li>0 = Disable Brown-out power saving mode. Brown-out detection operates in normal mode if enabled. The detection is always on.</li> <li>1 = Enable Brown-out power saving mode. Brown-out detection operates in power saving mode if enabled. Enable this bit will switch on internal 10kHz RC to be a timer for about 12.8ms interval of detection. The discrete detection will save much power but the hysteresis feature disappears.</li> </ul> |

#### **CONFIG0**

| 7   | 6 | 5 | 4 | 3    | 2     | 1    | 0 |

|-----|---|---|---|------|-------|------|---|

| CBS | - | - | - | 7-   | MOVCL | LOCK | - |

| r/w | - | - | - | 1- 1 | r/w   | r/w  | - |

unprogrammed value: 1111 1111b

| Bit | Name | Description                                                                                                                                                                                                                                                                                      |

|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | CBS  | <ul> <li>CONFIG boot select.</li> <li>This bit defines from which block MCU boots after all resets except software reset.</li> <li>1 = MCU will boot from APROM after all resets except software reset.</li> <li>0 = MCU will boot from LDROM after all resets except software reset.</li> </ul> |

#### CHPCON – Chip Control (TA protected)

| 7            | 6    | 5               | 4             | 3           | 2            | 1                 | 0            |

|--------------|------|-----------------|---------------|-------------|--------------|-------------------|--------------|

| SWRST        | ISPF | LDUEN           | XRAMEN        | -           | -            | BS <sup>[1]</sup> | ISPEN        |

| w            | r/w  | r/w             | r/w           | -           | -            | r/w               | r/w          |

| Address: 9FH | rese | et value: see T | able 6–2. N78 | BE059A/N78E | 055A SFR Des | scriptions and    | Reset Values |

| Bit | Name | Description                                                                                                                                                          | 3  |

|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1   | BS   | <b>Boot select.</b><br>There are different meanings of writing to or reading from this bit.                                                                          | S. |