# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | AVR                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 23                                                                      |

| Program Memory Size        | 4KB (2K x 16)                                                           |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 256 x 8                                                                 |

| RAM Size                   | 512 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                             |

| Data Converters            | A/D 8x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 32-TQFP                                                                 |

| Supplier Device Package    | 32-TQFP (7x7)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega48a-aur |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| Intr | roduction1                                                                                           |

|------|------------------------------------------------------------------------------------------------------|

| Fea  | ature1                                                                                               |

| 1.   | Description4                                                                                         |

| 2.   | Configuration Summary5                                                                               |

| 3.   | Ordering Information   6     3.1.   ATmega48A   6     3.2.   ATmega88A   7     3.3.   ATmega168A   8 |

| 4.   | Block Diagram9                                                                                       |

| 5.   | Pin Configurations                                                                                   |

| 6.   | I/O Multiplexing                                                                                     |

| 7.   | Resources                                                                                            |

| 8.   | Data Retention                                                                                       |

| 9.   | About Code Examples                                                                                  |

| 10.  | Capacitive Touch Sensing                                                                             |

| 11.  | Packaging Information22                                                                              |

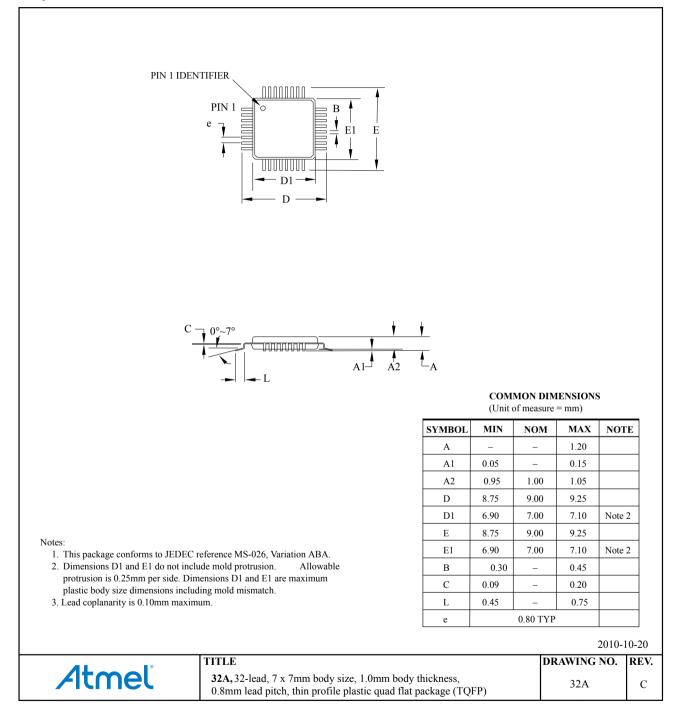

|      | 11.1. 32-pin 32A                                                                                     |

## 2. Configuration Summary

| Features                                        | ATmega48A/88A/168A |

|-------------------------------------------------|--------------------|

| Pin Count                                       | 28/32              |

| Flash (Bytes)                                   | 4K/8K/16K          |

| SRAM (Bytes)                                    | 512/1K/1K          |

| EEPROM (Bytes)                                  | 256/512/512        |

| Interrupt Vector Size (instruction word/vector) | 1/1/2              |

| General Purpose I/O Lines                       | 23                 |

| SPI                                             | 2                  |

| TWI (I <sup>2</sup> C)                          | 1                  |

| USART                                           | 1                  |

| ADC                                             | 10-bit 15kSPS      |

| ADC Channels                                    | 8                  |

| 8-bit Timer/Counters                            | 2                  |

| 16-bit Timer/Counters                           | 1                  |

ATmega88A and ATmega168A support a real Read-While-Write Self-Programming mechanism. There is a separate Boot Loader Section, and the SPM instruction can only execute from there. In ATmega48A, there is no Read-While-Write support and no separate Boot Loader Section. The SPM instruction can execute from the entire Flash.

### 3. Ordering Information

### 3.1. ATmega48A

| Speed [MHz] <sup>(3)</sup> | Power Supply [V] | Ordering Code <sup>(2)</sup>                                                                                                                                                                                                       | Package <sup>(1)</sup>                                                   | Operational Range             |

|----------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-------------------------------|

| 20                         | 1.8 - 5.5        | ATmega48A-AU<br>ATmega48A-AUR <sup>(4)</sup><br>ATmega48A-CCU<br>ATmega48A-CCUR <sup>(4)</sup><br>ATmega48A-MMH <sup>(5)</sup><br>ATmega48A-MMHR <sup>(4)(5)</sup><br>ATmega48A-MU<br>ATmega48A-MUR <sup>(4)</sup><br>ATmega48A-PU | 32A<br>32A<br>32CC1<br>32CC1<br>28M1<br>28M1<br>32M1-A<br>32M1-A<br>28P3 | Industrial<br>(-40°C to 85°C) |

#### Note:

- 1. This device can also be supplied in wafer form. Please contact your local Atmel sales office for detailed ordering information and minimum quantities.

- 2. Pb-free packaging, complies to the European Directive for Restriction of Hazardous Substances (RoHS directive). Also Halide free and fully Green.

- 3. Please refer to Speed Grades for Speed vs. V<sub>CC</sub>

- 4. Tape & Reel.

- 5. NiPdAu Lead Finish.

| Package | Package Type                                                                                      |  |  |  |  |  |  |  |  |

|---------|---------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

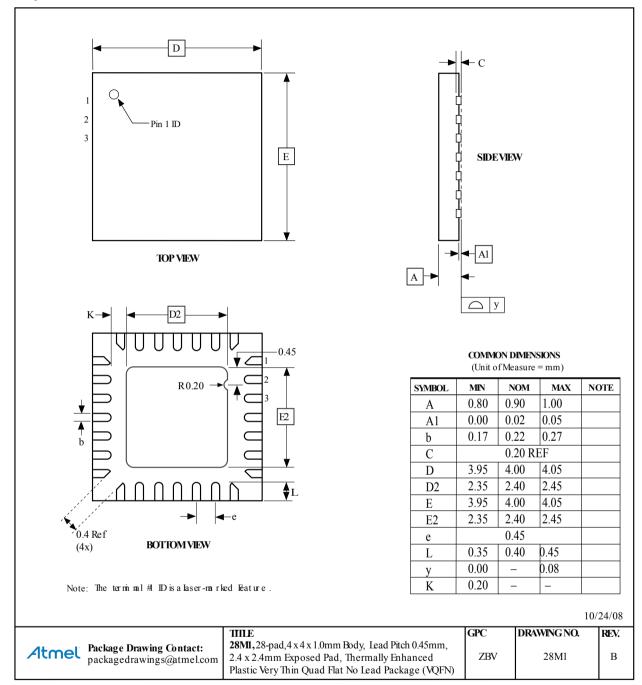

| 28M1    | 28-pad, 4 x 4 x 1.0 body, Lead Pitch 0.45mm Quad Flat No-Lead/Micro Lead Frame Package (QFN/ MLF) |  |  |  |  |  |  |  |  |

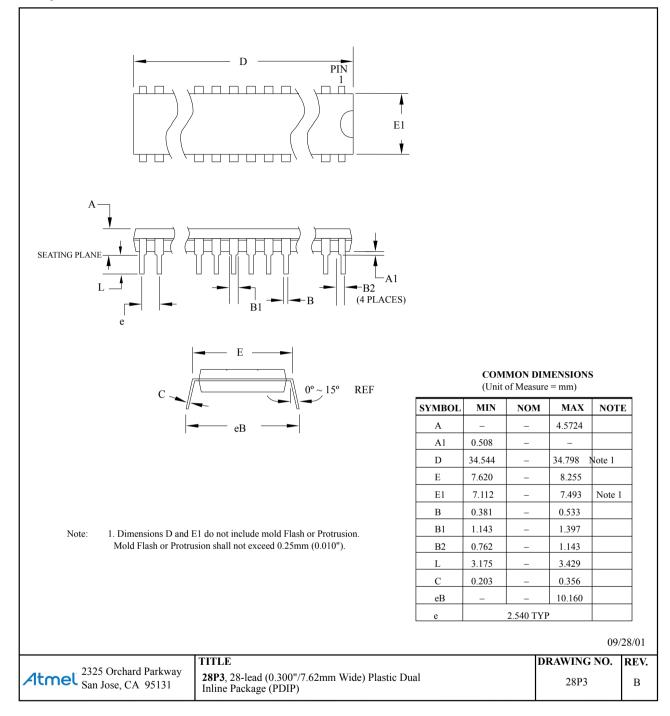

| 28P3    | 28-lead, 0.300" Wide, Plastic Dual Inline Package (PDIP)                                          |  |  |  |  |  |  |  |  |

| 32M1-A  | 32-pad, 5 x 5 x 1.0 body, Lead Pitch 0.50mm Quad Flat No-Lead/Micro Lead Frame Package (QFN/ MLF) |  |  |  |  |  |  |  |  |

| 32A     | 32-lead, Thin (1.0mm) Plastic Quad Flat Package (TQFP)                                            |  |  |  |  |  |  |  |  |

| 32CC1   | 32-ball, 4 x 4 x 0.6mm package, ball pitch 0.5mm, Ultra Thin, Fine-Pitch Ball Grill Array (UFBGA) |  |  |  |  |  |  |  |  |

### 3.2. ATmega88A

| Speed [MHz] <sup>(3)</sup> | Power Supply [V] | Ordering Code <sup>(2)</sup>                                                                                                                                                                                                       | Package <sup>(1)</sup>                                                   | Operational Range             |

|----------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-------------------------------|

| 20                         | 1.8 - 5.5        | ATmega88A-AU<br>ATmega88A-AUR <sup>(4)</sup><br>ATmega88A-CCU<br>ATmega88A-CCUR <sup>(4)</sup><br>ATmega88A-MMH <sup>(5)</sup><br>ATmega88A-MMHR <sup>(4)(5)</sup><br>ATmega88A-MU<br>ATmega88A-MUR <sup>(4)</sup><br>ATmega88A-PU | 32A<br>32A<br>32CC1<br>32CC1<br>28M1<br>28M1<br>32M1-A<br>32M1-A<br>28P3 | Industrial<br>(-40°C to 85°C) |

#### Note:

- 1. This device can also be supplied in wafer form. Please contact your local Atmel sales office for detailed ordering information and minimum quantities.

- 2. Pb-free packaging, complies to the European Directive for Restriction of Hazardous Substances (RoHS directive). Also Halide free and fully Green.

- 3. Please refer to Speed Grades for Speed vs.  $V_{CC}$

- 4. Tape & Reel.

- 5. NiPdAu Lead Finish.

| Package | Package Type                                                                                      |  |  |  |  |  |  |  |  |

|---------|---------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| 28M1    | 28-pad, 4 x 4 x 1.0 body, Lead Pitch 0.45mm Quad Flat No-Lead/Micro Lead Frame Package (QFN/ MLF) |  |  |  |  |  |  |  |  |

| 28P3    | 28-lead, 0.300" Wide, Plastic Dual Inline Package (PDIP)                                          |  |  |  |  |  |  |  |  |

| 32M1-A  | 32-pad, 5 x 5 x 1.0 body, Lead Pitch 0.50mm Quad Flat No-Lead/Micro Lead Frame Package (QFN/ MLF) |  |  |  |  |  |  |  |  |

| 32A     | 32-lead, Thin (1.0mm) Plastic Quad Flat Package (TQFP)                                            |  |  |  |  |  |  |  |  |

| 32CC1   | 32-ball, 4 x 4 x 0.6mm package, ball pitch 0.5mm, Ultra Thin, Fine-Pitch Ball Grill Array (UFBGA) |  |  |  |  |  |  |  |  |

### 3.3. ATmega168A

| Speed [MHz] <sup>(3)</sup> | Power Supply [V] | Ordering Code <sup>(2)</sup>                                                                                                                                                                                                                | Package <sup>(1)</sup>                                                   | Operational Range             |

|----------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-------------------------------|

| 20                         | 1.8 - 5.5        | ATmega168A-AU<br>ATmega168A-AUR <sup>(5)</sup><br>ATmega168A-CCU<br>ATmega168A-CCUR <sup>(5)</sup><br>ATmega168A-MMH <sup>(4)</sup><br>ATmega168A-MMHR <sup>(4)(5)</sup><br>ATmega168A-MU<br>ATmega168A-MUR <sup>(5)</sup><br>ATmega168A-PU | 32A<br>32A<br>32CC1<br>32CC1<br>28M1<br>28M1<br>32M1-A<br>32M1-A<br>28P3 | Industrial<br>(-40°C to 85°C) |

#### Note:

- 1. This device can also be supplied in wafer form. Please contact your local Atmel sales office for detailed ordering information and minimum quantities.

- 2. Pb-free packaging, complies to the European Directive for Restriction of Hazardous Substances (RoHS directive). Also Halide free and fully Green.

- 3. Please refer to Speed Grades for Speed vs.  $V_{CC}$

- 4. Tape & Reel.

- 5. NiPdAu Lead Finish.

| Package | Package Type                                                                                      |  |  |  |  |  |  |  |  |

|---------|---------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| 28M1    | 28-pad, 4 x 4 x 1.0 body, Lead Pitch 0.45mm Quad Flat No-Lead/Micro Lead Frame Package (QFN/ MLF) |  |  |  |  |  |  |  |  |

| 28P3    | 28-lead, 0.300" Wide, Plastic Dual Inline Package (PDIP)                                          |  |  |  |  |  |  |  |  |

| 32M1-A  | 32-pad, 5 x 5 x 1.0 body, Lead Pitch 0.50mm Quad Flat No-Lead/Micro Lead Frame Package (QFN/ MLF) |  |  |  |  |  |  |  |  |

| 32A     | 32-lead, Thin (1.0mm) Plastic Quad Flat Package (TQFP)                                            |  |  |  |  |  |  |  |  |

| 32CC1   | 32-ball, 4 x 4 x 0.6mm package, ball pitch 0.5mm, Ultra Thin, Fine-Pitch Ball Grill Array (UFBGA) |  |  |  |  |  |  |  |  |

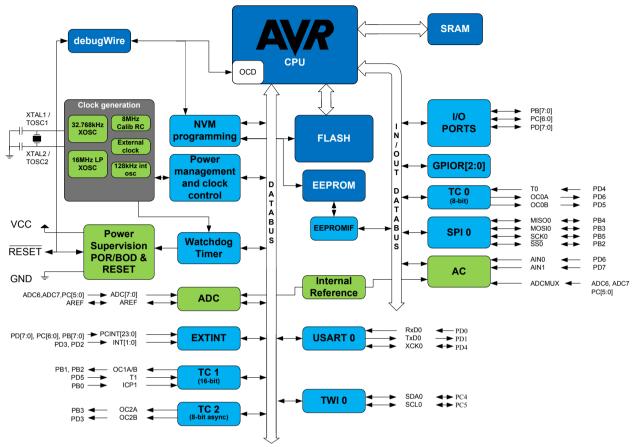

### 4. Block Diagram

Figure 4-1. Block Diagram

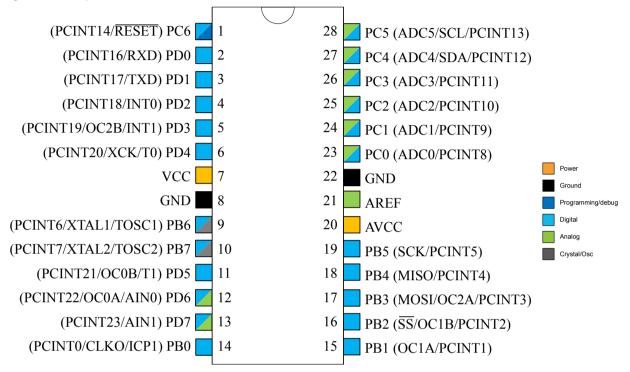

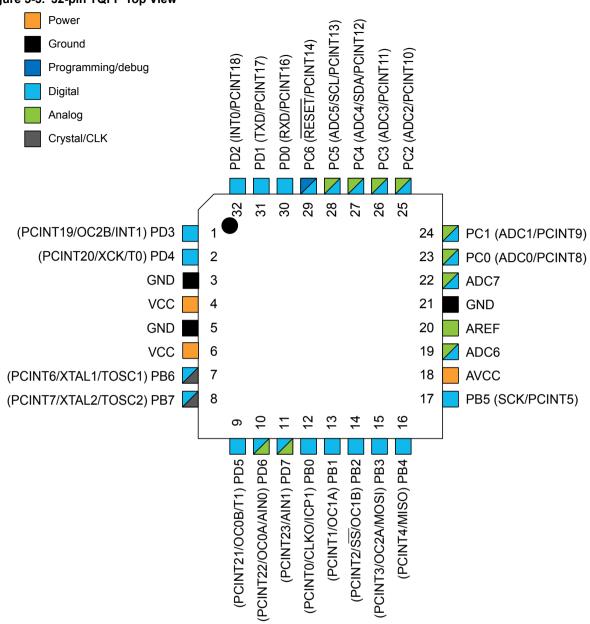

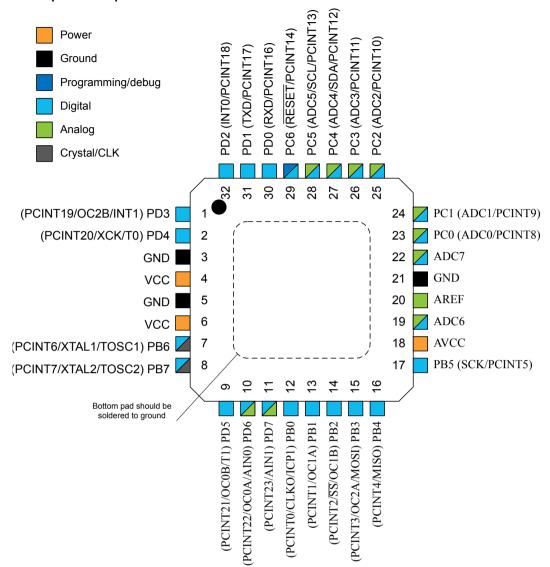

### 5. Pin Configurations

#### 5.1. Pin-out

Figure 5-1. 28-pin PDIP

#### Figure 5-3. 32-pin TQFP Top View

# Atmel

Figure 5-4. 32-pin MLF Top View

#### Table 5-1. 32UFBGA

|   | 1   | 2   | 3   | 4   | 5    | 6    |

|---|-----|-----|-----|-----|------|------|

| А | PD2 | PD1 | PC6 | PC4 | PC2  | PC1  |

| В | PD3 | PD4 | PD0 | PC5 | PC3  | PC0  |

| С | GND | GND | -   | -   | ADC7 | GND  |

| D | VCC | VCC | -   | -   | AREF | ADC6 |

| E | PB6 | PD6 | PB0 | PB2 | AVCC | PB5  |

| F | PB7 | PD5 | PD7 | PB1 | PB3  | PB4  |

### 5.2. Pin Descriptions

#### 5.2.1. VCC

Digital supply voltage.

#### 5.2.2. GND

Ground.

#### 5.2.3. Port B (PB[7:0]) XTAL1/XTAL2/TOSC1/TOSC2

Port B is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port B output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port B pins that are externally pulled low will source current if the pull-up resistors are activated. The Port B pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Depending on the clock selection fuse settings, PB6 can be used as input to the inverting Oscillator amplifier and input to the internal clock operating circuit.

Depending on the clock selection fuse settings, PB7 can be used as output from the inverting Oscillator amplifier.

If the Internal Calibrated RC Oscillator is used as chip clock source, PB[7:6] is used as TOSC[2:1] input for the Asynchronous Timer/Counter2 if the AS2 bit in ASSR is set.

#### 5.2.4. Port C (PC[5:0])

Port C is a 7-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The PC[5:0] output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port C pins that are externally pulled low will source current if the pull-up resistors are activated. The Port C pins are tri-stated when a reset condition becomes active, even if the clock is not running.

#### 5.2.5. PC6/RESET

If the RSTDISBL Fuse is programmed, PC6 is used as an I/O pin. Note that the electrical characteristics of PC6 differ from those of the other pins of Port C.

If the RSTDISBL Fuse is unprogrammed, PC6 is used as a Reset input. A low level on this pin for longer than the minimum pulse length will generate a Reset, even if the clock is not running. Shorter pulses are not guaranteed to generate a Reset.

The various special features of Port C are elaborated in the Alternate Functions of Port C section.

#### 5.2.6. Port D (PD[7:0])

Port D is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port D output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port D pins that are externally pulled low will source current if the pull-up resistors are activated. The Port D pins are tri-stated when a reset condition becomes active, even if the clock is not running.

#### 5.2.7. AV<sub>CC</sub>

$AV_{CC}$  is the supply voltage pin for the A/D Converter, PC[3:0], and PE[3:2]. It should be externally connected to  $V_{CC}$ , even if the ADC is not used. If the ADC is used, it should be connected to  $V_{CC}$  through a low-pass filter. Note that PC[6:4] use digital supply voltage,  $V_{CC}$ .

#### 5.2.8. AREF

AREF is the analog reference pin for the A/D Converter.

### 5.2.9. ADC[7:6] (TQFP and VFQFN Package Only)

In the TQFP and VFQFN package, ADC[7:6] serve as analog inputs to the A/D converter. These pins are powered from the analog supply and serve as 10-bit ADC channels.

### 6. I/O Multiplexing

Each pin is by default controlled by the PORT as a general purpose I/O and alternatively it can be assigned to one of the peripheral functions.

The following table describes the peripheral signals multiplexed to the PORT I/O pins.

| (32-pin<br>32UFBGA)<br>Pin# | (32-pin<br>MLF/<br>TQFP) | (28-pin<br>MLF)<br>Pin# | (28-pin<br>PIPD)<br>Pin# | PAD   | EXTINT | PCINT   | ADC/A<br>C | osc             | T/C #0 | T/C<br>#1 | USART<br>0 | I2C 0 | SPI 0          |

|-----------------------------|--------------------------|-------------------------|--------------------------|-------|--------|---------|------------|-----------------|--------|-----------|------------|-------|----------------|

|                             | Pin#                     |                         |                          |       |        |         |            |                 |        |           |            |       |                |

| B1                          | 1                        | 1                       | 5                        | PD[3] | INT1   | PCINT19 |            |                 | OC2B   |           |            |       |                |

| B2                          | 2                        | 2                       | 6                        | PD[4] |        | PCINT20 |            |                 | Т0     |           | XCK0       |       |                |

| D1                          | 4                        | 3                       | 7                        | VCC   |        |         |            |                 |        |           |            |       |                |

| C1                          | 3                        | 4                       | 8                        | GND   |        |         |            |                 |        |           |            |       |                |

| D2                          | 6                        | -                       | -                        | VCC   |        |         |            |                 |        |           |            |       |                |

| C2                          | 5                        | -                       | -                        | GND   |        |         |            |                 |        |           |            |       |                |

| E1                          | 7                        | 5                       | 9                        | PB[6] |        | PCINT6  |            | XTAL1/<br>TOSC1 |        |           |            |       |                |

| F1                          | 8                        | 6                       | 10                       | PB[7] |        | PCINT7  |            | XTAL2/<br>TOSC2 |        |           |            |       |                |

| F2                          | 9                        | 7                       | 11                       | PD[5] |        | PCINT21 |            |                 | OC0B   | T1        |            |       |                |

| E2                          | 10                       | 8                       | 12                       | PD[6] |        | PCINT22 | AIN0       |                 | OC0A   |           |            |       |                |

| F3                          | 11                       | 9                       | 13                       | PD[7] |        | PCINT23 | AIN1       |                 |        |           |            |       |                |

| E3                          | 12                       | 10                      | 14                       | PB[0] |        | PCINT0  |            | CLKO            | ICP1   |           |            |       |                |

| F4                          | 13                       | 11                      | 15                       | PB[1] |        | PCINT1  |            |                 | OC1A   |           |            |       |                |

| E4                          | 14                       | 12                      | 16                       | PB[2] |        | PCINT2  |            |                 | OC1B   |           |            |       | <del>SS0</del> |

| F5                          | 15                       | 13                      | 17                       | PB[3] |        | PCINT3  |            |                 | OC2A   |           |            |       | MOSI0          |

| F6                          | 16                       | 14                      | 18                       | PB[4] |        | PCINT4  |            |                 |        |           |            |       | MISO0          |

| E6                          | 17                       | 15                      | 19                       | PB[5] |        | PCINT5  |            |                 |        |           |            |       | SCK0           |

| E5                          | 18                       | 16                      | 20                       | AVCC  |        |         |            |                 |        |           |            |       |                |

| D6                          | 19                       | -                       | -                        | ADC6  |        |         | ADC6       |                 |        |           |            |       |                |

| D5                          | 20                       | 17                      | 21                       | AREF  |        |         |            |                 |        |           |            |       |                |

| C6                          | 21                       | 18                      | 22                       | GND   |        |         |            |                 |        |           |            |       |                |

| C5                          | 22                       | -                       | -                        | ADC7  |        |         | ADC7       |                 |        |           |            |       |                |

| B6                          | 23                       | 19                      | 13                       | PC[0] |        | PCINT8  | ADC0       |                 |        |           |            |       |                |

| A6                          | 24                       | 20                      | 24                       | PC[1] |        | PCINT9  | ADC1       |                 |        |           |            |       |                |

| A2                          | 25                       | 21                      | 25                       | PC[2] |        | PCINT10 | ADC2       |                 |        |           |            |       |                |

| B5                          | 26                       | 22                      | 26                       | PC[3] |        | PCINT11 | ADC3       |                 |        |           |            |       |                |

| A4                          | 27                       | 23                      | 27                       | PC[4] |        | PCINT12 | ADC4       |                 |        |           |            | SDA0  |                |

| B4                          | 28                       | 24                      | 28                       | PC[5] |        | PCINT13 | ADC5       |                 |        |           |            | SCL0  |                |

#### Table 6-1. PORT Function Multiplexing

### 7. Resources

A comprehensive set of development tools, application notes, and datasheets are available for download on http://www.atmel.com/avr.

### 8. Data Retention

Reliability Qualification results show that the projected data retention failure rate is much less than 1 PPM over 20 years at 85°C.

### 9. About Code Examples

This documentation contains simple code examples that briefly show how to use various parts of the device. These code examples assume that the part specific header file is included before compilation. Be aware that not all C compiler vendors include bit definitions in the header files and interrupt handling in C is compiler dependent. Confirm with the C compiler documentation for more details.

For I/O Registers located in extended I/O map, "IN", "OUT", "SBIS", "SBIC", "CBI", and "SBI" instructions must be replaced with instructions that allow access to extended I/O. Typically "LDS" and "STS" combined with "SBRS", "SBRC", "SBR", and "CBR".

### 10. Capacitive Touch Sensing

#### 10.1. QTouch Library

The Atmel<sup>®</sup> QTouch<sup>®</sup> Library provides a simple to use solution to realize touch sensitive interfaces on most Atmel AVR<sup>®</sup> microcontrollers. The QTouch Library includes support for the Atmel QTouch and Atmel QMatrix<sup>®</sup> acquisition methods.

Touch sensing can be added to any application by linking the appropriate Atmel QTouch Library for the AVR Microcontroller. This is done by using a simple set of APIs to define the touch channels and sensors, and then calling the touch sensing API's to retrieve the channel information and determine the touch sensor states.

The QTouch Library is FREE and downloadable from the Atmel website at the following location: http:// www.atmel.com/technologies/touch/. For implementation details and other information, refer to the Atmel QTouch Library User Guide - also available for download from the Atmel website.

### 11. Packaging Information

#### 11.1. 32-pin 32A

#### 28-pin 28M1 11.4.

#### 11.5. 28-pin 28P3

# Atmel Enabling Unlimited Possibilities<sup>®</sup>

Atmel Corporation 1600 Te

1600 Technology Drive, San Jose, CA 95110 USA

**T:** (+1)(408) 441.0311

F: (+1)(408) 436.4200

www.atmel.com

f У in 8 🖸 W

I

© 2016 Atmel Corporation. / Rev.: Atmel-42733B-ATmega48A/88A/168A\_Datasheet\_Summary-11/2016

Atmel<sup>®</sup>, Atmel logo and combinations thereof, Enabling Unlimited Possibilities<sup>®</sup>, AVR<sup>®</sup>, and others are registered trademarks or trademarks of Atmel Corporation in U.S. and other countries. Other terms and product names may be trademarks of others.

DISCLAIMER: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and products descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

SAFETY-CRITICAL, MILITARY, AND AUTOMOTIVE APPLICATIONS DISCLAIMER: Atmel products are not designed for and will not be used in connection with any applications where the failure of such products would reasonably be expected to result in significant personal injury or death ("Safety-Critical Applications") without an Atmel officer's specific written consent. Safety-Critical Applications include, without limitation, life support devices and systems, equipment or systems for the operation of nuclear facilities and weapons systems. Atmel products are not designed nor intended for use in military or aerospace applications or environments unless specifically designated by Atmel as military-grade. Atmel products are not designed nor intended for use in automotive applications unless specifically designated by Atmel as military-grade.