Welcome to **E-XFL.COM**

**Understanding Embedded - DSP (Digital Signal Processors)**

Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

# Applications of <u>Embedded - DSP (Digital Signal Processors)</u>

| Details                 |                                                                       |

|-------------------------|-----------------------------------------------------------------------|

| Product Status          | Obsolete                                                              |

| Туре                    | Fixed Point                                                           |

| Interface               | SPI, SSP, UART                                                        |

| Clock Rate              | 500MHz                                                                |

| Non-Volatile Memory     | ROM (1kB)                                                             |

| On-Chip RAM             | 148kB                                                                 |

| Voltage - I/O           | 3.30V                                                                 |

| Voltage - Core          | 1.20V                                                                 |

| Operating Temperature   | -40°C ~ 85°C (TA)                                                     |

| Mounting Type           | Surface Mount                                                         |

| Package / Case          | 160-LFBGA, CSPBGA                                                     |

| Supplier Device Package | 160-CSPBGA (12x12)                                                    |

| Purchase URL            | https://www.e-xfl.com/product-detail/analog-devices/adsp-bf533sbbc500 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **GENERAL DESCRIPTION**

The ADSP-BF531/ADSP-BF532/ADSP-BF533 processors are members of the Blackfin® family of products, incorporating the Analog Devices, Inc./Intel Micro Signal Architecture (MSA). Blackfin processors combine a dual-MAC state-of-the-art signal processing engine, the advantages of a clean, orthogonal RISC-like microprocessor instruction set, and single instruction, multiple data (SIMD) multimedia capabilities into a single instruction set architecture.

The ADSP-BF531/ADSP-BF532/ADSP-BF533 processors are completely code and pin-compatible, differing only with respect to their performance and on-chip memory. Specific performance and memory configurations are shown in Table 1.

**Table 1. Processor Comparison**

| Fe                   | atures                      | ADSP-BF531 | ADSP-BF532 | ADSP-BF533 |

|----------------------|-----------------------------|------------|------------|------------|

| SP                   | ORTs                        | 2          | 2          | 2          |

| UA                   | RT                          | 1          | 1          | 1          |

| SP                   | <u> </u>                    | 1          | 1          | 1          |

| GP                   | Timers                      | 3          | 3          | 3          |

| Wa                   | tchdog Timers               | 1          | 1          | 1          |

| RT                   | С                           | 1          | 1          | 1          |

| Pa                   | rallel Peripheral Interface | 1          | 1          | 1          |

| GP                   | lOs                         | 16         | 16         | 16         |

| ion                  | L1 Instruction SRAM/Cache   | 16K bytes  | 16K bytes  | 16K bytes  |

| urat                 | L1 Instruction SRAM         | 16K bytes  | 32K bytes  | 64K bytes  |

| ıfigi                | L1 Data SRAM/Cache          | 16K bytes  | 32K bytes  | 32K bytes  |

| Ö                    | L1 Data SRAM                |            |            | 32K bytes  |

| ory                  | L1 Scratchpad               | 4K bytes   | 4K bytes   | 4K bytes   |

| Memory Configuration | L3 Boot ROM                 | 1K bytes   | 1K bytes   | 1K bytes   |

| Ma                   | ximum Speed Grade           | 400 MHz    | 400 MHz    | 600 MHz    |

| Pa                   | ckage Options:              |            |            |            |

|                      | P_BGA                       | 160-Ball   | 160-Ball   | 160-Ball   |

|                      | stic BGA                    | 169-Ball   | 169-Ball   | 169-Ball   |

| LQ                   | FP                          | 176-Lead   | 176-Lead   | 176-Lead   |

By integrating a rich set of industry-leading system peripherals and memory, Blackfin processors are the platform of choice for next generation applications that require RISC-like programmability, multimedia support, and leading-edge signal processing in one integrated package.

### PORTABLE LOW POWER ARCHITECTURE

Blackfin processors provide world-class power management and performance. Blackfin processors are designed in a low power and low voltage design methodology and feature dynamic power management—the ability to vary both the voltage and frequency of operation to significantly lower overall power consumption. Varying the voltage and frequency can result in a substantial reduction in power consumption, compared with just varying the frequency of operation. This translates into longer battery life for portable appliances.

### **SYSTEM INTEGRATION**

The ADSP-BF531/ADSP-BF532/ADSP-BF533 processors are highly integrated system-on-a-chip solutions for the next generation of digital communication and consumer multimedia applications. By combining industry-standard interfaces with a high performance signal processing core, users can develop cost-effective solutions quickly without the need for costly external components. The system peripherals include a UART port, an SPI port, two serial ports (SPORTs), four general-purpose timers (three with PWM capability), a real-time clock, a watchdog timer, and a parallel peripheral interface.

#### PROCESSOR PERIPHERALS

The ADSP-BF531/ADSP-BF532/ADSP-BF533 processors contain a rich set of peripherals connected to the core via several high bandwidth buses, providing flexibility in system configuration as well as excellent overall system performance (see the functional block diagram in Figure 1 on Page 1). The generalpurpose peripherals include functions such as UART, timers with PWM (pulse-width modulation) and pulse measurement capability, general-purpose I/O pins, a real-time clock, and a watchdog timer. This set of functions satisfies a wide variety of typical system support needs and is augmented by the system expansion capabilities of the part. In addition to these generalpurpose peripherals, the processors contain high speed serial and parallel ports for interfacing to a variety of audio, video, and modem codec functions; an interrupt controller for flexible management of interrupts from the on-chip peripherals or external sources; and power management control functions to tailor the performance and power characteristics of the processor and system to many application scenarios.

All of the peripherals, except for general-purpose I/O, real-time clock, and timers, are supported by a flexible DMA structure. There is also a separate memory DMA channel dedicated to data transfers between the processor's various memory spaces, including external SDRAM and asynchronous memory. Multiple on-chip buses running at up to 133 MHz provide enough bandwidth to keep the processor core running along with activity on all of the on-chip and external peripherals.

The processors include an on-chip voltage regulator in support of the processor's dynamic power management capability. The voltage regulator provides a range of core voltage levels from  $V_{\rm DDEXT}.$  The voltage regulator can be bypassed at the user's discretion.

- Interrupts Each transmit and receive port generates an interrupt upon completing the transfer of a data-word or after transferring an entire data buffer or buffers through DMA.

- Multichannel capability Each SPORT supports 128 channels out of a 1,024-channel window and is compatible with the H.100, H.110, MVIP-90, and HMVIP standards.

An additional 250 mV of SPORT input hysteresis can be enabled by setting Bit 15 of the PLL\_CTL register. When this bit is set, all SPORT input pins have the increased hysteresis.

## **SERIAL PERIPHERAL INTERFACE (SPI) PORT**

The ADSP-BF531/ADSP-BF532/ADSP-BF533 processors have an SPI-compatible port that enables the processor to communicate with multiple SPI-compatible devices.

The SPI interface uses three pins for transferring data: two data pins (master output-slave input, MOSI, and master input-slave output, MISO) and a clock pin (serial clock, SCK). An SPI chip select input pin (\$\overline{SPISS}\$) lets other SPI devices select the processor, and seven SPI chip select output pins (\$\overline{SPISEL7}-1\$) let the processor select other SPI devices. The SPI select pins are reconfigured general-purpose I/O pins. Using these pins, the SPI port provides a full-duplex, synchronous serial interface which supports both master/slave modes and multimaster environments.

The baud rate and clock phase/polarities for the SPI port are programmable, and it has an integrated DMA controller, configurable to support transmit or receive data streams. The SPI DMA controller can only service unidirectional accesses at any given time.

The SPI port clock rate is calculated as:

$$SPI \ Clock \ Rate = \frac{f_{SCLK}}{2 \times SPI \ BAUD}$$

where the 16-bit SPI\_BAUD register contains a value of 2 to 65,535.

During transfers, the SPI port simultaneously transmits and receives by serially shifting data in and out on its two serial data lines. The serial clock line synchronizes the shifting and sampling of data on the two serial data lines.

### **UART PORT**

The ADSP-BF531/ADSP-BF532/ADSP-BF533 processors provide a full-duplex universal asynchronous receiver/transmitter (UART) port, which is fully compatible with PC-standard UARTs. The UART port provides a simplified UART interface to other peripherals or hosts, supporting full-duplex, DMA-supported, asynchronous transfers of serial data. The UART port includes support for 5 data bits to 8 data bits, 1 stop bit or 2 stop bits, and none, even, or odd parity. The UART port supports two modes of operation:

• PIO (programmed I/O) – The processor sends or receives data by writing or reading I/O-mapped UART registers. The data is double-buffered on both transmit and receive.

• DMA (direct memory access) – The DMA controller transfers both transmit and receive data. This reduces the number and frequency of interrupts required to transfer data to and from memory. The UART has two dedicated DMA channels, one for transmit and one for receive. These DMA channels have lower default priority than most DMA channels because of their relatively low service rates.

The baud rate, serial data format, error code generation and status, and interrupts for the UART port are programmable.

The UART programmable features include:

- Supporting bit rates ranging from ( $f_{SCLK}/1,048,576$ ) bits per second to ( $f_{SCLK}/16$ ) bits per second.

- Supporting data formats from seven bits to 12 bits per frame

- Both transmit and receive operations can be configured to generate maskable interrupts to the processor.

The UART port's clock rate is calculated as:

$$UART\ Clock\ Rate = \frac{f_{SCLK}}{16 \times UART\_Divisor}$$

where the 16-bit UART\_Divisor comes from the UART\_DLH register (most significant 8 bits) and UART\_DLL register (least significant 8 bits).

In conjunction with the general-purpose timer functions, autobaud detection is supported.

The capabilities of the UART are further extended with support for the Infrared Data Association (IrDA®) serial infrared physical layer link specification (SIR) protocol.

### **GENERAL-PURPOSE I/O PORT F**

The ADSP-BF531/ADSP-BF532/ADSP-BF533 processors have 16 bidirectional, general-purpose I/O pins on Port F (PF15–0). Each general-purpose I/O pin can be individually controlled by manipulation of the GPIO control, status and interrupt registers:

- GPIO direction control register Specifies the direction of each individual PFx pin as input or output.

- GPIO control and status registers The processor employs a "write one to modify" mechanism that allows any combination of individual GPIO pins to be modified in a single instruction, without affecting the level of any other GPIO pins. Four control registers are provided. One register is written in order to set GPIO pin values, one register is written in order to clear GPIO pin values, and one register is written in order to specify GPIO pin values. Reading the GPIO status register allows software to interrogate the sense of the GPIO pin.

- GPIO interrupt mask registers The two GPIO interrupt mask registers allow each individual PFx pin to function as an interrupt to the processor. Similar to the two GPIO control registers that are used to set and clear individual GPIO pin values, one GPIO interrupt mask register sets bits to enable interrupt function, and the other GPIO interrupt mask register clears bits to disable interrupt function.

### **Active Operating Mode—Moderate Power Savings**

In the active mode, the PLL is enabled but bypassed. Because the PLL is bypassed, the processor's core clock (CCLK) and system clock (SCLK) run at the input clock (CLKIN) frequency. DMA access is available to appropriately configured L1 memories.

In the active mode, it is possible to disable the PLL through the PLL control register (PLL\_CTL). If disabled, the PLL must be re-enabled before it can transition to the full-on or sleep modes.

**Table 4. Power Settings**

| Mode          | PLL                  | PLL<br>Bypassed | Core<br>Clock<br>(CCLK) | System<br>Clock<br>(SCLK) | Internal<br>Power<br>(V <sub>DDINT</sub> ) |

|---------------|----------------------|-----------------|-------------------------|---------------------------|--------------------------------------------|

| Full On       | Enabled              | No              | Enabled                 | Enabled                   | On                                         |

| Active        | Enabled/<br>Disabled | Yes             | Enabled                 | Enabled                   | On                                         |

| Sleep         | Enabled              | _               | Disabled                | Enabled                   | On                                         |

| Deep<br>Sleep | Disabled             | _               | Disabled                | Disabled                  | On                                         |

| Hibernate     | Disabled             | _               | Disabled                | Disabled                  | Off                                        |

## Sleep Operating Mode—High Dynamic Power Savings

The sleep mode reduces dynamic power dissipation by disabling the clock to the processor core (CCLK). The PLL and system clock (SCLK), however, continue to operate in this mode. Typically an external event or RTC activity will wake up the processor. When in the sleep mode, assertion of wakeup causes the processor to sense the value of the BYPASS bit in the PLL control register (PLL\_CTL). If BYPASS is disabled, the processor will transition to the full-on mode. If BYPASS is enabled, the processor will transition to the active mode.

When in the sleep mode, system DMA access to L1 memory is not supported.

# Deep Sleep Operating Mode—Maximum Dynamic Power Savings

The deep sleep mode maximizes dynamic power savings by disabling the clocks to the processor core (CCLK) and to all synchronous peripherals (SCLK). Asynchronous peripherals, such as the RTC, may still be running but cannot access internal resources or external memory. This powered-down mode can only be exited by assertion of the reset interrupt (RESET) or by an asynchronous interrupt generated by the RTC. When in deep sleep mode, an RTC asynchronous interrupt causes the processor to transition to the active mode. Assertion of RESET while in deep sleep mode causes the processor to transition to the full-on mode.

## **Hibernate State—Maximum Static Power Savings**

The hibernate state maximizes static power savings by disabling the voltage and clocks to the processor core (CCLK) and to all the synchronous peripherals (SCLK). The internal voltage regulator for the processor can be shut off by writing b#00 to the FREQ bits of the VR\_CTL register. In addition to disabling the clocks, this sets the internal power supply voltage ( $V_{\rm DDINT}$ ) to

0 V to provide the lowest static power dissipation. Any critical information stored internally (memory contents, register contents, etc.) must be written to a nonvolatile storage device prior to removing power if the processor state is to be preserved. Since  $V_{\rm DDEXT}$  is still supplied in this mode, all of the external pins three-state, unless otherwise specified. This allows other devices that may be connected to the processor to still have power applied without drawing unwanted current. The internal supply regulator can be woken up either by a real-time clock wakeup or by asserting the  $\overline{\rm RESET}$  pin.

#### **Power Savings**

As shown in Table 5, the processors support three different power domains. The use of multiple power domains maximizes flexibility, while maintaining compliance with industry standards and conventions. By isolating the internal logic of the processor into its own power domain, separate from the RTC and other I/O, the processor can take advantage of dynamic power management without affecting the RTC or other I/O devices. There are no sequencing requirements for the various power domains.

Table 5. Power Domains

| Power Domain                       | V <sub>DD</sub> Range |

|------------------------------------|-----------------------|

| All internal logic, except RTC     | $V_{DDINT}$           |

| RTC internal logic and crystal I/O | $V_{\text{DDRTC}}$    |

| All other I/O                      | $V_{DDEXT}$           |

The power dissipated by a processor is largely a function of the clock frequency of the processor and the square of the operating voltage. For example, reducing the clock frequency by 25% results in a 25% reduction in dynamic power dissipation, while reducing the voltage by 25% reduces dynamic power dissipation by more than 40%. Further, these power savings are additive, in that if the clock frequency and supply voltage are both reduced, the power savings can be dramatic.

The dynamic power management feature of the processor allows both the processor's input voltage ( $V_{DDINT}$ ) and clock frequency ( $f_{CCLK}$ ) to be dynamically controlled.

The savings in power dissipation can be modeled using the power savings factor and % power savings calculations.

The power savings factor is calculated as:

power savings factor

$$= \frac{f_{\text{CCLKRED}}}{f_{\text{CCLKNOM}}} \times \left(\frac{V_{\text{DDINTRED}}}{V_{\text{DDINTNOM}}}\right)^2 \times \left(\frac{t_{\text{RED}}}{t_{\text{NOM}}}\right)$$

where the variables in the equation are:

$f_{CCLKNOM}$  is the nominal core clock frequency  $f_{CCLKRED}$  is the reduced core clock frequency  $V_{DDINTNOM}$  is the nominal internal supply voltage  $V_{DDINTRED}$  is the reduced internal supply voltage

$t_{NOM}$  is the duration running at  $f_{CCLKNOM}$   $t_{RED}$  is the duration running at  $f_{CCLKRED}$  The percent power savings is calculated as:

% power savings =  $(1 - power savings factor) \times 100\%$

#### **VOLTAGE REGULATION**

The Blackfin processor provides an on-chip voltage regulator that can generate appropriate  $V_{\rm DDINT}$  voltage levels from the  $V_{\rm DDEXT}$  supply. See Operating Conditions on Page 20 for regulator tolerances and acceptable  $V_{\rm DDEXT}$  ranges for specific models.

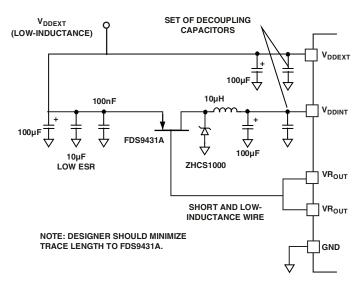

Figure 7 shows the typical external components required to complete the power management system. The regulator controls the internal logic voltage levels and is programmable with the voltage regulator control register (VR\_CTL) in increments of 50 mV. To reduce standby power consumption, the internal voltage regulator can be programmed to remove power to the processor core while keeping I/O power (V\_DDEXT) supplied. While in the hibernate state, I/O power is still being applied, eliminating the need for external buffers. The voltage regulator can be activated from this power-down state either through an RTC wakeup or by asserting  $\overline{\text{RESET}}$ , both of which initiate a boot sequence. The regulator can also be disabled and bypassed at the user's discretion.

Figure 7. Voltage Regulator Circuit

## **Voltage Regulator Layout Guidelines**

Regulator external component placement, board routing, and bypass capacitors all have a significant effect on noise injected into the other analog circuits on-chip. The VROUT1-0 traces and voltage regulator external components should be considered as noise sources when doing board layout and should not be routed or placed near sensitive circuits or components on the board. All internal and I/O power supplies should be well bypassed with bypass capacitors placed as close to the processors as possible.

For further details on the on-chip voltage regulator and related board design guidelines, see the *Switching Regulator Design Considerations for ADSP-BF533 Blackfin Processors (EE-228)* applications note on the Analog Devices web site (www.analog.com)—use site search on "EE-228".

#### **CLOCK SIGNALS**

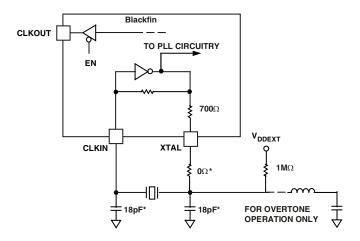

The ADSP-BF531/ADSP-BF532/ADSP-BF533 processors can be clocked by an external crystal, a sine wave input, or a buffered, shaped clock derived from an external clock oscillator.

If an external clock is used, it should be a TTL-compatible signal and must not be halted, changed, or operated below the specified frequency during normal operation. This signal is connected to the processor's CLKIN pin. When an external clock is used, the XTAL pin must be left unconnected.

Alternatively, because the processors include an on-chip oscillator circuit, an external crystal can be used. For fundamental frequency operation, use the circuit shown in Figure 8.

NOTE: VALUES MARKED WITH \* MUST BE CUSTOMIZED DEPENDING ON THE CRYSTAL AND LAYOUT. PLEASE ANALYZE CAREFULLY.

Figure 8. External Crystal Connections

A parallel-resonant, fundamental frequency, microprocessor-grade crystal is connected across the CLKIN and XTAL pins. The on-chip resistance between CLKIN and the XTAL pin is in the 500  $k\Omega$  range. Further parallel resistors are typically not recommended. The two capacitors and the series resistor shown in Figure 8 fine tune the phase and amplitude of the sine frequency. The capacitor and resistor values shown in Figure 8 are typical values only. The capacitor values are dependent upon the crystal manufacturer's load capacitance recommendations and the physical PCB layout. The resistor value depends on the drive level specified by the crystal manufacturer. System designs should verify the customized values based on careful investigation on multiple devices over the allowed temperature range.

A third-overtone crystal can be used at frequencies above 25 MHz. The circuit is then modified to ensure crystal operation only at the third overtone, by adding a tuned inductor circuit as shown in Figure 8.

more bytes until the flag is deasserted. The GPIO pin is chosen by the user and this information is transferred to the Blackfin processor via bits[10:5] of the FLAG header in the LDR image.

For each of the boot modes, a 10-byte header is first read from an external memory device. The header specifies the number of bytes to be transferred and the memory destination address. Multiple memory blocks can be loaded by any boot sequence. Once all blocks are loaded, program execution commences from the start of L1 instruction SRAM.

In addition, Bit 4 of the reset configuration register can be set by application code to bypass the normal boot sequence during a software reset. For this case, the processor jumps directly to the beginning of L1 instruction memory.

#### INSTRUCTION SET DESCRIPTION

The Blackfin processor family assembly language instruction set employs an algebraic syntax designed for ease of coding and readability. The instructions have been specifically tuned to provide a flexible, densely encoded instruction set that compiles to a very small final memory size. The instruction set also provides fully featured multifunction instructions that allow the programmer to use many of the processor core resources in a single instruction. Coupled with many features more often seen on microcontrollers, this instruction set is very efficient when compiling C and C++ source code. In addition, the architecture supports both user (algorithm/application code) and supervisor (O/S kernel, device drivers, debuggers, ISRs) modes of operation, allowing multiple levels of access to core processor resources.

The assembly language, which takes advantage of the processor's unique architecture, offers the following advantages:

- Seamlessly integrated DSP/CPU features are optimized for both 8-bit and 16-bit operations.

- A multi-issue load/store modified Harvard architecture, which supports two 16-bit MAC or four 8-bit ALU + two load/store + two pointer updates per cycle.

- All registers, I/O, and memory are mapped into a unified 4G byte memory space, providing a simplified programming model.

- Microcontroller features, such as arbitrary bit and bit-field manipulation, insertion, and extraction; integer operations on 8-, 16-, and 32-bit data types; and separate user and supervisor stack pointers.

- Code density enhancements, which include intermixing of 16-bit and 32-bit instructions (no mode switching, no code segregation). Frequently used instructions are encoded in 16 bits.

### **DEVELOPMENT TOOLS**

Analog Devices supports its processors with a complete line of software and hardware development tools, including integrated development environments (which include CrossCore® Embedded Studio and/or VisualDSP++®), evaluation products, emulators, and a wide variety of software add-ins.

### Integrated Development Environments (IDEs)

For C/C++ software writing and editing, code generation, and debug support, Analog Devices offers two IDEs.

The newest IDE, CrossCore Embedded Studio, is based on the Eclipse™ framework. Supporting most Analog Devices processor families, it is the IDE of choice for future processors, including multicore devices. CrossCore Embedded Studio seamlessly integrates available software add-ins to support real time operating systems, file systems, TCP/IP stacks, USB stacks, algorithmic software modules, and evaluation hardware board support packages. For more information visit www.analog.com/cces.

The other Analog Devices IDE, VisualDSP++, supports processor families introduced prior to the release of CrossCore Embedded Studio. This IDE includes the Analog Devices VDK real time operating system and an open source TCP/IP stack. For more information visit www.analog.com/visualdsp. Note that VisualDSP++ will not support future Analog Devices processors.

### **EZ-KIT Lite Evaluation Board**

For processor evaluation, Analog Devices provides wide range of EZ-KIT Lite<sup>®</sup> evaluation boards. Including the processor and key peripherals, the evaluation board also supports on-chip emulation capabilities and other evaluation and development features. Also available are various EZ-Extenders<sup>®</sup>, which are daughter cards delivering additional specialized functionality, including audio and video processing. For more information visit www.analog.com and search on "ezkit" or "ezextender".

#### **EZ-KIT Lite Evaluation Kits**

For a cost-effective way to learn more about developing with Analog Devices processors, Analog Devices offer a range of EZ-KIT Lite evaluation kits. Each evaluation kit includes an EZ-KIT Lite evaluation board, directions for downloading an evaluation version of the available IDE(s), a USB cable, and a power supply. The USB controller on the EZ-KIT Lite board connects to the USB port of the user's PC, enabling the chosen IDE evaluation suite to emulate the on-board processor in-circuit. This permits the customer to download, execute, and debug programs for the EZ-KIT Lite system. It also supports in-circuit programming of the on-board Flash device to store user-specific boot code, enabling standalone operation. With the full version of Cross-Core Embedded Studio or VisualDSP++ installed (sold separately), engineers can develop software for supported EZ-KITs or any custom system utilizing supported Analog Devices processors.

### Software Add-Ins for CrossCore Embedded Studio

Analog Devices offers software add-ins which seamlessly integrate with CrossCore Embedded Studio to extend its capabilities and reduce development time. Add-ins include board support packages for evaluation hardware, various middleware packages, and algorithmic modules. Documentation, help, configuration dialogs, and coding examples present in these add-ins are viewable through the CrossCore Embedded Studio IDE once the add-in is installed.

### **Board Support Packages for Evaluation Hardware**

Software support for the EZ-KIT Lite evaluation boards and EZ-Extender daughter cards is provided by software add-ins called Board Support Packages (BSPs). The BSPs contain the required drivers, pertinent release notes, and select example code for the given evaluation hardware. A download link for a specific BSP is located on the web page for the associated EZ-KIT or EZ-Extender product. The link is found in the *Product Download* area of the product web page.

## Middleware Packages

Analog Devices separately offers middleware add-ins such as real time operating systems, file systems, USB stacks, and TCP/IP stacks. For more information see the following web pages:

- www.analog.com/ucos3

- · www.analog.com/ucfs

- www.analog.com/ucusbd

- www.analog.com/lwip

### **Algorithmic Modules**

To speed development, Analog Devices offers add-ins that perform popular audio and video processing algorithms. These are available for use with both CrossCore Embedded Studio and VisualDSP++. For more information visit www.analog.com and search on "Blackfin software modules" or "SHARC software modules".

## Designing an Emulator-Compatible DSP Board (Target)

For embedded system test and debug, Analog Devices provides a family of emulators. On each JTAG DSP, Analog Devices supplies an IEEE 1149.1 JTAG Test Access Port (TAP). In-circuit emulation is facilitated by use of this JTAG interface. The emulator accesses the processor's internal features via the processor's TAP, allowing the developer to load code, set breakpoints, and view variables, memory, and registers. The processor must be halted to send data and commands, but once an operation is completed by the emulator, the DSP system is set to run at full speed with no impact on system timing. The emulators require the target board to include a header that supports connection of the DSP's JTAG port to the emulator.

For details on target board design issues including mechanical layout, single processor connections, signal buffering, signal termination, and emulator pod logic, see the Engineer-to-Engineer Note "Analog Devices JTAG Emulation Technical Reference" (EE-68) on the Analog Devices website (www.analog.com)—use site search on "EE-68." This document is updated regularly to keep pace with improvements to emulator support.

#### ADDITIONAL INFORMATION

The following publications that describe the ADSP-BF531/ ADSP-BF532/ADSP-BF533 processors (and related processors) can be ordered from any Analog Devices sales office or accessed electronically on our website:

- Getting Started With Blackfin Processors

- ADSP-BF533 Blackfin Processor Hardware Reference

- Blackfin Processor Programming Reference

- ADSP-BF531/ADSP-BF532/ADSP-BF533 Blackfin Processor Anomaly List

#### **RELATED SIGNAL CHAINS**

A *signal chain* is a series of signal-conditioning electronic components that receive input (data acquired from sampling either real-time phenomena or from stored data) in tandem, with the output of one portion of the chain supplying input to the next. Signal chains are often used in signal processing applications to gather and process data or to apply system controls based on analysis of real-time phenomena. For more information about this term and related topics, see the "signal chain" entry in Wikipedia or the Glossary of EE Terms on the Analog Devices website.

Analog Devices eases signal processing system development by providing signal processing components that are designed to work together well. A tool for viewing relationships between specific applications and related components is available on the www.analog.com website.

The Application Signal Chains page in the Circuits from the Lab™ site (http://www.analog.com/circuits) provides:

- Graphical circuit block diagram presentation of signal chains for a variety of circuit types and applications

- Drill down links for components in each chain to selection guides and application information

- Reference designs applying best practice design techniques

System designers should refer to *Estimating Power for the ADSP-BF531/BF532/BF533 Blackfin Processors (EE-229)*, which provides detailed information for optimizing designs for lowest power. All topics discussed in this section are described in detail in EE-229. Total power dissipation has two components:

- 1. Static, including leakage current

- 2. Dynamic, due to transistor switching characteristics

Many operating conditions can also affect power dissipation, including temperature, voltage, operating frequency, and processor activity. Electrical Characteristics on Page 22 shows the

current dissipation for internal circuitry ( $V_{DDINT}$ ).  $I_{DDDEEPSLEEP}$  specifies static power dissipation as a function of voltage ( $V_{DDINT}$ ) and temperature (see Table 14 or Table 15), and  $I_{DDINT}$  specifies the total power specification for the listed test conditions, including the dynamic component as a function of voltage ( $V_{DDINT}$ ) and frequency (Table 17).

The dynamic component is also subject to an Activity Scaling Factor (ASF) which represents application code running on the processor (Table 16).

Table 14. Static Current-500 MHz, 533 MHz, and 600 MHz Speed Grade Devices (mA)<sup>1</sup>

|                                  |        | Voltage (V <sub>DDINT</sub> ) <sup>2</sup> |        |        |        |        |        |        |        |        |        |        |         |        |        |

|----------------------------------|--------|--------------------------------------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------|--------|--------|

| T <sub>J</sub> (°C) <sup>2</sup> | 0.80 V | 0.85 V                                     | 0.90 V | 0.95 V | 1.00 V | 1.05 V | 1.10 V | 1.15 V | 1.20 V | 1.25 V | 1.30 V | 1.32 V | 1.375 V | 1.43 V | 1.45 V |

| -45                              | 4.3    | 5.3                                        | 5.9    | 7.0    | 8.2    | 9.8    | 11.2   | 13.0   | 15.2   | 17.7   | 20.2   | 21.6   | 25.5    | 30.1   | 32.0   |

| 0                                | 18.8   | 21.3                                       | 24.1   | 27.8   | 31.6   | 35.6   | 40.1   | 45.3   | 51.4   | 58.1   | 65.0   | 68.5   | 78.4    | 89.8   | 94.3   |

| 25                               | 35.3   | 39.9                                       | 45.0   | 50.9   | 57.3   | 64.4   | 72.9   | 80.9   | 90.3   | 101.4  | 112.1  | 118.0  | 133.7   | 151.6  | 158.7  |

| 40                               | 52.3   | 58.5                                       | 65.1   | 73.3   | 81.3   | 90.9   | 101.2  | 112.5  | 125.5  | 138.7  | 154.4  | 160.6  | 180.6   | 203.1  | 212.0  |

| 55                               | 73.6   | 82.5                                       | 92.0   | 102.7  | 114.4  | 126.3  | 141.2  | 155.7  | 172.7  | 191.1  | 212.1  | 220.8  | 247.6   | 277.7  | 289.5  |

| 70                               | 100.8  | 112.5                                      | 124.5  | 137.4  | 152.6  | 168.4  | 186.5  | 205.4  | 227.0  | 250.3  | 276.2  | 287.1  | 320.4   | 357.4  | 371.9  |

| 85                               | 133.3  | 148.5                                      | 164.2  | 180.5  | 198.8  | 219.0  | 241.0  | 264.5  | 290.6  | 319.7  | 350.2  | 364.6  | 404.9   | 449.7  | 467.2  |

| 100                              | 178.3  | 196.3                                      | 216.0  | 237.6  | 259.9  | 284.6  | 311.9  | 342.0  | 373.1  | 408.0  | 446.1  | 462.6  | 511.1   | 564.7  | 585.6  |

| 115                              | 223.3  | 245.9                                      | 270.2  | 295.7  | 323.5  | 353.3  | 386.1  | 421.1  | 460.1  | 500.9  | 545.0  | 566.5  | 624.3   | 688.1  | 712.8  |

| 125                              | 278.5  | 305.8                                      | 334.1  | 364.3  | 397.4  | 432.4  | 470.6  | 509.3  | 553.4  | 600.6  | 652.1  | 676.5  | 742.1   | 814.1  | 841.9  |

$<sup>^{1}\,\</sup>text{Values}$  are guaranteed maximum  $I_{\text{DDDEEPSLEEP}}$  specifications.

Table 15. Static Current-400 MHz Speed Grade Devices (mA)<sup>1</sup>

|         | Voltage (V <sub>DDINT</sub> ) <sup>2</sup> |        |        |        |        |        |        |        |        |        |        |        |

|---------|--------------------------------------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| °C)2 رT | 0.80 V                                     | 0.85 V | 0.90 V | 0.95 V | 1.00 V | 1.05 V | 1.10 V | 1.15 V | 1.20 V | 1.25 V | 1.30 V | 1.32 V |

| -45     | 0.9                                        | 1.1    | 1.3    | 1.5    | 1.8    | 2.2    | 2.6    | 3.1    | 3.8    | 4.4    | 5.0    | 5.4    |

| 0       | 3.3                                        | 3.7    | 4.2    | 4.8    | 5.5    | 6.3    | 7.2    | 8.1    | 8.9    | 10.1   | 11.2   | 11.9   |

| 25      | 7.5                                        | 8.4    | 9.4    | 10.0   | 11.2   | 12.6   | 14.1   | 15.5   | 17.2   | 19.0   | 21.2   | 21.9   |

| 40      | 12.0                                       | 13.1   | 14.3   | 15.9   | 17.4   | 19.4   | 21.5   | 23.5   | 25.8   | 28.1   | 30.8   | 32.0   |

| 55      | 18.3                                       | 20.0   | 21.9   | 23.6   | 26.0   | 28.2   | 30.8   | 33.7   | 36.8   | 39.8   | 43.4   | 45.0   |

| 70      | 27.7                                       | 30.3   | 32.6   | 35.3   | 38.2   | 41.7   | 45.2   | 49.0   | 52.8   | 57.6   | 62.4   | 64.2   |

| 85      | 38.2                                       | 41.7   | 44.9   | 48.6   | 52.7   | 57.3   | 61.7   | 66.7   | 72.0   | 77.5   | 83.9   | 86.5   |

| 100     | 54.1                                       | 58.1   | 63.2   | 67.8   | 73.2   | 78.8   | 84.9   | 91.5   | 98.4   | 106.0  | 113.8  | 117.2  |

| 115     | 73.9                                       | 80.0   | 86.3   | 91.9   | 99.1   | 106.6  | 114.1  | 122.4  | 131.1  | 140.9  | 151.1  | 155.5  |

| 125     | 98.7                                       | 106.3  | 113.8  | 122.1  | 130.8  | 140.2  | 149.7  | 160.4  | 171.9  | 183.8  | 197.0  | 202.4  |

<sup>&</sup>lt;sup>1</sup> Values are guaranteed maximum I<sub>DDDEEPSLEEP</sub> specifications.

<sup>&</sup>lt;sup>5</sup> Applies to JTAG input pins (TCK, TDI, TMS, TRST).

<sup>&</sup>lt;sup>6</sup> Absolute value.

<sup>&</sup>lt;sup>7</sup> Applies to three-statable pins.

<sup>&</sup>lt;sup>8</sup> Applies to all signal pins.

<sup>&</sup>lt;sup>9</sup>Guaranteed, but not tested.

<sup>&</sup>lt;sup>10</sup>See the ADSP-BF533 Blackfin Processor Hardware Reference Manual for definitions of sleep, deep sleep, and hibernate operating modes.

<sup>&</sup>lt;sup>11</sup>See Table 16 for the list of I<sub>DDINT</sub> power vectors covered by various Activity Scaling Factors (ASF).

<sup>&</sup>lt;sup>2</sup>Valid temperature and voltage ranges are model-specific. See Operating Conditions on Page 20.

<sup>&</sup>lt;sup>2</sup>Valid temperature and voltage ranges are model-specific. See Operating Conditions on Page 20.

### **ABSOLUTE MAXIMUM RATINGS**

Stresses greater than those listed in Table 18 may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions greater than those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods can affect device reliability.

**Table 18. Absolute Maximum Ratings**

| Parameter                                            | Rating                                                  |

|------------------------------------------------------|---------------------------------------------------------|

| Internal (Core) Supply Voltage (V <sub>DDINT</sub> ) | -0.3 V to +1.45 V                                       |

| External (I/O) Supply Voltage (V <sub>DDEXT</sub> )  | -0.5 V to +3.8 V                                        |

| Input Voltage <sup>1, 2</sup>                        | -0.5 V to +3.8 V                                        |

| Output Voltage Swing                                 | -0.5 V to V <sub>DDEXT</sub> + 0.5 V<br>-65°C to +150°C |

| Storage Temperature Range                            | -65°C to +150°C                                         |

| Junction Temperature While Biased                    | 125°C                                                   |

<sup>&</sup>lt;sup>1</sup> Applies to 100% transient duty cycle. For other duty cycles see Table 19.

Table 19. Maximum Duty Cycle for Input Transient Voltage<sup>1</sup>

| V <sub>IN</sub> Min (V) <sup>2</sup> | V <sub>IN</sub> Max (V) <sup>2</sup> | Maximum Duty Cycle <sup>3</sup> |

|--------------------------------------|--------------------------------------|---------------------------------|

| -0.50                                | +3.80                                | 100%                            |

| -0.70                                | +4.00                                | 40%                             |

| -0.80                                | +4.10                                | 25%                             |

| -0.90                                | +4.20                                | 15%                             |

| -1.00                                | +4.30                                | 10%                             |

<sup>&</sup>lt;sup>1</sup> Applies to all signal pins with the exception of CLKIN, XTAL, VROUT1-0.

#### **ESD SENSITIVITY**

### ESD (electrostatic discharge) sensitive device.

Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

$<sup>^2</sup>$  Applies only when  $V_{DDEXT}$  is within specifications. When  $V_{DDEXT}$  is outside specifications, the range is  $V_{DDEXT}\pm0.2~V.$

<sup>&</sup>lt;sup>2</sup> The individual values cannot be combined for analysis of a single instance of overshoot or undershoot. The worst case observed value must fall within one of the voltages specified and the total duration of the overshoot or undershoot (exceeding the 100% case) must be less than or equal to the corresponding duty cycle.

<sup>&</sup>lt;sup>3</sup> Duty cycle refers to the percentage of time the signal exceeds the value for the 100% case. This is equivalent to the measured duration of a single instance of overshoot or undershoot as a percentage of the period of occurrence.

### **PACKAGE INFORMATION**

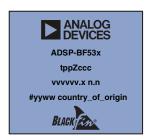

The information presented in Figure 10 and Table 20 provides details about the package branding for the Blackfin processors. For a complete listing of product availability, see the Ordering Guide on Page 63.

Figure 10. Product Information on Package

Table 20. Package Brand Information<sup>1</sup>

| Brand Key  | Field Description                            |

|------------|----------------------------------------------|

| ADSP-BF53x | Either ADSP-BF531, ADSP-BF532, or ADSP-BF533 |

| t          | Temperature Range                            |

| рр         | Package Type                                 |

| Z          | RoHS Compliant Part                          |

| ссс        | See Ordering Guide                           |

| vvvvv.x    | Assembly Lot Code                            |

| n.n        | Silicon Revision                             |

| #          | RoHS Compliant Designation                   |

| yyww       | Date Code                                    |

$<sup>^{\</sup>rm l}$  Non Automotive only. For branding information specific to Automotive products, contact Analog Devices Inc.

## **External Port Bus Request and Grant Cycle Timing**

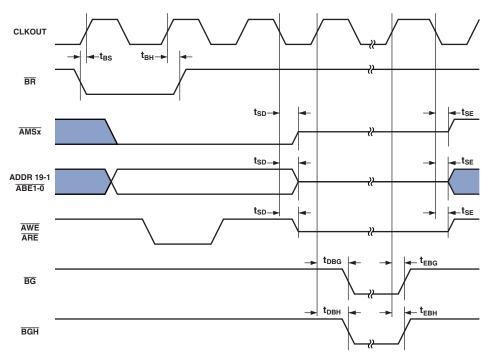

Table 26 and Figure 16 describe external port bus request and bus grant operations.

Table 26. External Port Bus Request and Grant Cycle Timing

|                                                                                                 |     | <sub>EXT</sub> = 1.8 V<br>BGA Packages | V <sub>DDEXT</sub> = 1<br>CSP_BGA Pa |    | V <sub>DDEXT</sub> = 2.5 V/3.3 V<br>All Packages |     |      |

|-------------------------------------------------------------------------------------------------|-----|----------------------------------------|--------------------------------------|----|--------------------------------------------------|-----|------|

| Parameter                                                                                       |     | Max                                    | Min Ma                               | ax | Min                                              | Max | Unit |

| Timing Requirements                                                                             |     |                                        |                                      |    |                                                  |     |      |

| t <sub>BS</sub> BR Asserted to CLKOUT High Setup                                                | 4.6 |                                        | 4.6                                  |    | 4.6                                              |     | ns   |

| t <sub>BH</sub> CLKOUT High to BR Deasserted Hold Time                                          | 1.0 |                                        | 1.0                                  |    | 0.0                                              |     | ns   |

| Switching Characteristics                                                                       |     |                                        |                                      |    |                                                  |     |      |

| $t_{SD}$ CLKOUT Low to $\overline{AMSx}$ , Address, and $\overline{ARE}/\overline{AWE}$ Disable |     | 4.5                                    | 4.5                                  | ;  |                                                  | 4.5 | ns   |

| $t_{SE}$ CLKOUT Low to $\overline{AMSx}$ , Address, and $\overline{ARE}/\overline{AWE}$ Enable  |     | 4.5                                    | 4.5                                  | ;  |                                                  | 4.5 | ns   |

| t <sub>DBG</sub> CLKOUT High to BG High Setup                                                   |     | 6.0                                    | 5.5                                  | ;  |                                                  | 3.6 | ns   |

| t <sub>EBG</sub> CLKOUT High to BG Deasserted Hold Time                                         |     | 6.0                                    | 4.6                                  | •  |                                                  | 3.6 | ns   |

| t <sub>DBH</sub> CLKOUT High to BGH High Setup                                                  |     | 6.0                                    | 5.5                                  | ;  |                                                  | 3.6 | ns   |

| t <sub>EBH</sub> CLKOUT High to BGH Deasserted Hold Time                                        |     | 6.0                                    | 4.6                                  | i  |                                                  | 3.6 | ns   |

Figure 16. External Port Bus Request and Grant Cycle Timing

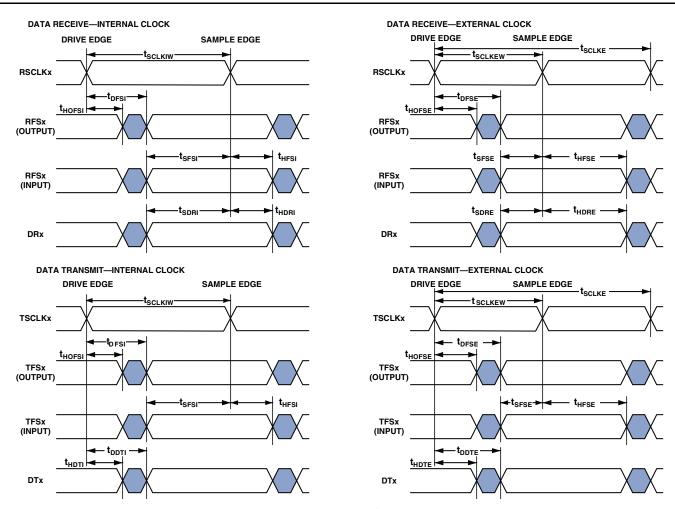

Figure 23. Serial Ports

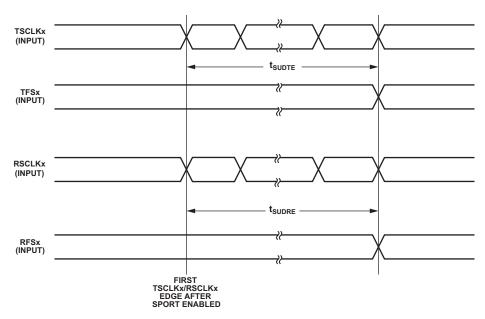

Figure 24. Serial Port Start Up with External Clock and Frame Sync

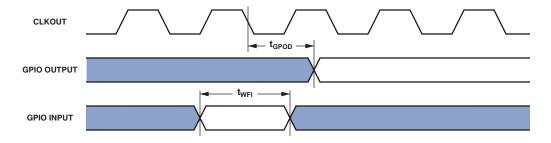

## General-Purpose I/O Port F Pin Cycle Timing

Table 34. General-Purpose I/O Port F Pin Cycle Timing

|                                                     | V <sub>DDEXT</sub> = | 1.8 V | $V_{DDEXT} = 2.5 \text{ V}/3.3 \text{ V}$ |     |      |

|-----------------------------------------------------|----------------------|-------|-------------------------------------------|-----|------|

| Parameter                                           | Min                  | Max   | Min                                       | Max | Unit |

| Timing Requirement                                  |                      |       |                                           |     |      |

| t <sub>WFI</sub> GPIO Input Pulse Width             |                      |       | t <sub>SCLK</sub> + 1                     |     | ns   |

| Switching Characteristic                            |                      |       |                                           |     |      |

| t <sub>GPOD</sub> GPIO Output Delay from CLKOUT Low |                      | 6     |                                           | 6   | ns   |

Figure 29. GPIO Cycle Timing

# Universal Asynchronous Receiver-Transmitter (UART) Ports—Receive and Transmit Timing

For information on the UART port receive and transmit operations, see the ADSP-BF533 Blackfin Processor Hardware Reference.

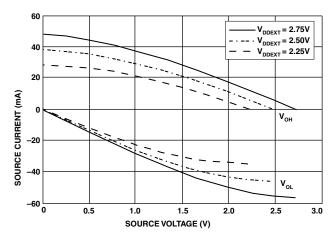

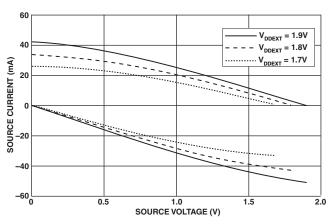

Figure 39. Drive Current C ( $V_{DDEXT} = 2.5 V$ )

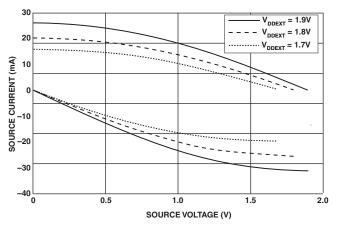

Figure 40. Drive Current C ( $V_{DDEXT} = 1.8 \text{ V}$ )

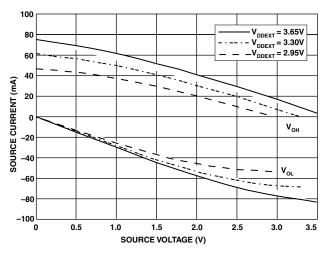

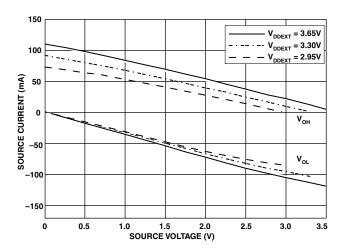

Figure 41. Drive Current C ( $V_{DDEXT} = 3.3 V$ )

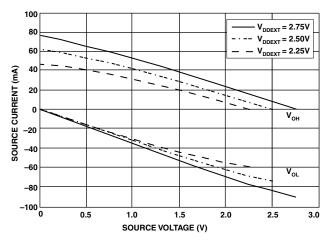

Figure 42. Drive Current D ( $V_{DDEXT} = 2.5 V$ )

Figure 43. Drive Current D ( $V_{DDEXT} = 1.8 V$ )

Figure 44. Drive Current D ( $V_{DDEXT} = 3.3 V$ )

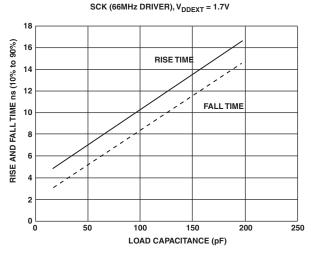

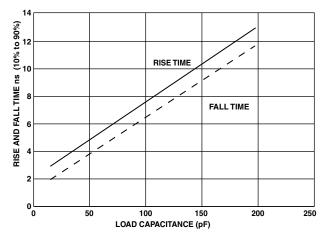

Figure 57. Typical Rise and Fall Times (10% to 90%) vs. Load Capacitance for Driver D at  $V_{\rm DDEXT}$  = 1.75 V

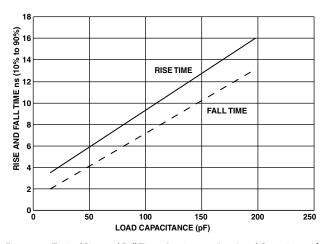

Figure 58. Typical Rise and Fall Times (10% to 90%) vs. Load Capacitance for Driver D at  $V_{\rm DDEXT}$  = 2.25 V

Figure 59. Typical Rise and Fall Times (10% to 90%) vs. Load Capacitance for Driver D at  $V_{\text{DDEXT}} = 3.65 \text{ V}$

## THERMAL CHARACTERISTICS

To determine the junction temperature on the application printed circuit board, use:

$$T_I = T_{CASE} + (\Psi_{IT} \times P_D)$$

where:

$T_I$  = Junction temperature (°C).

$T_{CASE}$  = Case temperature (°C) measured by customer at top center of package.

$\Psi_{IT}$  = From Table 38 through Table 40.

$P_D$  = Power dissipation (see the power dissipation discussion and the tables on 23 for the method to calculate  $P_D$ ).

Values of  $\theta_{JA}$  are provided for package comparison and printed circuit board design considerations.  $\theta_{JA}$  can be used for a first order approximation of  $T_I$  by the equation:

$$T_J = T_A + (\theta_{JA} \times P_D)$$

where:

$T_A$  = ambient temperature (°C).

In Table 38 through Table 40, airflow measurements comply with JEDEC standards JESD51–2 and JESD51–6, and the junction-to-board measurement complies with JESD51–8. The junction-to-case measurement complies with MIL-STD-883 (Method 1012.1). All measurements use a 2S2P JEDEC test board

Thermal resistance  $\theta_{JA}$  in Table 38 through Table 40 is the figure of merit relating to performance of the package and board in a convective environment.  $\theta_{JMA}$  represents the thermal resistance under two conditions of airflow.  $\Psi_{JT}$  represents the correlation between  $T_J$  and  $T_{CASE}$ .

Table 38. Thermal Characteristics for BC-160 Package

| Parameter             | Condition            | Typical | Unit |

|-----------------------|----------------------|---------|------|

| $\theta_{JA}$         | 0 Linear m/s Airflow | 27.1    | °C/W |

| $\theta_{\text{JMA}}$ | 1 Linear m/s Airflow | 23.85   | °C/W |

| $\theta_{\text{JMA}}$ | 2 Linear m/s Airflow | 22.7    | °C/W |

| $\theta_{\text{JC}}$  | Not Applicable       | 7.26    | °C/W |

| $\Psi_{\text{JT}}$    | 0 Linear m/s Airflow | 0.14    | °C/W |

| $\Psi_{\text{JT}}$    | 1 Linear m/s Airflow | 0.26    | °C/W |

| $\Psi_{	extsf{JT}}$   | 2 Linear m/s Airflow | 0.35    | °C/W |

Table 39. Thermal Characteristics for ST-176-1 Package

| Parameter             | Condition            | Typical | Unit |

|-----------------------|----------------------|---------|------|

| $\theta_{JA}$         | 0 Linear m/s Airflow | 34.9    | °C/W |

| $\theta_{\text{JMA}}$ | 1 Linear m/s Airflow | 33.0    | °C/W |

| $\theta_{\text{JMA}}$ | 2 Linear m/s Airflow | 32.0    | °C/W |

| $\Psi_{	extsf{JT}}$   | 0 Linear m/s Airflow | 0.50    | °C/W |

| $\Psi_{	extsf{JT}}$   | 1 Linear m/s Airflow | 0.75    | °C/W |

| $\Psi_{	extsf{JT}}$   | 2 Linear m/s Airflow | 1.00    | °C/W |

Table 40. Thermal Characteristics for B-169 Package

| Parameter           | Condition            | Typical | Unit |

|---------------------|----------------------|---------|------|

| $\theta_{JA}$       | 0 Linear m/s Airflow | 22.8    | °C/W |

| $\theta_{JMA}$      | 1 Linear m/s Airflow | 20.3    | °C/W |

| $\theta_{JMA}$      | 2 Linear m/s Airflow | 19.3    | °C/W |

| $\theta_{JC}$       | Not Applicable       | 10.39   | °C/W |

| $\Psi_{	extsf{JT}}$ | 0 Linear m/s Airflow | 0.59    | °C/W |

| $\Psi_{JT}$         | 1 Linear m/s Airflow | 0.88    | °C/W |

| $\Psi_{	extsf{JT}}$ | 2 Linear m/s Airflow | 1.37    | °C/W |

Table 44. 169-Ball PBGA Ball Assignment (Numerical by Ball Number)

| Ball No. | Signal      | Ball No. | Signal      | Ball No. | Signal             | Ball No. | Signal      | Ball No. | Signal |

|----------|-------------|----------|-------------|----------|--------------------|----------|-------------|----------|--------|

| A1       | PF4         | D16      | CLKOUT      | J2       | RSCLK1             | M12      | VDD         | U9       | DATA9  |

| A2       | PF5         | D17      | AMS0        | J6       | $V_{\text{DDEXT}}$ | M16      | ADDR7       | U10      | DATA7  |

| A3       | PF7         | E1       | MOSI        | J7       | GND                | M17      | ADDR8       | U11      | DATA5  |

| A4       | PF9         | E2       | MISO        | J8       | GND                | N1       | RFS0        | U12      | DATA4  |

| A5       | PF11        | E16      | AMS1        | J9       | GND                | N2       | RSCLK0      | U13      | DATA2  |

| A6       | PF12        | E17      | AMS2        | J10      | GND                | N16      | ADDR10      | U14      | DATA0  |

| A7       | PF14        | F1       | DT1PRI      | J11      | GND                | N17      | ADDR9       | U15      | ADDR16 |

| A8       | PPI3        | F2       | DT1SEC      | J12      | VDD                | P1       | TMR2        | U16      | ADDR18 |

| A9       | PPI1        | F6       | $V_{DDEXT}$ | J16      | ADDR1              | P2       | TMR1        | U17      | BGH    |

| A10      | RTXI        | F7       | $V_{DDEXT}$ | J17      | ADDR2              | P16      | ADDR12      |          |        |

| A11      | RTXO        | F8       | $V_{DDEXT}$ | K1       | DT0SEC             | P17      | ADDR11      |          |        |

| A12      | RESET       | F9       | $V_{DDEXT}$ | K2       | <b>DTOPRI</b>      | R1       | TMR0        |          |        |

| A13      | XTAL        | F10      | RTCVDD      | K6       | $V_{DDEXT}$        | R2       | TX          |          |        |

| A14      | CLKIN       | F11      | GND         | K7       | GND                | R16      | ADDR14      |          |        |

| A15      | SRAS        | F12      | VDD         | K8       | GND                | R17      | ADDR13      |          |        |

| A16      | SCAS        | F16      | AMS3        | К9       | GND                | T1       | RX          |          |        |

| A17      | SMS         | F17      | AOE         | K10      | GND                | T2       | $V_{DDEXT}$ |          |        |

| B1       | PF2         | G1       | TSCLK1      | K11      | GND                | T3       | TMS         |          |        |

| B2       | $V_{DDEXT}$ | G2       | TFS1        | K12      | VDD                | T4       | TDO         |          |        |

| В3       | PF6         | G6       | $V_{DDEXT}$ | K16      | ADDR3              | T5       | BMODE1      |          |        |

| B4       | PF8         | G7       | GND         | K17      | ADDR4              | T6       | DATA15      |          |        |

| B5       | PF10        | G8       | GND         | L1       | TFS0               | T7       | DATA13      |          |        |

| B6       | PF13        | G9       | GND         | L2       | TSCLK0             | T8       | DATA10      |          |        |

| B7       | PF15        | G10      | GND         | L6       | $V_{DDEXT}$        | T9       | DATA8       |          |        |

| B8       | PPI2        | G11      | GND         | L7       | GND                | T10      | DATA6       |          |        |

| B9       | PPI0        | G12      | VDD         | L8       | GND                | T11      | DATA3       |          |        |

| B10      | PPI_CLK     | G16      | ARE         | L9       | GND                | T12      | DATA1       |          |        |

| B11      | NMI         | G17      | AWE         | L10      | GND                | T13      | BG          |          |        |

| B12      | VROUT0      | H1       | DR1PRI      | L11      | GND                | T14      | ADDR19      |          |        |

| B13      | VROUT1      | H2       | DR1SEC      | L12      | VDD                | T15      | ADDR17      |          |        |

| B14      | SCKE        | H6       | $V_{DDEXT}$ | L16      | ADDR5              | T16      | GND         |          |        |

| B15      | SA10        | H7       | GND         | L17      | ADDR6              | T17      | ADDR15      |          |        |

| B16      | GND         | H8       | GND         | M1       | DROSEC             | U1       | <b>EMU</b>  |          |        |

| B17      | SWE         | H9       | GND         | M2       | DROPRI             | U2       | TRST        |          |        |

| C1       | PF1         | H10      | GND         | M6       | $V_{\text{DDEXT}}$ | U3       | TDI         |          |        |

| C2       | PF3         | H11      | GND         | M7       | $V_{\text{DDEXT}}$ | U4       | TCK         |          |        |

| C16      | ARDY        | H12      | VDD         | M8       | $V_{\text{DDEXT}}$ | U5       | BMODE0      |          |        |

| C17      | BR          | H16      | ABE0        | М9       | GND                | U6       | DATA14      |          |        |

| D1       | SCK         | H17      | ABE1        | M10      | VDD                | U7       | DATA12      |          |        |

| D2       | PF0         | J1       | RFS1        | M11      | VDD                | U8       | DATA11      |          |        |

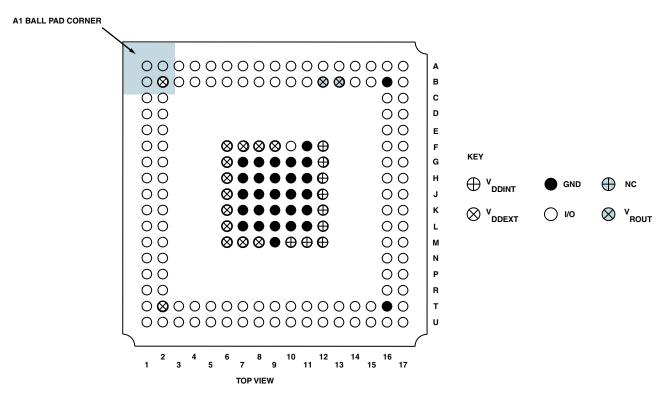

Figure 62. 169-Ball PBGA Ground Configuration (Top View)

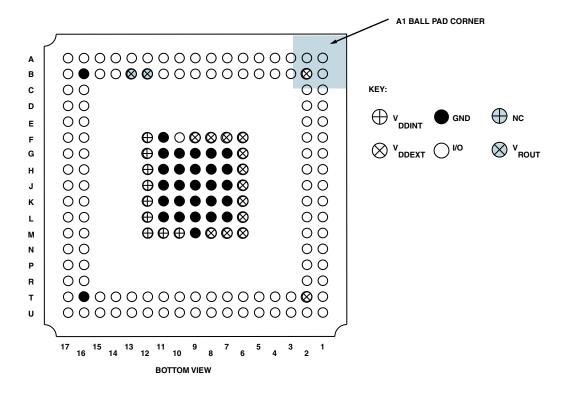

Figure 63. 169-Ball PBGA Ground Configuration (Bottom View)

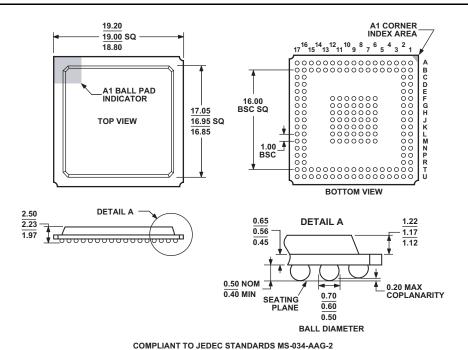

# **OUTLINE DIMENSIONS**

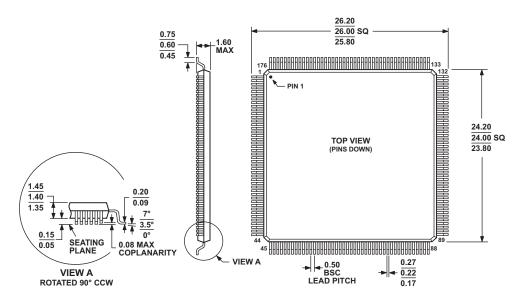

Dimensions in the outline dimension figures are shown in millimeters.

COMPLIANT TO JEDEC STANDARDS MS-026-BGA

Figure 64. 176-Lead Low Profile Quad Flat Package [LQFP] (ST-176-1) Dimensions shown in millimeters

Figure 66. 169-Ball Plastic Ball Grid Array [PBGA] (B-169)

Dimensions shown in millimeters

## **ORDERING GUIDE**

|                    | Temperature        | Speed Grade |                                     | Package  |  |

|--------------------|--------------------|-------------|-------------------------------------|----------|--|

| Model <sup>1</sup> | Range <sup>2</sup> | (Max)       | Package Description                 | Option   |  |

| ADSP-BF531SBB400   | -40°C to +85°C     | 400 MHz     | 169-Ball PBGA                       | B-169    |  |

| ADSP-BF531SBBZ400  | −40°C to +85°C     | 400 MHz     | 169-Ball PBGA                       | B-169    |  |

| ADSP-BF531SBBC400  | −40°C to +85°C     | 400 MHz     | 160-Ball CSP_BGA                    | BC-160-2 |  |

| ADSP-BF531SBBCZ400 | −40°C to +85°C     | 400 MHz     | 160-Ball CSP_BGA                    | BC-160-2 |  |

| ADSP-BF531SBBCZ4RL | −40°C to +85°C     | 400 MHz     | 160-Ball CSP_BGA, 13" Tape and Reel | BC-160-2 |  |

| ADSP-BF531SBSTZ400 | −40°C to +85°C     | 400 MHz     | 176-Lead LQFP                       | ST-176-1 |  |

| ADSP-BF532SBBZ400  | −40°C to +85°C     | 400 MHz     | 169-Ball PBGA                       | B-169    |  |

| ADSP-BF532SBBC400  | −40°C to +85°C     | 400 MHz     | 160-Ball CSP_BGA                    | BC-160-2 |  |

| ADSP-BF532SBBCZ400 | -40°C to +85°C     | 400 MHz     | 160-Ball CSP_BGA                    | BC-160-2 |  |

| ADSP-BF532SBSTZ400 | −40°C to +85°C     | 400 MHz     | 176-Lead LQFP                       | ST-176-1 |  |

| ADSP-BF533SBBZ400  | -40°C to +85°C     | 400 MHz     | 169-Ball PBGA                       | B-169    |  |

| ADSP-BF533SBBC400  | −40°C to +85°C     | 400 MHz     | 160-Ball CSP_BGA                    | BC-160-2 |  |

| ADSP-BF533SBBCZ400 | −40°C to +85°C     | 400 MHz     | 160-Ball CSP_BGA                    | BC-160-2 |  |

| ADSP-BF533SBSTZ400 | −40°C to +85°C     | 400 MHz     | 176-Lead LQFP                       | ST-176-1 |  |

| ADSP-BF533SBB500   | −40°C to +85°C     | 500 MHz     | 169-Ball PBGA                       | B-169    |  |

| ADSP-BF533SBBZ500  | −40°C to +85°C     | 500 MHz     | 169-Ball PBGA                       | B-169    |  |

| ADSP-BF533SBBC500  | −40°C to +85°C     | 500 MHz     | 160-Ball CSP_BGA                    | BC-160-2 |  |

| ADSP-BF533SBBCZ500 | −40°C to +85°C     | 500 MHz     | 160-Ball CSP_BGA                    | BC-160-2 |  |

| ADSP-BF533SBBC-5V  | −40°C to +85°C     | 533 MHz     | 160-Ball CSP_BGA                    | BC-160-2 |  |

| ADSP-BF533SBBCZ-5V | −40°C to +85°C     | 533 MHz     | 160-Ball CSP_BGA                    | BC-160-2 |  |

| ADSP-BF533SKBC-6V  | 0°C to +70°C       | 600 MHz     | 160-Ball CSP_BGA                    | BC-160-2 |  |

| ADSP-BF533SKBCZ-6V | 0°C to +70°C       | 600 MHz     | 160-Ball CSP_BGA                    | BC-160-2 |  |

| ADSP-BF533SKSTZ-5V | 0°C to +70°C       | 533 MHz     | 176-Lead LQFP                       | ST-176-1 |  |

$<sup>^{1}</sup>$  Z = RoHS compliant part.

<sup>&</sup>lt;sup>2</sup> Referenced temperature is ambient temperature. The ambient temperature is not a specification. Please see Operating Conditions on Page 20 for junction temperature (T<sub>j</sub>) specification which is the only temperature specification.