Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Obsolete                                                                     |

|--------------------------------|------------------------------------------------------------------------------|

| Number of LABs/CLBs            | 2125                                                                         |

| Number of Logic Elements/Cells | 17000                                                                        |

| Total RAM Bits                 | 282624                                                                       |

| Number of I/O                  | 201                                                                          |

| Number of Gates                | -                                                                            |

| Voltage - Supply               | 1.14V ~ 1.26V                                                                |

| Mounting Type                  | Surface Mount                                                                |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                              |

| Package / Case                 | 256-LBGA                                                                     |

| Supplier Device Package        | 256-FTBGA (17x17)                                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfxp2-17e-5ft256c |

|                                |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# LatticeXP2 Family Data Sheet Introduction

#### February 2012

# Features

- flexiFLASH<sup>™</sup> Architecture

- Instant-on

- Infinitely reconfigurable

- Single chip

- FlashBAK<sup>™</sup> technology

- Serial TAG memory

- Design security

### ■ Live Update Technology

- TransFR™ technology

- Secure updates with 128 bit AES encryption

- Dual-boot with external SPI

#### ■ sysDSP<sup>™</sup> Block

- Three to eight blocks for high performance Multiply and Accumulate

- 12 to 32 18x18 multipliers

- Each block supports one 36x36 multiplier or four 18x18 or eight 9x9 multipliers

#### Embedded and Distributed Memory

- Up to 885 Kbits sysMEM™ EBR

- Up to 83 Kbits Distributed RAM

### ■ sysCLOCK<sup>™</sup> PLLs

- Up to four analog PLLs per device

- Clock multiply, divide and phase shifting

# ■ Flexible I/O Buffer

- sysIO<sup>™</sup> buffer supports:

- LVCMOS 33/25/18/15/12; LVTTL

- SSTL 33/25/18 class I, II

- HSTL15 class I; HSTL18 class I, II

- PCI

- LVDS, Bus-LVDS, MLVDS, LVPECL, RSDS

#### Pre-engineered Source Synchronous Interfaces

- DDR / DDR2 interfaces up to 200 MHz

- 7:1 LVDS interfaces support display applications

- XGMII

- Density And Package Options

- 5k to 40k LUT4s, 86 to 540 I/Os

- csBGA, TQFP, PQFP, ftBGA and fpBGA packages

- Density migration supported

- Flexible Device Configuration

- SPI (master and slave) Boot Flash Interface

- Dual Boot Image supported

- Soft Error Detect (SED) macro embedded

## System Level Support

- IEEE 1149.1 and IEEE 1532 Compliant

- · On-chip oscillator for initialization & general use

- Devices operate with 1.2V power supply

| Device                        | XP2-5 | XP2-8 | XP2-17 | XP2-30 | XP2-40 |

|-------------------------------|-------|-------|--------|--------|--------|

| LUTs (K)                      | 5     | 8     | 17     | 29     | 40     |

| Distributed RAM (KBits)       | 10    | 18    | 35     | 56     | 83     |

| EBR SRAM (KBits)              | 166   | 221   | 276    | 387    | 885    |

| EBR SRAM Blocks               | 9     | 12    | 15     | 21     | 48     |

| sysDSP Blocks                 | 3     | 4     | 5      | 7      | 8      |

| 18 x 18 Multipliers           | 12    | 16    | 20     | 28     | 32     |

| V <sub>CC</sub> Voltage       | 1.2   | 1.2   | 1.2    | 1.2    | 1.2    |

| GPLL                          | 2     | 2     | 4      | 4      | 4      |

| Max Available I/O             | 172   | 201   | 358    | 472    | 540    |

| Packages and I/O Combinations |       |       | •      |        | •      |

| 132-Ball csBGA (8 x 8 mm)     | 86    | 86    |        |        |        |

| 144-Pin TQFP (20 x 20 mm)     | 100   | 100   |        |        |        |

| 208-Pin PQFP (28 x 28 mm)     | 146   | 146   | 146    |        |        |

| 256-Ball ftBGA (17 x17 mm)    | 172   | 201   | 201    | 201    |        |

| 484-Ball fpBGA (23 x 23 mm)   |       |       | 358    | 363    | 363    |

| 672-Ball fpBGA (27 x 27 mm)   |       |       |        | 472    | 540    |

#### Table 1-1. LatticeXP2 Family Selection Guide

### Data Sheet DS1009

<sup>© 2012</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

# LatticeXP2 Family Data Sheet Architecture

#### August 2014

Data Sheet DS1009

# **Architecture Overview**

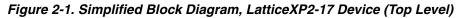

Each LatticeXP2 device contains an array of logic blocks surrounded by Programmable I/O Cells (PIC). Interspersed between the rows of logic blocks are rows of sysMEM<sup>™</sup> Embedded Block RAM (EBR) and a row of sys-DSP<sup>™</sup> Digital Signal Processing blocks as shown in Figure 2-1.

On the left and right sides of the Programmable Functional Unit (PFU) array, there are Non-volatile Memory Blocks. In configuration mode the nonvolatile memory is programmed via the IEEE 1149.1 TAP port or the sysCONFIG<sup>™</sup> peripheral port. On power up, the configuration data is transferred from the Non-volatile Memory Blocks to the configuration SRAM. With this technology, expensive external configuration memory is not required, and designs are secured from unauthorized read-back. This transfer of data from non-volatile memory to configuration SRAM via wide busses happens in microseconds, providing an "instant-on" capability that allows easy interfacing in many applications. LatticeXP2 devices can also transfer data from the sysMEM EBR blocks to the Non-volatile Memory Blocks at user request.

There are two kinds of logic blocks, the PFU and the PFU without RAM (PFF). The PFU contains the building blocks for logic, arithmetic, RAM and ROM functions. The PFF block contains building blocks for logic, arithmetic and ROM functions. Both PFU and PFF blocks are optimized for flexibility allowing complex designs to be implemented quickly and efficiently. Logic Blocks are arranged in a two-dimensional array. Only one type of block is used per row.

LatticeXP2 devices contain one or more rows of sysMEM EBR blocks. sysMEM EBRs are large dedicated 18Kbit memory blocks. Each sysMEM block can be configured in a variety of depths and widths of RAM or ROM. In addition, LatticeXP2 devices contain up to two rows of DSP Blocks. Each DSP block has multipliers and adder/accumulators, which are the building blocks for complex signal processing capabilities.

Each PIC block encompasses two PIOs (PIO pairs) with their respective sysIO buffers. The sysIO buffers of the LatticeXP2 devices are arranged into eight banks, allowing the implementation of a wide variety of I/O standards. PIO pairs on the left and right edges of the device can be configured as LVDS transmit/receive pairs. The PIC logic also includes pre-engineered support to aid in the implementation of high speed source synchronous standards such as 7:1 LVDS interfaces, found in many display applications, and memory interfaces including DDR and DDR2.

The LatticeXP2 registers in PFU and sysI/O can be configured to be SET or RESET. After power up and device is configured, the device enters into user mode with these registers SET/RESET according to the configuration setting, allowing device entering to a known state for predictable system function.

Other blocks provided include PLLs and configuration functions. The LatticeXP2 architecture provides up to four General Purpose PLLs (GPLL) per device. The GPLL blocks are located in the corners of the device.

The configuration block that supports features such as configuration bit-stream de-encryption, transparent updates and dual boot support is located between banks two and three. Every device in the LatticeXP2 family supports a sysCONFIG port, muxed with bank seven I/Os, which supports serial device configuration. A JTAG port is provided between banks two and three.

This family also provides an on-chip oscillator. LatticeXP2 devices use 1.2V as their core voltage.

<sup>© 2014</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

# **PFU Blocks**

The core of the LatticeXP2 device is made up of logic blocks in two forms, PFUs and PFFs. PFUs can be programmed to perform logic, arithmetic, distributed RAM and distributed ROM functions. PFF blocks can be programmed to perform logic, arithmetic and ROM functions. Except where necessary, the remainder of this data sheet will use the term PFU to refer to both PFU and PFF blocks.

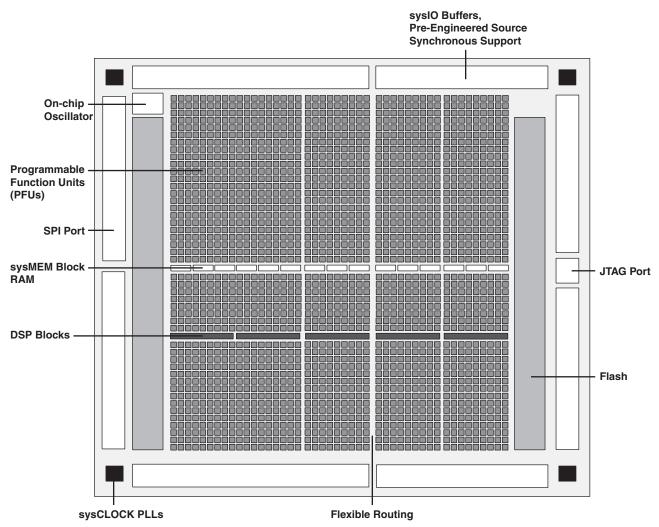

Each PFU block consists of four interconnected slices, numbered Slice 0 through Slice 3, as shown in Figure 2-2. All the interconnections to and from PFU blocks are from routing. There are 50 inputs and 23 outputs associated with each PFU block.

## Figure 2-2. PFU Diagram

## Slice

Slice 0 through Slice 2 contain two 4-input combinatorial Look-Up Tables (LUT4), which feed two registers. Slice 3 contains two LUT4s and no registers. For PFUs, Slice 0 and Slice 2 can also be configured as distributed memory, a capability not available in PFF blocks. Table 2-1 shows the capability of the slices in both PFF and PFU blocks along with the operation modes they enable. In addition, each PFU contains logic that allows the LUTs to be combined to perform functions such as LUT5, LUT6, LUT7 and LUT8. There is control logic to perform set/reset functions (programmable as synchronous/asynchronous), clock select, chip-select and wider RAM/ROM functions. Figure 2-3 shows an overview of the internal logic of the slice. The registers in the slice can be configured as positive/negative edge triggered or level sensitive clocks.

| Table 2-1. | Resources | and Modes | Available    | per Slice |

|------------|-----------|-----------|--------------|-----------|

|            |           |           | / IT analoio |           |

|         | PFU                     | 3Lock                   | PFF Block               |                    |  |

|---------|-------------------------|-------------------------|-------------------------|--------------------|--|

| Slice   | Resources               | Modes                   | Resources               | Modes              |  |

| Slice 0 | 2 LUT4s and 2 Registers | Logic, Ripple, RAM, ROM | 2 LUT4s and 2 Registers | Logic, Ripple, ROM |  |

| Slice 1 | 2 LUT4s and 2 Registers | Logic, Ripple, ROM      | 2 LUT4s and 2 Registers | Logic, Ripple, ROM |  |

| Slice 2 | 2 LUT4s and 2 Registers | Logic, Ripple, RAM, ROM | 2 LUT4s and 2 Registers | Logic, Ripple, ROM |  |

| Slice 3 | 2 LUT4s                 | Logic, ROM              | 2 LUT4s                 | Logic, ROM         |  |

Slice 0 through Slice 2 have 14 input signals: 13 signals from routing and one from the carry-chain (from the adjacent slice or PFU). There are seven outputs: six to routing and one to carry-chain (to the adjacent PFU). Slice 3 has 13 input signals from routing and four signals to routing. Table 2-2 lists the signals associated with Slice 0 to Slice 2.

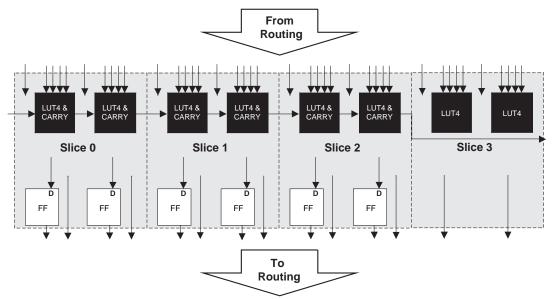

# Figure 2-6. Primary Clock Sources for XP2-17

Note: This diagram shows sources for the XP2-17 device. Smaller LatticeXP2 devices have two GPLLs.

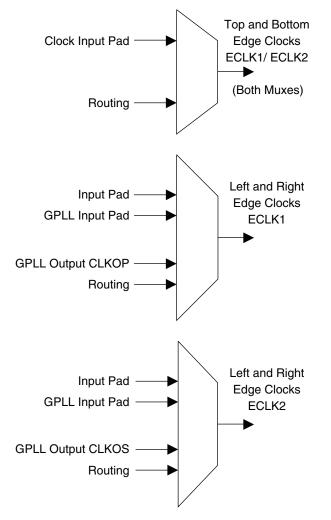

## Edge Clock Sources

Edge clock resources can be driven from a variety of sources at the same edge. Edge clock resources can be driven from adjacent edge clock PIOs, primary clock PIOs, PLLs and clock dividers as shown in Figure 2-8.

#### Figure 2-8. Edge Clock Sources

Note: This diagram shows sources for the XP2-17 device. Smaller LatticeXP2 devices have two GPLLs.

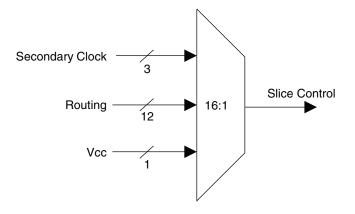

### Figure 2-14. Slice0 through Slice2 Control Selection

# **Edge Clock Routing**

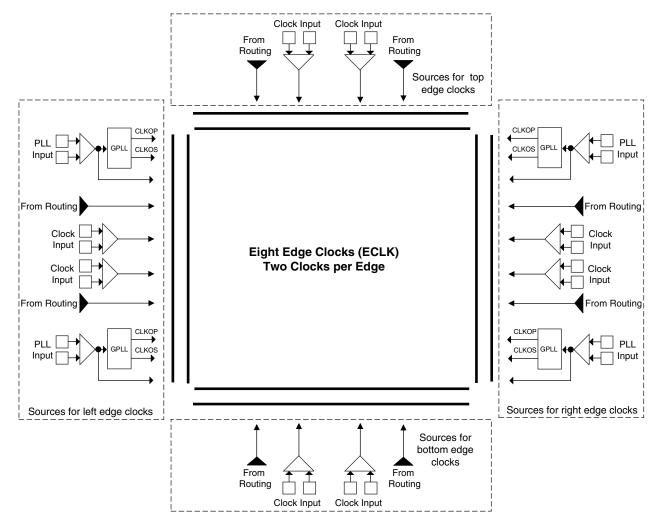

LatticeXP2 devices have eight high-speed edge clocks that are intended for use with the PIOs in the implementation of high-speed interfaces. Each device has two edge clocks per edge. Figure 2-15 shows the selection muxes for these clocks.

#### Figure 2-15. Edge Clock Mux Connections

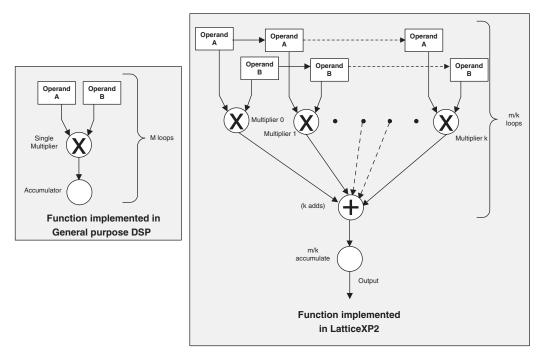

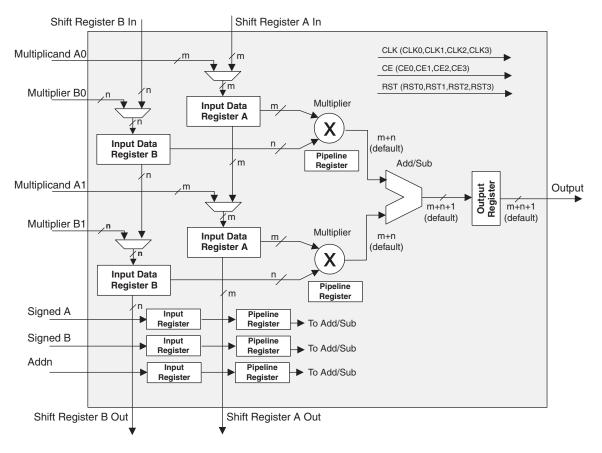

## sysDSP Block Capabilities

The sysDSP block in the LatticeXP2 family supports four functional elements in three 9, 18 and 36 data path widths. The user selects a function element for a DSP block and then selects the width and type (signed/unsigned) of its operands. The operands in the LatticeXP2 family sysDSP Blocks can be either signed or unsigned but not mixed within a function element. Similarly, the operand widths cannot be mixed within a block. DSP elements can be concatenated.

The resources in each sysDSP block can be configured to support the following four elements:

- MULT (Multiply)

- MAC (Multiply, Accumulate)

- MULTADDSUB (Multiply, Addition/Subtraction)

- MULTADDSUBSUM (Multiply, Addition/Subtraction, Accumulate)

The number of elements available in each block depends on the width selected from the three available options: x9, x18, and x36. A number of these elements are concatenated for highly parallel implementations of DSP functions. Table 2-6 shows the capabilities of the block.

| Table 2-6. Maximum Number of Elements in a Block |  |

|--------------------------------------------------|--|

|--------------------------------------------------|--|

| Width of Multiply | x9 | x18 | x36 |

|-------------------|----|-----|-----|

| MULT              | 8  | 4   | 1   |

| MAC               | 2  | 2   | —   |

| MULTADDSUB        | 4  | 2   | —   |

| MULTADDSUBSUM     | 2  | 1   | —   |

Some options are available in four elements. The input register in all the elements can be directly loaded or can be loaded as shift register from previous operand registers. By selecting 'dynamic operation' the following operations are possible:

# MULTADDSUB sysDSP Element

In this case, the operands A0 and B0 are multiplied and the result is added/subtracted with the result of the multiplier operation of operands A1 and B1. The user can enable the input, output and pipeline registers. Figure 2-22 shows the MULTADDSUB sysDSP element.

### Figure 2-22. MULTADDSUB

## DQSXFER

LatticeXP2 devices provide a DQSXFER signal to the output buffer to assist it in data transfer to DDR memories that require DQS strobe be shifted 90°. This shifted DQS strobe is generated by the DQSDEL block. The DQSXFER signal runs the span of the data bus.

# sysIO Buffer

Each I/O is associated with a flexible buffer referred to as a sysIO buffer. These buffers are arranged around the periphery of the device in groups referred to as banks. The sysIO buffers allow users to implement the wide variety of standards that are found in today's systems including LVCMOS, SSTL, HSTL, LVDS and LVPECL.

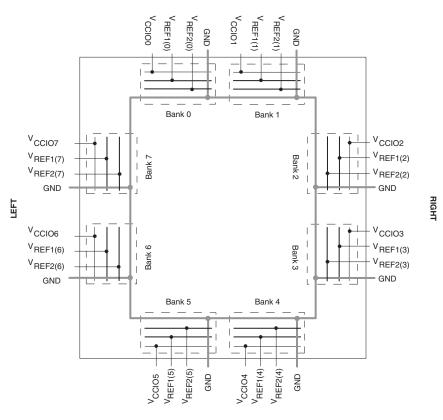

## sysIO Buffer Banks

LatticeXP2 devices have eight sysIO buffer banks for user I/Os arranged two per side. Each bank is capable of supporting multiple I/O standards. Each sysIO bank has its own I/O supply voltage ( $V_{CCIO}$ ). In addition, each bank has voltage references,  $V_{REF1}$  and  $V_{REF2}$ , that allow it to be completely independent from the others. Figure 2-32 shows the eight banks and their associated supplies.

In LatticeXP2 devices, single-ended output buffers and ratioed input buffers (LVTTL, LVCMOS and PCI) are powered using  $V_{CCIO}$ . LVTTL, LVCMOS33, LVCMOS25 and LVCMOS12 can also be set as fixed threshold inputs independent of  $V_{CCIO}$ .

Each bank can support up to two separate  $V_{REF}$  voltages,  $V_{REF1}$  and  $V_{REF2}$ , that set the threshold for the referenced input buffers. Some dedicated I/O pins in a bank can be configured to be a reference voltage supply pin. Each I/O is individually configurable based on the bank's supply and reference voltages.

тор

#### Figure 2-32. LatticeXP2 Banks

воттом

LatticeXP2 devices contain two types of sysIO buffer pairs.

#### 1. Top and Bottom (Banks 0, 1, 4 and 5) sysIO Buffer Pairs (Single-Ended Outputs Only)

The sysIO buffer pairs in the top banks of the device consist of two single-ended output drivers and two sets of single-ended input buffers (both ratioed and referenced). One of the referenced input buffers can also be configured as a differential input.

The two pads in the pair are described as "true" and "comp", where the true pad is associated with the positive side of the differential input buffer and the comp (complementary) pad is associated with the negative side of the differential input buffer.

Only the I/Os on the top and bottom banks have programmable PCI clamps.

2. Left and Right (Banks 2, 3, 6 and 7) sysIO Buffer Pairs (50% Differential and 100% Single-Ended Outputs) The sysIO buffer pairs in the left and right banks of the device consist of two single-ended output drivers, two sets of single-ended input buffers (both ratioed and referenced) and one differential output driver. One of the referenced input buffers can also be configured as a differential input.

The two pads in the pair are described as "true" and "comp", where the true pad is associated with the positive side of the differential I/O, and the comp pad is associated with the negative side of the differential I/O.

LVDS differential output drivers are available on 50% of the buffer pairs on the left and right banks.

## Typical sysIO I/O Behavior During Power-up

The internal power-on-reset (POR) signal is deactivated when  $V_{CC, V} C_{CCONFIG} (V_{CCIO7})$  and  $V_{CCAUX}$  have reached satisfactory levels. After the POR signal is deactivated, the FPGA core logic becomes active. It is the user's responsibility to ensure that all other  $V_{CCIO}$  banks are active with valid input logic levels to properly control the output logic states of all the I/O banks that are critical to the application. During power up and before the FPGA core logic becomes active, all user I/Os will be high-impedance with weak pull-up. Please refer to TN1136, <u>LatticeXP2 sysIO</u> Usage Guide for additional information.

The V<sub>CC</sub> and V<sub>CCAUX</sub> supply the power to the FPGA core fabric, whereas the V<sub>CCIO</sub> supplies power to the I/O buffers. In order to simplify system design while providing consistent and predictable I/O behavior, it is recommended that the I/O buffers be powered-up prior to the FPGA core fabric. V<sub>CCIO</sub> supplies should be powered-up before or together with the V<sub>CC</sub> and V<sub>CCAUX</sub> supplies.

## Supported sysIO Standards

The LatticeXP2 sysIO buffer supports both single-ended and differential standards. Single-ended standards can be further subdivided into LVCMOS, LVTTL and other standards. The buffers support the LVTTL, LVCMOS 1.2V, 1.5V, 1.8V, 2.5V and 3.3V standards. In the LVCMOS and LVTTL modes, the buffer has individual configuration options for drive strength, bus maintenance (weak pull-up, weak pull-down, or a bus-keeper latch) and open drain. Other single-ended standards supported include SSTL and HSTL. Differential standards supported include LVDS, MLVDS, BLVDS, LVPECL, RSDS, differential SSTL and differential HSTL. Tables 2-12 and 2-13 show the I/O standards (together with their supply and reference voltages) supported by LatticeXP2 devices. For further information on utilizing the sysIO buffer to support a variety of standards please see TN1136, LatticeXP2 sysIO Usage Guide.

- 1. Unlocked

- 2. Key Locked Presenting the key through the programming interface allows the device to be unlocked.

- 3. Permanently Locked The device is permanently locked.

To further complement the security of the device a One Time Programmable (OTP) mode is available. Once the device is set in this mode it is not possible to erase or re-program the Flash portion of the device.

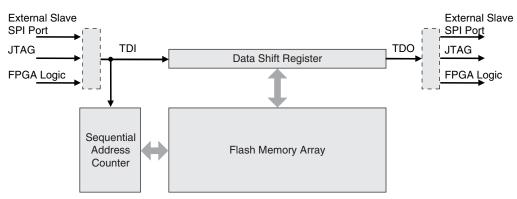

## Serial TAG Memory

LatticeXP2 devices offer 0.6 to 3.3kbits of Flash memory in the form of Serial TAG memory. The TAG memory is an area of the on-chip Flash that can be used for non-volatile storage including electronic ID codes, version codes, date stamps, asset IDs and calibration settings. A block diagram of the TAG memory is shown in Figure 2-34. The TAG memory is accessed in the same way as external SPI Flash and it can be read or programmed either through JTAG, an external Slave SPI Port, or directly from FPGA logic. To read the TAG memory, a start address is specified and the entire TAG memory contents are read sequentially in a first-in-first-out manner. The TAG memory is always accessible regardless of the device security settings. For more information, see TN1137, LatticeXP2 Memory Usage Guide and TN1141, LatticeXP2 sysCONFIG Usage Guide.

#### Figure 2-34. Serial TAG Memory Diagram

# Live Update Technology

Many applications require field updates of the FPGA. LatticeXP2 devices provide three features that enable this configuration to be done in a secure and failsafe manner while minimizing impact on system operation.

#### 1. Decryption Support

LatticeXP2 devices provide on-chip, non-volatile key storage to support decryption of a 128-bit AES encrypted bitstream, securing designs and deterring design piracy.

#### 2. TransFR (Transparent Field Reconfiguration)

TransFR I/O (TFR) is a unique Lattice technology that allows users to update their logic in the field without interrupting system operation using a single ispVM command. TransFR I/O allows I/O states to be frozen during device configuration. This allows the device to be field updated with a minimum of system disruption and downtime. For more information please see TN1087, <u>Minimizing System Interruption During Configuration</u>. Using TransFR Technology.

#### 3. Dual Boot Image Support

Dual boot images are supported for applications requiring reliable remote updates of configuration data for the system FPGA. After the system is running with a basic configuration, a new boot image can be downloaded remotely and stored in a separate location in the configuration storage device. Any time after the update the LatticeXP2 can be re-booted from this new configuration file. If there is a problem such as corrupt data during download or incorrect version number with this new boot image, the LatticeXP2 device can revert back to the

# **Density Shifting**

The LatticeXP2 family is designed to ensure that different density devices in the same family and in the same package have the same pinout. Furthermore, the architecture ensures a high success rate when performing design migration from lower density devices to higher density devices. In many cases, it is also possible to shift a lower utilization design targeted for a high-density device to a lower density device. However, the exact details of the final resource utilization will impact the likely success in each case.

# Supply Current (Standby)<sup>1, 2, 3, 4</sup>

| Symbol             | Parameter                                   | Device | Typical⁵ | Units |

|--------------------|---------------------------------------------|--------|----------|-------|

|                    |                                             | XP2-5  | 14       | mA    |

|                    |                                             | XP2-8  | 18       | mA    |

| I <sub>CC</sub>    | Core Power Supply Current                   | XP2-17 | 24       | mA    |

|                    |                                             | XP2-30 | 35       | mA    |

|                    |                                             | XP2-40 | 45       | mA    |

|                    |                                             | XP2-5  | 15       | mA    |

|                    |                                             | XP2-8  | 15       | mA    |

| I <sub>CCAUX</sub> | Auxiliary Power Supply Current <sup>6</sup> | XP2-17 | 15       | mA    |

|                    |                                             | XP2-30 | 16       | mA    |

|                    |                                             | XP2-40 | 16       | mA    |

|                    | PLL Power Supply Current (per PLL)          |        | 0.1      | mA    |

| Iccio              | Bank Power Supply Current (per bank)        |        | 2        | mA    |

| ссј                | V <sub>CCJ</sub> Power Supply Current       |        | 0.25     | mA    |

## **Over Recommended Operating Conditions**

1. For further information on supply current, please see TN1139, Power Estimation and Management for LatticeXP2 Devices.

2. Assumes all outputs are tristated, all inputs are configured as LVCMOS and held at the V<sub>CCIO</sub> or GND.

3. Frequency 0 MHz.

4. Pattern represents a "blank" configuration data file.

5.  $T_J = 25^{\circ}C$ , power supplies at nominal voltage.

6. In fpBGA and ftBGA packages the PLLs are connected to and powered from the auxiliary power supply. For these packages, the actual auxiliary supply current is the sum of I<sub>CCAUX</sub> and I<sub>CCPLL</sub>. For csBGA, PQFP and TQFP packages the PLLs are powered independent of the auxiliary power supply.

# LVPECL

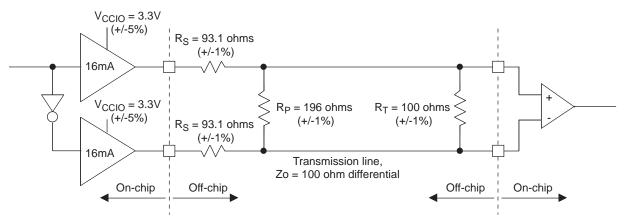

The LatticeXP2 devices support the differential LVPECL standard. This standard is emulated using complementary LVCMOS outputs in conjunction with a parallel resistor across the driver outputs. The LVPECL input standard is supported by the LVDS differential input buffer. The scheme shown in Figure 3-3 is one possible solution for point-to-point signals.

### Figure 3-3. Differential LVPECL

#### Table 3-3. LVPECL DC Conditions<sup>1</sup>

| Parameter         | Description                                         | Typical | Units |

|-------------------|-----------------------------------------------------|---------|-------|

| V <sub>CCIO</sub> | Output Driver Supply (+/-5%)                        | 3.30    | V     |

| Z <sub>OUT</sub>  | Driver Impedance                                    | 10      | Ω     |

| R <sub>S</sub>    | Driver Series Resistor (+/-1%)                      | 93      | Ω     |

| R <sub>P</sub>    | Driver Parallel Resistor (+/-1%)                    | 196     | Ω     |

| R <sub>T</sub>    | Receiver Termination (+/-1%)                        | 100     | Ω     |

| V <sub>OH</sub>   | Output High Voltage (After R <sub>P</sub> )         | 2.05    | V     |

| V <sub>OL</sub>   | Output Low Voltage (After R <sub>P</sub> )          | 1.25    | V     |

| V <sub>OD</sub>   | Output Differential Voltage (After R <sub>P</sub> ) |         | V     |

| V <sub>CM</sub>   | Output Common Mode Voltage                          | 1.65    | V     |

| Z <sub>BACK</sub> | Back Impedance                                      | 100.5   | Ω     |

| I <sub>DC</sub>   | DC Output Current                                   | 12.11   | mA    |

#### **Over Recommended Operating Conditions**

1. For input buffer, see LVDS table.

# RSDS

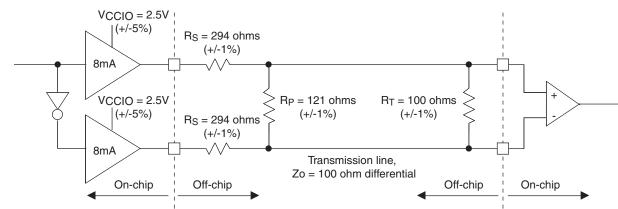

The LatticeXP2 devices support differential RSDS standard. This standard is emulated using complementary LVC-MOS outputs in conjunction with a parallel resistor across the driver outputs. The RSDS input standard is supported by the LVDS differential input buffer. The scheme shown in Figure 3-4 is one possible solution for RSDS standard implementation. Resistor values in Figure 3-4 are industry standard values for 1% resistors.

### Figure 3-4. RSDS (Reduced Swing Differential Standard)

#### Table 3-4. RSDS DC Conditions<sup>1</sup>

| Parameter         | Description                                         | Typical | Units |

|-------------------|-----------------------------------------------------|---------|-------|

| V <sub>CCIO</sub> | Output Driver Supply (+/-5%)                        | 2.50    | V     |

| Z <sub>OUT</sub>  | Driver Impedance                                    | 20      | Ω     |

| R <sub>S</sub>    | Driver Series Resistor (+/-1%)                      | 294     | Ω     |

| R <sub>P</sub>    | Driver Parallel Resistor (+/-1%)                    | 121     | Ω     |

| R <sub>T</sub>    | Receiver Termination (+/-1%)                        | 100     | Ω     |

| V <sub>OH</sub>   | Output High Voltage (After R <sub>P</sub> )         | 1.35    | V     |

| V <sub>OL</sub>   | Output Low Voltage (After R <sub>P</sub> )          | 1.15    | V     |

| V <sub>OD</sub>   | Output Differential Voltage (After R <sub>P</sub> ) | 0.20    | V     |

| V <sub>CM</sub>   | Output Common Mode Voltage                          | 1.25    | V     |

| Z <sub>BACK</sub> | Back Impedance                                      | 101.5   | Ω     |

| I <sub>DC</sub>   | DC Output Current                                   | 3.66    | mA    |

#### **Over Recommended Operating Conditions**

1. For input buffer, see LVDS table.

# **Register-to-Register Performance (Continued)**

| Function                         | -7 Timing | Units |

|----------------------------------|-----------|-------|

| DSP IP Functions                 |           |       |

| 16-Tap Fully-Parallel FIR Filter | 198       | MHz   |

| 1024-pt FFT                      | 221       | MHz   |

| 8X8 Matrix Multiplication        | 196       | MHz   |

1. These timing numbers were generated using the ispLEVER design tool. Exact performance may vary with device, design and tool version. The tool uses internal parameters that have been characterized but are not tested on every device.

# **Derating Timing Tables**

Logic timing provided in the following sections of this data sheet and the Diamond design tools are worst case numbers in the operating range. Actual delays at nominal temperature and voltage for best case process, can be much better than the values given in the tables. The Diamond design tool can provide logic timing numbers at a particular temperature and voltage.

# LatticeXP2 Internal Switching Characteristics<sup>1</sup>

|                         |                                                   | -      | 7     | -      | 6     | -      | 5     |       |

|-------------------------|---------------------------------------------------|--------|-------|--------|-------|--------|-------|-------|

| Parameter               | Description                                       | Min.   | Max.  | Min.   | Max.  | Min.   | Max.  | Units |

|                         | ic Mode Timing                                    |        |       |        |       |        |       | ••    |

| t <sub>LUT4_PFU</sub>   | LUT4 delay (A to D inputs to F<br>output)         | _      | 0.216 | _      | 0.238 | _      | 0.260 | ns    |

| t <sub>LUT6_PFU</sub>   | LUT6 delay (A to D inputs to OFX output)          | _      | 0.304 | _      | 0.399 | _      | 0.494 | ns    |

| t <sub>LSR_PFU</sub>    | Set/Reset to output of PFU (Asyn-<br>chronous)    | _      | 0.720 | _      | 0.769 | —      | 0.818 | ns    |

| t <sub>SUM_PFU</sub>    | Clock to Mux (M0,M1) Input<br>Setup Time          | 0.154  | _     | 0.151  | _     | 0.148  | _     | ns    |

| t <sub>HM_PFU</sub>     | Clock to Mux (M0,M1) Input Hold<br>Time           | -0.061 | _     | -0.057 | _     | -0.053 | _     | ns    |

| t <sub>SUD_PFU</sub>    | Clock to D input setup time                       | 0.061  | —     | 0.077  | —     | 0.093  | —     | ns    |

| t <sub>HD_PFU</sub>     | Clock to D input hold time                        | 0.002  |       | 0.003  |       | 0.003  |       | ns    |

| t <sub>CK2Q_PFU</sub>   | Clock to Q delay, (D-type Register Configuration) | _      | 0.342 | —      | 0.363 | —      | 0.383 | ns    |

| t <sub>RSTREC_PFU</sub> | Asynchronous reset recovery<br>time for PFU Logic | —      | 0.520 | —      | 0.634 | _      | 0.748 | ns    |

| t <sub>RST_PFU</sub>    | Asynchronous reset time for PFU Logic             | —      | 0.720 | —      | 0.769 | _      | 0.818 | ns    |

| PFU Dual Por            | t Memory Mode Timing                              |        |       |        |       |        |       |       |

| t <sub>CORAM_PFU</sub>  | Clock to Output (F Port)                          | —      | 1.082 | —      | 1.267 | —      | 1.452 | ns    |

| t <sub>SUDATA_PFU</sub> | Data Setup Time                                   | -0.206 | —     | -0.240 | _     | -0.274 | —     | ns    |

| t <sub>HDATA_PFU</sub>  | Data Hold Time                                    | 0.239  | _     | 0.275  | _     | 0.312  | —     | ns    |

| t <sub>SUADDR_PFU</sub> | Address Setup Time                                | -0.294 | _     | -0.333 | _     | -0.371 |       | ns    |

| t <sub>HADDR_PFU</sub>  | Address Hold Time                                 | 0.295  | —     | 0.333  | _     | 0.371  | —     | ns    |

| t <sub>SUWREN_PFU</sub> | Write/Read Enable Setup Time                      | -0.146 | —     | -0.169 | _     | -0.193 | —     | ns    |

| t <sub>HWREN_PFU</sub>  | Write/Read Enable Hold Time                       | 0.158  | _     | 0.182  | _     | 0.207  | —     | ns    |

| PIO Input/Out           | put Buffer Timing                                 |        |       |        |       |        |       |       |

| t <sub>IN_PIO</sub>     | Input Buffer Delay (LVCMOS25)                     | _      | 0.858 | —      | 0.766 | —      | 0.674 | ns    |

| t <sub>OUT_PIO</sub>    | Output Buffer Delay (LVCMOS25)                    |        | 1.561 | _      | 1.403 | —      | 1.246 | ns    |

| IOLOGIC Inpu            | it/Output Timing                                  |        |       |        |       |        |       |       |

| t <sub>SUI_PIO</sub>    | Input Register Setup Time (Data Before Clock)     | 0.583  | —     | 0.893  | _     | 1.201  | —     | ns    |

| t <sub>HI_PIO</sub>     | Input Register Hold Time (Data after Clock)       | 0.062  | —     | 0.322  | _     | 0.482  | _     | ns    |

| t <sub>COO_PIO</sub>    | Output Register Clock to Output Delay             | _      | 0.608 | —      | 0.661 | —      | 0.715 | ns    |

| t <sub>SUCE_PIO</sub>   | Input Register Clock Enable<br>Setup Time         | 0.032  | _     | 0.037  | _     | 0.041  | _     | ns    |

| t <sub>HCE_PIO</sub>    | Input Register Clock Enable Hold<br>Time          | -0.022 | _     | -0.025 | _     | -0.028 | _     | ns    |

| t <sub>SULSR_PIO</sub>  | Set/Reset Setup Time                              | 0.184  | —     | 0.201  |       | 0.217  | —     | ns    |

| t <sub>HLSR_PIO</sub>   | Set/Reset Hold Time                               | -0.080 |       | -0.086 |       | -0.093 | _     | ns    |

| t <sub>RSTREC_PIO</sub> | Asynchronous reset recovery time for IO Logic     | 0.228  | _     | 0.247  | _     | 0.266  | _     | ns    |

## **Over Recommended Operating Conditions**

# Lead-Free Packaging

# Commercial

| Part Number       | Voltage | Grade | Package         | Pins | Temp. | LUTs (k) |

|-------------------|---------|-------|-----------------|------|-------|----------|

| LFXP2-5E-5MN132C  | 1.2V    | -5    | Lead-Free csBGA | 132  | COM   | 5        |

| LFXP2-5E-6MN132C  | 1.2V    | -6    | Lead-Free csBGA | 132  | COM   | 5        |

| LFXP2-5E-7MN132C  | 1.2V    | -7    | Lead-Free csBGA | 132  | COM   | 5        |

| LFXP2-5E-5TN144C  | 1.2V    | -5    | Lead-Free TQFP  | 144  | COM   | 5        |

| LFXP2-5E-6TN144C  | 1.2V    | -6    | Lead-Free TQFP  | 144  | COM   | 5        |

| LFXP2-5E-7TN144C  | 1.2V    | -7    | Lead-Free TQFP  | 144  | COM   | 5        |

| LFXP2-5E-5QN208C  | 1.2V    | -5    | Lead-Free PQFP  | 208  | COM   | 5        |

| LFXP2-5E-6QN208C  | 1.2V    | -6    | Lead-Free PQFP  | 208  | COM   | 5        |

| LFXP2-5E-7QN208C  | 1.2V    | -7    | Lead-Free PQFP  | 208  | COM   | 5        |

| LFXP2-5E-5FTN256C | 1.2V    | -5    | Lead-Free ftBGA | 256  | COM   | 5        |

| LFXP2-5E-6FTN256C | 1.2V    | -6    | Lead-Free ftBGA | 256  | COM   | 5        |

| LFXP2-5E-7FTN256C | 1.2V    | -7    | Lead-Free ftBGA | 256  | COM   | 5        |

| Part Number       | Voltage | Grade | Package         | Pins | Temp. | LUTs (k) |

|-------------------|---------|-------|-----------------|------|-------|----------|

| LFXP2-8E-5MN132C  | 1.2V    | -5    | Lead-Free csBGA | 132  | COM   | 8        |

| LFXP2-8E-6MN132C  | 1.2V    | -6    | Lead-Free csBGA | 132  | COM   | 8        |

| LFXP2-8E-7MN132C  | 1.2V    | -7    | Lead-Free csBGA | 132  | COM   | 8        |

| LFXP2-8E-5TN144C  | 1.2V    | -5    | Lead-Free TQFP  | 144  | COM   | 8        |

| LFXP2-8E-6TN144C  | 1.2V    | -6    | Lead-Free TQFP  | 144  | COM   | 8        |

| LFXP2-8E-7TN144C  | 1.2V    | -7    | Lead-Free TQFP  | 144  | COM   | 8        |

| LFXP2-8E-5QN208C  | 1.2V    | -5    | Lead-Free PQFP  | 208  | COM   | 8        |

| LFXP2-8E-6QN208C  | 1.2V    | -6    | Lead-Free PQFP  | 208  | COM   | 8        |

| LFXP2-8E-7QN208C  | 1.2V    | -7    | Lead-Free PQFP  | 208  | COM   | 8        |

| LFXP2-8E-5FTN256C | 1.2V    | -5    | Lead-Free ftBGA | 256  | COM   | 8        |

| LFXP2-8E-6FTN256C | 1.2V    | -6    | Lead-Free ftBGA | 256  | COM   | 8        |

| LFXP2-8E-7FTN256C | 1.2V    | -7    | Lead-Free ftBGA | 256  | COM   | 8        |

| Part Number        | Voltage | Grade | Package         | Pins | Temp. | LUTs (k) |

|--------------------|---------|-------|-----------------|------|-------|----------|

| LFXP2-17E-5QN208C  | 1.2V    | -5    | Lead-Free PQFP  | 208  | COM   | 17       |

| LFXP2-17E-6QN208C  | 1.2V    | -6    | Lead-Free PQFP  | 208  | COM   | 17       |

| LFXP2-17E-7QN208C  | 1.2V    | -7    | Lead-Free PQFP  | 208  | COM   | 17       |

| LFXP2-17E-5FTN256C | 1.2V    | -5    | Lead-Free ftBGA | 256  | COM   | 17       |

| LFXP2-17E-6FTN256C | 1.2V    | -6    | Lead-Free ftBGA | 256  | COM   | 17       |

| LFXP2-17E-7FTN256C | 1.2V    | -7    | Lead-Free ftBGA | 256  | COM   | 17       |

| LFXP2-17E-5FN484C  | 1.2V    | -5    | Lead-Free fpBGA | 484  | COM   | 17       |

| LFXP2-17E-6FN484C  | 1.2V    | -6    | Lead-Free fpBGA | 484  | COM   | 17       |

| LFXP2-17E-7FN484C  | 1.2V    | -7    | Lead-Free fpBGA | 484  | СОМ   | 17       |