## E.J. Lattice Semiconductor Corporation - <u>LFXP2-17E-6FN484C Datasheet</u>

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                       |

|--------------------------------|------------------------------------------------------------------------------|

| Number of LABs/CLBs            | 2125                                                                         |

| Number of Logic Elements/Cells | 17000                                                                        |

| Total RAM Bits                 | 282624                                                                       |

| Number of I/O                  | 358                                                                          |

| Number of Gates                | -                                                                            |

| Voltage - Supply               | 1.14V ~ 1.26V                                                                |

| Mounting Type                  | Surface Mount                                                                |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                              |

| Package / Case                 | 484-BBGA                                                                     |

| Supplier Device Package        | 484-FPBGA (23x23)                                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfxp2-17e-6fn484c |

|                                |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

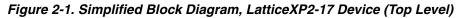

## LatticeXP2 Family Data Sheet Introduction

#### February 2012

#### Features

- flexiFLASH<sup>™</sup> Architecture

- Instant-on

- Infinitely reconfigurable

- Single chip

- FlashBAK<sup>™</sup> technology

- Serial TAG memory

- Design security

#### ■ Live Update Technology

- TransFR™ technology

- Secure updates with 128 bit AES encryption

- Dual-boot with external SPI

#### ■ sysDSP<sup>™</sup> Block

- Three to eight blocks for high performance Multiply and Accumulate

- 12 to 32 18x18 multipliers

- Each block supports one 36x36 multiplier or four 18x18 or eight 9x9 multipliers

#### Embedded and Distributed Memory

- Up to 885 Kbits sysMEM™ EBR

- Up to 83 Kbits Distributed RAM

#### ■ sysCLOCK<sup>™</sup> PLLs

- Up to four analog PLLs per device

- Clock multiply, divide and phase shifting

## ■ Flexible I/O Buffer

- sysIO<sup>™</sup> buffer supports:

- LVCMOS 33/25/18/15/12; LVTTL

- SSTL 33/25/18 class I, II

- HSTL15 class I; HSTL18 class I, II

- PCI

- LVDS, Bus-LVDS, MLVDS, LVPECL, RSDS

#### Pre-engineered Source Synchronous Interfaces

- DDR / DDR2 interfaces up to 200 MHz

- 7:1 LVDS interfaces support display applications

- XGMII

- Density And Package Options

- 5k to 40k LUT4s, 86 to 540 I/Os

- csBGA, TQFP, PQFP, ftBGA and fpBGA packages

- Density migration supported

- Flexible Device Configuration

- SPI (master and slave) Boot Flash Interface

- Dual Boot Image supported

- Soft Error Detect (SED) macro embedded

#### System Level Support

- IEEE 1149.1 and IEEE 1532 Compliant

- · On-chip oscillator for initialization & general use

- Devices operate with 1.2V power supply

| Device                        | XP2-5 | XP2-8 | XP2-17 | XP2-30 | XP2-40 |

|-------------------------------|-------|-------|--------|--------|--------|

| LUTs (K)                      | 5     | 8     | 17     | 29     | 40     |

| Distributed RAM (KBits)       | 10    | 18    | 35     | 56     | 83     |

| EBR SRAM (KBits)              | 166   | 221   | 276    | 387    | 885    |

| EBR SRAM Blocks               | 9     | 12    | 15     | 21     | 48     |

| sysDSP Blocks                 | 3     | 4     | 5      | 7      | 8      |

| 18 x 18 Multipliers           | 12    | 16    | 20     | 28     | 32     |

| V <sub>CC</sub> Voltage       | 1.2   | 1.2   | 1.2    | 1.2    | 1.2    |

| GPLL                          | 2     | 2     | 4      | 4      | 4      |

| Max Available I/O             | 172   | 201   | 358    | 472    | 540    |

| Packages and I/O Combinations |       |       | •      |        | •      |

| 132-Ball csBGA (8 x 8 mm)     | 86    | 86    |        |        |        |

| 144-Pin TQFP (20 x 20 mm)     | 100   | 100   |        |        |        |

| 208-Pin PQFP (28 x 28 mm)     | 146   | 146   | 146    |        |        |

| 256-Ball ftBGA (17 x17 mm)    | 172   | 201   | 201    | 201    |        |

| 484-Ball fpBGA (23 x 23 mm)   |       |       | 358    | 363    | 363    |

| 672-Ball fpBGA (27 x 27 mm)   |       |       |        | 472    | 540    |

#### Table 1-1. LatticeXP2 Family Selection Guide

#### Data Sheet DS1009

<sup>© 2012</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

## **PFU Blocks**

The core of the LatticeXP2 device is made up of logic blocks in two forms, PFUs and PFFs. PFUs can be programmed to perform logic, arithmetic, distributed RAM and distributed ROM functions. PFF blocks can be programmed to perform logic, arithmetic and ROM functions. Except where necessary, the remainder of this data sheet will use the term PFU to refer to both PFU and PFF blocks.

Each PFU block consists of four interconnected slices, numbered Slice 0 through Slice 3, as shown in Figure 2-2. All the interconnections to and from PFU blocks are from routing. There are 50 inputs and 23 outputs associated with each PFU block.

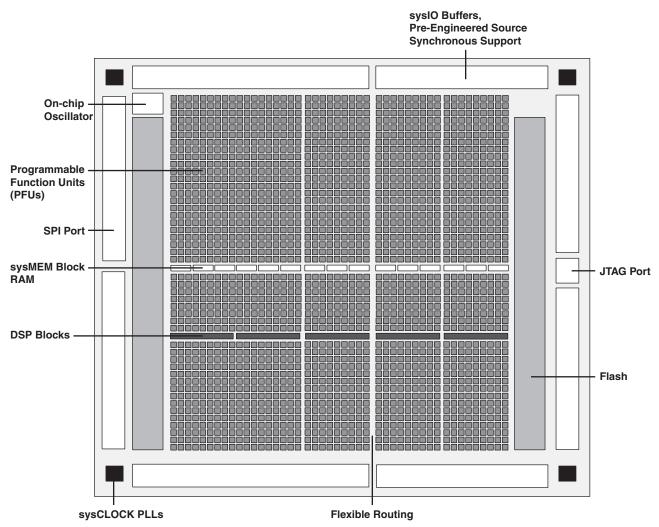

#### Figure 2-16. FlashBAK Technology

#### **Memory Cascading**

Larger and deeper blocks of RAMs can be created using EBR sysMEM Blocks. Typically, the Lattice design tools cascade memory transparently, based on specific design inputs.

#### Single, Dual and Pseudo-Dual Port Modes

In all the sysMEM RAM modes the input data and address for the ports are registered at the input of the memory array. The output data of the memory is optionally registered at the output.

EBR memory supports two forms of write behavior for single port or dual port operation:

- 1. Normal Data on the output appears only during a read cycle. During a write cycle, the data (at the current address) does not appear on the output. This mode is supported for all data widths.

- 2. Write Through A copy of the input data appears at the output of the same port during a write cycle. This mode is supported for all data widths.

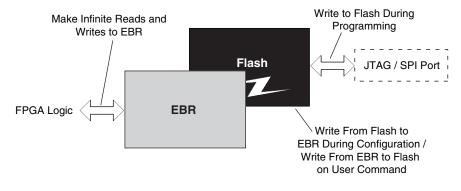

#### **Memory Core Reset**

The memory array in the EBR utilizes latches at the A and B output ports. These latches can be reset asynchronously or synchronously. RSTA and RSTB are local signals, which reset the output latches associated with Port A and Port B respectively. GSRN, the global reset signal, resets both ports. The output data latches and associated resets for both ports are as shown in Figure 2-17.

Figure 2-17. Memory Core Reset

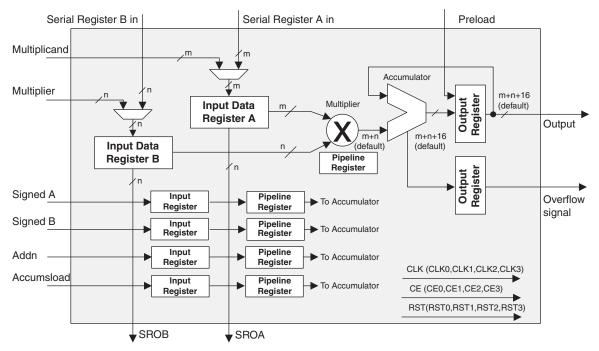

#### MAC sysDSP Element

In this case, the two operands, A and B, are multiplied and the result is added with the previous accumulated value. This accumulated value is available at the output. The user can enable the input and pipeline registers but the output register is always enabled. The output register is used to store the accumulated value. The Accumulators in the DSP blocks in LatticeXP2 family can be initialized dynamically. A registered overflow signal is also available. The overflow conditions are provided later in this document. Figure 2-21 shows the MAC sysDSP element.

#### Figure 2-21. MAC sysDSP

register. Similarly, CE and RST are selected from their four respective sources (CE0, CE1, CE2, CE3 and RST0, RST1, RST2, RST3) at each input register, pipeline register and output register.

#### Signed and Unsigned with Different Widths

The DSP block supports other widths, in addition to x9, x18 and x36 widths, of signed and unsigned multipliers. For unsigned operands, unused upper data bits should be filled to create a valid x9, x18 or x36 operand. For signed two's complement operands, sign extension of the most significant bit should be performed until x9, x18 or x36 width is reached. Table 2-7 provides an example of this.

#### Table 2-7. Sign Extension Example

| Number | Unsigned | Unsigned<br>9-bit | Unsigned<br>18-bit | Signed | Two's Complement<br>Signed 9 Bits | Two's Complement<br>Signed 18 Bits |

|--------|----------|-------------------|--------------------|--------|-----------------------------------|------------------------------------|

| +5     | 0101     | 000000101         | 00000000000000101  | 0101   | 00000101                          | 00000000000000101                  |

| -6     | N/A      | N/A               | N/A                | 1010   | 111111010                         | 1111111111111111010                |

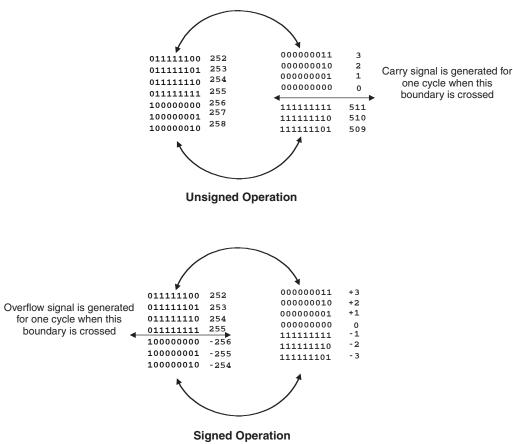

#### **OVERFLOW Flag from MAC**

The sysDSP block provides an overflow output to indicate that the accumulator has overflowed. "Roll-over" occurs and an overflow signal is indicated when any of the following is true: two unsigned numbers are added and the result is a smaller number than the accumulator, two positive numbers are added with a negative sum or two negative numbers are added with a positive sum. Note that when overflow occurs the overflow flag is present for only one cycle. By counting these overflow pulses in FPGA logic, larger accumulators can be constructed. The conditions for the overflow signal for signed and unsigned operands are listed in Figure 2-24.

#### Figure 2-24. Accumulator Overflow/Underflow

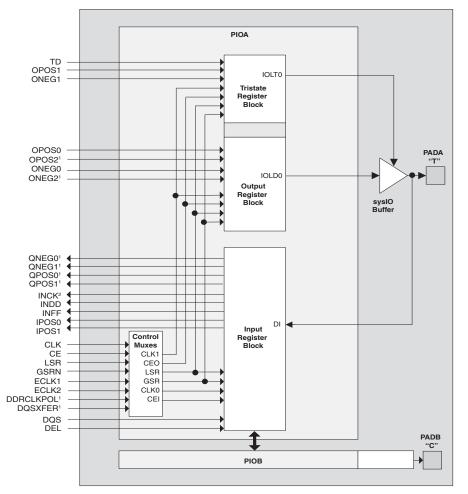

## Programmable I/O Cells (PIC)

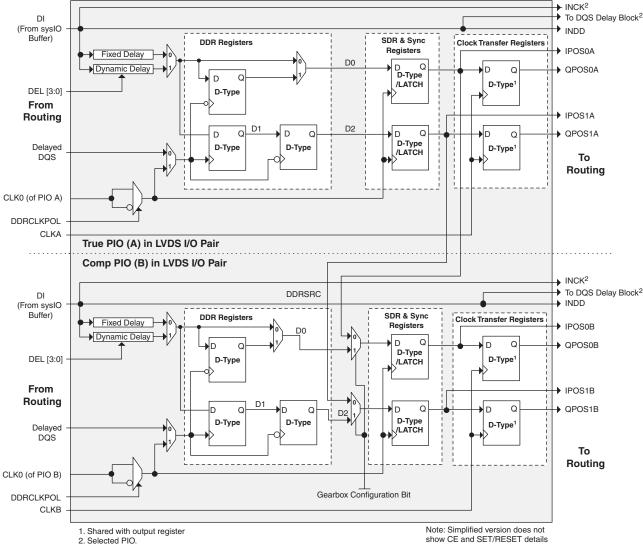

Each PIC contains two PIOs connected to their respective sysIO buffers as shown in Figure 2-25. The PIO Block supplies the output data (DO) and the tri-state control signal (TO) to the sysIO buffer and receives input from the buffer. Table 2-11 provides the PIO signal list.

#### Figure 2-25. PIC Diagram

Signals are available on left/right/bottom edges only.

Selected blocks.

Two adjacent PIOs can be joined to provide a differential I/O pair (labeled as "T" and "C") as shown in Figure 2-25. The PAD Labels "T" and "C" distinguish the two PIOs. Approximately 50% of the PIO pairs on the left and right edges of the device can be configured as true LVDS outputs. All I/O pairs can operate as inputs.

The signal DDRCLKPOL controls the polarity of the clock used in the synchronization registers. It ensures adequate timing when data is transferred from the DQS to system clock domain. For further discussion on this topic, see the DDR Memory section of this data sheet.

#### **Output Register Block**

The output register block provides the ability to register signals from the core of the device before they are passed to the sysIO buffers. The blocks on the PIOs on the left, right and bottom contain registers for SDR operation that are combined with an additional latch for DDR operation. Figure 2-27 shows the diagram of the Output Register Block for PIOs.

In SDR mode, ONEG0 feeds one of the flip-flops that then feeds the output. The flip-flop can be configured as a Dtype or latch. In DDR mode, ONEG0 and OPOS0 are fed into registers on the positive edge of the clock. At the next clock cycle the registered OPOS0 is latched. A multiplexer running off the same clock cycle selects the correct register to feed the output (D0).

By combining output blocks of the complementary PIOs and sharing some registers from input blocks, a gearbox function can be implemented, to take four data streams ONEG0A, ONEG1A, ONEG1B and ONEG1B. Figure 2-27

LatticeXP2 devices contain two types of sysIO buffer pairs.

#### 1. Top and Bottom (Banks 0, 1, 4 and 5) sysIO Buffer Pairs (Single-Ended Outputs Only)

The sysIO buffer pairs in the top banks of the device consist of two single-ended output drivers and two sets of single-ended input buffers (both ratioed and referenced). One of the referenced input buffers can also be configured as a differential input.

The two pads in the pair are described as "true" and "comp", where the true pad is associated with the positive side of the differential input buffer and the comp (complementary) pad is associated with the negative side of the differential input buffer.

Only the I/Os on the top and bottom banks have programmable PCI clamps.

2. Left and Right (Banks 2, 3, 6 and 7) sysIO Buffer Pairs (50% Differential and 100% Single-Ended Outputs) The sysIO buffer pairs in the left and right banks of the device consist of two single-ended output drivers, two sets of single-ended input buffers (both ratioed and referenced) and one differential output driver. One of the referenced input buffers can also be configured as a differential input.

The two pads in the pair are described as "true" and "comp", where the true pad is associated with the positive side of the differential I/O, and the comp pad is associated with the negative side of the differential I/O.

LVDS differential output drivers are available on 50% of the buffer pairs on the left and right banks.

#### Typical sysIO I/O Behavior During Power-up

The internal power-on-reset (POR) signal is deactivated when  $V_{CC, V} C_{CCONFIG} (V_{CCIO7})$  and  $V_{CCAUX}$  have reached satisfactory levels. After the POR signal is deactivated, the FPGA core logic becomes active. It is the user's responsibility to ensure that all other  $V_{CCIO}$  banks are active with valid input logic levels to properly control the output logic states of all the I/O banks that are critical to the application. During power up and before the FPGA core logic becomes active, all user I/Os will be high-impedance with weak pull-up. Please refer to TN1136, <u>LatticeXP2 sysIO</u> Usage Guide for additional information.

The V<sub>CC</sub> and V<sub>CCAUX</sub> supply the power to the FPGA core fabric, whereas the V<sub>CCIO</sub> supplies power to the I/O buffers. In order to simplify system design while providing consistent and predictable I/O behavior, it is recommended that the I/O buffers be powered-up prior to the FPGA core fabric. V<sub>CCIO</sub> supplies should be powered-up before or together with the V<sub>CC</sub> and V<sub>CCAUX</sub> supplies.

#### Supported sysIO Standards

The LatticeXP2 sysIO buffer supports both single-ended and differential standards. Single-ended standards can be further subdivided into LVCMOS, LVTTL and other standards. The buffers support the LVTTL, LVCMOS 1.2V, 1.5V, 1.8V, 2.5V and 3.3V standards. In the LVCMOS and LVTTL modes, the buffer has individual configuration options for drive strength, bus maintenance (weak pull-up, weak pull-down, or a bus-keeper latch) and open drain. Other single-ended standards supported include SSTL and HSTL. Differential standards supported include LVDS, MLVDS, BLVDS, LVPECL, RSDS, differential SSTL and differential HSTL. Tables 2-12 and 2-13 show the I/O standards (together with their supply and reference voltages) supported by LatticeXP2 devices. For further information on utilizing the sysIO buffer to support a variety of standards please see TN1136, LatticeXP2 sysIO Usage Guide.

- 1. Unlocked

- 2. Key Locked Presenting the key through the programming interface allows the device to be unlocked.

- 3. Permanently Locked The device is permanently locked.

To further complement the security of the device a One Time Programmable (OTP) mode is available. Once the device is set in this mode it is not possible to erase or re-program the Flash portion of the device.

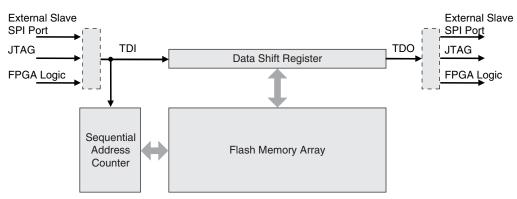

#### Serial TAG Memory

LatticeXP2 devices offer 0.6 to 3.3kbits of Flash memory in the form of Serial TAG memory. The TAG memory is an area of the on-chip Flash that can be used for non-volatile storage including electronic ID codes, version codes, date stamps, asset IDs and calibration settings. A block diagram of the TAG memory is shown in Figure 2-34. The TAG memory is accessed in the same way as external SPI Flash and it can be read or programmed either through JTAG, an external Slave SPI Port, or directly from FPGA logic. To read the TAG memory, a start address is specified and the entire TAG memory contents are read sequentially in a first-in-first-out manner. The TAG memory is always accessible regardless of the device security settings. For more information, see TN1137, LatticeXP2 Memory Usage Guide and TN1141, LatticeXP2 sysCONFIG Usage Guide.

#### Figure 2-34. Serial TAG Memory Diagram

#### Live Update Technology

Many applications require field updates of the FPGA. LatticeXP2 devices provide three features that enable this configuration to be done in a secure and failsafe manner while minimizing impact on system operation.

#### 1. **Decryption Support**

LatticeXP2 devices provide on-chip, non-volatile key storage to support decryption of a 128-bit AES encrypted bitstream, securing designs and deterring design piracy.

#### 2. TransFR (Transparent Field Reconfiguration)

TransFR I/O (TFR) is a unique Lattice technology that allows users to update their logic in the field without interrupting system operation using a single ispVM command. TransFR I/O allows I/O states to be frozen during device configuration. This allows the device to be field updated with a minimum of system disruption and downtime. For more information please see TN1087, <u>Minimizing System Interruption During Configuration</u>. Using TransFR Technology.

#### 3. Dual Boot Image Support

Dual boot images are supported for applications requiring reliable remote updates of configuration data for the system FPGA. After the system is running with a basic configuration, a new boot image can be downloaded remotely and stored in a separate location in the configuration storage device. Any time after the update the LatticeXP2 can be re-booted from this new configuration file. If there is a problem such as corrupt data during download or incorrect version number with this new boot image, the LatticeXP2 device can revert back to the

# LatticeXP2 Family Data Sheet DC and Switching Characteristics

#### September 2014

Data Sheet DS1009

## Absolute Maximum Ratings<sup>1, 2, 3</sup>

| Supply Voltage V <sub>CC</sub> 0.5 to 1.32V                                  |

|------------------------------------------------------------------------------|

| Supply Voltage $V_{CCAUX} \dots \dots \dots 0.5$ to $3.75V$                  |

| Supply Voltage $V_{CCJ} \dots \dots \dots \dots 0.5$ to $3.75V$              |

| Supply Voltage $V_{\mbox{\scriptsize CCPLL}}{}^4.\ldots\ldots$ -0.5 to 3.75V |

| Output Supply Voltage $V_{CCIO}$ $\ldots$ 0.5 to 3.75V                       |

| Input or I/O Tristate Voltage Applied $^5,\ldots\ldots$ -0.5 to 3.75V        |

| Storage Temperature (Ambient) $\ldots \ldots$ -65 to 150°C                   |

| Junction Temperature Under Bias (Tj) +125°C                                  |

1. Stress above those listed under the "Absolute Maximum Ratings" may cause permanent damage to the device. Functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

2. Compliance with the Lattice <u>Thermal Management</u> document is required.

3. All voltages referenced to GND.

4. V<sub>CCPLL</sub> only available on csBGA, PQFP and TQFP packages.

5. Overshoot and undershoot of -2V to ( $V_{IHMAX}$  + 2) volts is permitted for a duration of <20 ns.

## **Recommended Operating Conditions**

| Symbol                               | Parameter                                       | Min.  | Max.  | Units |

|--------------------------------------|-------------------------------------------------|-------|-------|-------|

| V <sub>CC</sub>                      | Core Supply Voltage                             | 1.14  | 1.26  | V     |

| V <sub>CCAUX</sub> <sup>4, 5</sup>   | Auxiliary Supply Voltage                        | 3.135 | 3.465 | V     |

| V <sub>CCPLL</sub> <sup>1</sup>      | PLL Supply Voltage                              | 3.135 | 3.465 | V     |

| V <sub>CCIO</sub> <sup>2, 3, 4</sup> | I/O Driver Supply Voltage                       | 1.14  | 3.465 | V     |

| V <sub>CCJ</sub> <sup>2</sup>        | Supply Voltage for IEEE 1149.1 Test Access Port | 1.14  | 3.465 | V     |

| t <sub>JCOM</sub>                    | Junction Temperature, Commercial Operation      | 0     | 85    | °C    |

| t <sub>JIND</sub>                    | Junction Temperature, Industrial Operation      | -40   | 100   | °C    |

1.  $V_{CCPLL}$  only available on csBGA, PQFP and TQFP packages.

If V<sub>CCIO</sub> or V<sub>CCJ</sub> is set to 1.2 V, they must be connected to the same power supply as V<sub>CC</sub>. If V<sub>CCIO</sub> or V<sub>CCJ</sub> is set to 3.3V, they must be connected to the same power supply as V<sub>CCAUX</sub>.

3. See recommended voltages by I/O standard in subsequent table.

4. To ensure proper I/O behavior,  $V_{CCIO}$  must be turned off at the same time or earlier than  $V_{CCAUX}$ .

5. In fpBGA and ftBGA packages, the PLLs are connected to, and powered from, the auxiliary power supply.

## **On-Chip Flash Memory Specifications**

| Symbol   | Parameter                                                        | Max.    | Units  |

|----------|------------------------------------------------------------------|---------|--------|

|          | Flash Programming Cycles per t <sub>RETENTION</sub> <sup>1</sup> | 10,000  | Cvcles |

| NPROGCYC | Flash Functional Programming Cycles                              | 100,000 | Oycles |

1. The minimum data retention, t<sub>RETENTION</sub>, is 20 years.

<sup>© 2014</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

## Hot Socketing Specifications<sup>1, 2, 3, 4</sup>

| Symbol          | Parameter                    | Condition                        | Min. | Тур. | Max. | Units |

|-----------------|------------------------------|----------------------------------|------|------|------|-------|

| I <sub>DK</sub> | Input or I/O Leakage Current | $0 \le V_{IN} \le V_{IH}$ (MAX.) | _    | _    | +/-1 | mA    |

1. Insensitive to sequence of  $V_{CC}$ ,  $V_{CCAUX}$  and  $V_{CCIO}$ . However, assumes monotonic rise/fall rates for  $V_{CC}$ ,  $V_{CCAUX}$  and  $V_{CCIO}$ .

2.  $0 \le V_{CC} \le V_{CC}$  (MAX),  $0 \le V_{CCIO} \le V_{CCIO}$  (MAX) or  $0 \le V_{CCAUX} \le V_{CCAUX}$  (MAX).

3.  $I_{DK}$  is additive to  $I_{PU}$ ,  $I_{PW}$  or  $I_{BH}$ .

4. LVCMOS and LVTTL only.

## **ESD** Performance

Please refer to the <u>LatticeXP2 Product Family Qualification Summary</u> for complete qualification data, including ESD performance.

## **DC Electrical Characteristics**

| Symbol                              | Parameter                        | Condition                                                                                             | Min.           | Тур. | Max.                  | Units |

|-------------------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------|----------------|------|-----------------------|-------|

| I <sub>IL</sub> , I <sub>IH</sub> 1 | Input or I/O Low Leakage         | $0 \le V_{IN} \le V_{CCIO}$                                                                           | —              |      | 10                    | μA    |

| 'IL', 'IH                           | Input of 1/O Low Leakage         | $V_{CCIO} \le V_{IN} \le V_{IH}$ (MAX)                                                                | —              | _    | 150                   | μΑ    |

| I <sub>PU</sub>                     | I/O Active Pull-up Current       | $0 \le V_{IN} \le 0.7 \ V_{CCIO}$                                                                     | -30            | _    | -150                  | μΑ    |

| I <sub>PD</sub>                     | I/O Active Pull-down Current     | $V_{IL}$ (MAX) $\leq V_{IN} \leq V_{CCIO}$                                                            | 30             |      | 210                   | μA    |

| I <sub>BHLS</sub>                   | Bus Hold Low Sustaining Current  | $V_{IN} = V_{IL}$ (MAX)                                                                               | 30             | _    | —                     | μΑ    |

| I <sub>BHHS</sub>                   | Bus Hold High Sustaining Current | $V_{IN} = 0.7 V_{CCIO}$                                                                               | -30            | _    | —                     | μΑ    |

| I <sub>BHLO</sub>                   | Bus Hold Low Overdrive Current   | $0 \le V_{IN} \le V_{CCIO}$                                                                           | —              | _    | 210                   | μΑ    |

| I <sub>BHHO</sub>                   | Bus Hold High Overdrive Current  | $0 \le V_{IN} \le V_{CCIO}$                                                                           | —              | _    | -150                  | μΑ    |

| V <sub>BHT</sub>                    | Bus Hold Trip Points             |                                                                                                       | $V_{IL}$ (MAX) | _    | V <sub>IH</sub> (MIN) | V     |

| C1                                  | I/O Capacitance <sup>2</sup>     | $V_{CCIO} = 3.3V, 2.5V, 1.8V, 1.5V, 1.2V, V_{CC} = 1.2V, V_{IO} = 0 \text{ to } V_{IH} \text{ (MAX)}$ | _              | 8    | _                     | pf    |

| C2                                  | Dedicated Input Capacitance      | $V_{CCIO} = 3.3V, 2.5V, 1.8V, 1.5V, 1.2V, V_{CC} = 1.2V, V_{IO} = 0 \text{ to } V_{IH} \text{ (MAX)}$ | —              | 6    | —                     | pf    |

#### **Over Recommended Operating Conditions**

1. Input or I/O leakage current is measured with the pin configured as an input or as an I/O with the output driver tri-stated. It is not measured with the output driver active. Bus maintenance circuits are disabled.

2. T<sub>A</sub> 25°C, f = 1.0 MHz.

## sysIO Differential Electrical Characteristics LVDS

| Parameter                         | Description                                    | Test Conditions                                                | Min.   | Тур. | Max.  | Units |

|-----------------------------------|------------------------------------------------|----------------------------------------------------------------|--------|------|-------|-------|

| V <sub>INP</sub> V <sub>INM</sub> | Input Voltage                                  |                                                                | 0      |      | 2.4   | V     |

| V <sub>CM</sub>                   | Input Common Mode Voltage                      | Half the Sum of the Two Inputs                                 | 0.05   |      | 2.35  | V     |

| V <sub>THD</sub>                  | Differential Input Threshold                   | Difference Between the Two Inputs                              | +/-100 |      |       | mV    |

| I <sub>IN</sub>                   | Input Current                                  | Power On or Power Off                                          | _      | _    | +/-10 | μΑ    |

| V <sub>OH</sub>                   | Output High Voltage for $V_{OP}$ or $V_{OM}$   | R <sub>T</sub> = 100 Ohm                                       | _      | 1.38 | 1.60  | V     |

| V <sub>OL</sub>                   | Output Low Voltage for $V_{OP}$ or $V_{OM}$    | R <sub>T</sub> = 100 Ohm                                       | 0.9V   | 1.03 |       | V     |

| V <sub>OD</sub>                   | Output Voltage Differential                    | (V <sub>OP</sub> - V <sub>OM</sub> ), R <sub>T</sub> = 100 Ohm | 250    | 350  | 450   | mV    |

| ΔV <sub>OD</sub>                  | Change in V <sub>OD</sub> Between High and Low |                                                                | _      | _    | 50    | mV    |

| V <sub>OS</sub>                   | Output Voltage Offset                          | $(V_{OP} + V_{OM})/2, R_{T} = 100 \text{ Ohm}$                 | 1.125  | 1.20 | 1.375 | V     |

| $\Delta V_{OS}$                   | Change in V <sub>OS</sub> Between H and L      |                                                                | _      |      | 50    | mV    |

| I <sub>SA</sub>                   | Output Short Circuit Current                   | V <sub>OD</sub> = 0V Driver Outputs Shorted to<br>Ground       | —      | _    | 24    | mA    |

| I <sub>SAB</sub>                  | Output Short Circuit Current                   | V <sub>OD</sub> = 0V Driver Outputs Shorted to<br>Each Other   | _      | _    | 12    | mA    |

#### **Over Recommended Operating Conditions**

#### Differential HSTL and SSTL

Differential HSTL and SSTL outputs are implemented as a pair of complementary single-ended outputs. All allowable single-ended output classes (class I and class II) are supported in this mode.

For further information on LVPECL, RSDS, MLVDS, BLVDS and other differential interfaces please see details in additional technical notes listed at the end of this data sheet.

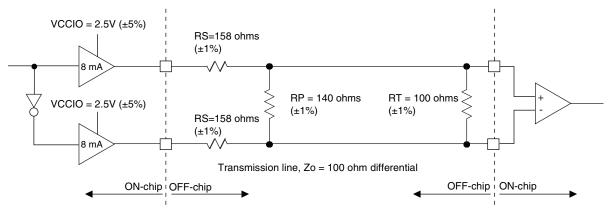

#### LVDS25E

The top and bottom sides of LatticeXP2 devices support LVDS outputs via emulated complementary LVCMOS outputs in conjunction with a parallel resistor across the driver outputs. The scheme shown in Figure 3-1 is one possible solution for point-to-point signals.

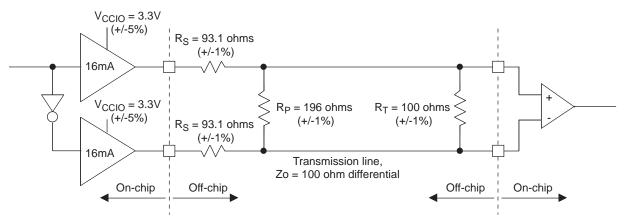

#### LVPECL

The LatticeXP2 devices support the differential LVPECL standard. This standard is emulated using complementary LVCMOS outputs in conjunction with a parallel resistor across the driver outputs. The LVPECL input standard is supported by the LVDS differential input buffer. The scheme shown in Figure 3-3 is one possible solution for point-to-point signals.

#### Figure 3-3. Differential LVPECL

#### Table 3-3. LVPECL DC Conditions<sup>1</sup>

| Parameter         | Description                                         | Typical | Units |

|-------------------|-----------------------------------------------------|---------|-------|

| V <sub>CCIO</sub> | Output Driver Supply (+/-5%)                        | 3.30    | V     |

| Z <sub>OUT</sub>  | Driver Impedance                                    | 10      | Ω     |

| R <sub>S</sub>    | Driver Series Resistor (+/-1%)                      | 93      | Ω     |

| R <sub>P</sub>    | Driver Parallel Resistor (+/-1%)                    | 196     | Ω     |

| R <sub>T</sub>    | Receiver Termination (+/-1%)                        | 100     | Ω     |

| V <sub>OH</sub>   | Output High Voltage (After R <sub>P</sub> )         | 2.05    | V     |

| V <sub>OL</sub>   | Output Low Voltage (After R <sub>P</sub> )          | 1.25    | V     |

| V <sub>OD</sub>   | Output Differential Voltage (After R <sub>P</sub> ) | 0.80    | V     |

| V <sub>CM</sub>   | Output Common Mode Voltage                          | 1.65    | V     |

| Z <sub>BACK</sub> | Back Impedance                                      | 100.5   | Ω     |

| I <sub>DC</sub>   | DC Output Current                                   | 12.11   | mA    |

#### **Over Recommended Operating Conditions**

1. For input buffer, see LVDS table.

#### RSDS

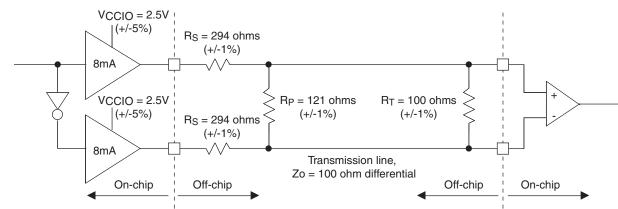

The LatticeXP2 devices support differential RSDS standard. This standard is emulated using complementary LVC-MOS outputs in conjunction with a parallel resistor across the driver outputs. The RSDS input standard is supported by the LVDS differential input buffer. The scheme shown in Figure 3-4 is one possible solution for RSDS standard implementation. Resistor values in Figure 3-4 are industry standard values for 1% resistors.

#### Figure 3-4. RSDS (Reduced Swing Differential Standard)

#### Table 3-4. RSDS DC Conditions<sup>1</sup>

| Parameter         | Description                                         | Typical | Units |

|-------------------|-----------------------------------------------------|---------|-------|

| V <sub>CCIO</sub> | Output Driver Supply (+/-5%)                        | 2.50    | V     |

| Z <sub>OUT</sub>  | Driver Impedance                                    | 20      | Ω     |

| R <sub>S</sub>    | Driver Series Resistor (+/-1%)                      | 294     | Ω     |

| R <sub>P</sub>    | Driver Parallel Resistor (+/-1%)                    | 121     | Ω     |

| R <sub>T</sub>    | Receiver Termination (+/-1%)                        | 100     | Ω     |

| V <sub>OH</sub>   | Output High Voltage (After R <sub>P</sub> )         | 1.35    | V     |

| V <sub>OL</sub>   | Output Low Voltage (After R <sub>P</sub> )          | 1.15    | V     |

| V <sub>OD</sub>   | Output Differential Voltage (After R <sub>P</sub> ) | 0.20    | V     |

| V <sub>CM</sub>   | Output Common Mode Voltage                          | 1.25    | V     |

| Z <sub>BACK</sub> | Back Impedance                                      | 101.5   | Ω     |

| I <sub>DC</sub>   | DC Output Current                                   | 3.66    | mA    |

#### **Over Recommended Operating Conditions**

1. For input buffer, see LVDS table.

### **Register-to-Register Performance (Continued)**

| Function                         | -7 Timing | Units |

|----------------------------------|-----------|-------|

| DSP IP Functions                 |           |       |

| 16-Tap Fully-Parallel FIR Filter | 198       | MHz   |

| 1024-pt FFT                      | 221       | MHz   |

| 8X8 Matrix Multiplication        | 196       | MHz   |

1. These timing numbers were generated using the ispLEVER design tool. Exact performance may vary with device, design and tool version. The tool uses internal parameters that have been characterized but are not tested on every device.

## **Derating Timing Tables**

Logic timing provided in the following sections of this data sheet and the Diamond design tools are worst case numbers in the operating range. Actual delays at nominal temperature and voltage for best case process, can be much better than the values given in the tables. The Diamond design tool can provide logic timing numbers at a particular temperature and voltage.

## LatticeXP2 External Switching Characteristics (Continued)

|                          |                                                                  |        | -    | 7    | -    | 6    | -5   |      |       |

|--------------------------|------------------------------------------------------------------|--------|------|------|------|------|------|------|-------|

| Parameter                | Description                                                      | Device | Min. | Max. | Min. | Max. | Min. | Max. | Units |

|                          |                                                                  | XP2-5  | 0.00 | —    | 0.00 | —    | 0.00 | —    | ns    |

|                          |                                                                  | XP2-8  | 0.00 | —    | 0.00 | —    | 0.00 | —    | ns    |

| t <sub>H_DELPLL</sub>    | Clock to Data Hold - PIO Input<br>Register with Input Data Delay | XP2-17 | 0.00 | —    | 0.00 | —    | 0.00 | —    | ns    |

|                          |                                                                  | XP2-30 | 0.00 |      | 0.00 | —    | 0.00 | —    | ns    |

|                          |                                                                  | XP2-40 | 0.00 |      | 0.00 | —    | 0.00 |      | ns    |

| DDR <sup>2</sup> and DDI | R2 <sup>3</sup> I/O Pin Parameters                               |        | •    |      |      | •    | •    |      | •     |

| t <sub>DVADQ</sub>       | Data Valid After DQS<br>(DDR Read)                               | XP2    | _    | 0.29 | —    | 0.29 | —    | 0.29 | UI    |

| t <sub>DVEDQ</sub>       | Data Hold After DQS<br>(DDR Read)                                | XP2    | 0.71 | _    | 0.71 | —    | 0.71 | _    | UI    |

| t <sub>DQVBS</sub>       | Data Valid Before DQS                                            | XP2    | 0.25 | —    | 0.25 | —    | 0.25 | —    | UI    |

| t <sub>DQVAS</sub>       | Data Valid After DQS                                             | XP2    | 0.25 |      | 0.25 | —    | 0.25 |      | UI    |

| f <sub>MAX_DDR</sub>     | DDR Clock Frequency                                              | XP2    | 95   | 200  | 95   | 166  | 95   | 133  | MHz   |

| f <sub>MAX_DDR2</sub>    | DDR Clock Frequency                                              | XP2    | 133  | 200  | 133  | 200  | 133  | 166  | MHz   |

| Primary Clock            | (                                                                |        |      |      |      |      |      |      |       |

| f <sub>MAX_PRI</sub>     | Frequency for Primary Clock<br>Tree                              | XP2    | _    | 420  | —    | 357  | —    | 311  | MHz   |

| t <sub>W_PRI</sub>       | Clock Pulse Width for Primary<br>Clock                           | XP2    | 1    | _    | 1    | —    | 1    | _    | ns    |

| t <sub>SKEW_PRI</sub>    | Primary Clock Skew Within a Bank                                 | XP2    | _    | 160  | —    | 160  | —    | 160  | ps    |

| Edge Clock (E            | CLK1 and ECLK2)                                                  |        | •    |      |      | •    | •    |      | •     |

| fMAX_ECLK                | Frequency for Edge Clock                                         | XP2    | —    | 420  | —    | 357  | —    | 311  | MHz   |

| <sup>t</sup> w_eclk      | Clock Pulse Width for Edge<br>Clock                              | XP2    | 1    | —    | 1    | —    | 1    | —    | ns    |

| t <sub>SKEW_ECLK</sub>   | Edge Clock Skew Within an<br>Edge of the Device                  | XP2    | -    | 130  | _    | 130  | —    | 130  | ps    |

#### **Over Recommended Operating Conditions**

1. General timing numbers based on LVCMOS 2.5, 12mA, 0pf load.

2. DDR timing numbers based on SSTL25.

3. DDR2 timing numbers based on SSTL18.

## LatticeXP2 Family Timing Adders<sup>1, 2, 3, 4</sup> (Continued)

| Buffer Type   | Description                              | -7    | -6    | -5    | Units |

|---------------|------------------------------------------|-------|-------|-------|-------|

| HSTL15_I      | HSTL_15 class I 4mA drive                | 0.32  | 0.69  | 1.06  | ns    |

| HSTL15D_I     | Differential HSTL 15 class I 4mA drive   | 0.32  | 0.69  | 1.06  | ns    |

| SSTL33_I      | SSTL_3 class I                           | -0.25 | 0.05  | 0.35  | ns    |

| SSTL33_II     | SSTL_3 class II                          | -0.31 | -0.02 | 0.27  | ns    |

| SSTL33D_I     | Differential SSTL_3 class I              | -0.25 | 0.05  | 0.35  | ns    |

| SSTL33D_II    | Differential SSTL_3 class II             | -0.31 | -0.02 | 0.27  | ns    |

| SSTL25_I      | SSTL_2 class I 8mA drive                 | -0.25 | 0.02  | 0.30  | ns    |

| SSTL25_II     | SSTL_2 class II 16mA drive               | -0.28 | 0.00  | 0.28  | ns    |

| SSTL25D_I     | Differential SSTL_2 class I 8mA drive    | -0.25 | 0.02  | 0.30  | ns    |

| SSTL25D_II    | Differential SSTL_2 class II 16mA drive  | -0.28 | 0.00  | 0.28  | ns    |

| SSTL18_I      | SSTL_1.8 class I                         | -0.17 | 0.13  | 0.43  | ns    |

| SSTL18_II     | SSTL_1.8 class II 8mA drive              | -0.18 | 0.12  | 0.42  | ns    |

| SSTL18D_I     | Differential SSTL_1.8 class I            | -0.17 | 0.13  | 0.43  | ns    |

| SSTL18D_II    | Differential SSTL_1.8 class II 8mA drive | -0.18 | 0.12  | 0.42  | ns    |

| LVTTL33_4mA   | LVTTL 4mA drive                          | -0.37 | -0.05 | 0.26  | ns    |

| LVTTL33_8mA   | LVTTL 8mA drive                          | -0.45 | -0.18 | 0.10  | ns    |

| LVTTL33_12mA  | LVTTL 12mA drive                         | -0.52 | -0.24 | 0.04  | ns    |

| LVTTL33_16mA  | LVTTL 16mA drive                         | -0.43 | -0.14 | 0.14  | ns    |

| LVTTL33_20mA  | LVTTL 20mA drive                         | -0.46 | -0.18 | 0.09  | ns    |

| LVCMOS33_4mA  | LVCMOS 3.3 4mA drive, fast slew rate     | -0.37 | -0.05 | 0.26  | ns    |

| LVCMOS33_8mA  | LVCMOS 3.3 8mA drive, fast slew rate     | -0.45 | -0.18 | 0.10  | ns    |

| LVCMOS33_12mA | LVCMOS 3.3 12mA drive, fast slew rate    | -0.52 | -0.24 | 0.04  | ns    |

| LVCMOS33_16mA | LVCMOS 3.3 16mA drive, fast slew rate    | -0.43 | -0.14 | 0.14  | ns    |

| LVCMOS33_20mA | LVCMOS 3.3 20mA drive, fast slew rate    | -0.46 | -0.18 | 0.09  | ns    |

| LVCMOS25_4mA  | LVCMOS 2.5 4mA drive, fast slew rate     | -0.42 | -0.15 | 0.13  | ns    |

| LVCMOS25_8mA  | LVCMOS 2.5 8mA drive, fast slew rate     | -0.48 | -0.21 | 0.05  | ns    |

| LVCMOS25_12mA | LVCMOS 2.5 12mA drive, fast slew rate    | 0.00  | 0.00  | 0.00  | ns    |

| LVCMOS25_16mA | LVCMOS 2.5 16mA drive, fast slew rate    | -0.45 | -0.18 | 0.08  | ns    |

| LVCMOS25_20mA | LVCMOS 2.5 20mA drive, fast slew rate    | -0.49 | -0.22 | 0.04  | ns    |

| LVCMOS18_4mA  | LVCMOS 1.8 4mA drive, fast slew rate     | -0.46 | -0.18 | 0.10  | ns    |

| LVCMOS18_8mA  | LVCMOS 1.8 8mA drive, fast slew rate     | -0.52 | -0.25 | 0.02  | ns    |

| LVCMOS18_12mA | LVCMOS 1.8 12mA drive, fast slew rate    | -0.56 | -0.30 | -0.03 | ns    |

| LVCMOS18_16mA | LVCMOS 1.8 16mA drive, fast slew rate    | -0.50 | -0.24 | 0.03  | ns    |

| LVCMOS15_4mA  | LVCMOS 1.5 4mA drive, fast slew rate     | -0.45 | -0.17 | 0.11  | ns    |

| LVCMOS15_8mA  | LVCMOS 1.5 8mA drive, fast slew rate     | -0.53 | -0.26 | 0.00  | ns    |

| LVCMOS12_2mA  | LVCMOS 1.2 2mA drive, fast slew rate     | -0.46 | -0.19 | 0.08  | ns    |

| LVCMOS12_6mA  | LVCMOS 1.2 6mA drive, fast slew rate     | -0.55 | -0.29 | -0.02 | ns    |

| LVCMOS33_4mA  | LVCMOS 3.3 4mA drive, slow slew rate     | 0.98  | 1.41  | 1.84  | ns    |

| LVCMOS33_8mA  | LVCMOS 3.3 8mA drive, slow slew rate     | 0.74  | 1.16  | 1.58  | ns    |

| LVCMOS33_12mA | LVCMOS 3.3 12mA drive, slow slew rate    | 0.56  | 0.97  | 1.38  | ns    |

| LVCMOS33_16mA | LVCMOS 3.3 16mA drive, slow slew rate    | 0.77  | 1.19  | 1.61  | ns    |

| LVCMOS33_20mA | LVCMOS 3.3 20mA drive, slow slew rate    | 0.57  | 0.98  | 1.40  | ns    |

#### **Over Recommended Operating Conditions**

## Pin Information Summary (Cont.)

| XP2-5                               |       |              |             | XP2-8       |              |              | XP2-17      |             | XP2-30       |             | XP2-40       |              |              |              |              |              |              |

|-------------------------------------|-------|--------------|-------------|-------------|--------------|--------------|-------------|-------------|--------------|-------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

| Pin Type                            |       | 132<br>csBGA | 144<br>TQFP | 208<br>PQFP | 256<br>ftBGA | 132<br>csBGA | 144<br>TQFP | 208<br>PQFP | 256<br>ftBGA | 208<br>PQFP | 256<br>ftBGA | 484<br>fpBGA | 256<br>ftBGA | 484<br>fpBGA | 672<br>fpBGA | 484<br>fpBGA | 672<br>fpBGA |

|                                     | Bank0 | 18           | 20          | 20          | 26           | 18           | 20          | 20          | 28           | 20          | 28           | 52           | 28           | 52           | 70           | 52           | 70           |

|                                     | Bank1 | 4            | 6           | 18          | 18           | 4            | 6           | 18          | 22           | 18          | 22           | 36           | 22           | 36           | 54           | 36           | 70           |

|                                     | Bank2 | 0            | 0           | 0           | 0            | 0            | 0           | 0           | 0            | 0           | 0            | 0            | 0            | 0            | 0            | 0            | 0            |

| PCI capable I/Os<br>Bonding Out per | Bank3 | 0            | 0           | 0           | 0            | 0            | 0           | 0           | 0            | 0           | 0            | 0            | 0            | 0            | 0            | 0            | 0            |

| Bank                                | Bank4 | 8            | 8           | 18          | 18           | 8            | 8           | 18          | 26           | 18          | 26           | 36           | 26           | 38           | 54           | 38           | 70           |

|                                     | Bank5 | 14           | 18          | 20          | 24           | 14           | 18          | 20          | 24           | 20          | 24           | 52           | 24           | 53           | 70           | 53           | 70           |

|                                     | Bank6 | 0            | 0           | 0           | 0            | 0            | 0           | 0           | 0            | 0           | 0            | 0            | 0            | 0            | 0            | 0            | 0            |

|                                     | Bank7 | 0            | 0           | 0           | 0            | 0            | 0           | 0           | 0            | 0           | 0            | 0            | 0            | 0            | 0            | 0            | 0            |

1. Minimum requirement to implement a fully functional 8-bit wide DDR bus. Available DDR interface consists of at least 12 I/Os (1 DQS + 1 DQSB + 8 DQs + 1 DM + Bank VREF1).

## **Logic Signal Connections**

Package pinout information can be found under "Data Sheets" on the LatticeXP2 product page of the Lattice website a www.latticesemi.com/products/fpga/xp2 and in the Lattice Diamond design software.

## **Thermal Management**

Thermal management is recommended as part of any sound FPGA design methodology. To assess the thermal characteristics of a system, Lattice specifies a maximum allowable junction temperature in all device data sheets. Designers must complete a thermal analysis of their specific design to ensure that the device and package do not exceed the junction temperature limits. Refer to the Lattice <u>Thermal Management</u> document to find the device/ package specific thermal values.

## For Further Information

- TN1139, Power Estimation and Management for LatticeXP2 Devices

- Power Calculator tool is included with the Lattice Diamond design tool or as a standalone download from <a href="http://www.latticesemi.com/products/designsoftware">www.latticesemi.com/products/designsoftware</a>

## **Conventional Packaging**

| Part Number      | Voltage | Grade | Package | Pins | Temp. | LUTs (k) |

|------------------|---------|-------|---------|------|-------|----------|

| LFXP2-5E-5M132C  | 1.2V    | -5    | csBGA   | 132  | COM   | 5        |

| LFXP2-5E-6M132C  | 1.2V    | -6    | csBGA   | 132  | COM   | 5        |

| LFXP2-5E-7M132C  | 1.2V    | -7    | csBGA   | 132  | COM   | 5        |

| LFXP2-5E-5FT256C | 1.2V    | -5    | ftBGA   | 256  | COM   | 5        |

| LFXP2-5E-6FT256C | 1.2V    | -6    | ftBGA   | 256  | COM   | 5        |

| LFXP2-5E-7FT256C | 1.2V    | -7    | ftBGA   | 256  | COM   | 5        |

Commercial

| Part Number      | Voltage | Grade | Package | Pins | Temp. | LUTs (k) |

|------------------|---------|-------|---------|------|-------|----------|

| LFXP2-8E-5M132C  | 1.2V    | -5    | csBGA   | 132  | COM   | 8        |

| LFXP2-8E-6M132C  | 1.2V    | -6    | csBGA   | 132  | COM   | 8        |

| LFXP2-8E-7M132C  | 1.2V    | -7    | csBGA   | 132  | COM   | 8        |

| LFXP2-8E-5FT256C | 1.2V    | -5    | ftBGA   | 256  | COM   | 8        |

| LFXP2-8E-6FT256C | 1.2V    | -6    | ftBGA   | 256  | COM   | 8        |

| LFXP2-8E-7FT256C | 1.2V    | -7    | ftBGA   | 256  | COM   | 8        |

| Part Number       | Voltage | Grade | Package | Pins | Temp. | LUTs (k) |

|-------------------|---------|-------|---------|------|-------|----------|

| LFXP2-17E-5FT256C | 1.2V    | -5    | ftBGA   | 256  | COM   | 17       |

| LFXP2-17E-6FT256C | 1.2V    | -6    | ftBGA   | 256  | COM   | 17       |

| LFXP2-17E-7FT256C | 1.2V    | -7    | ftBGA   | 256  | COM   | 17       |

| LFXP2-17E-5F484C  | 1.2V    | -5    | fpBGA   | 484  | COM   | 17       |

| LFXP2-17E-6F484C  | 1.2V    | -6    | fpBGA   | 484  | COM   | 17       |

| LFXP2-17E-7F484C  | 1.2V    | -7    | fpBGA   | 484  | COM   | 17       |

| Part Number       | Voltage | Grade | Package | Pins | Temp. | LUTs (k) |

|-------------------|---------|-------|---------|------|-------|----------|

| LFXP2-30E-5FT256C | 1.2V    | -5    | ftBGA   | 256  | COM   | 30       |

| LFXP2-30E-6FT256C | 1.2V    | -6    | ftBGA   | 256  | COM   | 30       |

| LFXP2-30E-7FT256C | 1.2V    | -7    | ftBGA   | 256  | COM   | 30       |

| LFXP2-30E-5F484C  | 1.2V    | -5    | fpBGA   | 484  | COM   | 30       |

| LFXP2-30E-6F484C  | 1.2V    | -6    | fpBGA   | 484  | COM   | 30       |

| LFXP2-30E-7F484C  | 1.2V    | -7    | fpBGA   | 484  | COM   | 30       |

| LFXP2-30E-5F672C  | 1.2V    | -5    | fpBGA   | 672  | COM   | 30       |

| LFXP2-30E-6F672C  | 1.2V    | -6    | fpBGA   | 672  | COM   | 30       |

| LFXP2-30E-7F672C  | 1.2V    | -7    | fpBGA   | 672  | COM   | 30       |