Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Obsolete                                                                     |

|--------------------------------|------------------------------------------------------------------------------|

| Number of LABs/CLBs            | 2125                                                                         |

| Number of Logic Elements/Cells | 17000                                                                        |

| Total RAM Bits                 | 282624                                                                       |

| Number of I/O                  | 201                                                                          |

| Number of Gates                | -                                                                            |

| Voltage - Supply               | 1.14V ~ 1.26V                                                                |

| Mounting Type                  | Surface Mount                                                                |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                              |

| Package / Case                 | 256-LBGA                                                                     |

| Supplier Device Package        | 256-FTBGA (17x17)                                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfxp2-17e-6ft256c |

|                                |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

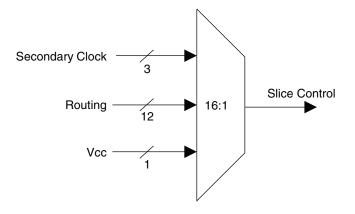

#### Figure 2-14. Slice0 through Slice2 Control Selection

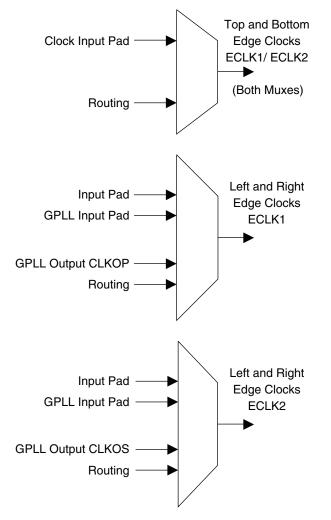

## **Edge Clock Routing**

LatticeXP2 devices have eight high-speed edge clocks that are intended for use with the PIOs in the implementation of high-speed interfaces. Each device has two edge clocks per edge. Figure 2-15 shows the selection muxes for these clocks.

#### Figure 2-15. Edge Clock Mux Connections

- In the 'Signed/Unsigned' options the operands can be switched between signed and unsigned on every cycle.

- In the 'Add/Sub' option the Accumulator can be switched between addition and subtraction on every cycle.

- The loading of operands can switch between parallel and serial operations.

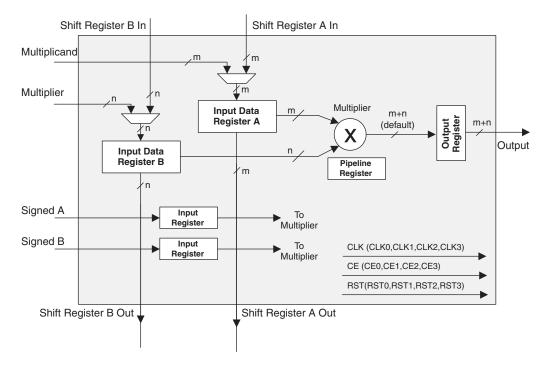

## **MULT sysDSP Element**

This multiplier element implements a multiply with no addition or accumulator nodes. The two operands, A and B, are multiplied and the result is available at the output. The user can enable the input/output and pipeline registers. Figure 2-20 shows the MULT sysDSP element.

#### Figure 2-20. MULT sysDSP Element

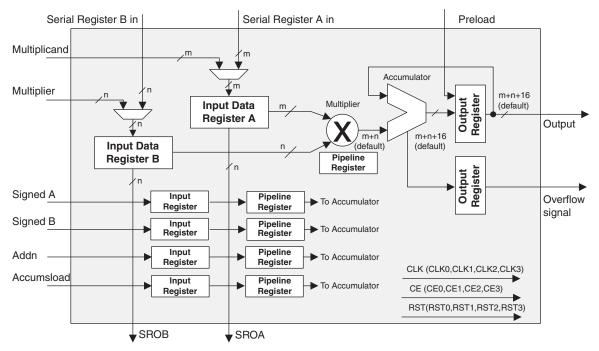

## MAC sysDSP Element

In this case, the two operands, A and B, are multiplied and the result is added with the previous accumulated value. This accumulated value is available at the output. The user can enable the input and pipeline registers but the output register is always enabled. The output register is used to store the accumulated value. The Accumulators in the DSP blocks in LatticeXP2 family can be initialized dynamically. A registered overflow signal is also available. The overflow conditions are provided later in this document. Figure 2-21 shows the MAC sysDSP element.

### Figure 2-21. MAC sysDSP

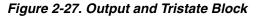

shows the diagram using this gearbox function. For more information on this topic, see TN1138, <u>LatticeXP2 High</u> <u>Speed I/O Interface</u>.

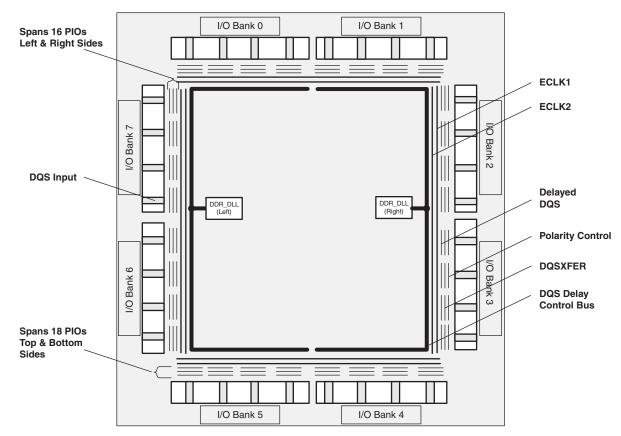

## Figure 2-28. DQS Input Routing (Left and Right)

|     | PIO A | PADA "T"<br>LVDS Pair       |

|-----|-------|-----------------------------|

|     | PIO B | PADB "C"                    |

|     | PIO A | PADA "T"<br>LVDS Pair       |

|     | PIO B | → PADB "C"                  |

|     | PIO A | PADA "T"<br>LVDS Pair       |

|     | PIO B | PADB "C"                    |

|     | PIO A | PADA "T"                    |

|     | PIO B | PADB "C"                    |

| DQS | PIO A | SysIO<br>Buffer<br>PADA "T" |

| •   |       | LVDS Pair                   |

|     | PIO B | PADB "C"                    |

|     | PIO A | PADA "T"<br>LVDS Pair       |

|     | PIO B | PADB "C"                    |

|     | PIO A | PADA "T"                    |

|     | PIO B | PADB "C"                    |

|     | PIO A | → PADA "T"                  |

|     | PIO B | LVDS Pair<br>PADB "C"       |

Figure 2-29. DQS Input Routing (Top and Bottom)

|              | PIO A                                                          | PADA "T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                               |

|--------------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

|              | PIO B                                                          | PADB "                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                               |

|              | -                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | J<br>¬                                                                                                        |

|              | PIO A                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                               |

|              | PIO B                                                          | PADB "                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | C"                                                                                                            |

|              | PIO A                                                          | PADA "T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                               |

|              |                                                                | LVDS F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                               |

|              | PIO B                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | - <b>-</b> J                                                                                                  |

|              | PIO A                                                          | PADA "T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                               |

|              | PIO B                                                          | PADB "C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                               |

|              | PIO A                                                          | syslO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                               |

| 500          |                                                                | Buffer PADA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | , <sub>T"</sub> I                                                                                             |

|              |                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                               |

| <b>■</b> DQS |                                                                | Delay LVDS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                               |

| ■ DQ3        | PIO B                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Pair I                                                                                                        |

| 4            |                                                                | LVDS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Pair  <br>"C"                                                                                                 |

| 4            | PIO B<br>PIO A                                                 | PADB "                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Pair                                                                                                          |

|              |                                                                | PADA "T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Pair                                                                                                          |

|              |                                                                | PADB " LVDS PADB "                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Pair  <br>"C"  <br>"Bair  <br>Pair  <br>C"  <br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>- |

|              | PIO A<br>PIO B                                                 | PADB " PADA "T LVDS PADB " PADA "T LVDS PADB " PADA "T LVDS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Pair I<br>"C" I<br>Pair I<br>C" I<br>C" I<br>Pair I<br>Pair I<br>Pair I                                       |

|              | → PIO A<br>→ PIO B<br>→ PIO A<br>→ PIO B                       | PADA "T<br>LVDS<br>PADA "T<br>LVDS<br>PADA "T<br>LVDS<br>PADA "T<br>LVDS<br>PADB "C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Pair  <br>"C"  <br>Pair  <br>Pair  <br>Pair  <br>C"  <br>Pair                                                 |

|              | → PIO A<br>→ PIO B<br>→ PIO A                                  | PADB " PADA "T LVDS PADB " PADA "T LVDS PADB " PADA "T LVDS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Pair I<br>Pair I<br>Pair I<br>Pair I<br>C                                                                     |

|              | → PIO A<br>→ PIO B<br>→ PIO A<br>→ PIO B                       | PADA "T<br>VOS<br>PADA "C<br>VOS<br>PADA "C<br>VOS<br>PADA "C<br>VOS<br>PADA "C<br>VOS<br>PADA "C<br>PADA "C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Pair I<br>"C" I<br>Pair I<br>C" I<br>Pair I<br>C" I<br>Pair I<br>Pair I<br>Pair I                             |

|              | → PIO A<br>→ PIO B<br>→ PIO A<br>→ PIO B<br>→ PIO A            | PADB "<br>PADB "                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Pair  <br>Pair  <br>Pair  <br>Pair  <br>Pair  <br>Pair  <br>C"  <br>Pair  <br>C"  <br>Pair  <br>C"  <br>Pair  |

|              | → PIO A<br>→ PIO B<br>→ PIO A<br>→ PIO B<br>→ PIO A<br>→ PIO B | PADA "T<br>LVDS<br>PADA "T | Pair  <br>'C"  <br>'Pair  <br>Pair  <br>Pair  <br>Pair  <br>Pair  <br>Pair  <br>Pair  <br>Pair  <br>Pair      |

### **DLL Calibrated DQS Delay Block**

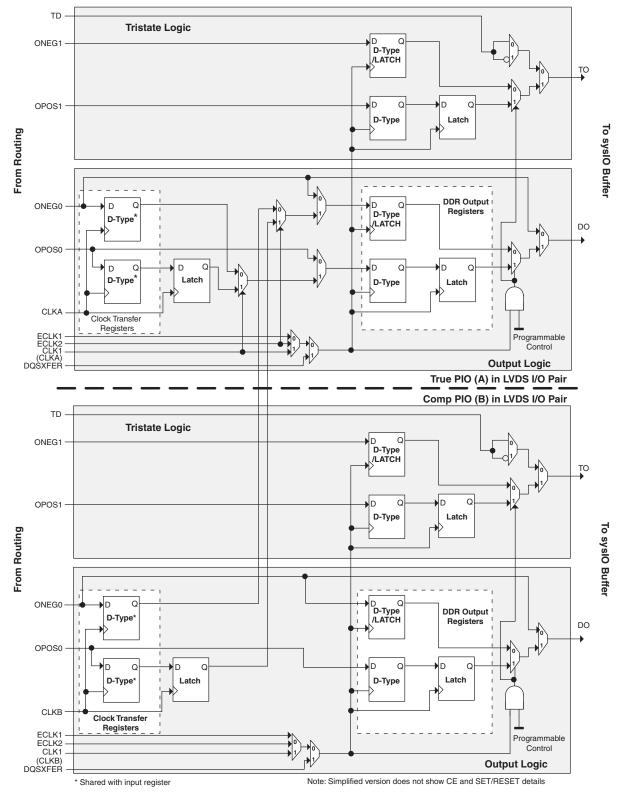

Source synchronous interfaces generally require the input clock to be adjusted in order to correctly capture data at the input register. For most interfaces a PLL is used for this adjustment. However, in DDR memories the clock, referred to as DQS, is not free-running, and this approach cannot be used. The DQS Delay block provides the required clock alignment for DDR memory interfaces.

The DQS signal (selected PIOs only, as shown in Figure 2-30) feeds from the PAD through a DQS delay element to a dedicated DQS routing resource. The DQS signal also feeds polarity control logic which controls the polarity of the clock to the sync registers in the input register blocks. Figure 2-30 and Figure 2-31 show how the DQS transition signals are routed to the PIOs.

The temperature, voltage and process variations of the DQS delay block are compensated by a set of 6-bit bus calibration signals from two dedicated DLLs (DDR\_DLL) on opposite sides of the device. Each DLL compensates DQS delays in its half of the device as shown in Figure 2-30. The DLL loop is compensated for temperature, voltage and process variations by the system clock and feedback loop.

Figure 2-30. Edge Clock, DLL Calibration and DQS Local Bus Distribution

#### Table 2-13. Supported Output Standards

| Output Standard                  | Drive                      | V <sub>CCIO</sub> (Nom.) |

|----------------------------------|----------------------------|--------------------------|

| Single-ended Interfaces          |                            |                          |

| LVTTL                            | 4mA, 8mA, 12mA, 16mA, 20mA | 3.3                      |

| LVCMOS33                         | 4mA, 8mA, 12mA 16mA, 20mA  | 3.3                      |

| LVCMOS25                         | 4mA, 8mA, 12mA, 16mA, 20mA | 2.5                      |

| LVCMOS18                         | 4mA, 8mA, 12mA, 16mA       | 1.8                      |

| LVCMOS15                         | 4mA, 8mA                   | 1.5                      |

| LVCMOS12                         | 2mA, 6mA                   | 1.2                      |

| LVCMOS33, Open Drain             | 4mA, 8mA, 12mA 16mA, 20mA  |                          |

| LVCMOS25, Open Drain             | 4mA, 8mA, 12mA 16mA, 20mA  |                          |

| LVCMOS18, Open Drain             | 4mA, 8mA, 12mA 16mA        | _                        |

| LVCMOS15, Open Drain             | 4mA, 8mA                   |                          |

| LVCMOS12, Open Drain             | 2mA, 6mA                   |                          |

| PCI33                            | N/A                        | 3.3                      |

| HSTL18 Class I, II               | N/A                        | 1.8                      |

| HSTL15 Class I                   | N/A                        | 1.5                      |

| SSTL33 Class I, II               | N/A                        | 3.3                      |

| SSTL25 Class I, II               | N/A                        | 2.5                      |

| SSTL18 Class I, II               | N/A                        | 1.8                      |

| Differential Interfaces          |                            |                          |

| Differential SSTL33, Class I, II | N/A                        | 3.3                      |

| Differential SSTL25, Class I, II | N/A                        | 2.5                      |

| Differential SSTL18, Class I, II | N/A                        | 1.8                      |

| Differential HSTL18, Class I, II | N/A                        | 1.8                      |

| Differential HSTL15, Class I     | N/A                        | 1.5                      |

| LVDS <sup>1, 2</sup>             | N/A                        | 2.5                      |

| MLVDS <sup>1</sup>               | N/A                        | 2.5                      |

| BLVDS <sup>1</sup>               | N/A                        | 2.5                      |

| LVPECL <sup>1</sup>              | N/A                        | 3.3                      |

| RSDS <sup>1</sup>                | N/A                        | 2.5                      |

| LVCMOS33D <sup>1</sup>           | 4mA, 8mA, 12mA, 16mA, 20mA | 3.3                      |

1. Emulated with external resistors.

2. On the left and right edges, LVDS outputs are supported with a dedicated differential output driver on 50% of the I/Os. This solution does not require external resistors at the driver.

## **Hot Socketing**

LatticeXP2 devices have been carefully designed to ensure predictable behavior during power-up and powerdown. Power supplies can be sequenced in any order. During power-up and power-down sequences, the I/Os remain in tri-state until the power supply voltage is high enough to ensure reliable operation. In addition, leakage into I/O pins is controlled to within specified limits. This allows for easy integration with the rest of the system. These capabilities make the LatticeXP2 ideal for many multiple power supply and hot-swap applications.

# IEEE 1149.1-Compliant Boundary Scan Testability

All LatticeXP2 devices have boundary scan cells that are accessed through an IEEE 1149.1 compliant Test Access Port (TAP). This allows functional testing of the circuit board, on which the device is mounted, through a serial scan path that can access all critical logic nodes. Internal registers are linked internally, allowing test data to be shifted in

# **Density Shifting**

The LatticeXP2 family is designed to ensure that different density devices in the same family and in the same package have the same pinout. Furthermore, the architecture ensures a high success rate when performing design migration from lower density devices to higher density devices. In many cases, it is also possible to shift a lower utilization design targeted for a high-density device to a lower density device. However, the exact details of the final resource utilization will impact the likely success in each case.

# sysIO Recommended Operating Conditions

|                                                       |       |                   | ended Operating | goonanions |                      |       |  |  |

|-------------------------------------------------------|-------|-------------------|-----------------|------------|----------------------|-------|--|--|

|                                                       |       | V <sub>CCIO</sub> |                 |            | V <sub>REF</sub> (V) |       |  |  |

| Standard                                              | Min.  | Тур.              | Max.            | Min.       | Тур.                 | Max.  |  |  |

| LVCMOS33 <sup>2</sup>                                 | 3.135 | 3.3               | 3.465           | —          | —                    | —     |  |  |

| LVCMOS25 <sup>2</sup>                                 | 2.375 | 2.5               | 2.625           | —          | —                    | —     |  |  |

| LVCMOS18                                              | 1.71  | 1.8               | 1.89            | —          | —                    | —     |  |  |

| LVCMOS15                                              | 1.425 | 1.5               | 1.575           | —          | —                    | —     |  |  |

| LVCMOS12 <sup>2</sup>                                 | 1.14  | 1.2               | 1.26            | —          | —                    | —     |  |  |

| LVTTL33 <sup>2</sup>                                  | 3.135 | 3.3               | 3.3 3.465 — —   |            |                      |       |  |  |

| PCI33                                                 | 3.135 | 3.3               | 3.465           | —          | —                    | —     |  |  |

| SSTL18_I <sup>2</sup> ,<br>SSTL18_II <sup>2</sup>     | 1.71  | 1.8               | 1.89            | 0.833      | 0.9                  | 0.969 |  |  |

| SSTL25_I <sup>2</sup> ,<br>SSTL25_II <sup>2</sup>     | 2.375 | 2.5               | 2.625           | 1.15       | 1.25                 | 1.35  |  |  |

| SSTL33_I <sup>2</sup> ,<br>SSTL33_II <sup>2</sup>     | 3.135 | 3.3               | 3.465           | 1.3        | 1.5                  | 1.7   |  |  |

| HSTL15_I <sup>2</sup>                                 | 1.425 | 1.5               | 1.575           | 0.68       | 0.75                 | 0.9   |  |  |

| HSTL18_I <sup>2</sup> ,<br>HSTL18_II <sup>2</sup>     | 1.71  | 1.8               | 1.89            | 0.816      | 0.816 0.9            |       |  |  |

| LVDS25 <sup>2</sup>                                   | 2.375 | 2.5               | 2.625           |            | —                    | —     |  |  |

| MLVDS251                                              | 2.375 | 2.5               | 2.625           |            | —                    | —     |  |  |

| LVPECL33 <sup>1, 2</sup>                              | 3.135 | 3.3               | 3.465           |            | —                    | —     |  |  |

| BLVDS25 <sup>1, 2</sup>                               | 2.375 | 2.5               | 2.625           |            | —                    | —     |  |  |

| RSDS <sup>1, 2</sup>                                  | 2.375 | 2.5               | 2.625           |            | —                    | —     |  |  |

| SSTL18D_I <sup>2</sup> ,<br>SSTL18D_II <sup>2</sup>   | 1.71  | 1.8               | 1.89            | _          | _                    | _     |  |  |

| SSTL25D_ I <sup>2</sup> ,<br>SSTL25D_II <sup>2</sup>  | 2.375 | 2.5               | 2.625           | _          | _                    | _     |  |  |

| SSTL33D_ I <sup>2</sup> ,<br>SSTL33D_ II <sup>2</sup> | 3.135 | 3.3               | 3.465           | —          | —                    | —     |  |  |

| HSTL15D_ I <sup>2</sup>                               | 1.425 | 1.5               | 1.575           |            | —                    | —     |  |  |

| HSTL18D_ I²,<br>HSTL18D_ II²                          | 1.71  | 1.8               | 1.89            | —          | _                    | —     |  |  |

#### **Over Recommended Operating Conditions**

1. Inputs on chip. Outputs are implemented with the addition of external resistors. 2. Input on this standard does not depend on the value of  $V_{CCIO}$ .

# sysIO Differential Electrical Characteristics LVDS

| Parameter                           | Description                                    | Test Conditions                                                  | Min.   | Тур. | Max.  | Units |

|-------------------------------------|------------------------------------------------|------------------------------------------------------------------|--------|------|-------|-------|

| V <sub>INP</sub> , V <sub>INM</sub> | Input Voltage                                  |                                                                  | 0      |      | 2.4   | V     |

| V <sub>CM</sub>                     | Input Common Mode Voltage                      | Half the Sum of the Two Inputs                                   | 0.05   |      | 2.35  | V     |

| V <sub>THD</sub>                    | Differential Input Threshold                   | Difference Between the Two Inputs                                | +/-100 |      |       | mV    |

| I <sub>IN</sub>                     | Input Current                                  | Power On or Power Off                                            | _      | _    | +/-10 | μΑ    |

| V <sub>OH</sub>                     | Output High Voltage for $V_{OP}$ or $V_{OM}$   | R <sub>T</sub> = 100 Ohm                                         | _      | 1.38 | 1.60  | V     |

| V <sub>OL</sub>                     | Output Low Voltage for $V_{OP}$ or $V_{OM}$    | R <sub>T</sub> = 100 Ohm                                         | 0.9V   | 1.03 |       | V     |

| V <sub>OD</sub>                     | Output Voltage Differential                    | (V <sub>OP</sub> - V <sub>OM</sub> ), R <sub>T</sub> = 100 Ohm   | 250    | 350  | 450   | mV    |

| ΔV <sub>OD</sub>                    | Change in V <sub>OD</sub> Between High and Low |                                                                  | _      | _    | 50    | mV    |

| V <sub>OS</sub>                     | Output Voltage Offset                          | (V <sub>OP</sub> + V <sub>OM</sub> )/2, R <sub>T</sub> = 100 Ohm | 1.125  | 1.20 | 1.375 | V     |

| $\Delta V_{OS}$                     | Change in V <sub>OS</sub> Between H and L      |                                                                  | _      |      | 50    | mV    |

| I <sub>SA</sub>                     | Output Short Circuit Current                   | V <sub>OD</sub> = 0V Driver Outputs Shorted to<br>Ground         | —      | _    | 24    | mA    |

| I <sub>SAB</sub>                    | Output Short Circuit Current                   | V <sub>OD</sub> = 0V Driver Outputs Shorted to<br>Each Other     | _      | _    | 12    | mA    |

#### **Over Recommended Operating Conditions**

## **Differential HSTL and SSTL**

Differential HSTL and SSTL outputs are implemented as a pair of complementary single-ended outputs. All allowable single-ended output classes (class I and class II) are supported in this mode.

For further information on LVPECL, RSDS, MLVDS, BLVDS and other differential interfaces please see details in additional technical notes listed at the end of this data sheet.

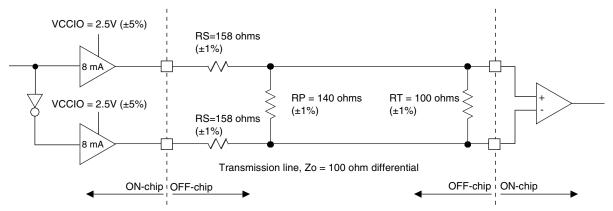

## LVDS25E

The top and bottom sides of LatticeXP2 devices support LVDS outputs via emulated complementary LVCMOS outputs in conjunction with a parallel resistor across the driver outputs. The scheme shown in Figure 3-1 is one possible solution for point-to-point signals.

# LatticeXP2 External Switching Characteristics (Continued)

|                        |                                                                       |             | -    | 7    | -    | 6    | -    | 5    |       |  |

|------------------------|-----------------------------------------------------------------------|-------------|------|------|------|------|------|------|-------|--|

| Parameter              | Description                                                           | Device      | Min. | Max. | Min. | Max. | Min. | Max. | Units |  |

|                        |                                                                       | XP2-5       | 1.00 | —    | 1.30 | —    | 1.60 | —    | ns    |  |

|                        |                                                                       | XP2-8       | 1.00 | —    | 1.30 | —    | 1.60 | —    | ns    |  |

| t <sub>HE</sub>        | Clock to Data Hold - PIO Input<br>Register                            | XP2-17      | 1.00 |      | 1.30 | —    | 1.60 | —    | ns    |  |

|                        |                                                                       | XP2-30      | 1.20 | —    | 1.60 | —    | 1.90 | —    | ns    |  |

|                        |                                                                       | XP2-40      | 1.20 | —    | 1.60 | —    | 1.90 | —    | ns    |  |

|                        |                                                                       | XP2-5       | 1.00 |      | 1.30 | —    | 1.60 | —    | ns    |  |

|                        |                                                                       | XP2-8       | 1.00 | —    | 1.30 | —    | 1.60 | —    | ns    |  |

| SU_DELE                | Clock to Data Setup - PIO Input<br>Register with Data Input Delay     | XP2-17      | 1.00 | —    | 1.30 | —    | 1.60 | —    | ns    |  |

|                        | Tiegister with Data input Delay                                       | XP2-30      | 1.20 | —    | 1.60 | —    | 1.90 | —    | ns    |  |

|                        |                                                                       | XP2-40      | 1.20 |      | 1.60 | —    | 1.90 | —    | ns    |  |

|                        |                                                                       | XP2-5       | 0.00 |      | 0.00 | —    | 0.00 | —    | ns    |  |

|                        |                                                                       | XP2-8       | 0.00 |      | 0.00 | —    | 0.00 | —    | ns    |  |

| <sup>t</sup> H_DELE    | DELE Clock to Data Hold - PIO Input<br>Register with Input Data Delay | XP2-17      | 0.00 |      | 0.00 | —    | 0.00 | —    | ns    |  |

|                        | riegister with input Data Delay                                       | XP2-30      | 0.00 |      | 0.00 | —    | 0.00 | —    | ns    |  |

|                        |                                                                       | XP2-40      | 0.00 |      | 0.00 | _    | 0.00 | —    | ns    |  |

| f <sub>MAX_IOE</sub>   | Clock Frequency of I/O and PFU<br>Register                            | XP2         | —    | 420  | _    | 357  | —    | 311  | MHz   |  |

| General I/O Pi         | in Parameters (using Primary Clo                                      | ck with PLL | .)1  |      |      |      |      |      |       |  |

|                        |                                                                       | XP2-5       | —    | 3.00 | —    | 3.30 | —    | 3.70 | ns    |  |

|                        |                                                                       | XP2-8       | —    | 3.00 |      | 3.30 | —    | 3.70 | ns    |  |

| t <sub>COPLL</sub>     | Clock to Output - PIO Output<br>Register                              | XP2-17      | —    | 3.00 | —    | 3.30 | —    | 3.70 | ns    |  |

|                        |                                                                       | XP2-30      | —    | 3.00 | —    | 3.30 | —    | 3.70 | ns    |  |

|                        |                                                                       | XP2-40      | —    | 3.00 | —    | 3.30 | —    | 3.70 | ns    |  |

|                        |                                                                       | XP2-5       | 1.00 |      | 1.20 | —    | 1.40 | —    | ns    |  |

|                        |                                                                       | XP2-8       | 1.00 |      | 1.20 | —    | 1.40 | —    | ns    |  |

| t <sub>SUPLL</sub>     | Clock to Data Setup - PIO Input<br>Register                           | XP2-17      | 1.00 |      | 1.20 | —    | 1.40 | —    | ns    |  |

|                        |                                                                       | XP2-30      | 1.00 | —    | 1.20 | —    | 1.40 | —    | ns    |  |

|                        |                                                                       | XP2-40      | 1.00 |      | 1.20 | —    | 1.40 | —    | ns    |  |

|                        |                                                                       | XP2-5       | 0.90 | —    | 1.10 | —    | 1.30 | —    | ns    |  |

|                        |                                                                       | XP2-8       | 0.90 | —    | 1.10 | —    | 1.30 | —    | ns    |  |

| t <sub>HPLL</sub>      | Clock to Data Hold - PIO Input<br>Register                            | XP2-17      | 0.90 | —    | 1.10 | —    | 1.30 | —    | ns    |  |

|                        |                                                                       | XP2-30      | 1.00 |      | 1.20 | —    | 1.40 | —    | ns    |  |

|                        |                                                                       | XP2-40      | 1.00 |      | 1.20 | —    | 1.40 | —    | ns    |  |

|                        |                                                                       | XP2-5       | 1.90 |      | 2.10 | —    | 2.30 | —    | ns    |  |

|                        |                                                                       | XP2-8       | 1.90 |      | 2.10 |      | 2.30 | _    | ns    |  |

| t <sub>SU_DELPLL</sub> | Clock to Data Setup - PIO Input<br>Register with Data Input Delay     | XP2-17      | 1.90 |      | 2.10 | —    | 2.30 | —    | ns    |  |

| -                      |                                                                       | XP2-30      | 2.00 |      | 2.20 | —    | 2.40 | —    | ns    |  |

|                        |                                                                       | XP2-40      | 2.00 |      | 2.20 | _    | 2.40 | _    | ns    |  |

### **Over Recommended Operating Conditions**

# LatticeXP2 Internal Switching Characteristics<sup>1</sup> (Continued)

|                                   |                                           | -      | 7     | -      | 6     | -      | 5     |       |

|-----------------------------------|-------------------------------------------|--------|-------|--------|-------|--------|-------|-------|

| Parameter                         | Description                               | Min.   | Max.  | Min.   | Max.  | Min.   | Max.  | Units |

| t <sub>HP_DSP</sub>               | Pipeline Register Hold Time               | -0.787 | _     | -0.890 | _     | -0.994 | —     | ns    |

| t <sub>SUO_DSP</sub>              | Output Register Setup Time                | 4.896  | _     | 5.413  | _     | 5.931  | —     | ns    |

| t <sub>HO_DSP</sub>               | Output Register Hold Time                 | -1.439 | _     | -1.604 | _     | -1.770 | —     | ns    |

| t <sub>COI_DSP</sub> <sup>3</sup> | Input Register Clock to Output<br>Time    | _      | 4.513 | —      | 4.947 | —      | 5.382 | ns    |

| t <sub>COP_DSP</sub> <sup>3</sup> | Pipeline Register Clock to Output<br>Time | _      | 2.153 | —      | 2.272 | —      | 2.391 | ns    |

| t <sub>COO_DSP</sub> <sup>3</sup> | Output Register Clock to Output Time      | _      | 0.569 | —      | 0.600 | —      | 0.631 | ns    |

| t <sub>SUADSUB</sub>              | AdSub Input Register Setup Time           | -0.270 | —     | -0.298 | _     | -0.327 | —     | ns    |

| t <sub>HADSUB</sub>               | AdSub Input Register Hold Time            | 0.306  |       | 0.338  |       | 0.371  |       | ns    |

## **Over Recommended Operating Conditions**

1. Internal parameters are characterized, but not tested on every device.

2. RST resets VCO and all counters in PLL.

3. These parameters include the Adder Subtractor block in the path.

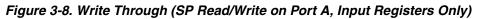

Note: Input data and address are registered at the positive edge of the clock and output data appears after the positive edge of the clock.

# LatticeXP2 Family Timing Adders<sup>1, 2, 3, 4</sup>

| Buffer Type      | Description                            | -7    | -6    | -5    | Units |

|------------------|----------------------------------------|-------|-------|-------|-------|

| Input Adjusters  |                                        |       |       |       |       |

| LVDS25           | LVDS                                   | -0.26 | -0.11 | 0.04  | ns    |

| BLVDS25          | BLVDS                                  | -0.26 | -0.11 | 0.04  | ns    |

| MLVDS            | LVDS                                   | -0.26 | -0.11 | 0.04  | ns    |

| RSDS             | RSDS                                   | -0.26 | -0.11 | 0.04  | ns    |

| LVPECL33         | LVPECL                                 | -0.26 | -0.11 | 0.04  | ns    |

| HSTL18_I         | HSTL_18 class I                        | -0.23 | -0.08 | 0.07  | ns    |

| HSTL18_II        | HSTL_18 class II                       | -0.23 | -0.08 | 0.07  | ns    |

| HSTL18D_I        | Differential HSTL 18 class I           | -0.28 | -0.13 | 0.02  | ns    |

| HSTL18D_II       | Differential HSTL 18 class II          | -0.28 | -0.13 | 0.02  | ns    |

| HSTL15_I         | HSTL_15 class I                        | -0.23 | -0.09 | 0.06  | ns    |

| HSTL15D_I        | Differential HSTL 15 class I           | -0.28 | -0.13 | 0.01  | ns    |

| SSTL33_I         | SSTL_3 class I                         | -0.20 | -0.04 | 0.12  | ns    |

| SSTL33_II        | SSTL_3 class II                        | -0.20 | -0.04 | 0.12  | ns    |

| SSTL33D_I        | Differential SSTL_3 class I            | -0.27 | -0.11 | 0.04  | ns    |

| SSTL33D_II       | Differential SSTL_3 class II           | -0.27 | -0.11 | 0.04  | ns    |

| SSTL25_I         | SSTL_2 class I                         | -0.21 | -0.06 | 0.10  | ns    |

| SSTL25_II        | SSTL_2 class II                        | -0.21 | -0.06 | 0.10  | ns    |

| SSTL25D_I        | Differential SSTL_2 class I            | -0.27 | -0.12 | 0.03  | ns    |

| SSTL25D_II       | Differential SSTL_2 class II           | -0.27 | -0.12 | 0.03  | ns    |

| SSTL18_I         | SSTL_18 class I                        | -0.23 | -0.08 | 0.07  | ns    |

| SSTL18_II        | SSTL_18 class II                       | -0.23 | -0.08 | 0.07  | ns    |

| SSTL18D_I        | Differential SSTL_18 class I           | -0.28 | -0.13 | 0.02  | ns    |

| SSTL18D_II       | Differential SSTL_18 class II          | -0.28 | -0.13 | 0.02  | ns    |

| LVTTL33          | LVTTL                                  | -0.09 | 0.05  | 0.18  | ns    |

| LVCMOS33         | LVCMOS 3.3                             | -0.09 | 0.05  | 0.18  | ns    |

| LVCMOS25         | LVCMOS 2.5                             | 0.00  | 0.00  | 0.00  | ns    |

| LVCMOS18         | LVCMOS 1.8                             | -0.23 | -0.07 | 0.09  | ns    |

| LVCMOS15         | LVCMOS 1.5                             | -0.20 | -0.02 | 0.16  | ns    |

| LVCMOS12         | LVCMOS 1.2                             | -0.35 | -0.20 | -0.04 | ns    |

| PCI33            | 3.3V PCI                               | -0.09 | 0.05  | 0.18  | ns    |

| Output Adjusters |                                        |       |       |       |       |

| LVDS25E          | LVDS 2.5 E⁵                            | -0.25 | 0.02  | 0.30  | ns    |

| LVDS25           | LVDS 2.5                               | -0.25 | 0.02  | 0.30  | ns    |

| BLVDS25          | BLVDS 2.5                              | -0.28 | 0.00  | 0.28  | ns    |

| MLVDS            | MLVDS 2.5 <sup>5</sup>                 | -0.28 | 0.00  | 0.28  | ns    |

| RSDS             | RSDS 2.5 <sup>5</sup>                  | -0.25 | 0.02  | 0.30  | ns    |

| LVPECL33         | LVPECL 3.3 <sup>5</sup>                | -0.37 | -0.10 | 0.18  | ns    |

| HSTL18_I         | HSTL_18 class I 8mA drive              | -0.17 | 0.13  | 0.43  | ns    |

| HSTL18_II        | HSTL_18 class II                       | -0.29 | 0.00  | 0.29  | ns    |

| HSTL18D_I        | Differential HSTL 18 class I 8mA drive | -0.17 | 0.13  | 0.43  | ns    |

| HSTL18D_II       | Differential HSTL 18 class II          | -0.29 | 0.00  | 0.29  | ns    |

## **Over Recommended Operating Conditions**

# LatticeXP2 Family Timing Adders<sup>1, 2, 3, 4</sup> (Continued)

#### **Over Recommended Operating Conditions**

| Buffer Type   | Description                           | -7    | -6    | -5    | Units |

|---------------|---------------------------------------|-------|-------|-------|-------|

| LVCMOS25_4mA  | LVCMOS 2.5 4mA drive, slow slew rate  | 1.05  | 1.43  | 1.81  | ns    |

| LVCMOS25_8mA  | LVCMOS 2.5 8mA drive, slow slew rate  | 0.78  | 1.15  | 1.52  | ns    |

| LVCMOS25_12mA | LVCMOS 2.5 12mA drive, slow slew rate | 0.59  | 0.96  | 1.33  | ns    |

| LVCMOS25_16mA | LVCMOS 2.5 16mA drive, slow slew rate | 0.81  | 1.18  | 1.55  | ns    |

| LVCMOS25_20mA | LVCMOS 2.5 20mA drive, slow slew rate | 0.61  | 0.98  | 1.35  | ns    |

| LVCMOS18_4mA  | LVCMOS 1.8 4mA drive, slow slew rate  | 1.01  | 1.38  | 1.75  | ns    |

| LVCMOS18_8mA  | LVCMOS 1.8 8mA drive, slow slew rate  | 0.72  | 1.08  | 1.45  | ns    |

| LVCMOS18_12mA | LVCMOS 1.8 12mA drive, slow slew rate | 0.53  | 0.90  | 1.26  | ns    |

| LVCMOS18_16mA | LVCMOS 1.8 16mA drive, slow slew rate | 0.74  | 1.11  | 1.48  | ns    |

| LVCMOS15_4mA  | LVCMOS 1.5 4mA drive, slow slew rate  | 0.96  | 1.33  | 1.71  | ns    |

| LVCMOS15_8mA  | LVCMOS 1.5 8mA drive, slow slew rate  | -0.53 | -0.26 | 0.00  | ns    |

| LVCMOS12_2mA  | LVCMOS 1.2 2mA drive, slow slew rate  | 0.90  | 1.27  | 1.65  | ns    |

| LVCMOS12_6mA  | LVCMOS 1.2 6mA drive, slow slew rate  | -0.55 | -0.29 | -0.02 | ns    |

| PCI33         | 3.3V PCI                              | -0.29 | -0.01 | 0.26  | ns    |

1. Timing Adders are characterized but not tested on every device.

2. LVCMOS timing measured with the load specified in Switching Test Condition table.

3. All other standards tested according to the appropriate specifications.

4. The base parameters used with these timing adders to calculate timing are listed in the LatticeXP2 Internal Switching Characteristics table under PIO Input/Output Timing.

5. These timing adders are measured with the recommended resistor values.

# Pin Information Summary

|                                          |                |              | XP          | 2-5         |              |              | XP          | 2-8         |              |             | XP2-17       | ,            |              | XP2-30       |         | XP2-40       |         |

|------------------------------------------|----------------|--------------|-------------|-------------|--------------|--------------|-------------|-------------|--------------|-------------|--------------|--------------|--------------|--------------|---------|--------------|---------|

| Pin Ty                                   | pe             | 132<br>csBGA | 144<br>TQFP | 208<br>PQFP | 256<br>ftBGA | 132<br>csBGA | 144<br>TQFP | 208<br>PQFP | 256<br>ftBGA | 208<br>PQFP | 256<br>ftBGA | 484<br>fpBGA | 256<br>ftBGA | 484<br>fpBGA | 672     | 484<br>fpBGA | 672     |

| Single Ended Us                          |                | 86           | 100         | 146         | 172          | 86           | 100         | 146         | 201          | 146         | 201          | 358          | 201          | 363          | 472     | 363          | 540     |

| Differential Pair                        | Normal         | 35           | 39          | 57          | 66           | 35           | 39          | 57          | 77           | 57          | 77           | 135          | 77           | 137          | 180     | 137          | 204     |

| User I/O                                 | Highspeed      | 8            | 11          | 16          | 20           | 8            | 11          | 16          | 23           | 16          | 23           | 44           | 23           | 44           | 56      | 44           | 66      |

|                                          | TAP            | 5            | 5           | 5           | 5            | 5            | 5           | 5           | 5            | 5           | 5            | 5            | 5            | 5            | 5       | 5            | 5       |

| Configuration                            | Muxed          | 9            | 9           | 9           | 9            | 9            | 9           | 9           | 9            | 9           | 9            | 9            | 9            | 9            | 9       | 9            | 9       |

|                                          | Dedicated      | 1            | 1           | 1           | 1            | 1            | 1           | 1           | 1            | 1           | 1            | 1            | 1            | 1            | 1       | 1            | 1       |

| Non Configura-                           | Muxed          | 5            | 5           | 7           | 7            | 7            | 7           | 9           | 9            | 11          | 11           | 21           | 7            | 11           | 13      | 11           | 13      |

| tion                                     | Dedicated      | 1            | 1           | 1           | 1            | 1            | 1           | 1           | 1            | 1           | 1            | 1            | 1            | 1            | 1       | 1            | 1       |

| Vcc                                      |                | 6            | 4           | 9           | 6            | 6            | 4           | 9           | 6            | 9           | 6            | 16           | 6            | 16           | 20      | 16           | 20      |

| Vccaux                                   |                | 4            | 4           | 4           | 4            | 4            | 4           | 4           | 4            | 4           | 4            | 8            | 4            | 8            | 8       | 8            | 8       |

| VCCPLL                                   |                | 2            | 2           | 2           | -            | 2            | 2           | 2           | -            | 4           | -            | -            | -            | -            | -       | -            | -       |

|                                          | Bank0          | 2            | 2           | 2           | 2            | 2            | 2           | 2           | 2            | 2           | 2            | 4            | 2            | 4            | 4       | 4            | 4       |

|                                          | Bank1          | 1            | 1           | 2           | 2            | 1            | 1           | 2           | 2            | 2           | 2            | 4            | 2            | 4            | 4       | 4            | 4       |

|                                          | Bank2          | 2            | 2           | 2           | 2            | 2            | 2           | 2           | 2            | 2           | 2            | 4            | 2            | 4            | 4       | 4            | 4       |

| VCCIO                                    | Bank3          | 1            | 1           | 2           | 2            | 1            | 1           | 2           | 2            | 2           | 2            | 4            | 2            | 4            | 4       | 4            | 4       |

|                                          | Bank4          | 1            | 1           | 2           | 2            | 1            | 1           | 2           | 2            | 2           | 2            | 4            | 2            | 4            | 4       | 4            | 4       |

|                                          | Bank5          | 2            | 2           | 2           | 2            | 2            | 2           | 2           | 2            | 2           | 2            | 4            | 2            | 4            | 4       | 4            | 4       |