Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                               |

|--------------------------------|-------------------------------------------------------------------------------|

| Product Status                 | Active                                                                        |

| Number of LABs/CLBs            | 3625                                                                          |

| Number of Logic Elements/Cells | 29000                                                                         |

| Total RAM Bits                 | 396288                                                                        |

| Number of I/O                  | 201                                                                           |

| Number of Gates                | -                                                                             |

| Voltage - Supply               | 1.14V ~ 1.26V                                                                 |

| Mounting Type                  | Surface Mount                                                                 |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                               |

| Package / Case                 | 256-LBGA                                                                      |

| Supplier Device Package        | 256-FTBGA (17x17)                                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfxp2-30e-5ftn256c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

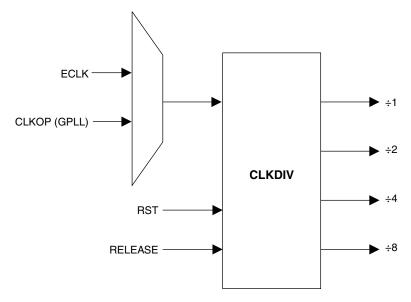

Figure 2-5. Clock Divider Connections

#### **Clock Distribution Network**

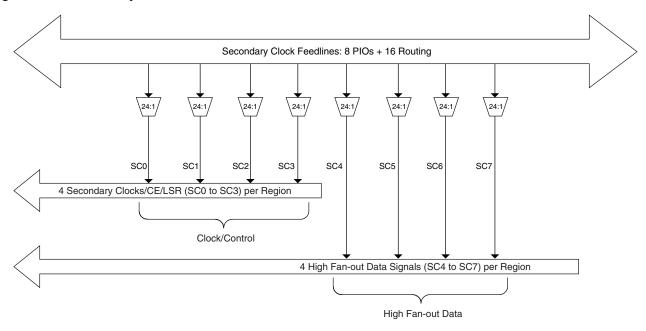

LatticeXP2 devices have eight quadrant-based primary clocks and between six and eight flexible region-based secondary clocks/control signals. Two high performance edge clocks are available on each edge of the device to support high speed interfaces. The clock inputs are selected from external I/Os, the sysCLOCK PLLs, or routing. Clock inputs are fed throughout the chip via the primary, secondary and edge clock networks.

#### **Primary Clock Sources**

LatticeXP2 devices derive primary clocks from four sources: PLL outputs, CLKDIV outputs, dedicated clock inputs and routing. LatticeXP2 devices have two to four sysCLOCK PLLs, located in the four corners of the device. There are eight dedicated clock inputs, two on each side of the device. Figure 2-6 shows the primary clock sources.

Figure 2-12. Secondary Clock Selection

#### Slice Clock Selection

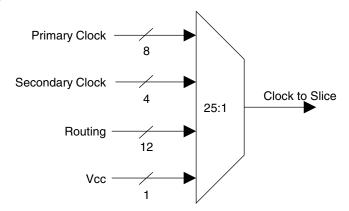

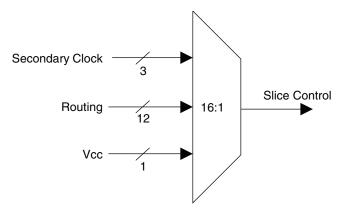

Figure 2-13 shows the clock selections and Figure 2-14 shows the control selections for Slice0 through Slice2. All the primary clocks and the four secondary clocks are routed to this clock selection mux. Other signals, via routing, can be used as clock inputs to the slices. Slice controls are generated from the secondary clocks or other signals connected via routing.

If none of the signals are selected for both clock and control, then the default value of the mux output is 1. Slice 3 does not have any registers; therefore it does not have the clock or control muxes.

Figure 2-13. Slice0 through Slice2 Clock Selection

Figure 2-14. Slice0 through Slice2 Control Selection

#### **Edge Clock Routing**

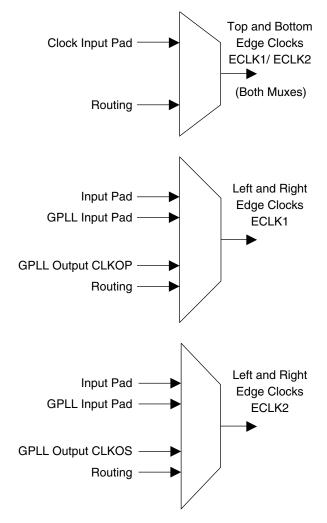

LatticeXP2 devices have eight high-speed edge clocks that are intended for use with the PIOs in the implementation of high-speed interfaces. Each device has two edge clocks per edge. Figure 2-15 shows the selection muxes for these clocks.

Figure 2-15. Edge Clock Mux Connections

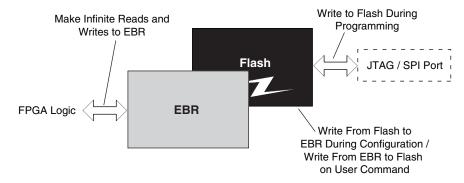

Figure 2-16. FlashBAK Technology

#### **Memory Cascading**

Larger and deeper blocks of RAMs can be created using EBR sysMEM Blocks. Typically, the Lattice design tools cascade memory transparently, based on specific design inputs.

#### Single, Dual and Pseudo-Dual Port Modes

In all the sysMEM RAM modes the input data and address for the ports are registered at the input of the memory array. The output data of the memory is optionally registered at the output.

EBR memory supports two forms of write behavior for single port or dual port operation:

- 1. Normal Data on the output appears only during a read cycle. During a write cycle, the data (at the current address) does not appear on the output. This mode is supported for all data widths.

- 2. Write Through A copy of the input data appears at the output of the same port during a write cycle. This mode is supported for all data widths.

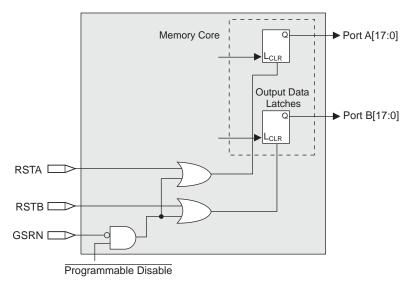

#### **Memory Core Reset**

The memory array in the EBR utilizes latches at the A and B output ports. These latches can be reset asynchronously or synchronously. RSTA and RSTB are local signals, which reset the output latches associated with Port A and Port B respectively. GSRN, the global reset signal, resets both ports. The output data latches and associated resets for both ports are as shown in Figure 2-17.

Figure 2-17. Memory Core Reset

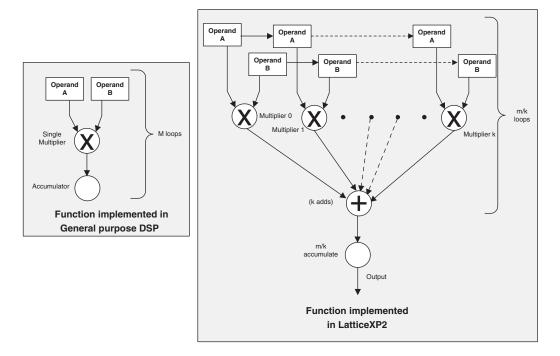

Figure 2-19. Comparison of General DSP and LatticeXP2 Approaches

#### sysDSP Block Capabilities

The sysDSP block in the LatticeXP2 family supports four functional elements in three 9, 18 and 36 data path widths. The user selects a function element for a DSP block and then selects the width and type (signed/unsigned) of its operands. The operands in the LatticeXP2 family sysDSP Blocks can be either signed or unsigned but not mixed within a function element. Similarly, the operand widths cannot be mixed within a block. DSP elements can be concatenated.

The resources in each sysDSP block can be configured to support the following four elements:

- MULT (Multiply)

- MAC (Multiply, Accumulate)

- MULTADDSUB (Multiply, Addition/Subtraction)

- MULTADDSUBSUM (Multiply, Addition/Subtraction, Accumulate)

The number of elements available in each block depends on the width selected from the three available options: x9, x18, and x36. A number of these elements are concatenated for highly parallel implementations of DSP functions. Table 2-6 shows the capabilities of the block.

Table 2-6. Maximum Number of Elements in a Block

| Width of Multiply | х9 | x18 | x36 |

|-------------------|----|-----|-----|

| MULT              | 8  | 4   | 1   |

| MAC               | 2  | 2   | _   |

| MULTADDSUB        | 4  | 2   | _   |

| MULTADDSUBSUM     | 2  | 1   | _   |

Some options are available in four elements. The input register in all the elements can be directly loaded or can be loaded as shift register from previous operand registers. By selecting 'dynamic operation' the following operations are possible:

- In the 'Signed/Unsigned' options the operands can be switched between signed and unsigned on every cycle.

- In the 'Add/Sub' option the Accumulator can be switched between addition and subtraction on every cycle.

- The loading of operands can switch between parallel and serial operations.

#### **MULT sysDSP Element**

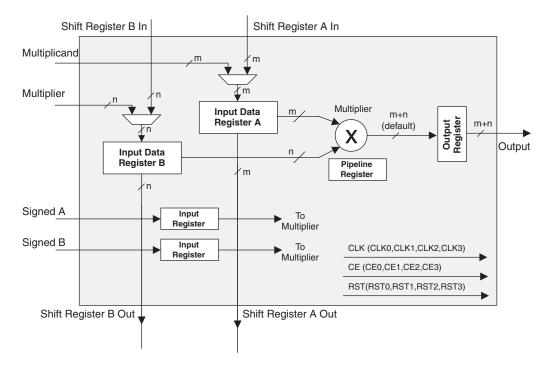

This multiplier element implements a multiply with no addition or accumulator nodes. The two operands, A and B, are multiplied and the result is available at the output. The user can enable the input/output and pipeline registers. Figure 2-20 shows the MULT sysDSP element.

Figure 2-20. MULT sysDSP Element

#### **Tristate Register Block**

The tristate register block provides the ability to register tri-state control signals from the core of the device before they are passed to the syslO buffers. The block contains a register for SDR operation and an additional latch for DDR operation. Figure 2-27 shows the Tristate Register Block with the Output Block

In SDR mode, ONEG1 feeds one of the flip-flops that then feeds the output. The flip-flop can be configured as D-type or latch. In DDR mode, ONEG1 and OPOS1 are fed into registers on the positive edge of the clock. Then in the next clock the registered OPOS1 is latched. A multiplexer running off the same clock cycle selects the correct register for feeding to the output (D0).

#### **Control Logic Block**

The control logic block allows the selection and modification of control signals for use in the PIO block. A clock signal is selected from general purpose routing, ECLK1, ECLK2 or a DQS signal (from the programmable DQS pin) and is provided to the input register block. The clock can optionally be inverted.

#### **DDR Memory Support**

PICs have additional circuitry to allow implementation of high speed source synchronous and DDR memory interfaces.

PICs have registered elements that support DDR memory interfaces. Interfaces on the left and right edges are designed for DDR memories that support 16 bits of data, whereas interfaces on the top and bottom are designed for memories that support 18 bits of data. One of every 16 PIOs on the left and right and one of every 18 PIOs on the top and bottom contain delay elements to facilitate the generation of DQS signals. The DQS signals feed the DQS buses which span the set of 16 or 18 PIOs. Figure 2-28 and Figure 2-29 show the DQS pin assignments in each set of PIOs.

The exact DQS pins are shown in a dual function in the Logic Signal Connections table in this data sheet. Additional detail is provided in the Signal Descriptions table. The DQS signal from the bus is used to strobe the DDR data from the memory into input register blocks. For additional information on using DDR memory support please see TN1138, LatticeXP2 High Speed I/O Interface.

#### **DQSXFER**

LatticeXP2 devices provide a DQSXFER signal to the output buffer to assist it in data transfer to DDR memories that require DQS strobe be shifted 90°. This shifted DQS strobe is generated by the DQSDEL block. The DQSXFER signal runs the span of the data bus.

#### sysIO Buffer

Each I/O is associated with a flexible buffer referred to as a sysIO buffer. These buffers are arranged around the periphery of the device in groups referred to as banks. The sysIO buffers allow users to implement the wide variety of standards that are found in today's systems including LVCMOS, SSTL, HSTL, LVDS and LVPECL.

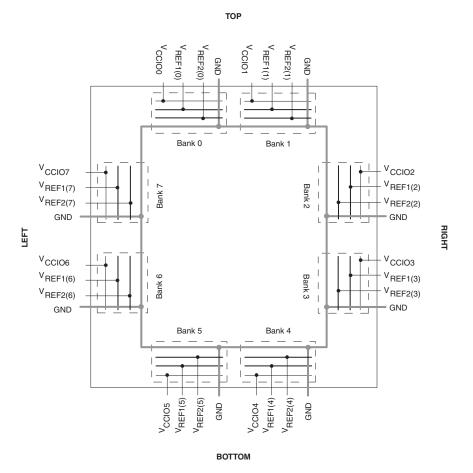

#### sysIO Buffer Banks

LatticeXP2 devices have eight sysIO buffer banks for user I/Os arranged two per side. Each bank is capable of supporting multiple I/O standards. Each sysIO bank has its own I/O supply voltage ( $V_{CCIO}$ ). In addition, each bank has voltage references,  $V_{REF1}$  and  $V_{REF2}$ , that allow it to be completely independent from the others. Figure 2-32 shows the eight banks and their associated supplies.

In LatticeXP2 devices, single-ended output buffers and ratioed input buffers (LVTTL, LVCMOS and PCI) are powered using  $V_{CCIO}$ . LVTTL, LVCMOS33, LVCMOS25 and LVCMOS12 can also be set as fixed threshold inputs independent of  $V_{CCIO}$ .

Each bank can support up to two separate  $V_{REF}$  voltages,  $V_{REF1}$  and  $V_{REF2}$ , that set the threshold for the referenced input buffers. Some dedicated I/O pins in a bank can be configured to be a reference voltage supply pin. Each I/O is individually configurable based on the bank's supply and reference voltages.

Figure 2-32. LatticeXP2 Banks

## Hot Socketing Specifications<sup>1, 2, 3, 4</sup>

| Symbol          | Parameter                    | Condition                        | Min. | Тур. | Max. | Units |

|-----------------|------------------------------|----------------------------------|------|------|------|-------|

| I <sub>DK</sub> | Input or I/O Leakage Current | $0 \le V_{IN} \le V_{IH}$ (MAX.) | _    | _    | +/-1 | mA    |

- 1. Insensitive to sequence of  $V_{CC}$ ,  $V_{CCAUX}$  and  $V_{CCIO}$ . However, assumes monotonic rise/fall rates for  $V_{CC}$ ,  $V_{CCAUX}$  and  $V_{CCIO}$ . 2.  $0 \le V_{CC} \le V_{CC}$  (MAX),  $0 \le V_{CCIO} \le V_{CCIO}$  (MAX) or  $0 \le V_{CCAUX} \le V_{CCAUX}$  (MAX).

- 3. I<sub>DK</sub> is additive to I<sub>PU</sub>, I<sub>PW</sub> or I<sub>BH</sub>.

- 4. LVCMOS and LVTTL only.

#### **ESD Performance**

Please refer to the LatticeXP2 Product Family Qualification Summary for complete qualification data, including ESD performance.

#### **DC Electrical Characteristics**

| Symbol                                            | Parameter                        | Condition                                                                                             | Min.                  | Тур. | Max.                  | Units |

|---------------------------------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------|------|-----------------------|-------|

| I I1                                              | Input or I/O Low Leakage         | $0 \leq V_{IN} \leq V_{CCIO}$                                                                         | _                     | _    | 10                    | μΑ    |

| I <sub>IL</sub> , I <sub>IH</sub> <sup>1</sup> Ir | linput of 1/O Low Leakage        | $V_{CCIO} \le V_{IN} \le V_{IH} \text{ (MAX)}$                                                        | _                     | _    | 150                   | μΑ    |

| I <sub>PU</sub>                                   | I/O Active Pull-up Current       | $0 \le V_{IN} \le 0.7 \ V_{CCIO}$                                                                     | -30                   | _    | -150                  | μΑ    |

| I <sub>PD</sub>                                   | I/O Active Pull-down Current     | $V_{IL}$ (MAX) $\leq V_{IN} \leq V_{CCIO}$                                                            | 30                    | _    | 210                   | μΑ    |

| I <sub>BHLS</sub>                                 | Bus Hold Low Sustaining Current  | $V_{IN} = V_{IL} (MAX)$                                                                               | 30                    | _    | _                     | μΑ    |

| I <sub>BHHS</sub>                                 | Bus Hold High Sustaining Current | $V_{IN} = 0.7 V_{CCIO}$                                                                               | -30                   | _    | _                     | μΑ    |

| I <sub>BHLO</sub>                                 | Bus Hold Low Overdrive Current   | $0 \le V_{IN} \le V_{CCIO}$                                                                           | _                     | _    | 210                   | μΑ    |

| I <sub>BHHO</sub>                                 | Bus Hold High Overdrive Current  | $0 \le V_{IN} \le V_{CCIO}$                                                                           | _                     | _    | -150                  | μΑ    |

| $V_{BHT}$                                         | Bus Hold Trip Points             |                                                                                                       | V <sub>IL</sub> (MAX) | _    | V <sub>IH</sub> (MIN) | V     |

| C1                                                | I/O Capacitance <sup>2</sup>     | $V_{CCIO} = 3.3V, 2.5V, 1.8V, 1.5V, 1.2V, V_{CC} = 1.2V, V_{IO} = 0 \text{ to } V_{IH} \text{ (MAX)}$ | _                     | 8    | _                     | pf    |

| C2                                                | Dedicated Input Capacitance      | $V_{CCIO} = 3.3V, 2.5V, 1.8V, 1.5V, 1.2V, V_{CC} = 1.2V, V_{IO} = 0 \text{ to } V_{IH} \text{ (MAX)}$ | _                     | 6    | _                     | pf    |

<sup>1.</sup> Input or I/O leakage current is measured with the pin configured as an input or as an I/O with the output driver tri-stated. It is not measured with the output driver active. Bus maintenance circuits are disabled.

<sup>2.</sup>  $T_A$  25°C, f = 1.0 MHz.

## sysIO Recommended Operating Conditions

|                                                       | V <sub>CCIO</sub> |      |       | V <sub>REF</sub> (V) |      |       |

|-------------------------------------------------------|-------------------|------|-------|----------------------|------|-------|

| Standard                                              | Min.              | Тур. | Max.  | Min.                 | Тур. | Max.  |

| LVCMOS33 <sup>2</sup>                                 | 3.135             | 3.3  | 3.465 | _                    | _    | _     |

| LVCMOS25 <sup>2</sup>                                 | 2.375             | 2.5  | 2.625 | _                    | _    | _     |

| LVCMOS18                                              | 1.71              | 1.8  | 1.89  | _                    | _    | _     |

| LVCMOS15                                              | 1.425             | 1.5  | 1.575 | _                    | _    | _     |

| LVCMOS12 <sup>2</sup>                                 | 1.14              | 1.2  | 1.26  | _                    | _    | _     |

| LVTTL33 <sup>2</sup>                                  | 3.135             | 3.3  | 3.465 | _                    | _    | _     |

| PCI33                                                 | 3.135             | 3.3  | 3.465 | _                    | _    | _     |

| SSTL18_I <sup>2</sup> ,<br>SSTL18_II <sup>2</sup>     | 1.71              | 1.8  | 1.89  | 0.833                | 0.9  | 0.969 |

| SSTL25_I <sup>2</sup> ,<br>SSTL25_II <sup>2</sup>     | 2.375             | 2.5  | 2.625 | 1.15                 | 1.25 | 1.35  |

| SSTL33_I <sup>2</sup> ,<br>SSTL33_II <sup>2</sup>     | 3.135             | 3.3  | 3.465 | 1.3                  | 1.5  | 1.7   |

| HSTL15_I <sup>2</sup>                                 | 1.425             | 1.5  | 1.575 | 0.68                 | 0.75 | 0.9   |

| HSTL18_I <sup>2</sup> ,<br>HSTL18_II <sup>2</sup>     | 1.71              | 1.8  | 1.89  | 0.816                | 0.9  | 1.08  |

| LVDS25 <sup>2</sup>                                   | 2.375             | 2.5  | 2.625 | _                    | _    | _     |

| MLVDS25 <sup>1</sup>                                  | 2.375             | 2.5  | 2.625 | _                    | _    | _     |

| LVPECL33 <sup>1, 2</sup>                              | 3.135             | 3.3  | 3.465 | _                    | _    | _     |

| BLVDS25 <sup>1, 2</sup>                               | 2.375             | 2.5  | 2.625 | _                    | _    | _     |

| RSDS <sup>1, 2</sup>                                  | 2.375             | 2.5  | 2.625 | _                    | _    | _     |

| SSTL18D_I <sup>2</sup> ,<br>SSTL18D_II <sup>2</sup>   | 1.71              | 1.8  | 1.89  | _                    | _    | _     |

| SSTL25D_ I <sup>2</sup> ,<br>SSTL25D_II <sup>2</sup>  | 2.375             | 2.5  | 2.625 | _                    | _    | _     |

| SSTL33D_ I <sup>2</sup> ,<br>SSTL33D_ II <sup>2</sup> | 3.135             | 3.3  | 3.465 | _                    | _    | _     |

| HSTL15D_ I <sup>2</sup>                               | 1.425             | 1.5  | 1.575 | _                    | _    | _     |

| HSTL18D_ I <sup>2</sup> ,<br>HSTL18D_ II <sup>2</sup> | 1.71              | 1.8  | 1.89  | _                    | _    | _     |

Inputs on chip. Outputs are implemented with the addition of external resistors.

Input on this standard does not depend on the value of V<sub>CCIO</sub>.

## sysIO Single-Ended DC Electrical Characteristics

| Input/Output | ,        | V <sub>IL</sub> V <sub>IH</sub> V <sub>OL</sub> V |                          | V <sub>IH</sub> |                       | V <sub>OH</sub>          |                        |                          |

|--------------|----------|---------------------------------------------------|--------------------------|-----------------|-----------------------|--------------------------|------------------------|--------------------------|

| Standard     | Min. (V) | Max. (V)                                          | Min. (V)                 | Max. (V)        | Max. (V)              | Min. (V)                 | I <sub>OL</sub> 1 (mA) | I <sub>OH</sub> ¹ (mA)   |

| LVCMOS33     | -0.3     | 0.8                                               | 2.0                      | 3.6             | 0.4                   | V <sub>CCIO</sub> - 0.4  | 20, 16,<br>12, 8, 4    | -20, -16,<br>-12, -8, -4 |

|              |          |                                                   |                          |                 | 0.2                   | V <sub>CCIO</sub> - 0.2  | 0.1                    | -0.1                     |

| LVTTL33      | -0.3     | 0.8                                               | 2.0                      | 3.6             | 0.4                   | V <sub>CCIO</sub> - 0.4  | 20, 16,<br>12, 8, 4    | -20, -16,<br>-12, -8, -4 |

|              |          |                                                   |                          |                 | 0.2                   | V <sub>CCIO</sub> - 0.2  | 0.1                    | -0.1                     |

| LVCMOS25     | -0.3     | 0.7                                               | 1.7                      | 3.6             | 0.4                   | V <sub>CCIO</sub> - 0.4  | 20, 16,<br>12, 8, 4    | -20, -16,<br>-12, -8, -4 |

|              |          |                                                   |                          |                 | 0.2                   | V <sub>CCIO</sub> - 0.2  | 0.1                    | -0.1                     |

| LVCMOS18     | -0.3     | 0.35 V <sub>CCIO</sub>                            | 0.65 V <sub>CCIO</sub>   | 3.6             | 0.4                   | V <sub>CCIO</sub> - 0.4  | 16, 12,<br>8, 4        | -16, -12,<br>-8, -4      |

|              |          |                                                   |                          |                 | 0.2                   | V <sub>CCIO</sub> - 0.2  | 0.1                    | -0.1                     |

| LVCMOS15     | -0.3     | 0.35 V <sub>CCIO</sub>                            | 0.65 V <sub>CCIO</sub>   | 3.6             | 0.4                   | V <sub>CCIO</sub> - 0.4  | 8, 4                   | -8, -4                   |

| LVOIVIOUTS   | -0.0     | 0.33 ACCIQ                                        | 0.02 ACCIO               | 0.0             | 0.2                   | V <sub>CCIO</sub> - 0.2  | 0.1                    | -0.1                     |

| LVCMOS12     | -0.3     | 0.35 V <sub>CC</sub>                              | 0.65 V <sub>CC</sub>     | 3.6             | 0.4                   | V <sub>CCIO</sub> - 0.4  | 6, 2                   | -6, -2                   |

|              | 0.0      |                                                   |                          |                 | 0.2                   | V <sub>CCIO</sub> - 0.2  | 0.1                    | -0.1                     |

| PCI33        | -0.3     | 0.3 V <sub>CCIO</sub>                             | 0.5 V <sub>CCIO</sub>    | 3.6             | 0.1 V <sub>CCIO</sub> | 0.9 V <sub>CCIO</sub>    | 1.5                    | -0.5                     |

| SSTL33_I     | -0.3     | V <sub>REF</sub> - 0.2                            | V <sub>REF</sub> + 0.2   | 3.6             | 0.7                   | V <sub>CCIO</sub> - 1.1  | 8                      | -8                       |

| SSTL33_II    | -0.3     | V <sub>REF</sub> - 0.2                            | V <sub>REF</sub> + 0.2   | 3.6             | 0.5                   | V <sub>CCIO</sub> - 0.9  | 16                     | -16                      |

| SSTL25_I     | -0.3     | V <sub>RFF</sub> - 0.18                           | V <sub>RFF</sub> + 0.18  | 3.6             | 0.54                  | V <sub>CCIO</sub> - 0.62 | 7.6                    | -7.6                     |

|              | 0.0      | THEF 0.10                                         | THEF ! O. 10             | 0.0             | 0.01                  | *0010 0.02               | 12                     | -12                      |

| SSTL25_II    | -0.3     | V <sub>RFF</sub> - 0.18                           | V <sub>REF</sub> + 0.18  | 3.6             | 0.35                  | V <sub>CCIO</sub> - 0.43 | 15.2                   | -15.2                    |

|              |          |                                                   |                          |                 | 0.00                  | • (() 0.10               | 20                     | -20                      |

| SSTL18_I     | -0.3     | V <sub>REF</sub> - 0.125                          | V <sub>REF</sub> + 0.125 | 3.6             | 0.4                   | V <sub>CCIO</sub> - 0.4  | 6.7                    | -6.7                     |

| SSTL18_II    | -0.3     | V <sub>DEE</sub> - 0 125                          | V <sub>REF</sub> + 0.125 | 3.6             | 0.28                  | V <sub>CCIO</sub> - 0.28 | 8                      | -8                       |

| 001210_11    | 0.0      | VREF 0.120                                        | VREF 1 0.120             | 0.0             | 0.20                  | VCCIO 0.20               | 11                     | -11                      |

| HSTL15_I     | -0.3     | V <sub>RFF</sub> - 0.1                            | V <sub>RFF</sub> + 0.1   | 3.6             | 0.4                   | V <sub>CCIO</sub> - 0.4  | 4                      | -4                       |

|              | 0.0      | HEF VII                                           | - HEF ' V''              | 0.0             | <b>U.</b> 1           | .000 0.1                 | 8                      | -8                       |

| HSTL18_I     | -0.3     | V <sub>RFF</sub> - 0.1                            | V <sub>REF</sub> + 0.1   | 3.6             | 0.4                   | V <sub>CCIO</sub> - 0.4  | 8                      | -8                       |

|              |          |                                                   |                          |                 |                       |                          | 12                     | -12                      |

| HSTL18_II    | -0.3     | V <sub>REF</sub> - 0.1                            | V <sub>REF</sub> + 0.1   | 3.6             | 0.4                   | V <sub>CCIO</sub> - 0.4  | 16                     | -16                      |

<sup>1.</sup> The average DC current drawn by I/Os between GND connections, or between the last GND in an I/O bank and the end of an I/O bank, as shown in the logic signal connections table shall not exceed n \* 8mA, where n is the number of I/Os between bank GND connections or between the last GND in a bank and the end of a bank.

## sysIO Differential Electrical Characteristics LVDS

#### **Over Recommended Operating Conditions**

| Parameter                           | Description                                                | Test Conditions                                                | Min.   | Тур. | Max.  | Units |

|-------------------------------------|------------------------------------------------------------|----------------------------------------------------------------|--------|------|-------|-------|

| V <sub>INP</sub> , V <sub>INM</sub> | Input Voltage                                              |                                                                | 0      |      | 2.4   | V     |

| V <sub>CM</sub>                     | Input Common Mode Voltage                                  | Half the Sum of the Two Inputs                                 | 0.05   | _    | 2.35  | V     |

| $V_{THD}$                           | Differential Input Threshold                               | Difference Between the Two Inputs                              | +/-100 | _    | _     | mV    |

| I <sub>IN</sub>                     | Input Current                                              | Power On or Power Off                                          | _      | _    | +/-10 | μΑ    |

| V <sub>OH</sub>                     | Output High Voltage for V <sub>OP</sub> or V <sub>OM</sub> | R <sub>T</sub> = 100 Ohm                                       | _      | 1.38 | 1.60  | V     |

| V <sub>OL</sub>                     | Output Low Voltage for V <sub>OP</sub> or V <sub>OM</sub>  | R <sub>T</sub> = 100 Ohm                                       | 0.9V   | 1.03 | _     | V     |

| $V_{OD}$                            | Output Voltage Differential                                | (V <sub>OP</sub> - V <sub>OM</sub> ), R <sub>T</sub> = 100 Ohm | 250    | 350  | 450   | mV    |

| ΔV <sub>OD</sub>                    | Change in V <sub>OD</sub> Between High and Low             |                                                                | _      | _    | 50    | mV    |

| V <sub>OS</sub>                     | Output Voltage Offset                                      | $(V_{OP} + V_{OM})/2$ , $R_T = 100 \text{ Ohm}$                | 1.125  | 1.20 | 1.375 | V     |

| $\Delta V_{OS}$                     | Change in V <sub>OS</sub> Between H and L                  |                                                                | _      | _    | 50    | mV    |

| I <sub>SA</sub>                     | Output Short Circuit Current                               | V <sub>OD</sub> = 0V Driver Outputs Shorted to Ground          | _      | _    | 24    | mA    |

| I <sub>SAB</sub>                    | Output Short Circuit Current                               | V <sub>OD</sub> = 0V Driver Outputs Shorted to Each Other      | _      |      | 12    | mA    |

#### **Differential HSTL and SSTL**

Differential HSTL and SSTL outputs are implemented as a pair of complementary single-ended outputs. All allowable single-ended output classes (class I and class II) are supported in this mode.

For further information on LVPECL, RSDS, MLVDS, BLVDS and other differential interfaces please see details in additional technical notes listed at the end of this data sheet.

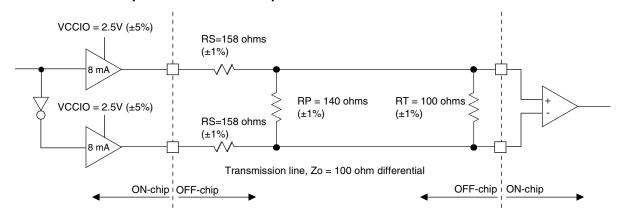

#### LVDS25E

The top and bottom sides of LatticeXP2 devices support LVDS outputs via emulated complementary LVCMOS outputs in conjunction with a parallel resistor across the driver outputs. The scheme shown in Figure 3-1 is one possible solution for point-to-point signals.

Figure 3-1. LVDS25E Output Termination Example

#### **LVPECL**

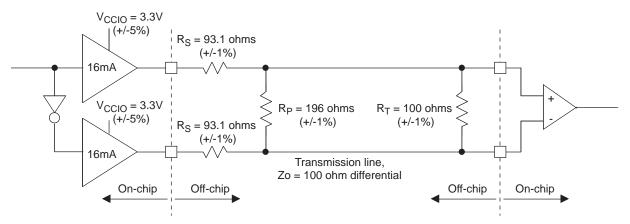

The LatticeXP2 devices support the differential LVPECL standard. This standard is emulated using complementary LVCMOS outputs in conjunction with a parallel resistor across the driver outputs. The LVPECL input standard is supported by the LVDS differential input buffer. The scheme shown in Figure 3-3 is one possible solution for point-to-point signals.

Figure 3-3. Differential LVPECL

Table 3-3. LVPECL DC Conditions1

| Parameter         | Description                                         | Typical | Units |

|-------------------|-----------------------------------------------------|---------|-------|

| V <sub>CCIO</sub> | Output Driver Supply (+/-5%)                        | 3.30    | V     |

| Z <sub>OUT</sub>  | Driver Impedance                                    | 10      | Ω     |

| $R_S$             | Driver Series Resistor (+/-1%)                      | 93      | Ω     |

| R <sub>P</sub>    | Driver Parallel Resistor (+/-1%)                    | 196     | Ω     |

| R <sub>T</sub>    | Receiver Termination (+/-1%)                        | 100     | Ω     |

| V <sub>OH</sub>   | Output High Voltage (After R <sub>P</sub> )         | 2.05    | V     |

| V <sub>OL</sub>   | Output Low Voltage (After R <sub>P</sub> )          | 1.25    | V     |

| V <sub>OD</sub>   | Output Differential Voltage (After R <sub>P</sub> ) | 0.80    | V     |

| V <sub>CM</sub>   | Output Common Mode Voltage                          | 1.65    | V     |

| Z <sub>BACK</sub> | Back Impedance                                      | 100.5   | Ω     |

| I <sub>DC</sub>   | DC Output Current                                   | 12.11   | mA    |

<sup>1.</sup> For input buffer, see LVDS table.

#### **RSDS**

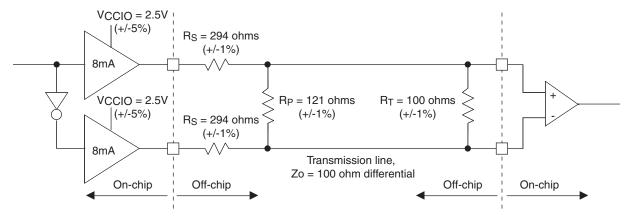

The LatticeXP2 devices support differential RSDS standard. This standard is emulated using complementary LVC-MOS outputs in conjunction with a parallel resistor across the driver outputs. The RSDS input standard is supported by the LVDS differential input buffer. The scheme shown in Figure 3-4 is one possible solution for RSDS standard implementation. Resistor values in Figure 3-4 are industry standard values for 1% resistors.

Figure 3-4. RSDS (Reduced Swing Differential Standard)

Table 3-4. RSDS DC Conditions1

| Parameter         | Description                                         | Typical | Units |

|-------------------|-----------------------------------------------------|---------|-------|

| V <sub>CCIO</sub> | Output Driver Supply (+/-5%)                        | 2.50    | V     |

| Z <sub>OUT</sub>  | Driver Impedance                                    | 20      | Ω     |

| $R_S$             | Driver Series Resistor (+/-1%)                      | 294     | Ω     |

| R <sub>P</sub>    | Driver Parallel Resistor (+/-1%)                    | 121     | Ω     |

| R <sub>T</sub>    | Receiver Termination (+/-1%)                        | 100     | Ω     |

| V <sub>OH</sub>   | Output High Voltage (After R <sub>P</sub> )         | 1.35    | V     |

| V <sub>OL</sub>   | Output Low Voltage (After R <sub>P</sub> )          | 1.15    | V     |

| V <sub>OD</sub>   | Output Differential Voltage (After R <sub>P</sub> ) | 0.20    | V     |

| $V_{CM}$          | Output Common Mode Voltage                          | 1.25    | V     |

| Z <sub>BACK</sub> | Back Impedance                                      | 101.5   | Ω     |

| I <sub>DC</sub>   | DC Output Current                                   | 3.66    | mA    |

<sup>1.</sup> For input buffer, see LVDS table.

#### **MLVDS**

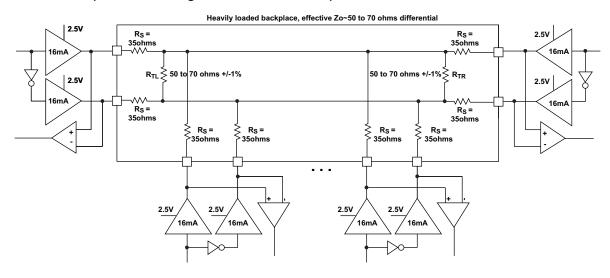

The LatticeXP2 devices support the differential MLVDS standard. This standard is emulated using complementary LVCMOS outputs in conjunction with a parallel resistor across the driver outputs. The MLVDS input standard is supported by the LVDS differential input buffer. The scheme shown in Figure 3-5 is one possible solution for MLVDS standard implementation. Resistor values in Figure 3-5 are industry standard values for 1% resistors.

Figure 3-5. MLVDS (Reduced Swing Differential Standard)

Table 3-5. MLVDS DC Conditions1

|                   |                                                      | Typical        |                |       |

|-------------------|------------------------------------------------------|----------------|----------------|-------|

| Parameter         | Description                                          | <b>Zo=50</b> Ω | <b>Zo=70</b> Ω | Units |

| V <sub>CCIO</sub> | Output Driver Supply (+/-5%)                         | 2.50           | 2.50           | V     |

| Z <sub>OUT</sub>  | Driver Impedance                                     | 10.00          | 10.00          | Ω     |

| R <sub>S</sub>    | Driver Series Resistor (+/-1%)                       | 35.00          | 35.00          | Ω     |

| R <sub>TL</sub>   | Driver Parallel Resistor (+/-1%)                     | 50.00          | 70.00          | Ω     |

| R <sub>TR</sub>   | Receiver Termination (+/-1%)                         | 50.00          | 70.00          | Ω     |

| V <sub>OH</sub>   | Output High Voltage (After R <sub>TL</sub> )         | 1.52           | 1.60           | V     |

| V <sub>OL</sub>   | Output Low Voltage (After R <sub>TL</sub> )          | 0.98           | 0.90           | V     |

| V <sub>OD</sub>   | Output Differential Voltage (After R <sub>TL</sub> ) | 0.54           | 0.70           | V     |

| V <sub>CM</sub>   | Output Common Mode Voltage                           | 1.25           | 1.25           | V     |

| I <sub>DC</sub>   | DC Output Current                                    | 21.74          | 20.00          | mA    |

<sup>1.</sup> For input buffer, see LVDS table.

For further information on LVPECL, RSDS, MLVDS, BLVDS and other differential interfaces please see details of additional technical information at the end of this data sheet.

## FlashBAK Time (from EBR to Flash)

#### **Over Recommended Operating Conditions**

| Device | EBR Density (Bits) | Time (Typ.) | Units |

|--------|--------------------|-------------|-------|

| XP2-5  | 166K               | 1.5         | S     |

| XP2-8  | 221K               | 1.5         | S     |

| XP2-17 | 276K               | 1.5         | S     |

| XP2-30 | 387K               | 2.0         | S     |

| XP2-40 | 885K               | 3.0         | S     |

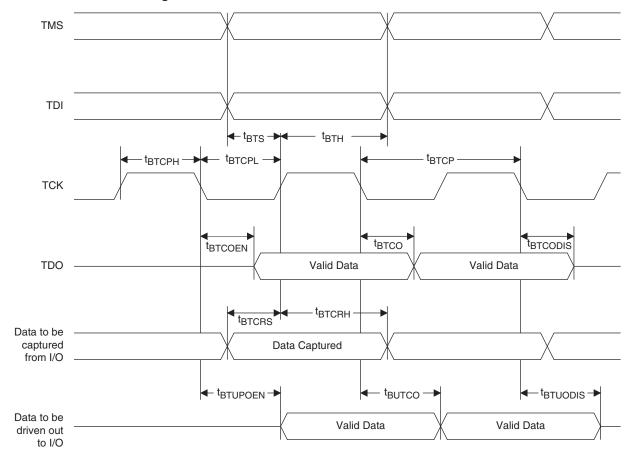

## **JTAG Port Timing Specifications**

| Symbol               | Parameter                                                          | Min.     | Max. | Units |

|----------------------|--------------------------------------------------------------------|----------|------|-------|

| f <sub>MAX</sub>     | TCK Clock Frequency                                                | <u> </u> | 25   | MHz   |

| t <sub>BTCP</sub>    | TCK [BSCAN] clock pulse width                                      | 40       | _    | ns    |

| t <sub>BTCPH</sub>   | TCK [BSCAN] clock pulse width high                                 | 20       | _    | ns    |

| t <sub>BTCPL</sub>   | TCK [BSCAN] clock pulse width low                                  | 20       | _    | ns    |

| t <sub>BTS</sub>     | TCK [BSCAN] setup time                                             | 8        | _    | ns    |

| t <sub>BTH</sub>     | TCK [BSCAN] hold time                                              | 10       | _    | ns    |

| t <sub>BTRF</sub>    | TCK [BSCAN] rise/fall time                                         | 50       | _    | mV/ns |

| t <sub>BTCO</sub>    | TAP controller falling edge of clock to valid output               | _        | 10   | ns    |

| t <sub>BTCODIS</sub> | TAP controller falling edge of clock to valid disable              | _        | 10   | ns    |

| t <sub>BTCOEN</sub>  | TAP controller falling edge of clock to valid enable               | _        | 10   | ns    |

| t <sub>BTCRS</sub>   | BSCAN test capture register setup time                             | 8        | _    | ns    |

| t <sub>BTCRH</sub>   | BSCAN test capture register hold time                              | 25       | _    | ns    |

| t <sub>BUTCO</sub>   | BSCAN test update register, falling edge of clock to valid output  | _        | 25   | ns    |

| t <sub>BTUODIS</sub> | BSCAN test update register, falling edge of clock to valid disable | _        | 25   | ns    |

| t <sub>BTUPOEN</sub> | BSCAN test update register, falling edge of clock to valid enable  | _        | 25   | ns    |

Figure 3-10. JTAG Port Timing Waveforms

## LatticeXP2 Family Data Sheet Pinout Information

February 2012 Data Sheet DS1009

## **Signal Descriptions**

| Signal Name                                                                          | I/O             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|--------------------------------------------------------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| General Purpose                                                                      | General Purpose |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|                                                                                      | B] I/O          | [Edge] indicates the edge of the device on which the pad is located. Valid edge designations are L (Left), B (Bottom), R (Right), T (Top).                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| P[Edge] [Row/Column Number*]_[A/B]                                                   |                 | [Row/Column Number] indicates the PFU row or the column of the device on which the PIC exists. When Edge is T (Top) or B (Bottom), only need to specify Row Number. When Edge is L (Left) or R (Right), only need to specify Column Number.                                                                                                                                                                                                                                                            |  |  |  |  |  |

| . [2-25-] [. 16-17-6-14-17-14-17-14-17-14-17-14-14-14-14-14-14-14-14-14-14-14-14-14- |                 | [A/B] indicates the PIO within the PIC to which the pad is connected. Some of these user-programmable pins are shared with special function pins. These pins, when not used as special purpose pins, can be programmed as I/Os for user logic. During configuration the user-programmable I/Os are tri-stated with an internal pull-up resistor enabled. If any pin is not used (or not bonded to a package pin), it is also tri-stated with an internal pull-up resistor enabled after configuration. |  |  |  |  |  |

| GSRN                                                                                 |                 | Global RESET signal (active low). Any I/O pin can be GSRN.                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| NC                                                                                   | _               | No connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| GND                                                                                  | _               | Ground. Dedicated pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| V <sub>CC</sub>                                                                      | _               | Power supply pins for core logic. Dedicated pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| V <sub>CCAUX</sub>                                                                   | _               | Auxiliary power supply pin. This dedicated pin powers all the differential and referenced input buffers.                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| V <sub>CCPLL</sub>                                                                   | _               | PLL supply pins. csBGA, PQFP and TQFP packages only.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| V <sub>CCIOx</sub>                                                                   | _               | Dedicated power supply pins for I/O bank x.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| V <sub>REF1_x</sub> , V <sub>REF2_x</sub>                                            | _               | Reference supply pins for I/O bank x. Pre-determined pins in each bank are assigned as $V_{\text{REF}}$ inputs. When not used, they may be used as I/O pins.                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| •                                                                                    | er progr        | ammable I/O pins when not in use for PLL or clock pins)                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| [LOC][num]_V <sub>CCPLL</sub>                                                        | _               | Power supply pin for PLL: LLC, LRC, URC, ULC, num = row from center.                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| [LOC][num]_GPLL[T, C]_IN_A                                                           | I               | General Purpose PLL (GPLL) input pads: LLC, LRC, URC, ULC, num = row from center, T = true and C = complement, index A,B,Cat each side.                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| [LOC][num]_GPLL[T, C]_FB_A                                                           | I               | Optional feedback GPLL input pads: LLC, LRC, URC, ULC, num = row from center, T = true and C = complement, index A,B,Cat each side.                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| PCLK[T, C]_[n:0]_[3:0]                                                               | I               | Primary Clock pads, $T = \text{true}$ and $C = \text{complement}$ , $n \text{ per side}$ , indexed by bank and 0,1,2,3 within bank.                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| [LOC]DQS[num]                                                                        | I               | DQS input pads: T (Top), R (Right), B (Bottom), L (Left), DQS, num = ball function number. Any pad can be configured to be output.                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| Test and Programming (Dedicated Pins)                                                |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| TMS                                                                                  | I               | Test Mode Select input, used to control the 1149.1 state machine. Pull-up is enabled during configuration.                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| тск                                                                                  | I               | Test Clock input pin, used to clock the 1149.1 state machine. No pull-up enabled.                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| TDI                                                                                  | I               | Test Data in pin. Used to load data into device using 1149.1 state machine. After power-up, this TAP port can be activated for configuration by sending appropriate command. (Note: once a configuration port is selected it is locked. Another configuration port cannot be selected until the power-up sequence). Pull-up is enabled during configuration.                                                                                                                                           |  |  |  |  |  |

© 2012 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

## PICs and DDR Data (DQ) Pins Associated with the DDR Strobe (DQS) Pin

| PICs Associated with DQS Strobe | PIO Within PIC                         | DDR Strobe (DQS) and<br>Data (DQ) Pins |  |  |  |  |  |

|---------------------------------|----------------------------------------|----------------------------------------|--|--|--|--|--|

| For Left and Right Edges        | For Left and Right Edges of the Device |                                        |  |  |  |  |  |

| P[Edge] [n-4]                   | Α                                      | DQ                                     |  |  |  |  |  |

| F[Edge] [II-4]                  | В                                      | DQ                                     |  |  |  |  |  |

| P[Edge] [n-3]                   | Α                                      | DQ                                     |  |  |  |  |  |

|                                 | В                                      | DQ                                     |  |  |  |  |  |

| P[Edge] [n-2]                   | Α                                      | DQ                                     |  |  |  |  |  |

| i [Luge] [ii-2]                 | В                                      | DQ                                     |  |  |  |  |  |

| P[Edge] [n-1]                   | Α                                      | DQ                                     |  |  |  |  |  |

| [=u9e] [II-1]                   | В                                      | DQ                                     |  |  |  |  |  |

| P[Edge] [n]                     | Α                                      | [Edge]DQSn                             |  |  |  |  |  |

| P[Edge] [n]                     | В                                      | DQ                                     |  |  |  |  |  |

| P[Edge] [n+1]                   | Α                                      | DQ                                     |  |  |  |  |  |

| i [Edge] [ii+1]                 | В                                      | DQ                                     |  |  |  |  |  |

| P[Edge] [n+2]                   | Α                                      | DQ                                     |  |  |  |  |  |

| i [Edge] [iii 2]                | В                                      | DQ                                     |  |  |  |  |  |

| P[Edge] [n+3]                   | Α                                      | DQ                                     |  |  |  |  |  |

| i [Edge] [ii+o]                 | В                                      | DQ                                     |  |  |  |  |  |

| For Top and Bottom Edge         | es of the Device                       |                                        |  |  |  |  |  |

| P[Edge] [n-4]                   | Α                                      | DQ                                     |  |  |  |  |  |

| i [Edgo] [ii i]                 | В                                      | DQ                                     |  |  |  |  |  |

| P[Edge] [n-3]                   | Α                                      | DQ                                     |  |  |  |  |  |

|                                 | В                                      | DQ                                     |  |  |  |  |  |

| P[Edge] [n-2]                   | Α                                      | DQ                                     |  |  |  |  |  |

|                                 | В                                      | DQ                                     |  |  |  |  |  |

| P[Edge] [n-1]                   | Α                                      | DQ                                     |  |  |  |  |  |

| [=u9e] [II-1]                   | В                                      | DQ                                     |  |  |  |  |  |

| P[Edge] [n]                     | Α                                      | [Edge]DQSn                             |  |  |  |  |  |

| r[Euge] [ii]                    | В                                      | DQ                                     |  |  |  |  |  |

| P[Edge] [n+1]                   | Α                                      | DQ                                     |  |  |  |  |  |

| [=390][]                        | В                                      | DQ                                     |  |  |  |  |  |

| P[Edge] [n+2]                   | Α                                      | DQ                                     |  |  |  |  |  |

| . [8-]                          | В                                      | DQ                                     |  |  |  |  |  |

| P[Edge] [n+3]                   | Α                                      | DQ                                     |  |  |  |  |  |

| . [=490] [0]                    | В                                      | DQ                                     |  |  |  |  |  |

| P[Edge] [n+4]                   | Α                                      | DQ                                     |  |  |  |  |  |

| . [=490] [111 1]                | В                                      | DQ                                     |  |  |  |  |  |

#### Notes:

- 1. "n" is a row PIC number.

- 2. The DDR interface is designed for memories that support one DQS strobe up to 16 bits of data for the left and right edges and up to 18 bits of data for the top and bottom edges. In some packages, all the potential DDR data (DQ) pins may not be available. PIC numbering definitions are provided in the "Signal Names" column of the Signal Descriptions table.

# LatticeXP2 Family Data Sheet Revision History

September 2014 Data Sheet DS1009

### **Revision History**

| Slave SPI ports of the device. The SRAM configuration space can be infinitely reconfigured through the JTAG and Master SPI ports."  Added External Slave SPI Port to Serial TAG Memory section. Upide Serial TAG Memory diagram.  DC and Switching Characteristics  DC and Switching Characteristics  Added "8W" specification to Hot Socketing Specifications table.  Updated Timing Tables  Clarifications for IIH in DC Electrical Characteristics table.  Added LVCMOS33D section  Updated DOA and DOA (Regs) to EBR Timing diagrams.  Removed Master Clock Frequency and Duty Cycle sections from LatticeXP2 sysCONFIG Port Timing Specifications table. These a listed on the On-chip Oscillator and Configuration Master Clock Clarifications to the On-chip Oscillator and Configuration Master Clock Clarified On-chip Oscillator and Configuration Master Clock Clarified On-chip Oscillator and Configuration of tscs. tscss, and sparameters. Removed tscp parameter.  Clarified On-chip Oscillator documentation  Added Switching Test Conditions  Pinout Information  Added "True LVDS Pairs Bonding Out per Bank," "DDR Banks Bor Out per I/O Bank," and "PCI capable I/Os Bonding Out per Bank" Information Summary in place of previous blank table "PCI and DI Capabilities of the Device-Package Combinations"  Removed pinout listing. This information is available on the Lattice product web pages  Ordering Information  Added XP2-17 "8W" and all other family OPNs.  Updated Absolute Maximum Ratings footnotes.  Updated Recommended Operating Conditions Table footnotes.  Updated Supply Current (Standby) Table  Updated Programming and Erase Flash Supply Current Table  Updated Register to Register Performance Table                                                                                                                                                                                                                                                                                                                                                                        | Date                | Version         | Section                                                        | Change Summary                                                                                                                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Characteristics    Dipotent Information   Added Thermal Management text section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | May 2007            | 01.1            | _                                                              | Initial release.                                                                                                                                                                                                                                          |

| Pinout Information  February 2008  O1.3  Architecture  Added LVCMOS33D to Supported Output Standards table.  Clarified: "This Flash can be programmed through either the JTAG Slave SPI ports of the device. The SRAM configuration space can be infinitely reconfigured through the JTAG and Master SPI ports.'  Added External Slave SPI Port to Serial TAG Memory section. Up Serial TAG Memory section up Serial TAG Memory section. U | September 2007 01.2 | 01.2            |                                                                | Added JTAG Port Timing Waveforms diagram.                                                                                                                                                                                                                 |

| Added LVCMOS33D to Supported Output Standards table.  Clarified: "This Flash can be programmed through either the JTAC Slave SPI ports of the device. The SRAM configuration space can be infinitely reconfigured through the JTAC and Master SPI ports: Added External Slave SPI Port to Serial TAG Memory section. Upsterial TAG Memory diagram.  DC and Switching Characteristics  DC and Switching Characteristics Added "8w" specification to Hot Socketing Specifications table.  Updated Timing Tables  Clarifications for III in DC Electrical Characteristics table.  Added LVCMOS33D section  Updated DOA and DOA (Regs) to EBR Timing diagrams.  Removed Master Clock Frequency and Duty Cycle sections from LatticeXP2 sysCONFIG Port Timing Specifications table. These a listed on the On-chip Oscillator and Configuration Master Clock Citeristics table.  Changed CSSPIN to CSSPISN in description of tscs. tscss. and to parameters. Removed tscs parameter.  Clarified On-chip Oscillator documentation  Added Switching Test Conditions  Added "True LVDS Pairs Bonding Out per Bank," "DDR Banks Bor Out per I/O Bank," and "PCI capable I/Os Bonding Out per Bank" Information Summary in place of previous blank table "PCI and DI Capabilities of the Device-Package Combinations"  Removed pinout listing. This information is available on the Lattice product web pages  Ordering Information  Added XP2-17 "8W" and all other family OPNs.  Updated Absolute Maximum Ratings footnotes.  Updated Recommended Operating Conditions Table footnotes.  Updated Programming and Erase Flash Supply Current Table  Updated Programming and Erase Flash Supply Current Table  Updated Register to Register Performance Table                                                                                                                                                                                                                                     |                     |                 |                                                                | Updated sysCLOCK PLL Timing table.                                                                                                                                                                                                                        |

| Clarified: "This Flash can be programmed through either the JTAG Slave SPI ports of the device. The SRAM configuration space can be infinitely reconfigured through the JTAG and Master SPI ports. Added External Slave SPI Port to Serial TAG Memory section. Upserial TAG Memory diagram.  DC and Switching Characteristics  DC and Switching Characteristics  Added "8W" specification to Hot Socketing Specifications table.  Updated Timing Tables  Clarifications for IIH in DC Electrical Characteristics table.  Added LVCMOS33D section  Updated DOA and DOA (Regs) to EBR Timing diagrams.  Removed Master Clock Frequency and Duty Cycle sections from LatticeXP2 sysCONFIG Port Timing Specifications table. These a listed on the On-chip Oscillator and Configuration Master Clock Clarified On-chip Oscillator and Configuration Master Clock Clarified On-chip Oscillator documentation  Added Switching Test Conditions  Pinout Information  Added "True LVDS Pairs Bonding Out per Bank," "DDR Banks Bor Out per I/O Bank," and "PCI capable I/Os Bonding Out per Bank" to Information Summary in place of previous blank table "PCI and DI Capabilities of the Device-Package Combinations"  Removed pinout listing. This information is available on the Lattice product web pages  Ordering Information  Added XP2-17 "8W" and all other family OPNs.  Updated Absolute Maximum Ratings footnotes.  Updated Recommended Operating Conditions Table footnotes.  Updated Programming and Erase Flash Supply Current Table  Updated Programming and Erase Flash Supply Current Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                     |                 | Pinout Information                                             | Added Thermal Management text section.                                                                                                                                                                                                                    |

| Slave SPI ports of the device. The SRAM configuration space can be infinitely reconfigured through the JTAG and Master SPI ports."  Added External Slave SPI Port to Serial TAG Memory section. Upserial TAG Memory diagram.  DC and Switching Characteristics  DC and Switching Characteristics  Added "8W" specification to Hot Socketing Specifications table.  Updated Timing Tables  Clarifications for IIH in DC Electrical Characteristics table.  Added LVCMOS33D section  Updated DOA and DOA (Regs) to EBR Timing diagrams.  Removed Master Clock Frequency and Duty Cycle sections from LatticeXP2 sysCONFIG Port Timing Specifications table. These a listed on the On-chip Oscillator and Configuration Master Clock Cl teristics table.  Changed CSSPIN to CSSPISN in description of t <sub>SCS</sub> , t <sub>SCSS</sub> , and sparameters. Removed t <sub>SCE</sub> parameter.  Clarified On-chip Oscillator documentation  Added Switching Test Conditions  Pinout Information  Added "True LVDS Pairs Bonding Out per Bank," "DDR Banks Bor Out per I/O Bank," and "PCI capable I/Os Bonding Out per Bank" Information Summary in place of previous blank table "PCI and DI Capabilities of the Device-Package Combinations"  Removed pinout listing. This information is available on the Lattice product web pages  Ordering Information  April 2008  O1.4  DC and Switching Characteristics  Updated Absolute Maximum Ratings footnotes.  Updated Recommended Operating Conditions Table footnotes.  Updated Programming and Erase Flash Supply Current Table  Updated Programming and Erase Flash Supply Current Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | February 2008       | 01.3            | Architecture                                                   | Added LVCMOS33D to Supported Output Standards table.                                                                                                                                                                                                      |

| DC and Switching Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                     |                 |                                                                | Clarified: "This Flash can be programmed through either the JTAG or Slave SPI ports of the device. The SRAM configuration space can also be infinitely reconfigured through the JTAG and Master SPI ports."                                               |