Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                        |

|--------------------------------|-------------------------------------------------------------------------------|

| Number of LABs/CLBs            | 3625                                                                          |

| Number of Logic Elements/Cells | 29000                                                                         |

| Total RAM Bits                 | 396288                                                                        |

| Number of I/O                  | 201                                                                           |

| Number of Gates                | -                                                                             |

| Voltage - Supply               | 1.14V ~ 1.26V                                                                 |

| Mounting Type                  | Surface Mount                                                                 |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                               |

| Package / Case                 | 256-LBGA                                                                      |

| Supplier Device Package        | 256-FTBGA (17x17)                                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfxp2-30e-6ftn256c |

|                                |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# LatticeXP2 Family Data Sheet Architecture

#### August 2014

Data Sheet DS1009

# **Architecture Overview**

Each LatticeXP2 device contains an array of logic blocks surrounded by Programmable I/O Cells (PIC). Interspersed between the rows of logic blocks are rows of sysMEM<sup>™</sup> Embedded Block RAM (EBR) and a row of sys-DSP<sup>™</sup> Digital Signal Processing blocks as shown in Figure 2-1.

On the left and right sides of the Programmable Functional Unit (PFU) array, there are Non-volatile Memory Blocks. In configuration mode the nonvolatile memory is programmed via the IEEE 1149.1 TAP port or the sysCONFIG<sup>™</sup> peripheral port. On power up, the configuration data is transferred from the Non-volatile Memory Blocks to the configuration SRAM. With this technology, expensive external configuration memory is not required, and designs are secured from unauthorized read-back. This transfer of data from non-volatile memory to configuration SRAM via wide busses happens in microseconds, providing an "instant-on" capability that allows easy interfacing in many applications. LatticeXP2 devices can also transfer data from the sysMEM EBR blocks to the Non-volatile Memory Blocks at user request.

There are two kinds of logic blocks, the PFU and the PFU without RAM (PFF). The PFU contains the building blocks for logic, arithmetic, RAM and ROM functions. The PFF block contains building blocks for logic, arithmetic and ROM functions. Both PFU and PFF blocks are optimized for flexibility allowing complex designs to be implemented quickly and efficiently. Logic Blocks are arranged in a two-dimensional array. Only one type of block is used per row.

LatticeXP2 devices contain one or more rows of sysMEM EBR blocks. sysMEM EBRs are large dedicated 18Kbit memory blocks. Each sysMEM block can be configured in a variety of depths and widths of RAM or ROM. In addition, LatticeXP2 devices contain up to two rows of DSP Blocks. Each DSP block has multipliers and adder/accumulators, which are the building blocks for complex signal processing capabilities.

Each PIC block encompasses two PIOs (PIO pairs) with their respective sysIO buffers. The sysIO buffers of the LatticeXP2 devices are arranged into eight banks, allowing the implementation of a wide variety of I/O standards. PIO pairs on the left and right edges of the device can be configured as LVDS transmit/receive pairs. The PIC logic also includes pre-engineered support to aid in the implementation of high speed source synchronous standards such as 7:1 LVDS interfaces, found in many display applications, and memory interfaces including DDR and DDR2.

The LatticeXP2 registers in PFU and sysI/O can be configured to be SET or RESET. After power up and device is configured, the device enters into user mode with these registers SET/RESET according to the configuration setting, allowing device entering to a known state for predictable system function.

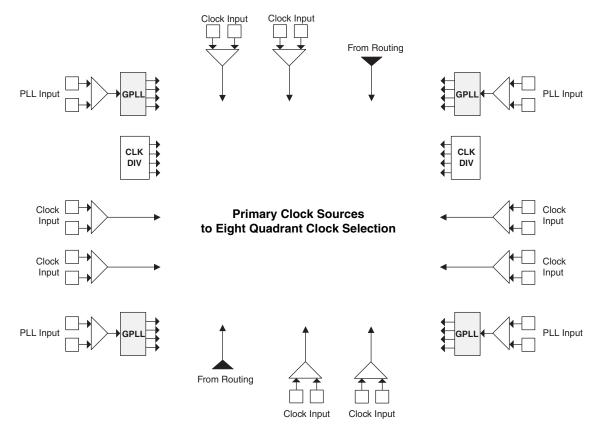

Other blocks provided include PLLs and configuration functions. The LatticeXP2 architecture provides up to four General Purpose PLLs (GPLL) per device. The GPLL blocks are located in the corners of the device.

The configuration block that supports features such as configuration bit-stream de-encryption, transparent updates and dual boot support is located between banks two and three. Every device in the LatticeXP2 family supports a sysCONFIG port, muxed with bank seven I/Os, which supports serial device configuration. A JTAG port is provided between banks two and three.

This family also provides an on-chip oscillator. LatticeXP2 devices use 1.2V as their core voltage.

<sup>© 2014</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

# Figure 2-6. Primary Clock Sources for XP2-17

Note: This diagram shows sources for the XP2-17 device. Smaller LatticeXP2 devices have two GPLLs.

# Primary Clock Routing

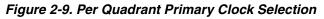

The clock routing structure in LatticeXP2 devices consists of a network of eight primary clock lines (CLK0 through CLK7) per quadrant. The primary clocks of each quadrant are generated from muxes located in the center of the device. All the clock sources are connected to these muxes. Figure 2-9 shows the clock routing for one quadrant. Each quadrant mux is identical. If desired, any clock can be routed globally.

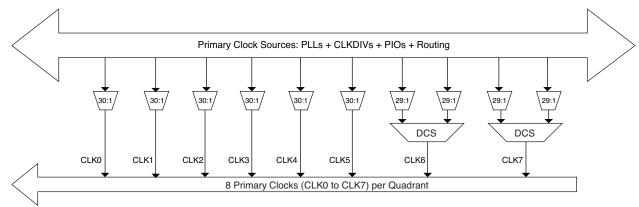

# **Dynamic Clock Select (DCS)**

The DCS is a smart multiplexer function available in the primary clock routing. It switches between two independent input clock sources without any glitches or runt pulses. This is achieved irrespective of when the select signal is toggled. There are two DCS blocks per quadrant; in total, eight DCS blocks per device. The inputs to the DCS block come from the center muxes. The output of the DCS is connected to primary clocks CLK6 and CLK7 (see Figure 2-9).

Figure 2-10 shows the timing waveforms of the default DCS operating mode. The DCS block can be programmed to other modes. For more information on the DCS, please see TN1126, <u>LatticeXP2 sysCLOCK PLL Design and</u> <u>Usage Guide</u>.

#### Figure 2-10. DCS Waveforms

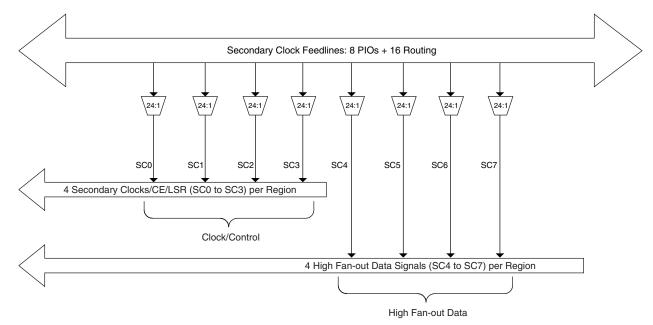

# Secondary Clock/Control Routing

Secondary clocks in the LatticeXP2 devices are region-based resources. The benefit of region-based resources is the relatively low injection delay and skew within the region, as compared to primary clocks. EBR rows, DSP rows and a special vertical routing channel bound the secondary clock regions. This special vertical routing channel aligns with either the left edge of the center DSP block in the DSP row or the center of the DSP row. Figure 2-11 shows this special vertical routing channel and the eight secondary clock regions for the LatticeXP2-40.

## Figure 2-12. Secondary Clock Selection

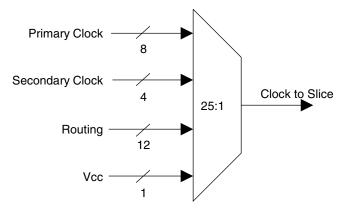

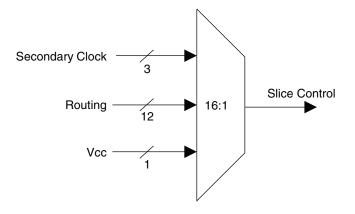

## Slice Clock Selection

Figure 2-13 shows the clock selections and Figure 2-14 shows the control selections for Slice0 through Slice2. All the primary clocks and the four secondary clocks are routed to this clock selection mux. Other signals, via routing, can be used as clock inputs to the slices. Slice controls are generated from the secondary clocks or other signals connected via routing.

If none of the signals are selected for both clock and control, then the default value of the mux output is 1. Slice 3 does not have any registers; therefore it does not have the clock or control muxes.

## Figure 2-13. Slice0 through Slice2 Clock Selection

#### Figure 2-14. Slice0 through Slice2 Control Selection

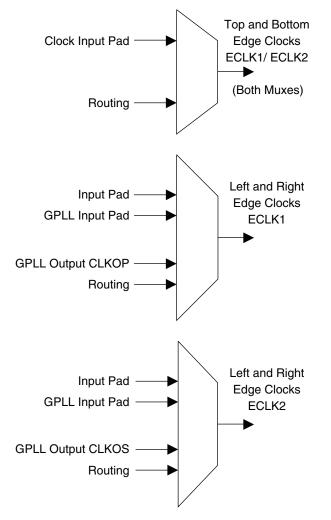

## **Edge Clock Routing**

LatticeXP2 devices have eight high-speed edge clocks that are intended for use with the PIOs in the implementation of high-speed interfaces. Each device has two edge clocks per edge. Figure 2-15 shows the selection muxes for these clocks.

#### Figure 2-15. Edge Clock Mux Connections

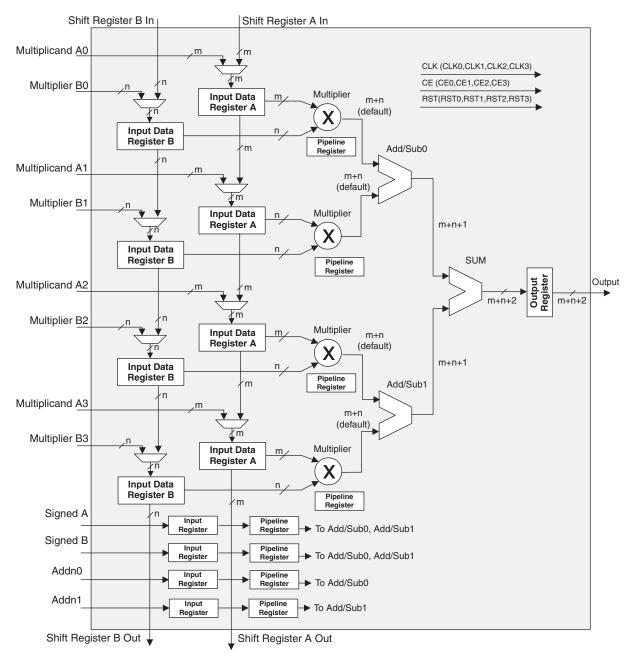

## MULTADDSUBSUM sysDSP Element

In this case, the operands A0 and B0 are multiplied and the result is added/subtracted with the result of the multiplier operation of operands A1 and B1. Additionally the operands A2 and B2 are multiplied and the result is added/ subtracted with the result of the multiplier operation of operands A3 and B3. The result of both addition/subtraction are added in a summation block. The user can enable the input, output and pipeline registers. Figure 2-23 shows the MULTADDSUBSUM sysDSP element.

#### Figure 2-23. MULTADDSUBSUM

## **Clock, Clock Enable and Reset Resources**

Global Clock, Clock Enable (CE) and Reset (RST) signals from routing are available to every DSP block. From four clock sources (CLK0, CLK1, CLK2, CLK3) one clock is selected for each input register, pipeline register and output

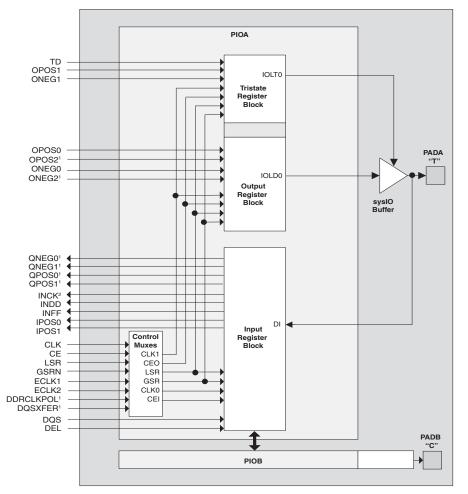

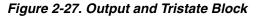

# Programmable I/O Cells (PIC)

Each PIC contains two PIOs connected to their respective sysIO buffers as shown in Figure 2-25. The PIO Block supplies the output data (DO) and the tri-state control signal (TO) to the sysIO buffer and receives input from the buffer. Table 2-11 provides the PIO signal list.

#### Figure 2-25. PIC Diagram

Signals are available on left/right/bottom edges only.

Selected blocks.

Two adjacent PIOs can be joined to provide a differential I/O pair (labeled as "T" and "C") as shown in Figure 2-25. The PAD Labels "T" and "C" distinguish the two PIOs. Approximately 50% of the PIO pairs on the left and right edges of the device can be configured as true LVDS outputs. All I/O pairs can operate as inputs.

shows the diagram using this gearbox function. For more information on this topic, see TN1138, <u>LatticeXP2 High</u> <u>Speed I/O Interface</u>.

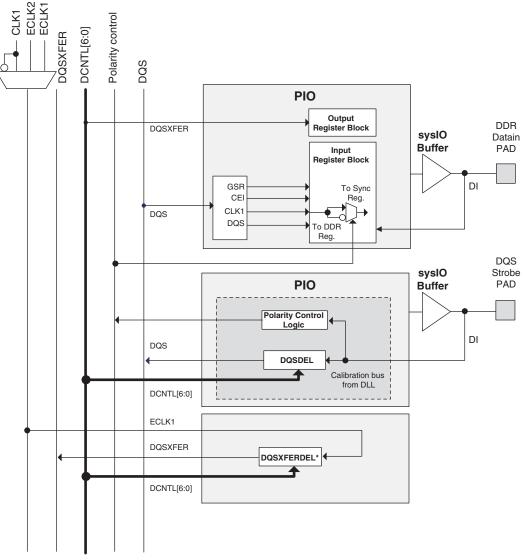

#### Figure 2-31. DQS Local Bus

\*DQSXFERDEL shifts ECLK1 by 90% and is not associated with a particular PIO.

# **Polarity Control Logic**

In a typical DDR memory interface design, the phase relationship between the incoming delayed DQS strobe and the internal system clock (during the READ cycle) is unknown. The LatticeXP2 family contains dedicated circuits to transfer data between these domains. To prevent set-up and hold violations, at the domain transfer between DQS (delayed) and the system clock, a clock polarity selector is used. This changes the edge on which the data is registered in the synchronizing registers in the input register block and requires evaluation at the start of each READ cycle for the correct clock polarity.

Prior to the READ operation in DDR memories, DQS is in tristate (pulled by termination). The DDR memory device drives DQS low at the start of the preamble state. A dedicated circuit detects this transition. This signal is used to control the polarity of the clock to the synchronizing registers.

- 1. Unlocked

- 2. Key Locked Presenting the key through the programming interface allows the device to be unlocked.

- 3. Permanently Locked The device is permanently locked.

To further complement the security of the device a One Time Programmable (OTP) mode is available. Once the device is set in this mode it is not possible to erase or re-program the Flash portion of the device.

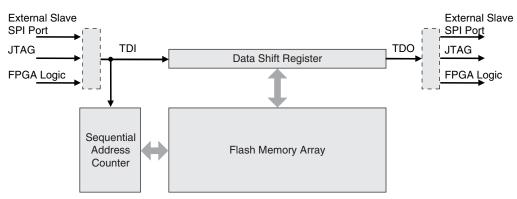

## Serial TAG Memory

LatticeXP2 devices offer 0.6 to 3.3kbits of Flash memory in the form of Serial TAG memory. The TAG memory is an area of the on-chip Flash that can be used for non-volatile storage including electronic ID codes, version codes, date stamps, asset IDs and calibration settings. A block diagram of the TAG memory is shown in Figure 2-34. The TAG memory is accessed in the same way as external SPI Flash and it can be read or programmed either through JTAG, an external Slave SPI Port, or directly from FPGA logic. To read the TAG memory, a start address is specified and the entire TAG memory contents are read sequentially in a first-in-first-out manner. The TAG memory is always accessible regardless of the device security settings. For more information, see TN1137, LatticeXP2 Memory Usage Guide and TN1141, LatticeXP2 sysCONFIG Usage Guide.

#### Figure 2-34. Serial TAG Memory Diagram

# Live Update Technology

Many applications require field updates of the FPGA. LatticeXP2 devices provide three features that enable this configuration to be done in a secure and failsafe manner while minimizing impact on system operation.

#### 1. **Decryption Support**

LatticeXP2 devices provide on-chip, non-volatile key storage to support decryption of a 128-bit AES encrypted bitstream, securing designs and deterring design piracy.

#### 2. TransFR (Transparent Field Reconfiguration)

TransFR I/O (TFR) is a unique Lattice technology that allows users to update their logic in the field without interrupting system operation using a single ispVM command. TransFR I/O allows I/O states to be frozen during device configuration. This allows the device to be field updated with a minimum of system disruption and downtime. For more information please see TN1087, <u>Minimizing System Interruption During Configuration</u>. Using TransFR Technology.

#### 3. Dual Boot Image Support

Dual boot images are supported for applications requiring reliable remote updates of configuration data for the system FPGA. After the system is running with a basic configuration, a new boot image can be downloaded remotely and stored in a separate location in the configuration storage device. Any time after the update the LatticeXP2 can be re-booted from this new configuration file. If there is a problem such as corrupt data during download or incorrect version number with this new boot image, the LatticeXP2 device can revert back to the

# LatticeXP2 Family Data Sheet DC and Switching Characteristics

#### September 2014

Data Sheet DS1009

# Absolute Maximum Ratings<sup>1, 2, 3</sup>

| Supply Voltage V <sub>CC</sub> 0.5 to 1.32V                                  |

|------------------------------------------------------------------------------|

| Supply Voltage $V_{CCAUX} \dots \dots \dots 0.5$ to $3.75V$                  |

| Supply Voltage $V_{CCJ} \dots \dots \dots \dots 0.5$ to $3.75V$              |

| Supply Voltage $V_{\mbox{\scriptsize CCPLL}}{}^4.\ldots\ldots$ -0.5 to 3.75V |

| Output Supply Voltage $V_{CCIO}$ $\ldots$ 0.5 to 3.75V                       |

| Input or I/O Tristate Voltage Applied $^5,\ldots\ldots$ -0.5 to 3.75V        |

| Storage Temperature (Ambient) $\ldots \ldots$ -65 to 150°C                   |

| Junction Temperature Under Bias (Tj) +125°C                                  |

1. Stress above those listed under the "Absolute Maximum Ratings" may cause permanent damage to the device. Functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

2. Compliance with the Lattice <u>Thermal Management</u> document is required.

3. All voltages referenced to GND.

4. V<sub>CCPLL</sub> only available on csBGA, PQFP and TQFP packages.

5. Overshoot and undershoot of -2V to ( $V_{IHMAX}$  + 2) volts is permitted for a duration of <20 ns.

# **Recommended Operating Conditions**

| Symbol                               | Parameter                                       | Min.  | Max.  | Units |

|--------------------------------------|-------------------------------------------------|-------|-------|-------|

| V <sub>CC</sub>                      | Core Supply Voltage                             | 1.14  | 1.26  | V     |

| V <sub>CCAUX</sub> <sup>4, 5</sup>   | Auxiliary Supply Voltage                        | 3.135 | 3.465 | V     |

| V <sub>CCPLL</sub> <sup>1</sup>      | PLL Supply Voltage                              | 3.135 | 3.465 | V     |

| V <sub>CCIO</sub> <sup>2, 3, 4</sup> | I/O Driver Supply Voltage                       | 1.14  | 3.465 | V     |

| V <sub>CCJ</sub> <sup>2</sup>        | Supply Voltage for IEEE 1149.1 Test Access Port | 1.14  | 3.465 | V     |

| t <sub>JCOM</sub>                    | Junction Temperature, Commercial Operation      | 0     | 85    | °C    |

| t <sub>JIND</sub>                    | Junction Temperature, Industrial Operation      | -40   | 100   | °C    |

1.  $V_{CCPLL}$  only available on csBGA, PQFP and TQFP packages.

If V<sub>CCIO</sub> or V<sub>CCJ</sub> is set to 1.2 V, they must be connected to the same power supply as V<sub>CC</sub>. If V<sub>CCIO</sub> or V<sub>CCJ</sub> is set to 3.3V, they must be connected to the same power supply as V<sub>CCAUX</sub>.

3. See recommended voltages by I/O standard in subsequent table.

4. To ensure proper I/O behavior,  $V_{CCIO}$  must be turned off at the same time or earlier than  $V_{CCAUX}$ .

5. In fpBGA and ftBGA packages, the PLLs are connected to, and powered from, the auxiliary power supply.

# **On-Chip Flash Memory Specifications**

| Symbol   | Parameter                                                        | Max.    | Units  |

|----------|------------------------------------------------------------------|---------|--------|

|          | Flash Programming Cycles per t <sub>RETENTION</sub> <sup>1</sup> | 10,000  | Cvcles |

| NPROGCYC | Flash Functional Programming Cycles                              | 100,000 | Oycles |

1. The minimum data retention, t<sub>RETENTION</sub>, is 20 years.

<sup>© 2014</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

# Initialization Supply Current<sup>1, 2, 3, 4, 5</sup>

#### **Over Recommended Operating Conditions**

| Symbol             | Parameter                                   | Device | Typical<br>(25°C, Max. Supply)⁵ | Units |

|--------------------|---------------------------------------------|--------|---------------------------------|-------|

|                    |                                             | XP2-5  | 20                              | mA    |

|                    |                                             | XP2-8  | 21                              | mA    |

| I <sub>CC</sub>    | Core Power Supply Current                   | XP2-17 | 44                              | mA    |

|                    |                                             | XP2-30 | 58                              | mA    |

|                    |                                             | XP2-40 | 62                              | mA    |

|                    |                                             | XP2-5  | 67                              | mA    |

|                    |                                             | XP2-8  | 74                              | mA    |

| I <sub>CCAUX</sub> | Auxiliary Power Supply Current <sup>7</sup> | XP2-17 | 112                             | mA    |

|                    |                                             | XP2-30 | 124                             | mA    |

|                    |                                             | XP2-40 | 130                             | mA    |

| I <sub>CCPLL</sub> | PLL Power Supply Current (per PLL)          |        | 1.8                             | mA    |

| I <sub>CCIO</sub>  | Bank Power Supply Current (per Bank)        |        | 6.4                             | mA    |

| I <sub>CCJ</sub>   | VCCJ Power Supply Current                   |        | 1.2                             | mA    |

1. For further information on supply current, please see TN1139, Power Estimation and Management for LatticeXP2 Devices.

2. Assumes all outputs are tristated, all inputs are configured as LVCMOS and held at the V<sub>CCIO</sub> or GND.

3. Frequency 0 MHz.

4. Does not include additional current from bypass or decoupling capacitor across the supply.

5. A specific configuration pattern is used that scales with the size of the device; consists of 75% PFU utilization, 50% EBR, and 25% I/O configuration.

6.  $T_J = 25^{\circ}C$ , power supplies at nominal voltage.

In fpBGA and ftBGA packages the PLLs are connected to and powered from the auxiliary power supply. For these packages, the actual

auxiliary supply current is the sum of I<sub>CCAUX</sub> and I<sub>CCPLL</sub>. For csBGA, PQFP and TQFP packages the PLLs are powered independent of the

auxiliary power supply.

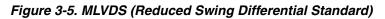

## MLVDS

The LatticeXP2 devices support the differential MLVDS standard. This standard is emulated using complementary LVCMOS outputs in conjunction with a parallel resistor across the driver outputs. The MLVDS input standard is supported by the LVDS differential input buffer. The scheme shown in Figure 3-5 is one possible solution for MLVDS standard implementation. Resistor values in Figure 3-5 are industry standard values for 1% resistors.

Table 3-5. MLVDS DC Conditions<sup>1</sup>

|                   |                                                      | Тур            |                |       |

|-------------------|------------------------------------------------------|----------------|----------------|-------|

| Parameter         | Description                                          | <b>Ζο=50</b> Ω | <b>Ζο=70</b> Ω | Units |

| V <sub>CCIO</sub> | Output Driver Supply (+/-5%)                         | 2.50           | 2.50           | V     |

| Z <sub>OUT</sub>  | Driver Impedance                                     | 10.00          | 10.00          | Ω     |

| R <sub>S</sub>    | Driver Series Resistor (+/-1%)                       | 35.00          | 35.00          | Ω     |

| R <sub>TL</sub>   | Driver Parallel Resistor (+/-1%)                     | 50.00          | 70.00          | Ω     |

| R <sub>TR</sub>   | Receiver Termination (+/-1%)                         | 50.00          | 70.00          | Ω     |

| V <sub>OH</sub>   | Output High Voltage (After R <sub>TL</sub> )         | 1.52           | 1.60           | V     |

| V <sub>OL</sub>   | Output Low Voltage (After R <sub>TL</sub> )          | 0.98           | 0.90           | V     |

| V <sub>OD</sub>   | Output Differential Voltage (After R <sub>TL</sub> ) | 0.54           | 0.70           | V     |

| V <sub>CM</sub>   | Output Common Mode Voltage                           | 1.25           | 1.25           | V     |

| I <sub>DC</sub>   | DC Output Current                                    | 21.74          | 20.00          | mA    |

1. For input buffer, see LVDS table.

For further information on LVPECL, RSDS, MLVDS, BLVDS and other differential interfaces please see details of additional technical information at the end of this data sheet.

# LatticeXP2 External Switching Characteristics

|                     |                                                                   |              | -                 | 7    | -    | 6    | -    | 5    |       |

|---------------------|-------------------------------------------------------------------|--------------|-------------------|------|------|------|------|------|-------|

| Parameter           | Description                                                       | Device       | Min.              | Max. | Min. | Max. | Min. | Max. | Units |

| General I/O Pi      | n Parameters (using Primary Clo                                   | ck without I | PLL) <sup>1</sup> | 1    | 1    |      |      | 1    |       |

|                     |                                                                   | XP2-5        | —                 | 3.80 |      | 4.20 | —    | 4.60 | ns    |

|                     |                                                                   | XP2-8        | —                 | 3.80 | —    | 4.20 | —    | 4.60 | ns    |

| t <sub>CO</sub>     | Clock to Output - PIO Output<br>Register                          | XP2-17       | —                 | 3.80 | —    | 4.20 | —    | 4.60 | ns    |

| Re                  |                                                                   | XP2-30       | —                 | 4.00 | —    | 4.40 | —    | 4.90 | ns    |

|                     |                                                                   | XP2-40       | —                 | 4.00 | —    | 4.40 | —    | 4.90 | ns    |

|                     |                                                                   | XP2-5        | 0.00              |      | 0.00 | —    | 0.00 |      | ns    |

|                     |                                                                   | XP2-8        | 0.00              | _    | 0.00 | —    | 0.00 | _    | ns    |

| t <sub>SU</sub>     | Clock to Data Setup - PIO Input<br>Register                       | XP2-17       | 0.00              | _    | 0.00 | —    | 0.00 | _    | ns    |

|                     |                                                                   | XP2-30       | 0.00              | _    | 0.00 | —    | 0.00 | _    | ns    |

|                     |                                                                   | XP2-40       | 0.00              |      | 0.00 | —    | 0.00 |      | ns    |

|                     |                                                                   | XP2-5        | 1.40              |      | 1.70 | —    | 1.90 |      | ns    |

|                     |                                                                   | XP2-8        | 1.40              | _    | 1.70 | —    | 1.90 | _    | ns    |

| t <sub>H</sub>      | Clock to Data Hold - PIO Input<br>Register                        | XP2-17       | 1.40              |      | 1.70 | —    | 1.90 | —    | ns    |

|                     |                                                                   | XP2-30       | 1.40              |      | 1.70 | —    | 1.90 |      | ns    |

|                     |                                                                   | XP2-40       | 1.40              |      | 1.70 | —    | 1.90 |      | ns    |

|                     |                                                                   | XP2-5        | 1.40              |      | 1.70 | —    | 1.90 |      | ns    |

|                     | Clock to Data Setup - PIO Input<br>Register with Data Input Delay | XP2-8        | 1.40              |      | 1.70 | —    | 1.90 |      | ns    |

| t <sub>SU_DEL</sub> |                                                                   | XP2-17       | 1.40              | _    | 1.70 | —    | 1.90 | _    | ns    |

|                     |                                                                   | XP2-30       | 1.40              |      | 1.70 | —    | 1.90 | —    | ns    |

|                     |                                                                   | XP2-40       | 1.40              |      | 1.70 | —    | 1.90 |      | ns    |

|                     |                                                                   | XP2-5        | 0.00              |      | 0.00 | —    | 0.00 |      | ns    |

|                     |                                                                   | XP2-8        | 0.00              |      | 0.00 | —    | 0.00 | —    | ns    |

| t <sub>H_DEL</sub>  | Clock to Data Hold - PIO Input<br>Register with Input Data Delay  | XP2-17       | 0.00              |      | 0.00 | —    | 0.00 | —    | ns    |

|                     |                                                                   | XP2-30       | 0.00              |      | 0.00 | —    | 0.00 |      | ns    |

|                     |                                                                   | XP2-40       | 0.00              |      | 0.00 | —    | 0.00 | —    | ns    |

| f <sub>MAX_IO</sub> | Clock Frequency of I/O and PFU Register                           | XP2          | _                 | 420  | —    | 357  | —    | 311  | MHz   |

| General I/O Pi      | n Parameters (using Edge Clock                                    | without PLI  | _) <sup>1</sup>   |      |      |      |      |      |       |

|                     |                                                                   | XP2-5        | —                 | 3.20 | _    | 3.60 | —    | 3.90 | ns    |

|                     |                                                                   | XP2-8        | _                 | 3.20 |      | 3.60 | —    | 3.90 | ns    |

| t <sub>COE</sub>    | Clock to Output - PIO Output<br>Register                          | XP2-17       | —                 | 3.20 | _    | 3.60 | —    | 3.90 | ns    |

|                     |                                                                   | XP2-30       | _                 | 3.20 |      | 3.60 |      | 3.90 | ns    |

|                     |                                                                   | XP2-40       | _                 | 3.20 |      | 3.60 | —    | 3.90 | ns    |

|                     |                                                                   | XP2-5        | 0.00              |      | 0.00 | —    | 0.00 |      | ns    |

|                     |                                                                   | XP2-8        | 0.00              |      | 0.00 | —    | 0.00 | —    | ns    |

| t <sub>SUE</sub>    | Clock to Data Setup - PIO Input<br>Register                       | XP2-17       | 0.00              | —    | 0.00 | —    | 0.00 | —    | ns    |

|                     |                                                                   | XP2-30       | 0.00              | —    | 0.00 | —    | 0.00 | —    | ns    |

|                     |                                                                   | XP2-40       | 0.00              | —    | 0.00 | —    | 0.00 | —    | ns    |

## **Over Recommended Operating Conditions**

# On-Chip Oscillator and Configuration Master Clock Characteristics

| Parameter              | Min.                | Max.                | Units |

|------------------------|---------------------|---------------------|-------|

| Master Clock Frequency | Selected value -30% | Selected value +30% | MHz   |

| Duty Cycle             | 40                  | 60                  | %     |

#### **Over Recommended Operating Conditions**

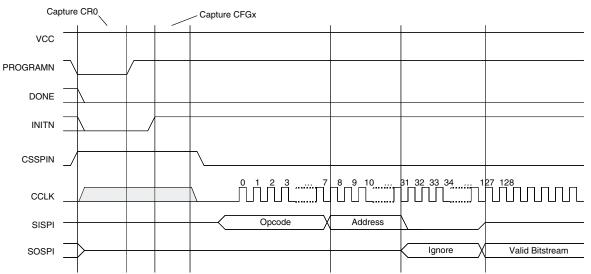

## Figure 3-9. Master SPI Configuration Waveforms

# Pin Information Summary

|                                          |                |              | XP          | 2-5         |              |              | XP          | 2-8         |              |             | XP2-17       | ,            |              | XP2-30       |         | XP           | 2-40    |

|------------------------------------------|----------------|--------------|-------------|-------------|--------------|--------------|-------------|-------------|--------------|-------------|--------------|--------------|--------------|--------------|---------|--------------|---------|

| Pin Ty                                   | pe             | 132<br>csBGA | 144<br>TQFP | 208<br>PQFP | 256<br>ftBGA | 132<br>csBGA | 144<br>TQFP | 208<br>PQFP | 256<br>ftBGA | 208<br>PQFP | 256<br>ftBGA | 484<br>fpBGA | 256<br>ftBGA | 484<br>fpBGA | 672     | 484<br>fpBGA | 672     |

| Single Ended Us                          |                | 86           | 100         | 146         | 172          | 86           | 100         | 146         | 201          | 146         | 201          | 358          | 201          | 363          | 472     | 363          | 540     |

| Differential Pair                        | Normal         | 35           | 39          | 57          | 66           | 35           | 39          | 57          | 77           | 57          | 77           | 135          | 77           | 137          | 180     | 137          | 204     |

| User I/O                                 | Highspeed      | 8            | 11          | 16          | 20           | 8            | 11          | 16          | 23           | 16          | 23           | 44           | 23           | 44           | 56      | 44           | 66      |

|                                          | TAP            | 5            | 5           | 5           | 5            | 5            | 5           | 5           | 5            | 5           | 5            | 5            | 5            | 5            | 5       | 5            | 5       |

| Configuration                            | Muxed          | 9            | 9           | 9           | 9            | 9            | 9           | 9           | 9            | 9           | 9            | 9            | 9            | 9            | 9       | 9            | 9       |

|                                          | Dedicated      | 1            | 1           | 1           | 1            | 1            | 1           | 1           | 1            | 1           | 1            | 1            | 1            | 1            | 1       | 1            | 1       |

| Non Configura-                           | Muxed          | 5            | 5           | 7           | 7            | 7            | 7           | 9           | 9            | 11          | 11           | 21           | 7            | 11           | 13      | 11           | 13      |

| tion                                     | Dedicated      | 1            | 1           | 1           | 1            | 1            | 1           | 1           | 1            | 1           | 1            | 1            | 1            | 1            | 1       | 1            | 1       |

| Vcc                                      |                | 6            | 4           | 9           | 6            | 6            | 4           | 9           | 6            | 9           | 6            | 16           | 6            | 16           | 20      | 16           | 20      |

| Vccaux                                   |                | 4            | 4           | 4           | 4            | 4            | 4           | 4           | 4            | 4           | 4            | 8            | 4            | 8            | 8       | 8            | 8       |

| VCCPLL                                   |                | 2            | 2           | 2           | -            | 2            | 2           | 2           | -            | 4           | -            | -            | -            | -            | -       | -            | -       |

|                                          | Bank0          | 2            | 2           | 2           | 2            | 2            | 2           | 2           | 2            | 2           | 2            | 4            | 2            | 4            | 4       | 4            | 4       |

|                                          | Bank1          | 1            | 1           | 2           | 2            | 1            | 1           | 2           | 2            | 2           | 2            | 4            | 2            | 4            | 4       | 4            | 4       |

|                                          | Bank2          | 2            | 2           | 2           | 2            | 2            | 2           | 2           | 2            | 2           | 2            | 4            | 2            | 4            | 4       | 4            | 4       |

| VCCIO                                    | Bank3          | 1            | 1           | 2           | 2            | 1            | 1           | 2           | 2            | 2           | 2            | 4            | 2            | 4            | 4       | 4            | 4       |

|                                          | Bank4          | 1            | 1           | 2           | 2            | 1            | 1           | 2           | 2            | 2           | 2            | 4            | 2            | 4            | 4       | 4            | 4       |

|                                          | Bank5          | 2            | 2           | 2           | 2            | 2            | 2           | 2           | 2            | 2           | 2            | 4            | 2            | 4            | 4       | 4            | 4       |

|                                          | Bank6          | 1            | 1           | 2           | 2            | 1            | 1           | 2           | 2            | 2           | 2            | 4            | 2            | 4            | 4       | 4            | 4       |

|                                          | Bank7          | 2            | 2           | 2           | 2            | 2            | 2           | 2           | 2            | 2           | 2            | 4            | 2            | 4            | 4       | 4            | 4       |

| GND, GND0-GNI                            | 77             | 15           | 15          | 20          | 20           | 15           | 15          | 22          | 20           | 22          | 20           | 56           | 20           | 56           | 64      | 56           | 64      |

| NC                                       |                | -            | -           | 4           | 31           | -            | -           | 2           | 2            | -           | 2            | 7            | 2            | 2            | 69      | 2            | 1       |

|                                          | Bank0          | 18/9         | 20/10       | 20/10       | 26/13        | 18/9         | 20/10       | 20/10       | 28/14        | 20/10       | 28/14        | 52/26        | 28/14        | 52/26        | 70/35   | 52/26        | 70/35   |

|                                          | Bank1          | 4/2          | 6/3         | 18/9        | 18/9         | 4/2          | 6/3         | 18/9        | 22/11        | 18/9        | 22/11        | 36/18        | 22/11        | 36/18        | 54/27   | 36/18        | 70/35   |

| Qia ala Ea da di                         | Bank2          | 16/8         | 18/9        | 18/9        | 22/11        | 16/8         | 18/9        | 18/9        | 26/13        | 18/9        | 26/13        | 46/23        | 26/13        | 46/23        | 56/28   | 46/23        | 64/32   |

| Single Ended/<br>Differential I/O        | Bank3          | 4/2          | 4/2         | 16/8        | 20/10        | 4/2          | 4/2         | 16/8        | 24/12        | 16/8        | 24/12        | 44/22        | 24/12        | 46/23        | 56/28   | 46/23        | 66/33   |

| per Bank                                 | Bank4          | 8/4          | 8/4         | 18/9        | 18/9         | 8/4          | 8/4         | 18/9        | 26/13        | 18/9        | 26/13        | 36/18        | 26/13        | 38/19        | 54/27   | 38/19        | 70/35   |

|                                          | Bank5          | 14/7         | 18/9        | 20/10       | 24/12        | 14/7         | 18/9        | 20/10       | 24/12        | 20/10       | 24/12        | 52/26        | 24/12        | 53/26        | 70/35   | 53/26        | 70/35   |

|                                          | Bank6          | 6/3          | 8/4         | 18/9        | 22/11        | 6/3          | 8/4         | 18/9        | 27/13        | 18/9        | 27/13        | 46/23        | 27/13        | 46/23        | 56/28   | 46/23        | 66/33   |

|                                          | Bank7          | 16/8         | 18/9        | 18/9        | 22/11        | 16/8         | 18/9        | 18/9        | 24/12        | 18/9        | 24/12        | 46/23        | 24/12        | 46/23        | 56/28   | 46/23        | 64/32   |

|                                          | Bank0          | 0            | 0           | 0           | 0            | 0            | 0           | 0           | 0            | 0           | 0            | 0            | 0            | 0            | 0       | 0            | 0       |

|                                          | Bank1<br>Bank2 | 0            | 0<br>4      | 0<br>4      | 0<br>5       | 0            | 4           | 0           | 0            | 0<br>4      | 0            | 0<br>11      | 0            | 0            | 0<br>14 | 0<br>11      | 0<br>16 |

| True LVDS Pairs                          | Bank3          | 3<br>1       | 4           | 4           | 5            | 3<br>1       | 4           | 4           | 6            | 4           | 6            | 11           | 6            | 11           | 14      | 11           | 17      |

| Bonding Out per                          | Bank4          | 0            | 0           | 4           | 0            | 0            | 0           | 4           | 0            | 4           | 0            | 0            | 0            | 0            | 0       | 0            | 0       |

| Bank                                     | Bank5          | 0            | 0           | 0           | 0            | 0            | 0           | 0           | 0            | 0           | 0            | 0            | 0            | 0            | 0       | 0            | 0       |

|                                          | Bank6          | 1            | 2           | 4           | 5            | 1            | 2           | 4           | 6            | 4           | 6            | 11           | 6            | 11           | 14      | 11           | 17      |

|                                          | Bank7          | 3            | 4           | 4           | 5            | 3            | 4           | 4           | 5            | 4           | 5            | 11           | 5            | 11           | 14      | 11           | 16      |

|                                          | Bank0          | 1            | 1           | 1           | 1            | 1            | 1           | 1           | 1            | 1           | 1            | 3            | 1            | 2            | 4       | 2            | 4       |

|                                          | Bank1          | 0            | 0           | 1           | 1            | 0            | 0           | 1           | 1            | 1           | 1            | 2            | 1            | 2            | 3       | 2            | 4       |

|                                          | Bank2          | 1            | 1           | 1           | 1            | 1            | 1           | 1           | 1            | 1           | 1            | 2            | 1            | 3            | 3       | 3            | 4       |

| DDR Banks                                | Bank3          | 0            | 0           | 1           | 1            | 0            | 0           | 1           | 1            | 1           | 1            | 2            | 1            | 3            | 3       | 3            | 4       |

| Bonding Out per<br>I/O Bank <sup>1</sup> | Bank4          | 0            | 0           | 1           | 1            | 0            | 0           | 1           | 1            | 1           | 1            | 2            | 1            | 2            | 3       | 2            | 4       |

| "O Durik                                 | Bank5          | 1            | 1           | 1           | 1            | 1            | 1           | 1           | 1            | 1           | 1            | 3            | 1            | 2            | 4       | 2            | 4       |

|                                          | Bank6          | 0            | 0           | 1           | 1            | 0            | 0           | 1           | 1            | 1           | 1            | 2            | 1            | 3            | 3       | 3            | 4       |

|                                          | Bank7          | 1            | 1           | 1           | 1            | 1            | 1           | 1           | 1            | 1           | 1            | 2            | 1            | 3            | 3       | 3            | 4       |

|                                          |                |              |             |             |              |              |             |             |              |             | · ·          | I            |              | -            | -       | -            | · ·     |

# Lead-Free Packaging

# Commercial

| Part Number       | Voltage | Grade | Package         | Pins | Temp. | LUTs (k) |

|-------------------|---------|-------|-----------------|------|-------|----------|

| LFXP2-5E-5MN132C  | 1.2V    | -5    | Lead-Free csBGA | 132  | COM   | 5        |

| LFXP2-5E-6MN132C  | 1.2V    | -6    | Lead-Free csBGA | 132  | COM   | 5        |

| LFXP2-5E-7MN132C  | 1.2V    | -7    | Lead-Free csBGA | 132  | COM   | 5        |

| LFXP2-5E-5TN144C  | 1.2V    | -5    | Lead-Free TQFP  | 144  | COM   | 5        |

| LFXP2-5E-6TN144C  | 1.2V    | -6    | Lead-Free TQFP  | 144  | COM   | 5        |

| LFXP2-5E-7TN144C  | 1.2V    | -7    | Lead-Free TQFP  | 144  | COM   | 5        |

| LFXP2-5E-5QN208C  | 1.2V    | -5    | Lead-Free PQFP  | 208  | COM   | 5        |

| LFXP2-5E-6QN208C  | 1.2V    | -6    | Lead-Free PQFP  | 208  | COM   | 5        |

| LFXP2-5E-7QN208C  | 1.2V    | -7    | Lead-Free PQFP  | 208  | COM   | 5        |

| LFXP2-5E-5FTN256C | 1.2V    | -5    | Lead-Free ftBGA | 256  | COM   | 5        |

| LFXP2-5E-6FTN256C | 1.2V    | -6    | Lead-Free ftBGA | 256  | COM   | 5        |

| LFXP2-5E-7FTN256C | 1.2V    | -7    | Lead-Free ftBGA | 256  | COM   | 5        |

| Part Number       | Voltage | Grade | Package         | Pins | Temp. | LUTs (k) |

|-------------------|---------|-------|-----------------|------|-------|----------|

| LFXP2-8E-5MN132C  | 1.2V    | -5    | Lead-Free csBGA | 132  | COM   | 8        |

| LFXP2-8E-6MN132C  | 1.2V    | -6    | Lead-Free csBGA | 132  | COM   | 8        |

| LFXP2-8E-7MN132C  | 1.2V    | -7    | Lead-Free csBGA | 132  | COM   | 8        |

| LFXP2-8E-5TN144C  | 1.2V    | -5    | Lead-Free TQFP  | 144  | COM   | 8        |

| LFXP2-8E-6TN144C  | 1.2V    | -6    | Lead-Free TQFP  | 144  | COM   | 8        |

| LFXP2-8E-7TN144C  | 1.2V    | -7    | Lead-Free TQFP  | 144  | COM   | 8        |

| LFXP2-8E-5QN208C  | 1.2V    | -5    | Lead-Free PQFP  | 208  | COM   | 8        |

| LFXP2-8E-6QN208C  | 1.2V    | -6    | Lead-Free PQFP  | 208  | COM   | 8        |

| LFXP2-8E-7QN208C  | 1.2V    | -7    | Lead-Free PQFP  | 208  | COM   | 8        |

| LFXP2-8E-5FTN256C | 1.2V    | -5    | Lead-Free ftBGA | 256  | COM   | 8        |

| LFXP2-8E-6FTN256C | 1.2V    | -6    | Lead-Free ftBGA | 256  | COM   | 8        |

| LFXP2-8E-7FTN256C | 1.2V    | -7    | Lead-Free ftBGA | 256  | COM   | 8        |

| Part Number        | Voltage | Grade | Package         | Pins | Temp. | LUTs (k) |

|--------------------|---------|-------|-----------------|------|-------|----------|

| LFXP2-17E-5QN208C  | 1.2V    | -5    | Lead-Free PQFP  | 208  | COM   | 17       |

| LFXP2-17E-6QN208C  | 1.2V    | -6    | Lead-Free PQFP  | 208  | COM   | 17       |

| LFXP2-17E-7QN208C  | 1.2V    | -7    | Lead-Free PQFP  | 208  | COM   | 17       |

| LFXP2-17E-5FTN256C | 1.2V    | -5    | Lead-Free ftBGA | 256  | COM   | 17       |

| LFXP2-17E-6FTN256C | 1.2V    | -6    | Lead-Free ftBGA | 256  | COM   | 17       |

| LFXP2-17E-7FTN256C | 1.2V    | -7    | Lead-Free ftBGA | 256  | COM   | 17       |

| LFXP2-17E-5FN484C  | 1.2V    | -5    | Lead-Free fpBGA | 484  | COM   | 17       |

| LFXP2-17E-6FN484C  | 1.2V    | -6    | Lead-Free fpBGA | 484  | COM   | 17       |

| LFXP2-17E-7FN484C  | 1.2V    | -7    | Lead-Free fpBGA | 484  | COM   | 17       |

| Part Number        | Voltage | Grade | Package         | Pins | Temp. | LUTs (k) |

|--------------------|---------|-------|-----------------|------|-------|----------|

| LFXP2-30E-5FTN256C | 1.2V    | -5    | Lead-Free ftBGA | 256  | COM   | 30       |

| LFXP2-30E-6FTN256C | 1.2V    | -6    | Lead-Free ftBGA | 256  | COM   | 30       |

| LFXP2-30E-7FTN256C | 1.2V    | -7    | Lead-Free ftBGA | 256  | COM   | 30       |

| LFXP2-30E-5FN484C  | 1.2V    | -5    | Lead-Free fpBGA | 484  | COM   | 30       |

| LFXP2-30E-6FN484C  | 1.2V    | -6    | Lead-Free fpBGA | 484  | COM   | 30       |

| LFXP2-30E-7FN484C  | 1.2V    | -7    | Lead-Free fpBGA | 484  | COM   | 30       |

| LFXP2-30E-5FN672C  | 1.2V    | -5    | Lead-Free fpBGA | 672  | COM   | 30       |

| LFXP2-30E-6FN672C  | 1.2V    | -6    | Lead-Free fpBGA | 672  | COM   | 30       |

| LFXP2-30E-7FN672C  | 1.2V    | -7    | Lead-Free fpBGA | 672  | COM   | 30       |

| Part Number       | Voltage | Grade | Package         | Pins | Temp. | LUTs (k) |

|-------------------|---------|-------|-----------------|------|-------|----------|

| LFXP2-40E-5FN484C | 1.2V    | -5    | Lead-Free fpBGA | 484  | COM   | 40       |

| LFXP2-40E-6FN484C | 1.2V    | -6    | Lead-Free fpBGA | 484  | COM   | 40       |

| LFXP2-40E-7FN484C | 1.2V    | -7    | Lead-Free fpBGA | 484  | COM   | 40       |

| LFXP2-40E-5FN672C | 1.2V    | -5    | Lead-Free fpBGA | 672  | COM   | 40       |

| LFXP2-40E-6FN672C | 1.2V    | -6    | Lead-Free fpBGA | 672  | COM   | 40       |

| LFXP2-40E-7FN672C | 1.2V    | -7    | Lead-Free fpBGA | 672  | COM   | 40       |

## Industrial

| Part Number       | Voltage | Grade | Package         | Pins | Temp. | LUTs (k) |

|-------------------|---------|-------|-----------------|------|-------|----------|

| LFXP2-5E-5MN132I  | 1.2V    | -5    | Lead-Free csBGA | 132  | IND   | 5        |

| LFXP2-5E-6MN132I  | 1.2V    | -6    | Lead-Free csBGA | 132  | IND   | 5        |

| LFXP2-5E-5TN144I  | 1.2V    | -5    | Lead-Free TQFP  | 144  | IND   | 5        |

| LFXP2-5E-6TN144I  | 1.2V    | -6    | Lead-Free TQFP  | 144  | IND   | 5        |

| LFXP2-5E-5QN208I  | 1.2V    | -5    | Lead-Free PQFP  | 208  | IND   | 5        |

| LFXP2-5E-6QN208I  | 1.2V    | -6    | Lead-Free PQFP  | 208  | IND   | 5        |

| LFXP2-5E-5FTN256I | 1.2V    | -5    | Lead-Free ftBGA | 256  | IND   | 5        |

| LFXP2-5E-6FTN256I | 1.2V    | -6    | Lead-Free ftBGA | 256  | IND   | 5        |

| Part Number       | Voltage | Grade | Package         | Pins | Temp. | LUTs (k) |

|-------------------|---------|-------|-----------------|------|-------|----------|

| LFXP2-8E-5MN132I  | 1.2V    | -5    | Lead-Free csBGA | 132  | IND   | 8        |

| LFXP2-8E-6MN132I  | 1.2V    | -6    | Lead-Free csBGA | 132  | IND   | 8        |

| LFXP2-8E-5TN144I  | 1.2V    | -5    | Lead-Free TQFP  | 144  | IND   | 8        |

| LFXP2-8E-6TN144I  | 1.2V    | -6    | Lead-Free TQFP  | 144  | IND   | 8        |

| LFXP2-8E-5QN208I  | 1.2V    | -5    | Lead-Free PQFP  | 208  | IND   | 8        |

| LFXP2-8E-6QN208I  | 1.2V    | -6    | Lead-Free PQFP  | 208  | IND   | 8        |

| LFXP2-8E-5FTN256I | 1.2V    | -5    | Lead-Free ftBGA | 256  | IND   | 8        |

| LFXP2-8E-6FTN256I | 1.2V    | -6    | Lead-Free ftBGA | 256  | IND   | 8        |

# **Conventional Packaging**

| Part Number      | Voltage | Grade | Package | Pins | Temp. | LUTs (k) |

|------------------|---------|-------|---------|------|-------|----------|

| LFXP2-5E-5M132C  | 1.2V    | -5    | csBGA   | 132  | COM   | 5        |

| LFXP2-5E-6M132C  | 1.2V    | -6    | csBGA   | 132  | COM   | 5        |

| LFXP2-5E-7M132C  | 1.2V    | -7    | csBGA   | 132  | COM   | 5        |

| LFXP2-5E-5FT256C | 1.2V    | -5    | ftBGA   | 256  | COM   | 5        |

| LFXP2-5E-6FT256C | 1.2V    | -6    | ftBGA   | 256  | COM   | 5        |

| LFXP2-5E-7FT256C | 1.2V    | -7    | ftBGA   | 256  | COM   | 5        |

Commercial

| Part Number      | Voltage | Grade | Package | Pins | Temp. | LUTs (k) |

|------------------|---------|-------|---------|------|-------|----------|

| LFXP2-8E-5M132C  | 1.2V    | -5    | csBGA   | 132  | COM   | 8        |

| LFXP2-8E-6M132C  | 1.2V    | -6    | csBGA   | 132  | COM   | 8        |

| LFXP2-8E-7M132C  | 1.2V    | -7    | csBGA   | 132  | COM   | 8        |

| LFXP2-8E-5FT256C | 1.2V    | -5    | ftBGA   | 256  | COM   | 8        |

| LFXP2-8E-6FT256C | 1.2V    | -6    | ftBGA   | 256  | COM   | 8        |

| LFXP2-8E-7FT256C | 1.2V    | -7    | ftBGA   | 256  | COM   | 8        |

| Part Number       | Voltage | Grade | Package | Pins | Temp. | LUTs (k) |

|-------------------|---------|-------|---------|------|-------|----------|

| LFXP2-17E-5FT256C | 1.2V    | -5    | ftBGA   | 256  | COM   | 17       |

| LFXP2-17E-6FT256C | 1.2V    | -6    | ftBGA   | 256  | COM   | 17       |

| LFXP2-17E-7FT256C | 1.2V    | -7    | ftBGA   | 256  | COM   | 17       |

| LFXP2-17E-5F484C  | 1.2V    | -5    | fpBGA   | 484  | COM   | 17       |

| LFXP2-17E-6F484C  | 1.2V    | -6    | fpBGA   | 484  | COM   | 17       |

| LFXP2-17E-7F484C  | 1.2V    | -7    | fpBGA   | 484  | COM   | 17       |

| Part Number       | Voltage | Grade | Package | Pins | Temp. | LUTs (k) |

|-------------------|---------|-------|---------|------|-------|----------|

| LFXP2-30E-5FT256C | 1.2V    | -5    | ftBGA   | 256  | COM   | 30       |

| LFXP2-30E-6FT256C | 1.2V    | -6    | ftBGA   | 256  | COM   | 30       |

| LFXP2-30E-7FT256C | 1.2V    | -7    | ftBGA   | 256  | COM   | 30       |

| LFXP2-30E-5F484C  | 1.2V    | -5    | fpBGA   | 484  | COM   | 30       |

| LFXP2-30E-6F484C  | 1.2V    | -6    | fpBGA   | 484  | COM   | 30       |

| LFXP2-30E-7F484C  | 1.2V    | -7    | fpBGA   | 484  | COM   | 30       |

| LFXP2-30E-5F672C  | 1.2V    | -5    | fpBGA   | 672  | COM   | 30       |

| LFXP2-30E-6F672C  | 1.2V    | -6    | fpBGA   | 672  | COM   | 30       |

| LFXP2-30E-7F672C  | 1.2V    | -7    | fpBGA   | 672  | COM   | 30       |

| Part Number      | Voltage | Grade | Package | Pins | Temp. | LUTs (k) |

|------------------|---------|-------|---------|------|-------|----------|

| LFXP2-40E-5F484I | 1.2V    | -5    | fpBGA   | 484  | IND   | 40       |

| LFXP2-40E-6F484I | 1.2V    | -6    | fpBGA   | 484  | IND   | 40       |

| LFXP2-40E-5F672I | 1.2V    | -5    | fpBGA   | 672  | IND   | 40       |

| LFXP2-40E-6F672I | 1.2V    | -6    | fpBGA   | 672  | IND   | 40       |