# E.J. Lattice Semiconductor Corporation - <u>LFXP2-30E-7FN484C Datasheet</u>

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                       |

|--------------------------------|------------------------------------------------------------------------------|

| Number of LABs/CLBs            | 3625                                                                         |

| Number of Logic Elements/Cells | 29000                                                                        |

| Total RAM Bits                 | 396288                                                                       |

| Number of I/O                  | 363                                                                          |

| Number of Gates                |                                                                              |

| Voltage - Supply               | 1.14V ~ 1.26V                                                                |

| Mounting Type                  | Surface Mount                                                                |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                              |

| Package / Case                 | 484-BBGA                                                                     |

| Supplier Device Package        | 484-FPBGA (23x23)                                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfxp2-30e-7fn484c |

|                                |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

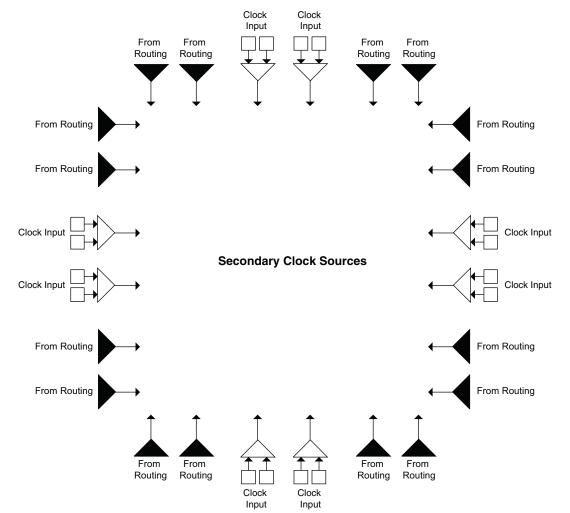

### Secondary Clock/Control Sources

LatticeXP2 devices derive secondary clocks (SC0 through SC7) from eight dedicated clock input pads and the rest from routing. Figure 2-7 shows the secondary clock sources.

#### Figure 2-7. Secondary Clock Sources

## Programmable I/O Cells (PIC)

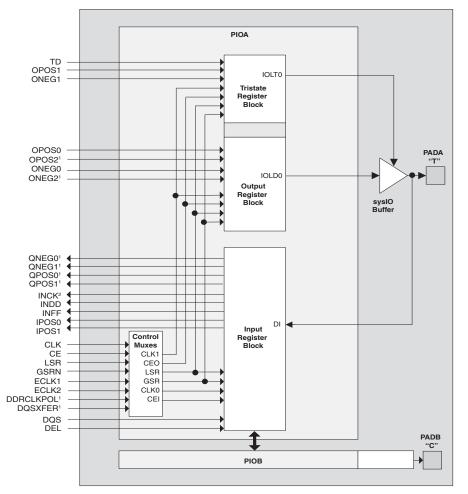

Each PIC contains two PIOs connected to their respective sysIO buffers as shown in Figure 2-25. The PIO Block supplies the output data (DO) and the tri-state control signal (TO) to the sysIO buffer and receives input from the buffer. Table 2-11 provides the PIO signal list.

### Figure 2-25. PIC Diagram

Signals are available on left/right/bottom edges only.

Selected blocks.

Two adjacent PIOs can be joined to provide a differential I/O pair (labeled as "T" and "C") as shown in Figure 2-25. The PAD Labels "T" and "C" distinguish the two PIOs. Approximately 50% of the PIO pairs on the left and right edges of the device can be configured as true LVDS outputs. All I/O pairs can operate as inputs.

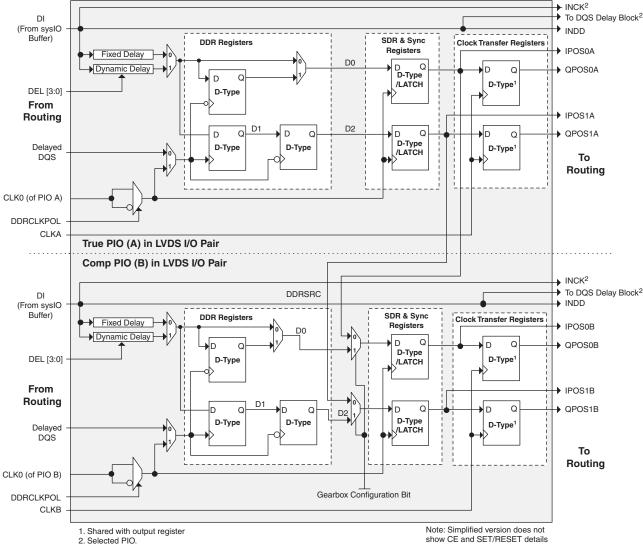

The signal DDRCLKPOL controls the polarity of the clock used in the synchronization registers. It ensures adequate timing when data is transferred from the DQS to system clock domain. For further discussion on this topic, see the DDR Memory section of this data sheet.

## **Output Register Block**

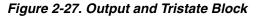

The output register block provides the ability to register signals from the core of the device before they are passed to the sysIO buffers. The blocks on the PIOs on the left, right and bottom contain registers for SDR operation that are combined with an additional latch for DDR operation. Figure 2-27 shows the diagram of the Output Register Block for PIOs.

In SDR mode, ONEG0 feeds one of the flip-flops that then feeds the output. The flip-flop can be configured as a Dtype or latch. In DDR mode, ONEG0 and OPOS0 are fed into registers on the positive edge of the clock. At the next clock cycle the registered OPOS0 is latched. A multiplexer running off the same clock cycle selects the correct register to feed the output (D0).

By combining output blocks of the complementary PIOs and sharing some registers from input blocks, a gearbox function can be implemented, to take four data streams ONEG0A, ONEG1A, ONEG1B and ONEG1B. Figure 2-27

shows the diagram using this gearbox function. For more information on this topic, see TN1138, <u>LatticeXP2 High</u> <u>Speed I/O Interface</u>.

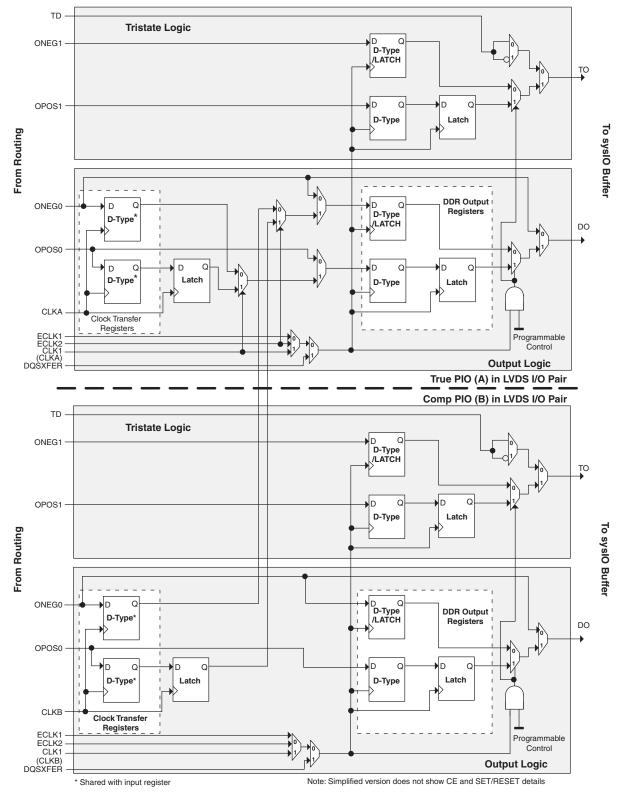

#### Figure 2-31. DQS Local Bus

\*DQSXFERDEL shifts ECLK1 by 90% and is not associated with a particular PIO.

## **Polarity Control Logic**

In a typical DDR memory interface design, the phase relationship between the incoming delayed DQS strobe and the internal system clock (during the READ cycle) is unknown. The LatticeXP2 family contains dedicated circuits to transfer data between these domains. To prevent set-up and hold violations, at the domain transfer between DQS (delayed) and the system clock, a clock polarity selector is used. This changes the edge on which the data is registered in the synchronizing registers in the input register block and requires evaluation at the start of each READ cycle for the correct clock polarity.

Prior to the READ operation in DDR memories, DQS is in tristate (pulled by termination). The DDR memory device drives DQS low at the start of the preamble state. A dedicated circuit detects this transition. This signal is used to control the polarity of the clock to the synchronizing registers.

# Initialization Supply Current<sup>1, 2, 3, 4, 5</sup>

### **Over Recommended Operating Conditions**

| Symbol             | Parameter                                   | Device | Typical<br>(25°C, Max. Supply) <sup>6</sup> | Units |

|--------------------|---------------------------------------------|--------|---------------------------------------------|-------|

|                    |                                             | XP2-5  | 20                                          | mA    |

|                    |                                             | XP2-8  | 21                                          | mA    |

| I <sub>CC</sub>    | Core Power Supply Current                   | XP2-17 | 44                                          | mA    |

|                    |                                             | XP2-30 | 58                                          | mA    |

|                    |                                             | XP2-40 | 62                                          | mA    |

|                    |                                             | XP2-5  | 67                                          | mA    |

|                    |                                             | XP2-8  | 74                                          | mA    |

| I <sub>CCAUX</sub> | Auxiliary Power Supply Current <sup>7</sup> | XP2-17 | 112                                         | mA    |

|                    |                                             | XP2-30 | 124                                         | mA    |

|                    |                                             | XP2-40 | 130                                         | mA    |

| I <sub>CCPLL</sub> | PLL Power Supply Current (per PLL)          |        | 1.8                                         | mA    |

| I <sub>CCIO</sub>  | Bank Power Supply Current (per Bank)        |        | 6.4                                         | mA    |

| I <sub>CCJ</sub>   | VCCJ Power Supply Current                   |        | 1.2                                         | mA    |

1. For further information on supply current, please see TN1139, Power Estimation and Management for LatticeXP2 Devices.

2. Assumes all outputs are tristated, all inputs are configured as LVCMOS and held at the V<sub>CCIO</sub> or GND.

3. Frequency 0 MHz.

4. Does not include additional current from bypass or decoupling capacitor across the supply.

5. A specific configuration pattern is used that scales with the size of the device; consists of 75% PFU utilization, 50% EBR, and 25% I/O configuration.

6.  $T_J = 25^{\circ}C$ , power supplies at nominal voltage.

In fpBGA and ftBGA packages the PLLs are connected to and powered from the auxiliary power supply. For these packages, the actual

auxiliary supply current is the sum of I<sub>CCAUX</sub> and I<sub>CCPLL</sub>. For csBGA, PQFP and TQFP packages the PLLs are powered independent of the

auxiliary power supply.

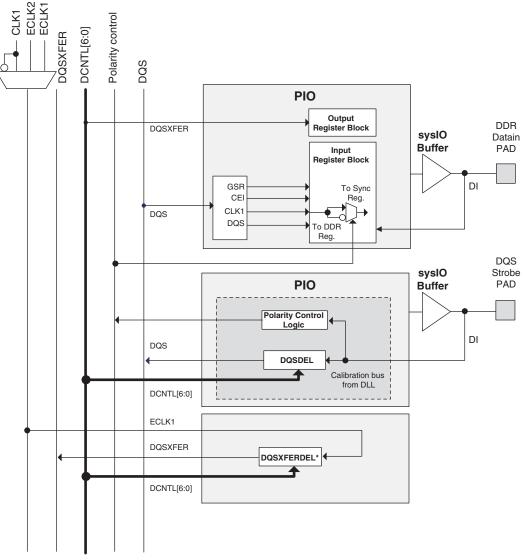

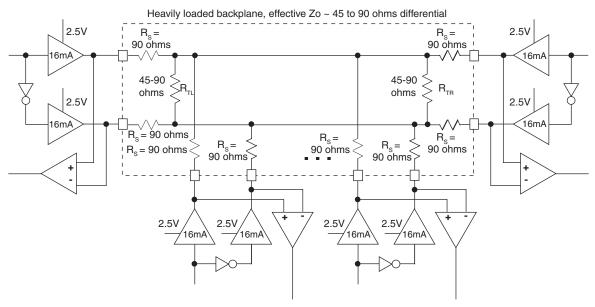

## BLVDS

The LatticeXP2 devices support the BLVDS standard. This standard is emulated using complementary LVCMOS outputs in conjunction with a parallel external resistor across the driver outputs. BLVDS is intended for use when multi-drop and bi-directional multi-point differential signaling is required. The scheme shown in Figure 3-2 is one possible solution for bi-directional multi-point differential signals.

#### Table 3-2. BLVDS DC Conditions<sup>1</sup>

|                   |                                                      | Typical          |                  |       |

|-------------------|------------------------------------------------------|------------------|------------------|-------|

| Parameter         | Description                                          | <b>Ζο = 45</b> Ω | <b>Ζο = 90</b> Ω | Units |

| V <sub>CCIO</sub> | Output Driver Supply (+/- 5%)                        | 2.50             | 2.50             | V     |

| Z <sub>OUT</sub>  | Driver Impedance                                     | 10.00            | 10.00            | Ω     |

| R <sub>S</sub>    | Driver Series Resistor (+/- 1%)                      | 90.00            | 90.00            | Ω     |

| R <sub>TL</sub>   | Driver Parallel Resistor (+/- 1%)                    | 45.00            | 90.00            | Ω     |

| R <sub>TR</sub>   | Receiver Termination (+/- 1%)                        | 45.00            | 90.00            | Ω     |

| V <sub>OH</sub>   | Output High Voltage (After R <sub>TL</sub> )         | 1.38             | 1.48             | V     |

| V <sub>OL</sub>   | Output Low Voltage (After R <sub>TL</sub> )          | 1.12             | 1.02             | V     |

| V <sub>OD</sub>   | Output Differential Voltage (After R <sub>TL</sub> ) | 0.25             | 0.46             | V     |

| V <sub>CM</sub>   | Output Common Mode Voltage                           | 1.25             | 1.25             | V     |

| I <sub>DC</sub>   | DC Output Current                                    | 11.24            | 10.20            | mA    |

**Over Recommended Operating Conditions**

1. For input buffer, see LVDS table.

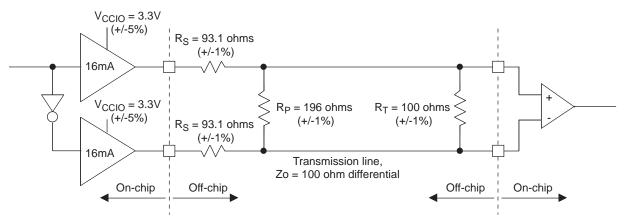

## LVPECL

The LatticeXP2 devices support the differential LVPECL standard. This standard is emulated using complementary LVCMOS outputs in conjunction with a parallel resistor across the driver outputs. The LVPECL input standard is supported by the LVDS differential input buffer. The scheme shown in Figure 3-3 is one possible solution for point-to-point signals.

### Figure 3-3. Differential LVPECL

#### Table 3-3. LVPECL DC Conditions<sup>1</sup>

| Parameter         | Description                                         | Typical | Units |

|-------------------|-----------------------------------------------------|---------|-------|

| V <sub>CCIO</sub> | Output Driver Supply (+/-5%)                        | 3.30    | V     |

| Z <sub>OUT</sub>  | Driver Impedance                                    | 10      | Ω     |

| R <sub>S</sub>    | Driver Series Resistor (+/-1%)                      | 93      | Ω     |

| R <sub>P</sub>    | Driver Parallel Resistor (+/-1%)                    | 196     | Ω     |

| R <sub>T</sub>    | Receiver Termination (+/-1%)                        | 100     | Ω     |

| V <sub>OH</sub>   | Output High Voltage (After R <sub>P</sub> )         | 2.05    | V     |

| V <sub>OL</sub>   | Output Low Voltage (After R <sub>P</sub> )          | 1.25    | V     |

| V <sub>OD</sub>   | Output Differential Voltage (After R <sub>P</sub> ) | 0.80    | V     |

| V <sub>CM</sub>   | Output Common Mode Voltage                          | 1.65    | V     |

| Z <sub>BACK</sub> | Back Impedance                                      | 100.5   | Ω     |

| I <sub>DC</sub>   | DC Output Current                                   | 12.11   | mA    |

#### **Over Recommended Operating Conditions**

1. For input buffer, see LVDS table.

## **Register-to-Register Performance (Continued)**

| Function                         | -7 Timing | Units |

|----------------------------------|-----------|-------|

| DSP IP Functions                 |           |       |

| 16-Tap Fully-Parallel FIR Filter | 198       | MHz   |

| 1024-pt FFT                      | 221       | MHz   |

| 8X8 Matrix Multiplication        | 196       | MHz   |

1. These timing numbers were generated using the ispLEVER design tool. Exact performance may vary with device, design and tool version. The tool uses internal parameters that have been characterized but are not tested on every device.

## **Derating Timing Tables**

Logic timing provided in the following sections of this data sheet and the Diamond design tools are worst case numbers in the operating range. Actual delays at nominal temperature and voltage for best case process, can be much better than the values given in the tables. The Diamond design tool can provide logic timing numbers at a particular temperature and voltage.

# LatticeXP2 External Switching Characteristics

|                     |                                                                   |              | -7                |      | -6   |      | -5   |      |       |

|---------------------|-------------------------------------------------------------------|--------------|-------------------|------|------|------|------|------|-------|

| Parameter           | Description                                                       | Device       | Min.              | Max. | Min. | Max. | Min. | Max. | Units |

| General I/O Pi      | n Parameters (using Primary Clo                                   | ck without I | PLL) <sup>1</sup> | 1    | 1    |      |      | 1    |       |

|                     |                                                                   | XP2-5        | —                 | 3.80 |      | 4.20 | —    | 4.60 | ns    |

|                     |                                                                   | XP2-8        | —                 | 3.80 | —    | 4.20 | —    | 4.60 | ns    |

| t <sub>CO</sub>     | Clock to Output - PIO Output<br>Register                          | XP2-17       | —                 | 3.80 | —    | 4.20 | —    | 4.60 | ns    |

|                     |                                                                   | XP2-30       | —                 | 4.00 | —    | 4.40 | —    | 4.90 | ns    |

|                     |                                                                   | XP2-40       | —                 | 4.00 | —    | 4.40 | —    | 4.90 | ns    |

|                     |                                                                   | XP2-5        | 0.00              |      | 0.00 | —    | 0.00 |      | ns    |

|                     |                                                                   | XP2-8        | 0.00              | _    | 0.00 | —    | 0.00 | _    | ns    |

| t <sub>SU</sub>     | Clock to Data Setup - PIO Input<br>Register                       | XP2-17       | 0.00              | _    | 0.00 | —    | 0.00 | _    | ns    |

|                     |                                                                   | XP2-30       | 0.00              | _    | 0.00 | —    | 0.00 | _    | ns    |

|                     |                                                                   | XP2-40       | 0.00              |      | 0.00 | —    | 0.00 |      | ns    |

|                     |                                                                   | XP2-5        | 1.40              |      | 1.70 | —    | 1.90 |      | ns    |

|                     |                                                                   | XP2-8        | 1.40              | _    | 1.70 | —    | 1.90 | _    | ns    |

| t <sub>H</sub>      | Clock to Data Hold - PIO Input<br>Register                        | XP2-17       | 1.40              |      | 1.70 | —    | 1.90 | —    | ns    |

|                     |                                                                   | XP2-30       | 1.40              |      | 1.70 | —    | 1.90 |      | ns    |

|                     |                                                                   | XP2-40       | 1.40              |      | 1.70 | —    | 1.90 |      | ns    |

|                     | Clock to Data Setup - PIO Input<br>Register with Data Input Delay | XP2-5        | 1.40              |      | 1.70 | —    | 1.90 |      | ns    |

|                     |                                                                   | XP2-8        | 1.40              |      | 1.70 | —    | 1.90 |      | ns    |

| t <sub>SU_DEL</sub> |                                                                   | XP2-17       | 1.40              | _    | 1.70 | —    | 1.90 | _    | ns    |

|                     |                                                                   | XP2-30       | 1.40              |      | 1.70 | —    | 1.90 | —    | ns    |

|                     |                                                                   | XP2-40       | 1.40              |      | 1.70 | —    | 1.90 |      | ns    |

|                     |                                                                   | XP2-5        | 0.00              |      | 0.00 | —    | 0.00 |      | ns    |

|                     |                                                                   | XP2-8        | 0.00              |      | 0.00 | —    | 0.00 | —    | ns    |

| t <sub>H_DEL</sub>  | Clock to Data Hold - PIO Input<br>Register with Input Data Delay  | XP2-17       | 0.00              |      | 0.00 | —    | 0.00 | —    | ns    |

|                     |                                                                   | XP2-30       | 0.00              |      | 0.00 | —    | 0.00 |      | ns    |

|                     |                                                                   | XP2-40       | 0.00              |      | 0.00 | —    | 0.00 | —    | ns    |

| f <sub>MAX_IO</sub> | Clock Frequency of I/O and PFU Register                           | XP2          | _                 | 420  | —    | 357  | —    | 311  | MHz   |

| General I/O Pi      | n Parameters (using Edge Clock                                    | without PLI  | _) <sup>1</sup>   |      |      |      |      |      |       |

|                     |                                                                   | XP2-5        | —                 | 3.20 | _    | 3.60 | —    | 3.90 | ns    |

|                     |                                                                   | XP2-8        | _                 | 3.20 |      | 3.60 | —    | 3.90 | ns    |

| t <sub>COE</sub>    | Clock to Output - PIO Output<br>Register                          | XP2-17       | —                 | 3.20 | _    | 3.60 | —    | 3.90 | ns    |

|                     |                                                                   | XP2-30       | _                 | 3.20 |      | 3.60 | _    | 3.90 | ns    |

|                     |                                                                   | XP2-40       | _                 | 3.20 |      | 3.60 | —    | 3.90 | ns    |

|                     |                                                                   | XP2-5        | 0.00              |      | 0.00 | —    | 0.00 |      | ns    |

|                     |                                                                   | XP2-8        | 0.00              |      | 0.00 | —    | 0.00 | —    | ns    |

| t <sub>SUE</sub>    | Clock to Data Setup - PIO Input<br>Register                       | XP2-17       | 0.00              | —    | 0.00 | —    | 0.00 | —    | ns    |

|                     |                                                                   | XP2-30       | 0.00              | —    | 0.00 | —    | 0.00 | —    | ns    |

|                     |                                                                   | XP2-40       | 0.00              | —    | 0.00 | —    | 0.00 | —    | ns    |

# LatticeXP2 Internal Switching Characteristics<sup>1</sup> (Continued)

|                                   |                                        | -7     |       | -6     |       | -5     |       |       |

|-----------------------------------|----------------------------------------|--------|-------|--------|-------|--------|-------|-------|

| Parameter                         | Description                            | Min.   | Max.  | Min.   | Max.  | Min.   | Max.  | Units |

| t <sub>HP_DSP</sub>               | Pipeline Register Hold Time            | -0.787 | _     | -0.890 | _     | -0.994 | —     | ns    |

| t <sub>SUO_DSP</sub>              | Output Register Setup Time             | 4.896  | _     | 5.413  | _     | 5.931  | —     | ns    |

| t <sub>HO_DSP</sub>               | Output Register Hold Time              | -1.439 | _     | -1.604 | _     | -1.770 | —     | ns    |

| t <sub>COI_DSP</sub> <sup>3</sup> | Input Register Clock to Output<br>Time | _      | 4.513 | —      | 4.947 | —      | 5.382 | ns    |

| t <sub>COP_DSP</sub> <sup>3</sup> | Pipeline Register Clock to Output Time | _      | 2.153 | —      | 2.272 | —      | 2.391 | ns    |

| t <sub>COO_DSP</sub> <sup>3</sup> | Output Register Clock to Output Time   | _      | 0.569 | —      | 0.600 | —      | 0.631 | ns    |

| t <sub>SUADSUB</sub>              | AdSub Input Register Setup Time        | -0.270 | —     | -0.298 | _     | -0.327 | —     | ns    |

| t <sub>HADSUB</sub>               | AdSub Input Register Hold Time         | 0.306  |       | 0.338  |       | 0.371  |       | ns    |

## **Over Recommended Operating Conditions**

1. Internal parameters are characterized, but not tested on every device.

2. RST resets VCO and all counters in PLL.

3. These parameters include the Adder Subtractor block in the path.

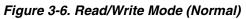

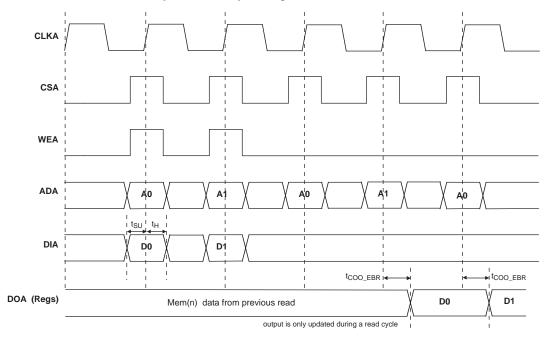

## **EBR Timing Diagrams**

Note: Input data and address are registered at the positive edge of the clock and output data appears after the positive edge of the clock.

Figure 3-7. Read/Write Mode with Input and Output Registers

# LatticeXP2 Family Timing Adders<sup>1, 2, 3, 4</sup>

| Buffer Type      | Description                            | -7    | -6    | -5    | Units |

|------------------|----------------------------------------|-------|-------|-------|-------|

| Input Adjusters  |                                        |       |       |       |       |

| LVDS25           | LVDS                                   | -0.26 | -0.11 | 0.04  | ns    |

| BLVDS25          | BLVDS                                  | -0.26 | -0.11 | 0.04  | ns    |

| MLVDS            | LVDS                                   | -0.26 | -0.11 | 0.04  | ns    |

| RSDS             | RSDS                                   | -0.26 | -0.11 | 0.04  | ns    |

| LVPECL33         | LVPECL                                 | -0.26 | -0.11 | 0.04  | ns    |

| HSTL18_I         | HSTL_18 class I                        | -0.23 | -0.08 | 0.07  | ns    |

| HSTL18_II        | HSTL_18 class II                       | -0.23 | -0.08 | 0.07  | ns    |

| HSTL18D_I        | Differential HSTL 18 class I           | -0.28 | -0.13 | 0.02  | ns    |

| HSTL18D_II       | Differential HSTL 18 class II          | -0.28 | -0.13 | 0.02  | ns    |

| HSTL15_I         | HSTL_15 class I                        | -0.23 | -0.09 | 0.06  | ns    |

| HSTL15D_I        | Differential HSTL 15 class I           | -0.28 | -0.13 | 0.01  | ns    |

| SSTL33_I         | SSTL_3 class I                         | -0.20 | -0.04 | 0.12  | ns    |

| SSTL33_II        | SSTL_3 class II                        | -0.20 | -0.04 | 0.12  | ns    |

| SSTL33D_I        | Differential SSTL_3 class I            | -0.27 | -0.11 | 0.04  | ns    |

| SSTL33D_II       | Differential SSTL_3 class II           | -0.27 | -0.11 | 0.04  | ns    |

| SSTL25_I         | SSTL_2 class I                         | -0.21 | -0.06 | 0.10  | ns    |

| SSTL25_II        | SSTL_2 class II                        | -0.21 | -0.06 | 0.10  | ns    |

| SSTL25D_I        | Differential SSTL_2 class I            | -0.27 | -0.12 | 0.03  | ns    |

| SSTL25D_II       | Differential SSTL_2 class II           | -0.27 | -0.12 | 0.03  | ns    |

| SSTL18_I         | SSTL_18 class I                        | -0.23 | -0.08 | 0.07  | ns    |

| SSTL18_II        | SSTL_18 class II                       | -0.23 | -0.08 | 0.07  | ns    |

| SSTL18D_I        | Differential SSTL_18 class I           | -0.28 | -0.13 | 0.02  | ns    |

| SSTL18D_II       | Differential SSTL_18 class II          | -0.28 | -0.13 | 0.02  | ns    |

| LVTTL33          | LVTTL                                  | -0.09 | 0.05  | 0.18  | ns    |

| LVCMOS33         | LVCMOS 3.3                             | -0.09 | 0.05  | 0.18  | ns    |

| LVCMOS25         | LVCMOS 2.5                             | 0.00  | 0.00  | 0.00  | ns    |

| LVCMOS18         | LVCMOS 1.8                             | -0.23 | -0.07 | 0.09  | ns    |

| LVCMOS15         | LVCMOS 1.5                             | -0.20 | -0.02 | 0.16  | ns    |

| LVCMOS12         | LVCMOS 1.2                             | -0.35 | -0.20 | -0.04 | ns    |

| PCI33            | 3.3V PCI                               | -0.09 | 0.05  | 0.18  | ns    |

| Output Adjusters |                                        |       |       |       |       |

| LVDS25E          | LVDS 2.5 E⁵                            | -0.25 | 0.02  | 0.30  | ns    |

| LVDS25           | LVDS 2.5                               | -0.25 | 0.02  | 0.30  | ns    |

| BLVDS25          | BLVDS 2.5                              | -0.28 | 0.00  | 0.28  | ns    |

| MLVDS            | MLVDS 2.5 <sup>5</sup>                 | -0.28 | 0.00  | 0.28  | ns    |

| RSDS             | RSDS 2.5 <sup>5</sup>                  | -0.25 | 0.02  | 0.30  | ns    |

| LVPECL33         | LVPECL 3.3 <sup>5</sup>                | -0.37 | -0.10 | 0.18  | ns    |

| HSTL18_I         | HSTL_18 class I 8mA drive              | -0.17 | 0.13  | 0.43  | ns    |

| HSTL18_II        | HSTL_18 class II                       | -0.29 | 0.00  | 0.29  | ns    |

| HSTL18D_I        | Differential HSTL 18 class I 8mA drive | -0.17 | 0.13  | 0.43  | ns    |

| HSTL18D_II       | Differential HSTL 18 class II          | -0.29 | 0.00  | 0.29  | ns    |

# LatticeXP2 Family Timing Adders<sup>1, 2, 3, 4</sup> (Continued)

| Buffer Type   | Description                              | -7    | -6    | -5    | Units |

|---------------|------------------------------------------|-------|-------|-------|-------|

| HSTL15_I      | HSTL_15 class I 4mA drive                | 0.32  | 0.69  | 1.06  | ns    |

| HSTL15D_I     | Differential HSTL 15 class I 4mA drive   | 0.32  | 0.69  | 1.06  | ns    |

| SSTL33_I      | SSTL_3 class I                           | -0.25 | 0.05  | 0.35  | ns    |

| SSTL33_II     | SSTL_3 class II                          | -0.31 | -0.02 | 0.27  | ns    |

| SSTL33D_I     | Differential SSTL_3 class I              | -0.25 | 0.05  | 0.35  | ns    |

| SSTL33D_II    | Differential SSTL_3 class II             | -0.31 | -0.02 | 0.27  | ns    |

| SSTL25_I      | SSTL_2 class I 8mA drive                 | -0.25 | 0.02  | 0.30  | ns    |

| SSTL25_II     | SSTL_2 class II 16mA drive               | -0.28 | 0.00  | 0.28  | ns    |

| SSTL25D_I     | Differential SSTL_2 class I 8mA drive    | -0.25 | 0.02  | 0.30  | ns    |

| SSTL25D_II    | Differential SSTL_2 class II 16mA drive  | -0.28 | 0.00  | 0.28  | ns    |

| SSTL18_I      | SSTL_1.8 class I                         | -0.17 | 0.13  | 0.43  | ns    |

| SSTL18_II     | SSTL_1.8 class II 8mA drive              | -0.18 | 0.12  | 0.42  | ns    |

| SSTL18D_I     | Differential SSTL_1.8 class I            | -0.17 | 0.13  | 0.43  | ns    |

| SSTL18D_II    | Differential SSTL_1.8 class II 8mA drive | -0.18 | 0.12  | 0.42  | ns    |

| LVTTL33_4mA   | LVTTL 4mA drive                          | -0.37 | -0.05 | 0.26  | ns    |

| LVTTL33_8mA   | LVTTL 8mA drive                          | -0.45 | -0.18 | 0.10  | ns    |

| LVTTL33_12mA  | LVTTL 12mA drive                         | -0.52 | -0.24 | 0.04  | ns    |

| LVTTL33_16mA  | LVTTL 16mA drive                         | -0.43 | -0.14 | 0.14  | ns    |

| LVTTL33_20mA  | LVTTL 20mA drive                         | -0.46 | -0.18 | 0.09  | ns    |

| LVCMOS33_4mA  | LVCMOS 3.3 4mA drive, fast slew rate     | -0.37 | -0.05 | 0.26  | ns    |

| LVCMOS33_8mA  | LVCMOS 3.3 8mA drive, fast slew rate     | -0.45 | -0.18 | 0.10  | ns    |

| LVCMOS33_12mA | LVCMOS 3.3 12mA drive, fast slew rate    | -0.52 | -0.24 | 0.04  | ns    |

| LVCMOS33_16mA | LVCMOS 3.3 16mA drive, fast slew rate    | -0.43 | -0.14 | 0.14  | ns    |

| LVCMOS33_20mA | LVCMOS 3.3 20mA drive, fast slew rate    | -0.46 | -0.18 | 0.09  | ns    |

| LVCMOS25_4mA  | LVCMOS 2.5 4mA drive, fast slew rate     | -0.42 | -0.15 | 0.13  | ns    |

| LVCMOS25_8mA  | LVCMOS 2.5 8mA drive, fast slew rate     | -0.48 | -0.21 | 0.05  | ns    |

| LVCMOS25_12mA | LVCMOS 2.5 12mA drive, fast slew rate    | 0.00  | 0.00  | 0.00  | ns    |

| LVCMOS25_16mA | LVCMOS 2.5 16mA drive, fast slew rate    | -0.45 | -0.18 | 0.08  | ns    |

| LVCMOS25_20mA | LVCMOS 2.5 20mA drive, fast slew rate    | -0.49 | -0.22 | 0.04  | ns    |

| LVCMOS18_4mA  | LVCMOS 1.8 4mA drive, fast slew rate     | -0.46 | -0.18 | 0.10  | ns    |

| LVCMOS18_8mA  | LVCMOS 1.8 8mA drive, fast slew rate     | -0.52 | -0.25 | 0.02  | ns    |

| LVCMOS18_12mA | LVCMOS 1.8 12mA drive, fast slew rate    | -0.56 | -0.30 | -0.03 | ns    |

| LVCMOS18_16mA | LVCMOS 1.8 16mA drive, fast slew rate    | -0.50 | -0.24 | 0.03  | ns    |

| LVCMOS15_4mA  | LVCMOS 1.5 4mA drive, fast slew rate     | -0.45 | -0.17 | 0.11  | ns    |

| LVCMOS15_8mA  | LVCMOS 1.5 8mA drive, fast slew rate     | -0.53 | -0.26 | 0.00  | ns    |

| LVCMOS12_2mA  | LVCMOS 1.2 2mA drive, fast slew rate     | -0.46 | -0.19 | 0.08  | ns    |

| LVCMOS12_6mA  | LVCMOS 1.2 6mA drive, fast slew rate     | -0.55 | -0.29 | -0.02 | ns    |

| LVCMOS33_4mA  | LVCMOS 3.3 4mA drive, slow slew rate     | 0.98  | 1.41  | 1.84  | ns    |

| LVCMOS33_8mA  | LVCMOS 3.3 8mA drive, slow slew rate     | 0.74  | 1.16  | 1.58  | ns    |

| LVCMOS33_12mA | LVCMOS 3.3 12mA drive, slow slew rate    | 0.56  | 0.97  | 1.38  | ns    |

| LVCMOS33_16mA | LVCMOS 3.3 16mA drive, slow slew rate    | 0.77  | 1.19  | 1.61  | ns    |

| LVCMOS33_20mA | LVCMOS 3.3 20mA drive, slow slew rate    | 0.57  | 0.98  | 1.40  | ns    |

# sysCLOCK PLL Timing

| Parameter                      | Description                              | Conditions                               | Min.  | Тур. | Max.  | Units |

|--------------------------------|------------------------------------------|------------------------------------------|-------|------|-------|-------|

| f <sub>IN</sub>                | Input Clock Frequency (CLKI, CLKFB)      |                                          | 10    | —    | 435   | MHz   |

| f <sub>OUT</sub>               | Output Clock Frequency (CLKOP,<br>CLKOS) |                                          | 10    | _    | 435   | MHz   |

| f                              | K-Divider Output Frequency               | CLKOK                                    | 0.078 | —    | 217.5 | MHz   |

| f <sub>OUT2</sub>              | R-Divider Output Frequency               | CLKOK2                                   | 3.3   |      | 145   | MHz   |

| f <sub>VCO</sub>               | PLL VCO Frequency                        |                                          | 435   |      | 870   | MHz   |

| f <sub>PFD</sub>               | Phase Detector Input Frequency           |                                          | 10    |      | 435   | MHz   |

| AC Characte                    | eristics                                 | •                                        |       |      | •     |       |

| t <sub>DT</sub>                | Output Clock Duty Cycle                  | Default duty cycle selected <sup>3</sup> | 45    | 50   | 55    | %     |

| t <sub>CPA</sub>               | Coarse Phase Adjust                      |                                          | -5    | 0    | 5     | %     |

| t <sub>PH</sub> <sup>4</sup>   | Output Phase Accuracy                    |                                          | -5    | 0    | 5     | %     |

|                                |                                          | f <sub>OUT</sub> > 400 MHz               | _     |      | ±50   | ps    |

| t <sub>OPJIT</sub> 1           | Output Clock Period Jitter               | 100 MHz < f <sub>OUT</sub> < 400 MHz     | _     |      | ±125  | ps    |

|                                |                                          | f <sub>OUT</sub> < 100 MHz               | _     |      | 0.025 | UIPP  |

| t <sub>SK</sub>                | Input Clock to Output Clock Skew         | N/M = integer                            |       |      | ±240  | ps    |

| t <sub>OPW</sub>               | Output Clock Pulse Width                 | At 90% or 10%                            | 1     |      | —     | ns    |

| <b>•</b> 2                     | PLL Lock-in Time                         | 25 to 435 MHz                            | _     |      | 50    | μs    |

| t <sub>LOCK</sub> <sup>2</sup> | FLL LOCK-III TIITIe                      | 10 to 25 MHz                             | _     |      | 100   | μs    |

| t <sub>IPJIT</sub>             | Input Clock Period Jitter                |                                          | —     |      | ±200  | ps    |

| t <sub>FBKDLY</sub>            | External Feedback Delay                  |                                          |       |      | 10    | ns    |

| t <sub>HI</sub>                | Input Clock High Time                    | 90% to 90%                               | 0.5   |      | —     | ns    |

| t <sub>LO</sub>                | Input Clock Low Time                     | 10% to 10%                               | 0.5   | —    | —     | ns    |

| t <sub>RSTKW</sub>             | Reset Signal Pulse Width (RSTK)          |                                          | 10    | —    | —     | ns    |

| t <sub>RSTW</sub>              | Reset Signal Pulse Width (RST)           |                                          | 500   | —    | —     | ns    |

### **Over Recommended Operating Conditions**

1. Jitter sample is taken over 10,000 samples of the primary PLL output with clean reference clock.

2. Output clock is valid after t<sub>LOCK</sub> for PLL reset and dynamic delay adjustment.

3. Using LVDS output buffers.

4. Relative to CLKOP.

# Flash Download Time (from On-Chip Flash to SRAM)

### **Over Recommended Operating Conditions**

| Symbol  | Parar                                                           | neter  | Min. | Тур. | Max. | Units |

|---------|-----------------------------------------------------------------|--------|------|------|------|-------|

| -       |                                                                 | XP2-5  | —    | 1.8  | 2.1  | ms    |

|         | PROGRAMN Low-to-                                                | XP2-8  | —    | 1.9  | 2.3  | ms    |

|         | High. Transition to Done                                        | XP2-17 | —    | 1.7  | 2.0  | ms    |

|         | High.                                                           | XP2-30 | —    | 2.0  | 2.1  | ms    |

| H .     |                                                                 | XP2-40 | —    | 2.0  | 2.3  | ms    |

| REFRESH |                                                                 | XP2-5  | —    | 1.8  | 2.1  | ms    |

|         | Power-up refresh when                                           | XP2-8  | —    | 1.9  | 2.3  | ms    |

|         | PROGRAMN is pulled                                              | XP2-17 | —    | 1.7  | 2.0  | ms    |

|         | up to V <sub>CC</sub><br>(V <sub>CC</sub> =V <sub>CC</sub> Min) | XP2-30 | —    | 2.0  | 2.1  | ms    |

|         |                                                                 | XP2-40 | —    | 2.0  | 2.3  | ms    |

## Flash Program Time

#### **Over Recommended Operating Conditions**

|                     |        |              | Program Time |       |

|---------------------|--------|--------------|--------------|-------|

| Device              | F      | lash Density | Тур.         | Units |

| XP2-5               | 1.2M   | TAG          | 1.0          | ms    |

| 767-2               | 1.2101 | Main Array   | 1.1          | S     |

| XP2-8               | 2.0M   | TAG          | 1.0          | ms    |

| XP2-8 2.0W          | 2.0101 | Main Array   | 1.4          | S     |

| XP2-17              | 3.6M   | TAG          | 1.0          | ms    |

| AF2-17              | 3.0101 | Main Array   | 1.8          | S     |

|                     | 6.0M   | TAG          | 2.0          | ms    |

| XP2-30              | 0.0101 | Main Array   | 3.0          | S     |

| XP2-40              | 8.0M   | TAG          | 2.0          | ms    |

| ∧r∠ <del>*4</del> 0 | 0.0101 | Main Array   | 4.0          | S     |

## **Flash Erase Time**

|        | Flash Density |            | Erase Time |       |

|--------|---------------|------------|------------|-------|

| Device |               |            | Тур.       | Units |

| XP2-5  | 1.2M          | TAG        | 1.0        | S     |

| AF 2-5 | 1.211         | Main Array | 3.0        | S     |

| XP2-8  | 2.0M          | TAG        | 1.0        | S     |

|        | 2.0101        | Main Array | 4.0        | S     |

| XP2-17 | 3.6M          | TAG        | 1.0        | S     |

|        |               | Main Array | 5.0        | S     |

| XP2-30 | 6.0M          | TAG        | 2.0        | S     |

|        | 0.0101        | Main Array | 7.0        | S     |

| XP2-40 | 8.0M          | TAG        | 2.0        | S     |

|        | 0.000         | Main Array | 9.0        | S     |

# LatticeXP2 Family Data Sheet Pinout Information

#### February 2012

Data Sheet DS1009

| Signal Name                               | I/O     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|-------------------------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| General Purpose                           |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|                                           |         | [Edge] indicates the edge of the device on which the pad is located. Valid edge designations are L (Left), B (Bottom), R (Right), T (Top).                                                                                                                                                                                                                                                                                                                                                             |  |  |

| P[Edge] [Row/Column Number*]_[A/B]        | I/O     | [Row/Column Number] indicates the PFU row or the column of the device on which the PIC exists. When Edge is T (Top) or B (Bottom), only need to specify Row Number. When Edge is L (Left) or R (Right), only need to specify Column Number.                                                                                                                                                                                                                                                            |  |  |

|                                           |         | [A/B] indicates the PIO within the PIC to which the pad is connected. Some of these user-programmable pins are shared with special function pins. These pins, when not used as special purpose pins, can be programmed as I/Os for user logic. During configuration the user-programmable I/Os are tri-stated with an internal pull-up resistor enabled. If any pin is not used (or not bonded to a package pin), it is also tri-stated with an internal pull-up resistor enabled after configuration. |  |  |

| GSRN                                      | I       | Global RESET signal (active low). Any I/O pin can be GSRN.                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| NC                                        | —       | No connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| GND                                       | _       | Ground. Dedicated pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| V <sub>CC</sub>                           | _       | Power supply pins for core logic. Dedicated pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| V <sub>CCAUX</sub>                        |         | Auxiliary power supply pin. This dedicated pin powers all the differential and referenced input buffers.                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| V <sub>CCPLL</sub>                        | —       | PLL supply pins. csBGA, PQFP and TQFP packages only.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| V <sub>CCIOx</sub>                        | _       | Dedicated power supply pins for I/O bank x.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| V <sub>REF1_x</sub> , V <sub>REF2_x</sub> | —       | Reference supply pins for I/O bank x. Pre-determined pins in each bank are assigned as $V_{\text{REF}}$ inputs. When not used, they may be used as I/O pins.                                                                                                                                                                                                                                                                                                                                           |  |  |

| PLL and Clock Functions (Used as us       | er prog | rammable I/O pins when not in use for PLL or clock pins)                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| [LOC][num]_V <sub>CCPLL</sub>             | —       | Power supply pin for PLL: LLC, LRC, URC, ULC, num = row from center.                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| [LOC][num]_GPLL[T, C]_IN_A                | I       | General Purpose PLL (GPLL) input pads: LLC, LRC, URC, ULC, num = row from center, $T =$ true and $C =$ complement, index A,B,Cat each side.                                                                                                                                                                                                                                                                                                                                                            |  |  |

| [LOC][num]_GPLL[T, C]_FB_A                | I       | Optional feedback GPLL input pads: LLC, LRC, URC, ULC, num = row from center, $T =$ true and $C =$ complement, index A,B,Cat each side.                                                                                                                                                                                                                                                                                                                                                                |  |  |

| PCLK[T, C]_[n:0]_[3:0]                    | I       | Primary Clock pads, $T =$ true and $C =$ complement, n per side, indexed by bank and 0,1,2,3 within bank.                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| [LOC]DQS[num]                             |         | DQS input pads: T (Top), R (Right), B (Bottom), L (Left), DQS, num = ball function number. Any pad can be configured to be output.                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| Test and Programming (Dedicated Pi        | ns)     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| TMS                                       | I       | Test Mode Select input, used to control the 1149.1 state machine. Pull-up is enabled during configuration.                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| тск                                       | I       | Test Clock input pin, used to clock the 1149.1 state machine. No pull-up enabled.                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| TDI I                                     |         | Test Data in pin. Used to load data into device using 1149.1 state machine.<br>After power-up, this TAP port can be activated for configuration by sending<br>appropriate command. (Note: once a configuration port is selected it is<br>locked. Another configuration port cannot be selected until the power-up                                                                                                                                                                                      |  |  |

# © 2012 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

sequence). Pull-up is enabled during configuration.

| Part Number      | Voltage | Grade | Package | Pins | Temp. | LUTs (k) |

|------------------|---------|-------|---------|------|-------|----------|

| LFXP2-40E-5F484C | 1.2V    | -5    | fpBGA   | 484  | COM   | 40       |

| LFXP2-40E-6F484C | 1.2V    | -6    | fpBGA   | 484  | COM   | 40       |

| LFXP2-40E-7F484C | 1.2V    | -7    | fpBGA   | 484  | COM   | 40       |

| LFXP2-40E-5F672C | 1.2V    | -5    | fpBGA   | 672  | COM   | 40       |

| LFXP2-40E-6F672C | 1.2V    | -6    | fpBGA   | 672  | COM   | 40       |

| LFXP2-40E-7F672C | 1.2V    | -7    | fpBGA   | 672  | COM   | 40       |

#### Industrial

| Part Number      | Voltage | Grade | Package | Pins | Temp. | LUTs (k) |

|------------------|---------|-------|---------|------|-------|----------|

| LFXP2-5E-5M132I  | 1.2V    | -5    | csBGA   | 132  | IND   | 5        |

| LFXP2-5E-6M132I  | 1.2V    | -6    | csBGA   | 132  | IND   | 5        |

| LFXP2-5E-6FT256I | 1.2V    | -6    | ftBGA   | 256  | IND   | 5        |

| Part Number      | Voltage | Grade | Package | Pins | Temp. | LUTs (k) |

|------------------|---------|-------|---------|------|-------|----------|

| LFXP2-8E-5M132I  | 1.2V    | -5    | csBGA   | 132  | IND   | 8        |

| LFXP2-8E-6M132I  | 1.2V    | -6    | csBGA   | 132  | IND   | 8        |

| LFXP2-5E-5FT256I | 1.2V    | -5    | ftBGA   | 256  | IND   | 5        |

| LFXP2-8E-5FT256I | 1.2V    | -5    | ftBGA   | 256  | IND   | 8        |

| LFXP2-8E-6FT256I | 1.2V    | -6    | ftBGA   | 256  | IND   | 8        |

| Part Number       | Voltage | Grade | Package | Pins | Temp. | LUTs (k) |

|-------------------|---------|-------|---------|------|-------|----------|

| LFXP2-17E-5FT256I | 1.2V    | -5    | ftBGA   | 256  | IND   | 17       |

| LFXP2-17E-6FT256I | 1.2V    | -6    | ftBGA   | 256  | IND   | 17       |

| LFXP2-17E-5F484I  | 1.2V    | -5    | fpBGA   | 484  | IND   | 17       |

| LFXP2-17E-6F484I  | 1.2V    | -6    | fpBGA   | 484  | IND   | 17       |

| Part Number       | Voltage | Grade | Package | Pins | Temp. | LUTs (k) |

|-------------------|---------|-------|---------|------|-------|----------|

| LFXP2-30E-5FT256I | 1.2V    | -5    | ftBGA   | 256  | IND   | 30       |

| LFXP2-30E-6FT256I | 1.2V    | -6    | ftBGA   | 256  | IND   | 30       |

| LFXP2-30E-5F484I  | 1.2V    | -5    | fpBGA   | 484  | IND   | 30       |

| LFXP2-30E-6F484I  | 1.2V    | -6    | fpBGA   | 484  | IND   | 30       |

| LFXP2-30E-5F672I  | 1.2V    | -5    | fpBGA   | 672  | IND   | 30       |

| LFXP2-30E-6F672I  | 1.2V    | -6    | fpBGA   | 672  | IND   | 30       |

# LatticeXP2 Family Data Sheet Supplemental Information

#### February 2012

Data Sheet DS1009

## **For Further Information**

A variety of technical notes for the LatticeXP2 FPGA family are available on the Lattice Semiconductor web site at <u>www.latticesemi.com</u>.

- TN1136, LatticeXP2 sysIO Usage Guide

- TN1137, LatticeXP2 Memory Usage Guide

- TN1138, LatticeXP2 High Speed I/O Interface

- TN1126, LatticeXP2 sysCLOCK PLL Design and Usage Guide

- TN1139, Power Estimation and Management for LatticeXP2 Devices

- TN1140, LatticeXP2 sysDSP Usage Guide

- TN1141, LatticeXP2 sysCONFIG Usage Guide

- TN1142, LatticeXP2 Configuration Encryption and Security Usage Guide

- TN1087, Minimizing System Interruption During Configuration Using TransFR Technology

- TN1220, LatticeXP2 Dual Boot Feature

- TN1130, LatticeXP2 Soft Error Detection (SED) Usage Guide

- TN1143, LatticeXP2 Hardware Checklist

For further information on interface standards refer to the following websites:

- JEDEC Standards (LVTTL, LVCMOS, SSTL, HSTL): www.jedec.org

- PCI: <u>www.pcisig.com</u>

© 2012 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Date            | Version | Section                             | Change Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------|---------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| April 2008      | 01.4    | DC and Switching                    | Updated Flash Download Time (From On-Chip Flash to SRAM) Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| (cont.)         | (cont.) | Characteristics (cont.)             | Updated Flash Program Time Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                 |         |                                     | Updated Flash Erase Time Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                 |         |                                     | Updated FlashBAK (from EBR to Flash) Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                 |         |                                     | Updated Hot Socketing Specifications Table footnotes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                 |         | Pinout Information                  | Updated Signal Descriptions Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| June 2008       | 01.5    | Architecture                        | Removed Read-Before-Write sysMEM EBR mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |