Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                                              |

|--------------------------------|------------------------------------------------------------------------------|

| Product Status                 | Obsolete                                                                     |

| Number of LABs/CLBs            | 3625                                                                         |

| Number of Logic Elements/Cells | 29000                                                                        |

| Total RAM Bits                 | 396288                                                                       |

| Number of I/O                  | 201                                                                          |

| Number of Gates                | -                                                                            |

| Voltage - Supply               | 1.14V ~ 1.26V                                                                |

| Mounting Type                  | Surface Mount                                                                |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                              |

| Package / Case                 | 256-LBGA                                                                     |

| Supplier Device Package        | 256-FTBGA (17x17)                                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfxp2-30e-7ft256c |

|                                |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# LatticeXP2 Family Data Sheet Architecture

#### August 2014

Data Sheet DS1009

## **Architecture Overview**

Each LatticeXP2 device contains an array of logic blocks surrounded by Programmable I/O Cells (PIC). Interspersed between the rows of logic blocks are rows of sysMEM<sup>™</sup> Embedded Block RAM (EBR) and a row of sys-DSP<sup>™</sup> Digital Signal Processing blocks as shown in Figure 2-1.

On the left and right sides of the Programmable Functional Unit (PFU) array, there are Non-volatile Memory Blocks. In configuration mode the nonvolatile memory is programmed via the IEEE 1149.1 TAP port or the sysCONFIG<sup>™</sup> peripheral port. On power up, the configuration data is transferred from the Non-volatile Memory Blocks to the configuration SRAM. With this technology, expensive external configuration memory is not required, and designs are secured from unauthorized read-back. This transfer of data from non-volatile memory to configuration SRAM via wide busses happens in microseconds, providing an "instant-on" capability that allows easy interfacing in many applications. LatticeXP2 devices can also transfer data from the sysMEM EBR blocks to the Non-volatile Memory Blocks at user request.

There are two kinds of logic blocks, the PFU and the PFU without RAM (PFF). The PFU contains the building blocks for logic, arithmetic, RAM and ROM functions. The PFF block contains building blocks for logic, arithmetic and ROM functions. Both PFU and PFF blocks are optimized for flexibility allowing complex designs to be implemented quickly and efficiently. Logic Blocks are arranged in a two-dimensional array. Only one type of block is used per row.

LatticeXP2 devices contain one or more rows of sysMEM EBR blocks. sysMEM EBRs are large dedicated 18Kbit memory blocks. Each sysMEM block can be configured in a variety of depths and widths of RAM or ROM. In addition, LatticeXP2 devices contain up to two rows of DSP Blocks. Each DSP block has multipliers and adder/accumulators, which are the building blocks for complex signal processing capabilities.

Each PIC block encompasses two PIOs (PIO pairs) with their respective sysIO buffers. The sysIO buffers of the LatticeXP2 devices are arranged into eight banks, allowing the implementation of a wide variety of I/O standards. PIO pairs on the left and right edges of the device can be configured as LVDS transmit/receive pairs. The PIC logic also includes pre-engineered support to aid in the implementation of high speed source synchronous standards such as 7:1 LVDS interfaces, found in many display applications, and memory interfaces including DDR and DDR2.

The LatticeXP2 registers in PFU and sysI/O can be configured to be SET or RESET. After power up and device is configured, the device enters into user mode with these registers SET/RESET according to the configuration setting, allowing device entering to a known state for predictable system function.

Other blocks provided include PLLs and configuration functions. The LatticeXP2 architecture provides up to four General Purpose PLLs (GPLL) per device. The GPLL blocks are located in the corners of the device.

The configuration block that supports features such as configuration bit-stream de-encryption, transparent updates and dual boot support is located between banks two and three. Every device in the LatticeXP2 family supports a sysCONFIG port, muxed with bank seven I/Os, which supports serial device configuration. A JTAG port is provided between banks two and three.

This family also provides an on-chip oscillator. LatticeXP2 devices use 1.2V as their core voltage.

<sup>© 2014</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

## Modes of Operation

Each slice has up to four potential modes of operation: Logic, Ripple, RAM and ROM.

#### Logic Mode

In this mode, the LUTs in each slice are configured as LUT4s. A LUT4 has 16 possible input combinations. Fourinput logic functions are generated by programming the LUT4. Since there are two LUT4s per slice, a LUT5 can be constructed within one slice. Larger LUTs such as LUT6, LUT7 and LUT8, can be constructed by concatenating two or more slices. Note that a LUT8 requires more than four slices.

#### **Ripple Mode**

Ripple mode allows efficient implementation of small arithmetic functions. In ripple mode, the following functions can be implemented by each slice:

- Addition 2-bit

- Subtraction 2-bit

- Add/Subtract 2-bit using dynamic control

- Up counter 2-bit

- Down counter 2-bit

- Up/Down counter with async clear

- Up/Down counter with preload (sync)

- Ripple mode multiplier building block

- Multiplier support

- Comparator functions of A and B inputs

- A greater-than-or-equal-to B

- A not-equal-to B

- A less-than-or-equal-to B

Two carry signals, FCI and FCO, are generated per slice in this mode, allowing fast arithmetic functions to be constructed by concatenating slices.

#### RAM Mode

In this mode, a 16x4-bit distributed Single Port RAM (SPR) can be constructed using each LUT block in Slice 0 and Slice 2 as a 16x1-bit memory. Slice 1 is used to provide memory address and control signals. A 16x2-bit Pseudo Dual Port RAM (PDPR) memory is created by using one slice as the read-write port and the other companion slice as the read-only port.

The Lattice design tools support the creation of a variety of different size memories. Where appropriate, the software will construct these using distributed memory primitives that represent the capabilities of the PFU. Table 2-3 shows the number of slices required to implement different distributed RAM primitives. For more information on using RAM in LatticeXP2 devices, please see TN1137, <u>LatticeXP2 Memory Usage Guide</u>.

#### Table 2-3. Number of Slices Required For Implementing Distributed RAM

|                  | SPR 16X4 | PDPR 16X4 |

|------------------|----------|-----------|

| Number of slices | 3        | 3         |

Note: SPR = Single Port RAM, PDPR = Pseudo Dual Port RAM

#### **ROM Mode**

ROM mode uses the LUT logic; hence, Slices 0 through 3 can be used in the ROM mode. Preloading is accomplished through the programming interface during PFU configuration.

## Primary Clock Routing

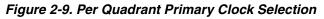

The clock routing structure in LatticeXP2 devices consists of a network of eight primary clock lines (CLK0 through CLK7) per quadrant. The primary clocks of each quadrant are generated from muxes located in the center of the device. All the clock sources are connected to these muxes. Figure 2-9 shows the clock routing for one quadrant. Each quadrant mux is identical. If desired, any clock can be routed globally.

## **Dynamic Clock Select (DCS)**

The DCS is a smart multiplexer function available in the primary clock routing. It switches between two independent input clock sources without any glitches or runt pulses. This is achieved irrespective of when the select signal is toggled. There are two DCS blocks per quadrant; in total, eight DCS blocks per device. The inputs to the DCS block come from the center muxes. The output of the DCS is connected to primary clocks CLK6 and CLK7 (see Figure 2-9).

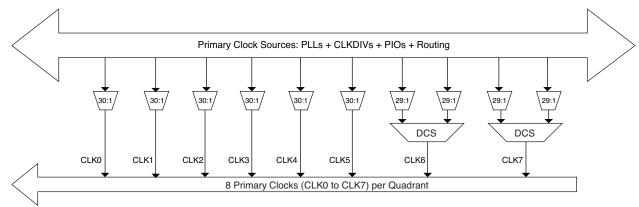

Figure 2-10 shows the timing waveforms of the default DCS operating mode. The DCS block can be programmed to other modes. For more information on the DCS, please see TN1126, <u>LatticeXP2 sysCLOCK PLL Design and</u> <u>Usage Guide</u>.

#### Figure 2-10. DCS Waveforms

## Secondary Clock/Control Routing

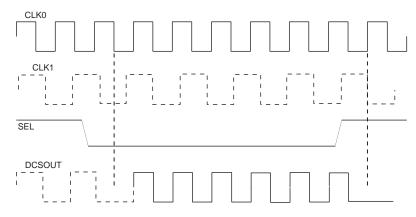

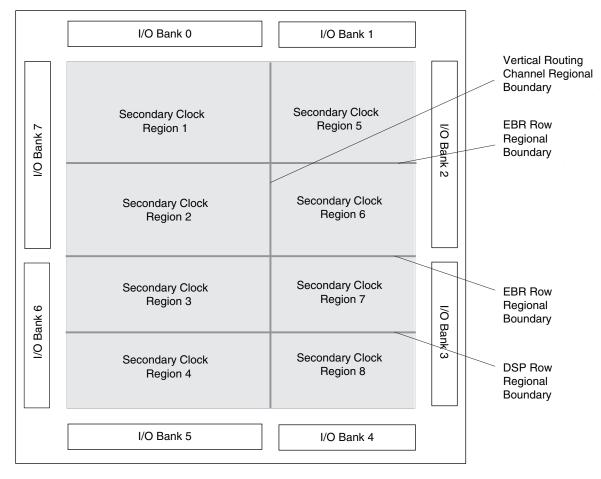

Secondary clocks in the LatticeXP2 devices are region-based resources. The benefit of region-based resources is the relatively low injection delay and skew within the region, as compared to primary clocks. EBR rows, DSP rows and a special vertical routing channel bound the secondary clock regions. This special vertical routing channel aligns with either the left edge of the center DSP block in the DSP row or the center of the DSP row. Figure 2-11 shows this special vertical routing channel and the eight secondary clock regions for the LatticeXP2-40.

LatticeXP2-30 and smaller devices have six secondary clock regions. All devices in the LatticeXP2 family have four secondary clocks (SC0 to SC3) which are distributed to every region.

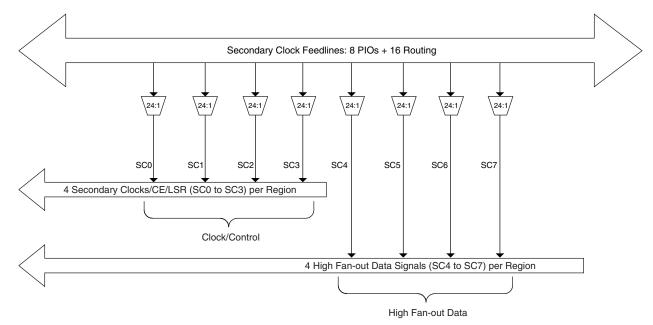

The secondary clock muxes are located in the center of the device. Figure 2-12 shows the mux structure of the secondary clock routing. Secondary clocks SC0 to SC3 are used for clock and control and SC4 to SC7 are used for high fan-out signals.

## Figure 2-12. Secondary Clock Selection

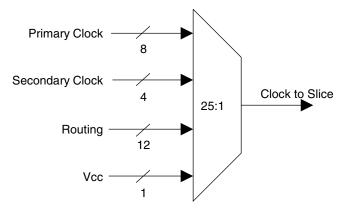

## Slice Clock Selection

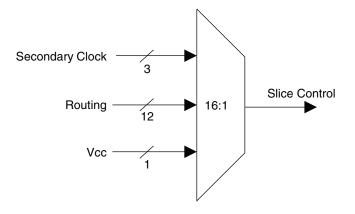

Figure 2-13 shows the clock selections and Figure 2-14 shows the control selections for Slice0 through Slice2. All the primary clocks and the four secondary clocks are routed to this clock selection mux. Other signals, via routing, can be used as clock inputs to the slices. Slice controls are generated from the secondary clocks or other signals connected via routing.

If none of the signals are selected for both clock and control, then the default value of the mux output is 1. Slice 3 does not have any registers; therefore it does not have the clock or control muxes.

## Figure 2-13. Slice0 through Slice2 Clock Selection

### Figure 2-14. Slice0 through Slice2 Control Selection

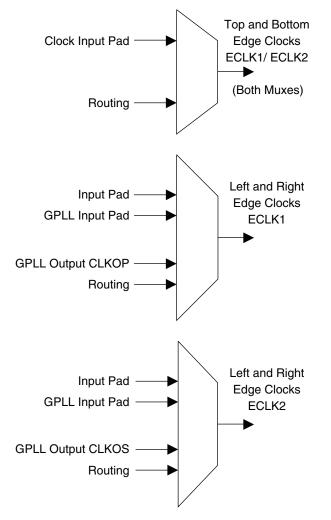

## **Edge Clock Routing**

LatticeXP2 devices have eight high-speed edge clocks that are intended for use with the PIOs in the implementation of high-speed interfaces. Each device has two edge clocks per edge. Figure 2-15 shows the selection muxes for these clocks.

#### Figure 2-15. Edge Clock Mux Connections

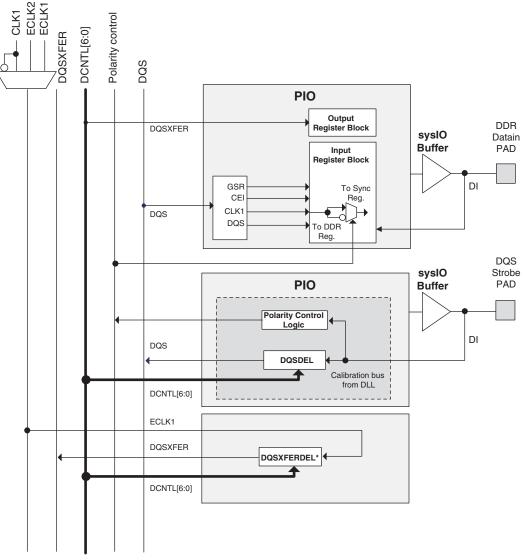

#### Figure 2-31. DQS Local Bus

\*DQSXFERDEL shifts ECLK1 by 90% and is not associated with a particular PIO.

## **Polarity Control Logic**

In a typical DDR memory interface design, the phase relationship between the incoming delayed DQS strobe and the internal system clock (during the READ cycle) is unknown. The LatticeXP2 family contains dedicated circuits to transfer data between these domains. To prevent set-up and hold violations, at the domain transfer between DQS (delayed) and the system clock, a clock polarity selector is used. This changes the edge on which the data is registered in the synchronizing registers in the input register block and requires evaluation at the start of each READ cycle for the correct clock polarity.

Prior to the READ operation in DDR memories, DQS is in tristate (pulled by termination). The DDR memory device drives DQS low at the start of the preamble state. A dedicated circuit detects this transition. This signal is used to control the polarity of the clock to the synchronizing registers.

#### Table 2-13. Supported Output Standards

| Output Standard                  | Drive                      | V <sub>CCIO</sub> (Nom.) |  |  |  |

|----------------------------------|----------------------------|--------------------------|--|--|--|

| Single-ended Interfaces          |                            |                          |  |  |  |

| LVTTL                            | 4mA, 8mA, 12mA, 16mA, 20mA | 3.3                      |  |  |  |

| LVCMOS33                         | 4mA, 8mA, 12mA 16mA, 20mA  | 3.3                      |  |  |  |

| LVCMOS25                         | 4mA, 8mA, 12mA, 16mA, 20mA | 2.5                      |  |  |  |

| LVCMOS18                         | 4mA, 8mA, 12mA, 16mA       | 1.8                      |  |  |  |

| LVCMOS15                         | 4mA, 8mA                   | 1.5                      |  |  |  |

| LVCMOS12                         | 2mA, 6mA                   | 1.2                      |  |  |  |

| LVCMOS33, Open Drain             | 4mA, 8mA, 12mA 16mA, 20mA  |                          |  |  |  |

| LVCMOS25, Open Drain             | 4mA, 8mA, 12mA 16mA, 20mA  |                          |  |  |  |

| LVCMOS18, Open Drain             | 4mA, 8mA, 12mA 16mA        | _                        |  |  |  |

| LVCMOS15, Open Drain             | 4mA, 8mA                   |                          |  |  |  |

| LVCMOS12, Open Drain             | 2mA, 6mA                   |                          |  |  |  |

| PCI33                            | N/A                        | 3.3                      |  |  |  |

| HSTL18 Class I, II               | N/A                        | 1.8                      |  |  |  |

| HSTL15 Class I                   | N/A                        | 1.5                      |  |  |  |

| SSTL33 Class I, II               | N/A                        | 3.3                      |  |  |  |

| SSTL25 Class I, II               | N/A                        | 2.5                      |  |  |  |

| SSTL18 Class I, II               | N/A                        | 1.8                      |  |  |  |

| Differential Interfaces          |                            |                          |  |  |  |

| Differential SSTL33, Class I, II | N/A                        | 3.3                      |  |  |  |

| Differential SSTL25, Class I, II | N/A                        | 2.5                      |  |  |  |

| Differential SSTL18, Class I, II | N/A                        | 1.8                      |  |  |  |

| Differential HSTL18, Class I, II | N/A                        | 1.8                      |  |  |  |

| Differential HSTL15, Class I     | N/A                        | 1.5                      |  |  |  |

| LVDS <sup>1, 2</sup>             | N/A                        | 2.5                      |  |  |  |

| MLVDS <sup>1</sup>               | N/A                        | 2.5                      |  |  |  |

| BLVDS <sup>1</sup>               | N/A                        | 2.5                      |  |  |  |

| LVPECL <sup>1</sup>              | N/A                        | 3.3                      |  |  |  |

| RSDS <sup>1</sup>                | N/A                        | 2.5                      |  |  |  |

| LVCMOS33D <sup>1</sup>           | 4mA, 8mA, 12mA, 16mA, 20mA | 3.3                      |  |  |  |

1. Emulated with external resistors.

2. On the left and right edges, LVDS outputs are supported with a dedicated differential output driver on 50% of the I/Os. This solution does not require external resistors at the driver.

## **Hot Socketing**

LatticeXP2 devices have been carefully designed to ensure predictable behavior during power-up and powerdown. Power supplies can be sequenced in any order. During power-up and power-down sequences, the I/Os remain in tri-state until the power supply voltage is high enough to ensure reliable operation. In addition, leakage into I/O pins is controlled to within specified limits. This allows for easy integration with the rest of the system. These capabilities make the LatticeXP2 ideal for many multiple power supply and hot-swap applications.

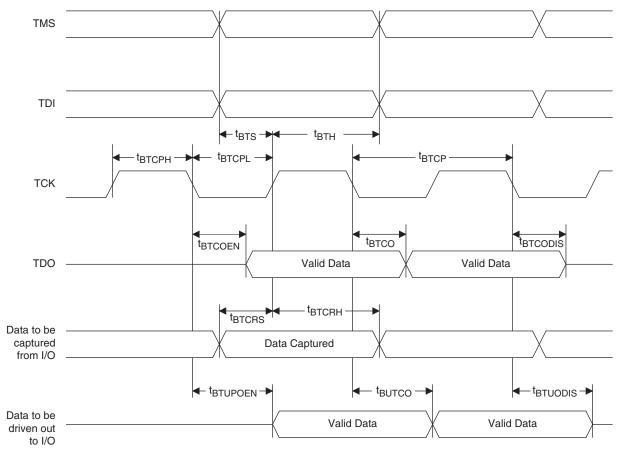

## IEEE 1149.1-Compliant Boundary Scan Testability

All LatticeXP2 devices have boundary scan cells that are accessed through an IEEE 1149.1 compliant Test Access Port (TAP). This allows functional testing of the circuit board, on which the device is mounted, through a serial scan path that can access all critical logic nodes. Internal registers are linked internally, allowing test data to be shifted in

# LatticeXP2 Family Data Sheet DC and Switching Characteristics

#### September 2014

Data Sheet DS1009

## Absolute Maximum Ratings<sup>1, 2, 3</sup>

| Supply Voltage V <sub>CC</sub> 0.5 to 1.32V                                  |

|------------------------------------------------------------------------------|

| Supply Voltage $V_{CCAUX} \dots \dots \dots 0.5$ to $3.75V$                  |

| Supply Voltage $V_{CCJ} \dots \dots \dots \dots 0.5$ to $3.75V$              |

| Supply Voltage $V_{\mbox{\scriptsize CCPLL}}{}^4.\ldots\ldots$ -0.5 to 3.75V |

| Output Supply Voltage $V_{CCIO}$ $\ldots$ 0.5 to 3.75V                       |

| Input or I/O Tristate Voltage Applied $^5,\ldots\ldots$ -0.5 to 3.75V        |

| Storage Temperature (Ambient) $\ldots \ldots$ -65 to 150°C                   |

| Junction Temperature Under Bias (Tj) +125°C                                  |

1. Stress above those listed under the "Absolute Maximum Ratings" may cause permanent damage to the device. Functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

2. Compliance with the Lattice <u>Thermal Management</u> document is required.

3. All voltages referenced to GND.

4. V<sub>CCPLL</sub> only available on csBGA, PQFP and TQFP packages.

5. Overshoot and undershoot of -2V to ( $V_{IHMAX}$  + 2) volts is permitted for a duration of <20 ns.

## **Recommended Operating Conditions**

| Symbol                               | Parameter                                       | Min.  | Max.  | Units |

|--------------------------------------|-------------------------------------------------|-------|-------|-------|

| V <sub>CC</sub>                      | Core Supply Voltage                             | 1.14  | 1.26  | V     |

| V <sub>CCAUX</sub> <sup>4, 5</sup>   | Auxiliary Supply Voltage                        | 3.135 | 3.465 | V     |

| V <sub>CCPLL</sub> <sup>1</sup>      | PLL Supply Voltage                              | 3.135 | 3.465 | V     |

| V <sub>CCIO</sub> <sup>2, 3, 4</sup> | I/O Driver Supply Voltage                       | 1.14  | 3.465 | V     |

| V <sub>CCJ</sub> <sup>2</sup>        | Supply Voltage for IEEE 1149.1 Test Access Port |       | 3.465 | V     |

| t <sub>JCOM</sub>                    | Junction Temperature, Commercial Operation      |       | 85    | °C    |

| t <sub>JIND</sub>                    | Junction Temperature, Industrial Operation      | -40   | 100   | °C    |

1.  $V_{CCPLL}$  only available on csBGA, PQFP and TQFP packages.

If V<sub>CCIO</sub> or V<sub>CCJ</sub> is set to 1.2 V, they must be connected to the same power supply as V<sub>CC</sub>. If V<sub>CCIO</sub> or V<sub>CCJ</sub> is set to 3.3V, they must be connected to the same power supply as V<sub>CCAUX</sub>.

3. See recommended voltages by I/O standard in subsequent table.

4. To ensure proper I/O behavior,  $V_{CCIO}$  must be turned off at the same time or earlier than  $V_{CCAUX}$ .

5. In fpBGA and ftBGA packages, the PLLs are connected to, and powered from, the auxiliary power supply.

## **On-Chip Flash Memory Specifications**

| Symbol   | Parameter                                                        | Max.    | Units  |

|----------|------------------------------------------------------------------|---------|--------|

|          | Flash Programming Cycles per t <sub>RETENTION</sub> <sup>1</sup> | 10,000  | Cvcles |

| NPROGCYC | Flash Functional Programming Cycles                              | 100,000 | Oycles |

1. The minimum data retention, t<sub>RETENTION</sub>, is 20 years.

<sup>© 2014</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

## Supply Current (Standby)<sup>1, 2, 3, 4</sup>

| Symbol             | Parameter                                   | Device | Typical⁵ | Units |

|--------------------|---------------------------------------------|--------|----------|-------|

|                    |                                             | XP2-5  | 14       | mA    |

|                    |                                             | XP2-8  | 18       | mA    |

| lcc                | Core Power Supply Current                   | XP2-17 | 24       | mA    |

|                    |                                             | XP2-30 | 35       | mA    |

|                    |                                             | XP2-40 | 45       | mA    |

| I <sub>CCAUX</sub> | Auxiliary Power Supply Current <sup>6</sup> | XP2-5  | 15       | mA    |

|                    |                                             | XP2-8  | 15       | mA    |

|                    |                                             | XP2-17 | 15       | mA    |

|                    |                                             | XP2-30 | 16       | mA    |

|                    |                                             | XP2-40 | 16       | mA    |

| CCPLL              | PLL Power Supply Current (per PLL)          |        | 0.1      | mA    |

| CCIO               | Bank Power Supply Current (per bank)        |        | 2        | mA    |

| CCJ                | V <sub>CCJ</sub> Power Supply Current       |        | 0.25     | mA    |

## **Over Recommended Operating Conditions**

1. For further information on supply current, please see TN1139, Power Estimation and Management for LatticeXP2 Devices.

2. Assumes all outputs are tristated, all inputs are configured as LVCMOS and held at the V<sub>CCIO</sub> or GND.

3. Frequency 0 MHz.

4. Pattern represents a "blank" configuration data file.

5.  $T_J = 25^{\circ}C$ , power supplies at nominal voltage.

6. In fpBGA and ftBGA packages the PLLs are connected to and powered from the auxiliary power supply. For these packages, the actual auxiliary supply current is the sum of I<sub>CCAUX</sub> and I<sub>CCPLL</sub>. For csBGA, PQFP and TQFP packages the PLLs are powered independent of the auxiliary power supply.

# LatticeXP2 Family Timing Adders<sup>1, 2, 3, 4</sup> (Continued)

#### **Over Recommended Operating Conditions**

| Buffer Type   | Description                           | -7    | -6    | -5    | Units |

|---------------|---------------------------------------|-------|-------|-------|-------|

| LVCMOS25_4mA  | LVCMOS 2.5 4mA drive, slow slew rate  | 1.05  | 1.43  | 1.81  | ns    |

| LVCMOS25_8mA  | LVCMOS 2.5 8mA drive, slow slew rate  | 0.78  | 1.15  | 1.52  | ns    |

| LVCMOS25_12mA | LVCMOS 2.5 12mA drive, slow slew rate | 0.59  | 0.96  | 1.33  | ns    |

| LVCMOS25_16mA | LVCMOS 2.5 16mA drive, slow slew rate | 0.81  | 1.18  | 1.55  | ns    |

| LVCMOS25_20mA | LVCMOS 2.5 20mA drive, slow slew rate | 0.61  | 0.98  | 1.35  | ns    |

| LVCMOS18_4mA  | LVCMOS 1.8 4mA drive, slow slew rate  | 1.01  | 1.38  | 1.75  | ns    |

| LVCMOS18_8mA  | LVCMOS 1.8 8mA drive, slow slew rate  | 0.72  | 1.08  | 1.45  | ns    |

| LVCMOS18_12mA | LVCMOS 1.8 12mA drive, slow slew rate | 0.53  | 0.90  | 1.26  | ns    |

| LVCMOS18_16mA | LVCMOS 1.8 16mA drive, slow slew rate | 0.74  | 1.11  | 1.48  | ns    |

| LVCMOS15_4mA  | LVCMOS 1.5 4mA drive, slow slew rate  | 0.96  | 1.33  | 1.71  | ns    |

| LVCMOS15_8mA  | LVCMOS 1.5 8mA drive, slow slew rate  | -0.53 | -0.26 | 0.00  | ns    |

| LVCMOS12_2mA  | LVCMOS 1.2 2mA drive, slow slew rate  | 0.90  | 1.27  | 1.65  | ns    |

| LVCMOS12_6mA  | LVCMOS 1.2 6mA drive, slow slew rate  | -0.55 | -0.29 | -0.02 | ns    |

| PCI33         | 3.3V PCI                              | -0.29 | -0.01 | 0.26  | ns    |

1. Timing Adders are characterized but not tested on every device.

2. LVCMOS timing measured with the load specified in Switching Test Condition table.

3. All other standards tested according to the appropriate specifications.

4. The base parameters used with these timing adders to calculate timing are listed in the LatticeXP2 Internal Switching Characteristics table under PIO Input/Output Timing.

5. These timing adders are measured with the recommended resistor values.

## LatticeXP2 sysCONFIG Port Timing Specifications

| Parameter            | Description                                                  | Min  | Max      | Units  |

|----------------------|--------------------------------------------------------------|------|----------|--------|

| sysCONFIG PC         | R, Initialization and Wake Up                                |      | <u> </u> |        |

| t <sub>ICFG</sub>    | Minimum Vcc to INITN High                                    |      | 50       | ms     |

| t <sub>VMC</sub>     | Time from t <sub>ICFG</sub> to valid Master CCLK             | _    | 2        | μs     |

| t <sub>PRGMRJ</sub>  | PROGRAMN Pin Pulse Rejection                                 | —    | 12       | ns     |

| t <sub>PRGM</sub>    | PROGRAMN Low Time to Start Configuration                     | 50   | —        | ns     |

| t <sub>DINIT</sub> 1 | PROGRAMN High to INITN High Delay                            |      | 1        | ms     |

| t <sub>DPPINIT</sub> | Delay Time from PROGRAMN Low to INITN Low                    |      | 50       | ns     |

| t <sub>DPPDONE</sub> | Delay Time from PROGRAMN Low to DONE Low                     | —    | 50       | ns     |

| t <sub>IODISS</sub>  | User I/O Disable from PROGRAMN Low                           |      | 35       | ns     |

| t <sub>IOENSS</sub>  | User I/O Enabled Time from CCLK Edge During Wake-up Sequence |      | 25       | ns     |

| t <sub>MWC</sub>     | Additional Wake Master Clock Signals after DONE Pin High     | 0    | —        | Cycles |

| sysCONFIG SP         | I Port (Master)                                              |      | •        |        |

| t <sub>CFGX</sub>    | INITN High to CCLK Low                                       | —    | 1        | μs     |

| t <sub>CSSPI</sub>   | INITN High to CSSPIN Low                                     | _    | 2        | μs     |

| t <sub>CSCCLK</sub>  | CCLK Low before CSSPIN Low                                   | 0    | —        | ns     |

| t <sub>SOCDO</sub>   | CCLK Low to Output Valid                                     | _    | 15       | ns     |

| t <sub>CSPID</sub>   | CSSPIN[0:1] Low to First CCLK Edge Setup Time                | 2cyc | 600+6cyc | ns     |

| f <sub>MAXSPI</sub>  | Max CCLK Frequency                                           | _    | 20       | MHz    |

| t <sub>SUSPI</sub>   | SOSPI Data Setup Time Before CCLK                            | 7    | —        | ns     |

| t <sub>HSPI</sub>    | SOSPI Data Hold Time After CCLK                              | 10   | —        | ns     |

| sysCONFIG SP         | I Port (Slave)                                               |      | •        |        |

| f <sub>MAXSPIS</sub> | Slave CCLK Frequency                                         | —    | 25       | MHz    |

| t <sub>RF</sub>      | Rise and Fall Time                                           | 50   | —        | mV/ns  |

| t <sub>stco</sub>    | Falling Edge of CCLK to SOSPI Active                         | —    | 20       | ns     |

| t <sub>STOZ</sub>    | Falling Edge of CCLK to SOSPI Disable                        |      | 20       | ns     |

| t <sub>STSU</sub>    | Data Setup Time (SISPI)                                      | 8    | —        | ns     |

| t <sub>STH</sub>     | Data Hold Time (SISPI)                                       | 10   | —        | ns     |

| t <sub>STCKH</sub>   | CCLK Clock Pulse Width, High                                 | 0.02 | 200      | μs     |

| t <sub>STCKL</sub>   | CCLK Clock Pulse Width, Low                                  | 0.02 | 200      | μs     |

| t <sub>STVO</sub>    | Falling Edge of CCLK to Valid SOSPI Output                   | _    | 20       | ns     |

| t <sub>SCS</sub>     | CSSPISN High Time                                            | 25   | —        | ns     |

| t <sub>SCSS</sub>    | CSSPISN Setup Time                                           | 25   | -        | ns     |

| t <sub>SCSH</sub>    | CSSPISN Hold Time                                            | 25   | —        | ns     |

## **Over Recommended Operating Conditions**

1. Re-toggling the PROGRAMN pin is not permitted until the INITN pin is high. Avoid consecutive toggling of PROGRAMN.

## On-Chip Oscillator and Configuration Master Clock Characteristics

| Parameter              | Min.                | Units               |     |

|------------------------|---------------------|---------------------|-----|

| Master Clock Frequency | Selected value -30% | Selected value +30% | MHz |

| Duty Cycle             | 40                  | 60                  | %   |

## **Over Recommended Operating Conditions**

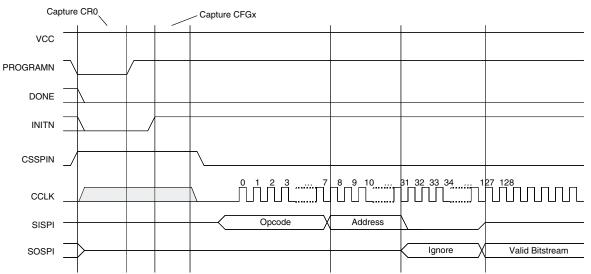

## Figure 3-9. Master SPI Configuration Waveforms

## **Switching Test Conditions**

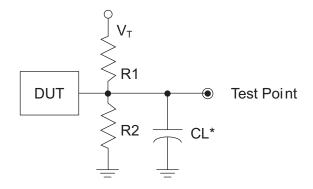

Figure 3-11 shows the output test load that is used for AC testing. The specific values for resistance, capacitance, voltage, and other test conditions are shown in Table 3-6.

## Figure 3-11. Output Test Load, LVTTL and LVCMOS Standards

\*CL Includes Test Fixture and Probe Capacitance

Table 3-6. Test Fixture Required Components, Non-Terminated Interfaces

| Test Condition                                   | R <sub>1</sub> | R <sub>2</sub> | CL  | Timing Ref.                       | V <sub>T</sub>    |

|--------------------------------------------------|----------------|----------------|-----|-----------------------------------|-------------------|

|                                                  |                |                |     | LVCMOS 3.3 = 1.5V                 | —                 |

|                                                  |                |                |     | LVCMOS 2.5 = $V_{CCIO}/2$         | —                 |

| LVTTL and other LVCMOS settings (L -> H, H -> L) | $\infty$       | $\infty$       | 0pF | LVCMOS 1.8 = V <sub>CCIO</sub> /2 | —                 |

|                                                  |                |                |     | LVCMOS 1.5 = $V_{CCIO}/2$         | —                 |

|                                                  |                |                |     | LVCMOS 1.2 = V <sub>CCIO</sub> /2 | —                 |

| LVCMOS 2.5 I/O (Z -> H)                          | $\infty$       | 1MΩ            |     | V <sub>CCIO</sub> /2              |                   |

| LVCMOS 2.5 I/O (Z -> L)                          | 1MΩ            | $\infty$       |     | V <sub>CCIO</sub> /2              | V <sub>CCIO</sub> |

| LVCMOS 2.5 I/O (H -> Z)                          | $\infty$       | 100            |     | V <sub>OH</sub> - 0.10            | —                 |

| LVCMOS 2.5 I/O (L -> Z)                          | 100            | $\infty$       |     | V <sub>OL</sub> + 0.10            | V <sub>CCIO</sub> |

Note: Output test conditions for all other interfaces are determined by the respective standards.

# LatticeXP2 Family Data Sheet Pinout Information

#### February 2012

Data Sheet DS1009

| Signal Name                               | I/O     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General Purpose                           |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                           |         | [Edge] indicates the edge of the device on which the pad is located. Valid edge designations are L (Left), B (Bottom), R (Right), T (Top).                                                                                                                                                                                                                                                                                                                                                             |

| P[Edge] [Row/Column Number*]_[A/B]        | I/O     | [Row/Column Number] indicates the PFU row or the column of the device on which the PIC exists. When Edge is T (Top) or B (Bottom), only need to specify Row Number. When Edge is L (Left) or R (Right), only need to specify Column Number.                                                                                                                                                                                                                                                            |

|                                           |         | [A/B] indicates the PIO within the PIC to which the pad is connected. Some of these user-programmable pins are shared with special function pins. These pins, when not used as special purpose pins, can be programmed as I/Os for user logic. During configuration the user-programmable I/Os are tri-stated with an internal pull-up resistor enabled. If any pin is not used (or not bonded to a package pin), it is also tri-stated with an internal pull-up resistor enabled after configuration. |

| GSRN                                      | I       | Global RESET signal (active low). Any I/O pin can be GSRN.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| NC                                        | —       | No connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| GND                                       | _       | Ground. Dedicated pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| V <sub>CC</sub>                           | —       | Power supply pins for core logic. Dedicated pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| V <sub>CCAUX</sub>                        | _       | Auxiliary power supply pin. This dedicated pin powers all the differential and referenced input buffers.                                                                                                                                                                                                                                                                                                                                                                                               |

| V <sub>CCPLL</sub>                        | —       | PLL supply pins. csBGA, PQFP and TQFP packages only.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| V <sub>CCIOx</sub>                        | _       | Dedicated power supply pins for I/O bank x.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| V <sub>REF1_x</sub> , V <sub>REF2_x</sub> | —       | Reference supply pins for I/O bank x. Pre-determined pins in each bank are assigned as $V_{\text{REF}}$ inputs. When not used, they may be used as I/O pins.                                                                                                                                                                                                                                                                                                                                           |

|                                           | er prog | rammable I/O pins when not in use for PLL or clock pins)                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| [LOC][num]_V <sub>CCPLL</sub>             | —       | Power supply pin for PLL: LLC, LRC, URC, ULC, num = row from center.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| [LOC][num]_GPLL[T, C]_IN_A                | I       | General Purpose PLL (GPLL) input pads: LLC, LRC, URC, ULC, num = row from center, $T =$ true and $C =$ complement, index A,B,Cat each side.                                                                                                                                                                                                                                                                                                                                                            |

| [LOC][num]_GPLL[T, C]_FB_A                | I       | Optional feedback GPLL input pads: LLC, LRC, URC, ULC, num = row from center, $T =$ true and C = complement, index A,B,Cat each side.                                                                                                                                                                                                                                                                                                                                                                  |

| PCLK[T, C]_[n:0]_[3:0]                    | I       | Primary Clock pads, T = true and C = complement, n per side, indexed by bank and $0,1,2,3$ within bank.                                                                                                                                                                                                                                                                                                                                                                                                |

| [LOC]DQS[num]                             | I       | DQS input pads: T (Top), R (Right), B (Bottom), L (Left), DQS, num = ball function number. Any pad can be configured to be output.                                                                                                                                                                                                                                                                                                                                                                     |

| Test and Programming (Dedicated Pi        | ns)     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| TMS                                       | I       | Test Mode Select input, used to control the 1149.1 state machine. Pull-up is enabled during configuration.                                                                                                                                                                                                                                                                                                                                                                                             |

| тск                                       | I       | Test Clock input pin, used to clock the 1149.1 state machine. No pull-up enabled.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ты                                        | I       | Test Data in pin. Used to load data into device using 1149.1 state machine.<br>After power-up, this TAP port can be activated for configuration by sending<br>appropriate command. (Note: once a configuration port is selected it is<br>locked. Another configuration port cannot be selected until the power-up                                                                                                                                                                                      |

# © 2012 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

sequence). Pull-up is enabled during configuration.

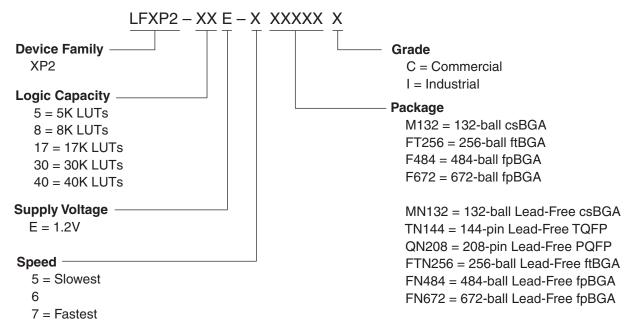

# LatticeXP2 Family Data Sheet Ordering Information

#### February 2012

Data Sheet DS1009

## **Part Number Description**

## **Ordering Information**

The LatticeXP2 devices are marked with a single temperature grade, either Commercial or Industrial, as shown below.

© 2012 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Part Number        | Voltage | Grade | Package         | Pins | Temp. | LUTs (k) |

|--------------------|---------|-------|-----------------|------|-------|----------|

| LFXP2-30E-5FTN256C | 1.2V    | -5    | Lead-Free ftBGA | 256  | COM   | 30       |

| LFXP2-30E-6FTN256C | 1.2V    | -6    | Lead-Free ftBGA | 256  | COM   | 30       |

| LFXP2-30E-7FTN256C | 1.2V    | -7    | Lead-Free ftBGA | 256  | COM   | 30       |

| LFXP2-30E-5FN484C  | 1.2V    | -5    | Lead-Free fpBGA | 484  | COM   | 30       |

| LFXP2-30E-6FN484C  | 1.2V    | -6    | Lead-Free fpBGA | 484  | COM   | 30       |

| LFXP2-30E-7FN484C  | 1.2V    | -7    | Lead-Free fpBGA | 484  | COM   | 30       |

| LFXP2-30E-5FN672C  | 1.2V    | -5    | Lead-Free fpBGA | 672  | COM   | 30       |

| LFXP2-30E-6FN672C  | 1.2V    | -6    | Lead-Free fpBGA | 672  | COM   | 30       |

| LFXP2-30E-7FN672C  | 1.2V    | -7    | Lead-Free fpBGA | 672  | COM   | 30       |

| Part Number       | Voltage | Grade | Package         | Pins | Temp. | LUTs (k) |

|-------------------|---------|-------|-----------------|------|-------|----------|

| LFXP2-40E-5FN484C | 1.2V    | -5    | Lead-Free fpBGA | 484  | COM   | 40       |

| LFXP2-40E-6FN484C | 1.2V    | -6    | Lead-Free fpBGA | 484  | COM   | 40       |

| LFXP2-40E-7FN484C | 1.2V    | -7    | Lead-Free fpBGA | 484  | COM   | 40       |

| LFXP2-40E-5FN672C | 1.2V    | -5    | Lead-Free fpBGA | 672  | COM   | 40       |

| LFXP2-40E-6FN672C | 1.2V    | -6    | Lead-Free fpBGA | 672  | COM   | 40       |

| LFXP2-40E-7FN672C | 1.2V    | -7    | Lead-Free fpBGA | 672  | COM   | 40       |

## Industrial

| Part Number       | Voltage | Grade | Package         | Pins | Temp. | LUTs (k) |

|-------------------|---------|-------|-----------------|------|-------|----------|

| LFXP2-5E-5MN132I  | 1.2V    | -5    | Lead-Free csBGA | 132  | IND   | 5        |

| LFXP2-5E-6MN132I  | 1.2V    | -6    | Lead-Free csBGA | 132  | IND   | 5        |

| LFXP2-5E-5TN144I  | 1.2V    | -5    | Lead-Free TQFP  | 144  | IND   | 5        |

| LFXP2-5E-6TN144I  | 1.2V    | -6    | Lead-Free TQFP  | 144  | IND   | 5        |

| LFXP2-5E-5QN208I  | 1.2V    | -5    | Lead-Free PQFP  | 208  | IND   | 5        |

| LFXP2-5E-6QN208I  | 1.2V    | -6    | Lead-Free PQFP  | 208  | IND   | 5        |

| LFXP2-5E-5FTN256I | 1.2V    | -5    | Lead-Free ftBGA | 256  | IND   | 5        |

| LFXP2-5E-6FTN256I | 1.2V    | -6    | Lead-Free ftBGA | 256  | IND   | 5        |

| Part Number       | Voltage | Grade | Package         | Pins | Temp. | LUTs (k) |

|-------------------|---------|-------|-----------------|------|-------|----------|

| LFXP2-8E-5MN132I  | 1.2V    | -5    | Lead-Free csBGA | 132  | IND   | 8        |

| LFXP2-8E-6MN132I  | 1.2V    | -6    | Lead-Free csBGA | 132  | IND   | 8        |

| LFXP2-8E-5TN144I  | 1.2V    | -5    | Lead-Free TQFP  | 144  | IND   | 8        |

| LFXP2-8E-6TN144I  | 1.2V    | -6    | Lead-Free TQFP  | 144  | IND   | 8        |

| LFXP2-8E-5QN208I  | 1.2V    | -5    | Lead-Free PQFP  | 208  | IND   | 8        |

| LFXP2-8E-6QN208I  | 1.2V    | -6    | Lead-Free PQFP  | 208  | IND   | 8        |

| LFXP2-8E-5FTN256I | 1.2V    | -5    | Lead-Free ftBGA | 256  | IND   | 8        |

| LFXP2-8E-6FTN256I | 1.2V    | -6    | Lead-Free ftBGA | 256  | IND   | 8        |

## **Conventional Packaging**

| Part Number      | Voltage | Grade | Package | Pins | Temp. | LUTs (k) |

|------------------|---------|-------|---------|------|-------|----------|

| LFXP2-5E-5M132C  | 1.2V    | -5    | csBGA   | 132  | COM   | 5        |

| LFXP2-5E-6M132C  | 1.2V    | -6    | csBGA   | 132  | COM   | 5        |

| LFXP2-5E-7M132C  | 1.2V    | -7    | csBGA   | 132  | COM   | 5        |

| LFXP2-5E-5FT256C | 1.2V    | -5    | ftBGA   | 256  | COM   | 5        |

| LFXP2-5E-6FT256C | 1.2V    | -6    | ftBGA   | 256  | COM   | 5        |

| LFXP2-5E-7FT256C | 1.2V    | -7    | ftBGA   | 256  | COM   | 5        |

Commercial

| Part Number      | Voltage | Grade | Package | Pins | Temp. | LUTs (k) |

|------------------|---------|-------|---------|------|-------|----------|

| LFXP2-8E-5M132C  | 1.2V    | -5    | csBGA   | 132  | COM   | 8        |

| LFXP2-8E-6M132C  | 1.2V    | -6    | csBGA   | 132  | COM   | 8        |

| LFXP2-8E-7M132C  | 1.2V    | -7    | csBGA   | 132  | COM   | 8        |

| LFXP2-8E-5FT256C | 1.2V    | -5    | ftBGA   | 256  | COM   | 8        |

| LFXP2-8E-6FT256C | 1.2V    | -6    | ftBGA   | 256  | COM   | 8        |

| LFXP2-8E-7FT256C | 1.2V    | -7    | ftBGA   | 256  | COM   | 8        |

| Part Number       | Voltage | Grade | Package | Pins | Temp. | LUTs (k) |

|-------------------|---------|-------|---------|------|-------|----------|

| LFXP2-17E-5FT256C | 1.2V    | -5    | ftBGA   | 256  | COM   | 17       |

| LFXP2-17E-6FT256C | 1.2V    | -6    | ftBGA   | 256  | COM   | 17       |

| LFXP2-17E-7FT256C | 1.2V    | -7    | ftBGA   | 256  | COM   | 17       |

| LFXP2-17E-5F484C  | 1.2V    | -5    | fpBGA   | 484  | COM   | 17       |

| LFXP2-17E-6F484C  | 1.2V    | -6    | fpBGA   | 484  | COM   | 17       |

| LFXP2-17E-7F484C  | 1.2V    | -7    | fpBGA   | 484  | COM   | 17       |

| Part Number       | Voltage | Grade | Package | Pins | Temp. | LUTs (k) |

|-------------------|---------|-------|---------|------|-------|----------|

| LFXP2-30E-5FT256C | 1.2V    | -5    | ftBGA   | 256  | COM   | 30       |

| LFXP2-30E-6FT256C | 1.2V    | -6    | ftBGA   | 256  | COM   | 30       |

| LFXP2-30E-7FT256C | 1.2V    | -7    | ftBGA   | 256  | COM   | 30       |

| LFXP2-30E-5F484C  | 1.2V    | -5    | fpBGA   | 484  | COM   | 30       |

| LFXP2-30E-6F484C  | 1.2V    | -6    | fpBGA   | 484  | COM   | 30       |

| LFXP2-30E-7F484C  | 1.2V    | -7    | fpBGA   | 484  | COM   | 30       |

| LFXP2-30E-5F672C  | 1.2V    | -5    | fpBGA   | 672  | COM   | 30       |

| LFXP2-30E-6F672C  | 1.2V    | -6    | fpBGA   | 672  | COM   | 30       |

| LFXP2-30E-7F672C  | 1.2V    | -7    | fpBGA   | 672  | COM   | 30       |

# LatticeXP2 Family Data Sheet Revision History

September 2014

Data Sheet DS1009

## **Revision History**

|                | Version | Section                                                                                                                                                                                                           | Change Summary                                                                                                                                                                                                                                                     |

|----------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| May 2007       | 01.1    |                                                                                                                                                                                                                   | Initial release.                                                                                                                                                                                                                                                   |

| September 2007 | 01.2    | DC and Switching<br>Characteristics                                                                                                                                                                               | Added JTAG Port Timing Waveforms diagram.                                                                                                                                                                                                                          |

|                |         |                                                                                                                                                                                                                   | Updated sysCLOCK PLL Timing table.                                                                                                                                                                                                                                 |

|                |         | Pinout Information                                                                                                                                                                                                | Added Thermal Management text section.                                                                                                                                                                                                                             |

| February 2008  | 01.3    | Architecture                                                                                                                                                                                                      | Added LVCMOS33D to Supported Output Standards table.                                                                                                                                                                                                               |

|                |         | Clarified: "This Flash can be programmed through either the JTAG or<br>Slave SPI ports of the device. The SRAM configuration space can also<br>be infinitely reconfigured through the JTAG and Master SPI ports." |                                                                                                                                                                                                                                                                    |

|                |         |                                                                                                                                                                                                                   | Added External Slave SPI Port to Serial TAG Memory section. Updated Serial TAG Memory diagram.                                                                                                                                                                     |

|                |         | DC and Switching<br>Characteristics                                                                                                                                                                               | Updated Flash Programming Specifications table.                                                                                                                                                                                                                    |

|                |         |                                                                                                                                                                                                                   | Added "8W" specification to Hot Socketing Specifications table.                                                                                                                                                                                                    |

|                |         |                                                                                                                                                                                                                   | Updated Timing Tables                                                                                                                                                                                                                                              |

|                |         |                                                                                                                                                                                                                   | Clarifications for IIH in DC Electrical Characteristics table.                                                                                                                                                                                                     |

|                |         |                                                                                                                                                                                                                   | Added LVCMOS33D section                                                                                                                                                                                                                                            |

|                |         |                                                                                                                                                                                                                   | Updated DOA and DOA (Regs) to EBR Timing diagrams.                                                                                                                                                                                                                 |

|                |         |                                                                                                                                                                                                                   | Removed Master Clock Frequency and Duty Cycle sections from the LatticeXP2 sysCONFIG Port Timing Specifications table. These are listed on the On-chip Oscillator and Configuration Master Clock Characteristics table.                                            |

|                |         |                                                                                                                                                                                                                   | Changed CSSPIN to CSSPISN in description of $t_{SCS},t_{SCSS},$ and $t_{SCSH}$ parameters. Removed $t_{SOE}$ parameter.                                                                                                                                            |

|                |         |                                                                                                                                                                                                                   | Clarified On-chip Oscillator documentation                                                                                                                                                                                                                         |

|                |         |                                                                                                                                                                                                                   | Added Switching Test Conditions                                                                                                                                                                                                                                    |

|                |         | Pinout Information                                                                                                                                                                                                | Added "True LVDS Pairs Bonding Out per Bank," "DDR Banks Bonding<br>Out per I/O Bank," and "PCI capable I/Os Bonding Out per Bank" to Pin<br>Information Summary in place of previous blank table "PCI and DDR<br>Capabilities of the Device-Package Combinations" |

|                |         |                                                                                                                                                                                                                   | Removed pinout listing. This information is available on the LatticeXP2 product web pages                                                                                                                                                                          |

|                |         | Ordering Information                                                                                                                                                                                              | Added XP2-17 "8W" and all other family OPNs.                                                                                                                                                                                                                       |

| April 2008     | 01.4    | DC and Switching                                                                                                                                                                                                  | Updated Absolute Maximum Ratings footnotes.                                                                                                                                                                                                                        |

|                |         | Characteristics                                                                                                                                                                                                   | Updated Recommended Operating Conditions Table footnotes.                                                                                                                                                                                                          |

|                |         |                                                                                                                                                                                                                   | Updated Supply Current (Standby) Table                                                                                                                                                                                                                             |

|                |         |                                                                                                                                                                                                                   | Updated Initialization Supply Current Table                                                                                                                                                                                                                        |

|                |         |                                                                                                                                                                                                                   | Updated Programming and Erase Flash Supply Current Table                                                                                                                                                                                                           |

|                |         |                                                                                                                                                                                                                   | Updated Register to Register Performance Table                                                                                                                                                                                                                     |

|                |         |                                                                                                                                                                                                                   | Updated LatticeXP2 External Switching Characteristics Table                                                                                                                                                                                                        |

|                |         |                                                                                                                                                                                                                   | Updated LatticeXP2 Internal Switching Characteristics Table                                                                                                                                                                                                        |

|                |         |                                                                                                                                                                                                                   | Updated sysCLOCK PLL Timing Table                                                                                                                                                                                                                                  |

© 2014 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.