Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                            |

|--------------------------------|----------------------------------------------------------------------------|

| Product Status                 | Obsolete                                                                   |

| Number of LABs/CLBs            | 625                                                                        |

| Number of Logic Elements/Cells | 5000                                                                       |

| Total RAM Bits                 | 169984                                                                     |

| Number of I/O                  | 86                                                                         |

| Number of Gates                |                                                                            |

| Voltage - Supply               | 1.14V ~ 1.26V                                                              |

| Mounting Type                  | Surface Mount                                                              |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                         |

| Package / Case                 | 132-LFBGA, CSPBGA                                                          |

| Supplier Device Package        | 132-CSBGA (8x8)                                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfxp2-5e-5m132i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

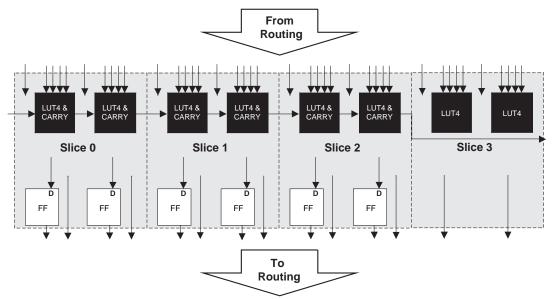

## Figure 2-2. PFU Diagram

## Slice

Slice 0 through Slice 2 contain two 4-input combinatorial Look-Up Tables (LUT4), which feed two registers. Slice 3 contains two LUT4s and no registers. For PFUs, Slice 0 and Slice 2 can also be configured as distributed memory, a capability not available in PFF blocks. Table 2-1 shows the capability of the slices in both PFF and PFU blocks along with the operation modes they enable. In addition, each PFU contains logic that allows the LUTs to be combined to perform functions such as LUT5, LUT6, LUT7 and LUT8. There is control logic to perform set/reset functions (programmable as synchronous/asynchronous), clock select, chip-select and wider RAM/ROM functions. Figure 2-3 shows an overview of the internal logic of the slice. The registers in the slice can be configured as positive/negative edge triggered or level sensitive clocks.

| Table 2-1. | Resources | and Modes | Available    | per Slice |

|------------|-----------|-----------|--------------|-----------|

|            |           |           | / IT analoio |           |

|         | PFU BLock               |                         | PFF Block               |                    |  |

|---------|-------------------------|-------------------------|-------------------------|--------------------|--|

| Slice   | Resources               | Modes                   | Resources               | Modes              |  |

| Slice 0 | 2 LUT4s and 2 Registers | Logic, Ripple, RAM, ROM | 2 LUT4s and 2 Registers | Logic, Ripple, ROM |  |

| Slice 1 | 2 LUT4s and 2 Registers | Logic, Ripple, ROM      | 2 LUT4s and 2 Registers | Logic, Ripple, ROM |  |

| Slice 2 | 2 LUT4s and 2 Registers | Logic, Ripple, RAM, ROM | 2 LUT4s and 2 Registers | Logic, Ripple, ROM |  |

| Slice 3 | 2 LUT4s                 | Logic, ROM              | 2 LUT4s                 | Logic, ROM         |  |

Slice 0 through Slice 2 have 14 input signals: 13 signals from routing and one from the carry-chain (from the adjacent slice or PFU). There are seven outputs: six to routing and one to carry-chain (to the adjacent PFU). Slice 3 has 13 input signals from routing and four signals to routing. Table 2-2 lists the signals associated with Slice 0 to Slice 2.

## Modes of Operation

Each slice has up to four potential modes of operation: Logic, Ripple, RAM and ROM.

#### Logic Mode

In this mode, the LUTs in each slice are configured as LUT4s. A LUT4 has 16 possible input combinations. Fourinput logic functions are generated by programming the LUT4. Since there are two LUT4s per slice, a LUT5 can be constructed within one slice. Larger LUTs such as LUT6, LUT7 and LUT8, can be constructed by concatenating two or more slices. Note that a LUT8 requires more than four slices.

#### **Ripple Mode**

Ripple mode allows efficient implementation of small arithmetic functions. In ripple mode, the following functions can be implemented by each slice:

- Addition 2-bit

- Subtraction 2-bit

- Add/Subtract 2-bit using dynamic control

- Up counter 2-bit

- Down counter 2-bit

- Up/Down counter with async clear

- Up/Down counter with preload (sync)

- Ripple mode multiplier building block

- Multiplier support

- Comparator functions of A and B inputs

- A greater-than-or-equal-to B

- A not-equal-to B

- A less-than-or-equal-to B

Two carry signals, FCI and FCO, are generated per slice in this mode, allowing fast arithmetic functions to be constructed by concatenating slices.

#### RAM Mode

In this mode, a 16x4-bit distributed Single Port RAM (SPR) can be constructed using each LUT block in Slice 0 and Slice 2 as a 16x1-bit memory. Slice 1 is used to provide memory address and control signals. A 16x2-bit Pseudo Dual Port RAM (PDPR) memory is created by using one slice as the read-write port and the other companion slice as the read-only port.

The Lattice design tools support the creation of a variety of different size memories. Where appropriate, the software will construct these using distributed memory primitives that represent the capabilities of the PFU. Table 2-3 shows the number of slices required to implement different distributed RAM primitives. For more information on using RAM in LatticeXP2 devices, please see TN1137, <u>LatticeXP2 Memory Usage Guide</u>.

#### Table 2-3. Number of Slices Required For Implementing Distributed RAM

|                  | SPR 16X4 | PDPR 16X4 |

|------------------|----------|-----------|

| Number of slices | 3        | 3         |

Note: SPR = Single Port RAM, PDPR = Pseudo Dual Port RAM

#### **ROM Mode**

ROM mode uses the LUT logic; hence, Slices 0 through 3 can be used in the ROM mode. Preloading is accomplished through the programming interface during PFU configuration.

# Routing

There are many resources provided in the LatticeXP2 devices to route signals individually or as busses with related control signals. The routing resources consist of switching circuitry, buffers and metal interconnect (routing) segments.

The inter-PFU connections are made with x1 (spans two PFU), x2 (spans three PFU) or x6 (spans seven PFU) connections. The x1 and x2 connections provide fast and efficient connections in horizontal and vertical directions. The x2 and x6 resources are buffered to allow both short and long connections routing between PFUs.

The LatticeXP2 family has an enhanced routing architecture to produce a compact design. The Diamond design tool takes the output of the synthesis tool and places and routes the design. Generally, the place and route tool is completely automatic, although an interactive routing editor is available to optimize the design.

# sysCLOCK Phase Locked Loops (PLL)

The sysCLOCK PLLs provide the ability to synthesize clock frequencies. The LatticeXP2 family supports between two and four full featured General Purpose PLLs (GPLL). The architecture of the GPLL is shown in Figure 2-4.

CLKI, the PLL reference frequency, is provided either from the pin or from routing; it feeds into the Input Clock Divider block. CLKFB, the feedback signal, is generated from CLKOP (the primary clock output) or from a user clock pin/logic. CLKFB feeds into the Feedback Divider and is used to multiply the reference frequency.

Both the input path and feedback signals enter the Voltage Controlled Oscillator (VCO) block. The phase and frequency of the VCO are determined from the input path and feedback signals. A LOCK signal is generated by the VCO to indicate that the VCO is locked with the input clock signal.

The output of the VCO feeds into the CLKOP Divider, a post-scalar divider. The duty cycle of the CLKOP Divider output can be fine tuned using the Duty Trim block, which creates the CLKOP signal. By allowing the VCO to operate at higher frequencies than CLKOP, the frequency range of the GPLL is expanded. The output of the CLKOP Divider is passed through the CLKOK Divider, a secondary clock divider, to generate lower frequencies for the CLKOK output. For applications that require even lower frequencies, the CLKOP signal is passed through a divide-by-three divider to produce the CLKOK2 output. The CLKOK2 output is provided for applications that use source synchronous logic. The Phase/Duty Cycle/Duty Trim block is used to adjust the phase and duty cycle of the CLKOP Divider output to generate the CLKOS signal. The phase/duty cycle setting can be pre-programmed or dynamically adjusted.

The clock outputs from the GPLL; CLKOP, CLKOK, CLKOK2 and CLKOS, are fed to the clock distribution network.

For further information on the GPLL please see TN1126, LatticeXP2 sysCLOCK PLL Design and Usage Guide.

## Primary Clock Routing

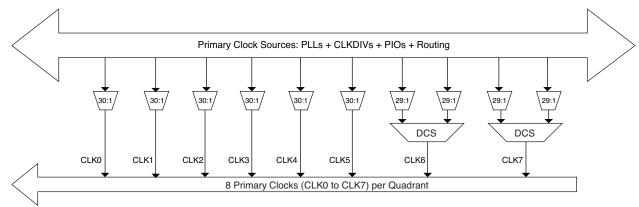

The clock routing structure in LatticeXP2 devices consists of a network of eight primary clock lines (CLK0 through CLK7) per quadrant. The primary clocks of each quadrant are generated from muxes located in the center of the device. All the clock sources are connected to these muxes. Figure 2-9 shows the clock routing for one quadrant. Each quadrant mux is identical. If desired, any clock can be routed globally.

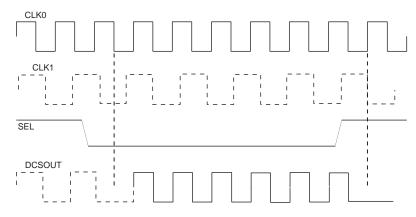

## **Dynamic Clock Select (DCS)**

The DCS is a smart multiplexer function available in the primary clock routing. It switches between two independent input clock sources without any glitches or runt pulses. This is achieved irrespective of when the select signal is toggled. There are two DCS blocks per quadrant; in total, eight DCS blocks per device. The inputs to the DCS block come from the center muxes. The output of the DCS is connected to primary clocks CLK6 and CLK7 (see Figure 2-9).

Figure 2-10 shows the timing waveforms of the default DCS operating mode. The DCS block can be programmed to other modes. For more information on the DCS, please see TN1126, <u>LatticeXP2 sysCLOCK PLL Design and</u> <u>Usage Guide</u>.

#### Figure 2-10. DCS Waveforms

## Secondary Clock/Control Routing

Secondary clocks in the LatticeXP2 devices are region-based resources. The benefit of region-based resources is the relatively low injection delay and skew within the region, as compared to primary clocks. EBR rows, DSP rows and a special vertical routing channel bound the secondary clock regions. This special vertical routing channel aligns with either the left edge of the center DSP block in the DSP row or the center of the DSP row. Figure 2-11 shows this special vertical routing channel and the eight secondary clock regions for the LatticeXP2-40.

For further information on the sysMEM EBR block, please see TN1137, LatticeXP2 Memory Usage Guide.

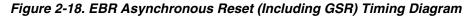

## **EBR Asynchronous Reset**

EBR asynchronous reset or GSR (if used) can only be applied if all clock enables are low for a clock cycle before the reset is applied and released a clock cycle after the low-to-high transition of the reset signal, as shown in Figure 2-18. The GSR input to the EBR is always asynchronous.

| Reset                  |  |

|------------------------|--|

| Clock                  |  |

| Clock ——————<br>Enable |  |

If all clock enables remain enabled, the EBR asynchronous reset or GSR may only be applied and released after the EBR read and write clock inputs are in a steady state condition for a minimum of 1/f<sub>MAX</sub> (EBR clock). The reset release must adhere to the EBR synchronous reset setup time before the next active read or write clock edge.

If an EBR is pre-loaded during configuration, the GSR input must be disabled or the release of the GSR during device Wake Up must occur before the release of the device I/Os becoming active.

These instructions apply to all EBR RAM and ROM implementations.

Note that there are no reset restrictions if the EBR synchronous reset is used and the EBR GSR input is disabled.

## sysDSP™ Block

The LatticeXP2 family provides a sysDSP block making it ideally suited for low cost, high performance Digital Signal Processing (DSP) applications. Typical functions used in these applications include Bit Correlators, Fast Fourier Transform (FFT) functions, Finite Impulse Response (FIR) Filter, Reed-Solomon Encoder/Decoder, Turbo Encoder/ Decoder and Convolutional Encoder/Decoder. These complex signal processing functions use similar building blocks such as multiply-adders and multiply-accumulators.

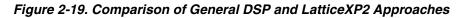

## sysDSP Block Approach Compare to General DSP

Conventional general-purpose DSP chips typically contain one to four (Multiply and Accumulate) MAC units with fixed data-width multipliers; this leads to limited parallelism and limited throughput. Their throughput is increased by higher clock speeds. The LatticeXP2 family, on the other hand, has many DSP blocks that support different data-widths. This allows the designer to use highly parallel implementations of DSP functions. The designer can optimize the DSP performance vs. area by choosing appropriate levels of parallelism. Figure 2-19 compares the fully serial and the mixed parallel and serial implementations.

## sysDSP Block Capabilities

The sysDSP block in the LatticeXP2 family supports four functional elements in three 9, 18 and 36 data path widths. The user selects a function element for a DSP block and then selects the width and type (signed/unsigned) of its operands. The operands in the LatticeXP2 family sysDSP Blocks can be either signed or unsigned but not mixed within a function element. Similarly, the operand widths cannot be mixed within a block. DSP elements can be concatenated.

The resources in each sysDSP block can be configured to support the following four elements:

- MULT (Multiply)

- MAC (Multiply, Accumulate)

- MULTADDSUB (Multiply, Addition/Subtraction)

- MULTADDSUBSUM (Multiply, Addition/Subtraction, Accumulate)

The number of elements available in each block depends on the width selected from the three available options: x9, x18, and x36. A number of these elements are concatenated for highly parallel implementations of DSP functions. Table 2-6 shows the capabilities of the block.

| Table 2-6. Maximum Number of Elements in a Block |  |

|--------------------------------------------------|--|

|--------------------------------------------------|--|

| Width of Multiply | x9 | x18 | x36 |

|-------------------|----|-----|-----|

| MULT              | 8  | 4   | 1   |

| MAC               | 2  | 2   | —   |

| MULTADDSUB        | 4  | 2   | —   |

| MULTADDSUBSUM     | 2  | 1   | —   |

Some options are available in four elements. The input register in all the elements can be directly loaded or can be loaded as shift register from previous operand registers. By selecting 'dynamic operation' the following operations are possible:

register. Similarly, CE and RST are selected from their four respective sources (CE0, CE1, CE2, CE3 and RST0, RST1, RST2, RST3) at each input register, pipeline register and output register.

### Signed and Unsigned with Different Widths

The DSP block supports other widths, in addition to x9, x18 and x36 widths, of signed and unsigned multipliers. For unsigned operands, unused upper data bits should be filled to create a valid x9, x18 or x36 operand. For signed two's complement operands, sign extension of the most significant bit should be performed until x9, x18 or x36 width is reached. Table 2-7 provides an example of this.

#### Table 2-7. Sign Extension Example

| Number | Unsigned | Unsigned<br>9-bit | Unsigned<br>18-bit | Signed | Two's Complement<br>Signed 9 Bits | Two's Complement<br>Signed 18 Bits |

|--------|----------|-------------------|--------------------|--------|-----------------------------------|------------------------------------|

| +5     | 0101     | 000000101         | 00000000000000101  | 0101   | 00000101                          | 00000000000000101                  |

| -6     | N/A      | N/A               | N/A                | 1010   | 111111010                         | 1111111111111111010                |

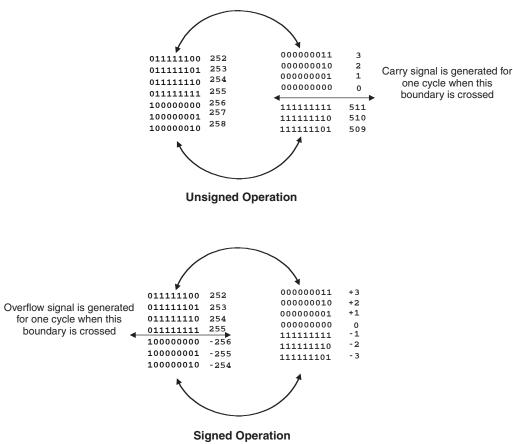

## **OVERFLOW Flag from MAC**

The sysDSP block provides an overflow output to indicate that the accumulator has overflowed. "Roll-over" occurs and an overflow signal is indicated when any of the following is true: two unsigned numbers are added and the result is a smaller number than the accumulator, two positive numbers are added with a negative sum or two negative numbers are added with a positive sum. Note that when overflow occurs the overflow flag is present for only one cycle. By counting these overflow pulses in FPGA logic, larger accumulators can be constructed. The conditions for the overflow signal for signed and unsigned operands are listed in Figure 2-24.

#### Figure 2-24. Accumulator Overflow/Underflow

### **IPexpress**<sup>™</sup>

The user can access the sysDSP block via the Lattice IPexpress tool, which provides the option to configure each DSP module (or group of modules), or by direct HDL instantiation. In addition, Lattice has partnered with The Math-Works<sup>®</sup> to support instantiation in the Simulink<sup>®</sup> tool, a graphical simulation environment. Simulink works with Diamond to dramatically shorten the DSP design cycle in Lattice FPGAs.

## **Optimized DSP Functions**

Lattice provides a library of optimized DSP IP functions. Some of the IP cores planned for the LatticeXP2 DSP include the Bit Correlator, FFT functions, FIR Filter, Reed-Solomon Encoder/Decoder, Turbo Encoder/Decoder and Convolutional Encoder/Decoder. Please contact Lattice to obtain the latest list of available DSP IP cores.

## **Resources Available in the LatticeXP2 Family**

Table 2-8 shows the maximum number of multipliers for each member of the LatticeXP2 family. Table 2-9 shows the maximum available EBR RAM Blocks and Serial TAG Memory bits in each LatticeXP2 device. EBR blocks, together with Distributed RAM can be used to store variables locally for fast DSP operations.

| Device | DSP Block | 9x9 Multiplier | 18x18 Multiplier | 36x36 Multiplier |

|--------|-----------|----------------|------------------|------------------|

| XP2-5  | 3         | 24             | 12               | 3                |

| XP2-8  | 4         | 32             | 16               | 4                |

| XP2-17 | 5         | 40             | 20               | 5                |

| XP2-30 | 7         | 56             | 28               | 7                |

| XP2-40 | 8         | 64             | 32               | 8                |

#### Table 2-8. Maximum Number of DSP Blocks in the LatticeXP2 Family

| Device | EBR SRAM Block | Total EBR SRAM<br>(Kbits) | TAG Memory<br>(Bits) |

|--------|----------------|---------------------------|----------------------|

| XP2-5  | 9              | 166                       | 632                  |

| XP2-8  | 12             | 221                       | 768                  |

| XP2-17 | 15             | 276                       | 2184                 |

| XP2-30 | 21             | 387                       | 2640                 |

| XP2-40 | 48             | 885                       | 3384                 |

## LatticeXP2 DSP Performance

Table 2-10 lists the maximum performance in Millions of MAC (MMAC) operations per second for each member of the LatticeXP2 family.

#### Table 2-10. DSP Performance

| Device | DSP Block | DSP Performance<br>MMAC |

|--------|-----------|-------------------------|

| XP2-5  | 3         | 3,900                   |

| XP2-8  | 4         | 5,200                   |

| XP2-17 | 5         | 6,500                   |

| XP2-30 | 7         | 9,100                   |

| XP2-40 | 8         | 10,400                  |

For further information on the sysDSP block, please see TN1140, <u>LatticeXP2 sysDSP Usage Guide</u>.

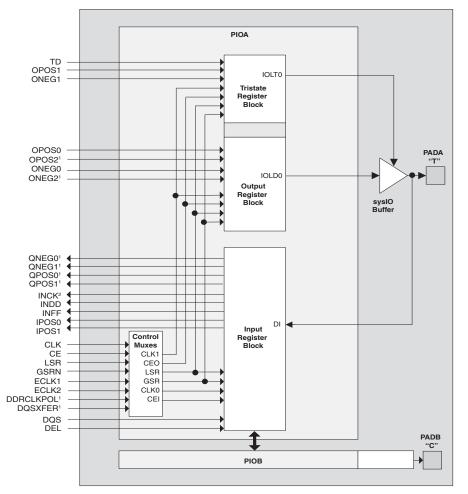

# Programmable I/O Cells (PIC)

Each PIC contains two PIOs connected to their respective sysIO buffers as shown in Figure 2-25. The PIO Block supplies the output data (DO) and the tri-state control signal (TO) to the sysIO buffer and receives input from the buffer. Table 2-11 provides the PIO signal list.

#### Figure 2-25. PIC Diagram

Signals are available on left/right/bottom edges only.

Selected blocks.

Two adjacent PIOs can be joined to provide a differential I/O pair (labeled as "T" and "C") as shown in Figure 2-25. The PAD Labels "T" and "C" distinguish the two PIOs. Approximately 50% of the PIO pairs on the left and right edges of the device can be configured as true LVDS outputs. All I/O pairs can operate as inputs.

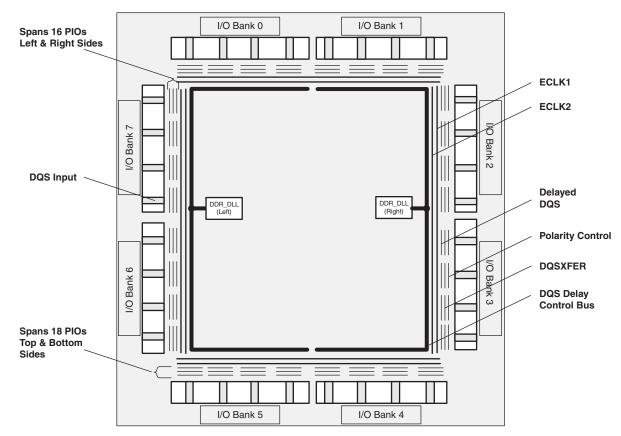

## **DLL Calibrated DQS Delay Block**

Source synchronous interfaces generally require the input clock to be adjusted in order to correctly capture data at the input register. For most interfaces a PLL is used for this adjustment. However, in DDR memories the clock, referred to as DQS, is not free-running, and this approach cannot be used. The DQS Delay block provides the required clock alignment for DDR memory interfaces.

The DQS signal (selected PIOs only, as shown in Figure 2-30) feeds from the PAD through a DQS delay element to a dedicated DQS routing resource. The DQS signal also feeds polarity control logic which controls the polarity of the clock to the sync registers in the input register blocks. Figure 2-30 and Figure 2-31 show how the DQS transition signals are routed to the PIOs.

The temperature, voltage and process variations of the DQS delay block are compensated by a set of 6-bit bus calibration signals from two dedicated DLLs (DDR\_DLL) on opposite sides of the device. Each DLL compensates DQS delays in its half of the device as shown in Figure 2-30. The DLL loop is compensated for temperature, voltage and process variations by the system clock and feedback loop.

Figure 2-30. Edge Clock, DLL Calibration and DQS Local Bus Distribution

#### Table 2-13. Supported Output Standards

| Output Standard                  | Drive                      | V <sub>CCIO</sub> (Nom.) |

|----------------------------------|----------------------------|--------------------------|

| Single-ended Interfaces          |                            |                          |

| LVTTL                            | 4mA, 8mA, 12mA, 16mA, 20mA | 3.3                      |

| LVCMOS33                         | 4mA, 8mA, 12mA 16mA, 20mA  | 3.3                      |

| LVCMOS25                         | 4mA, 8mA, 12mA, 16mA, 20mA | 2.5                      |

| LVCMOS18                         | 4mA, 8mA, 12mA, 16mA       | 1.8                      |

| LVCMOS15                         | 4mA, 8mA                   | 1.5                      |

| LVCMOS12                         | 2mA, 6mA                   | 1.2                      |

| LVCMOS33, Open Drain             | 4mA, 8mA, 12mA 16mA, 20mA  |                          |

| LVCMOS25, Open Drain             | 4mA, 8mA, 12mA 16mA, 20mA  |                          |

| LVCMOS18, Open Drain             | 4mA, 8mA, 12mA 16mA        |                          |

| LVCMOS15, Open Drain             | 4mA, 8mA                   |                          |

| LVCMOS12, Open Drain             | 2mA, 6mA                   |                          |

| PCI33                            | N/A                        | 3.3                      |

| HSTL18 Class I, II               | N/A                        | 1.8                      |

| HSTL15 Class I                   | N/A                        | 1.5                      |

| SSTL33 Class I, II               | N/A                        | 3.3                      |

| SSTL25 Class I, II               | N/A                        | 2.5                      |

| SSTL18 Class I, II               | N/A                        | 1.8                      |

| Differential Interfaces          |                            |                          |

| Differential SSTL33, Class I, II | N/A                        | 3.3                      |

| Differential SSTL25, Class I, II | N/A                        | 2.5                      |

| Differential SSTL18, Class I, II | N/A                        | 1.8                      |

| Differential HSTL18, Class I, II | N/A                        | 1.8                      |

| Differential HSTL15, Class I     | N/A                        | 1.5                      |

| LVDS <sup>1, 2</sup>             | N/A                        | 2.5                      |

| MLVDS <sup>1</sup>               | N/A                        | 2.5                      |

| BLVDS <sup>1</sup>               | N/A                        | 2.5                      |

| LVPECL <sup>1</sup>              | N/A                        | 3.3                      |

| RSDS <sup>1</sup>                | N/A                        | 2.5                      |

| LVCMOS33D <sup>1</sup>           | 4mA, 8mA, 12mA, 16mA, 20mA | 3.3                      |

1. Emulated with external resistors.

2. On the left and right edges, LVDS outputs are supported with a dedicated differential output driver on 50% of the I/Os. This solution does not require external resistors at the driver.

## **Hot Socketing**

LatticeXP2 devices have been carefully designed to ensure predictable behavior during power-up and powerdown. Power supplies can be sequenced in any order. During power-up and power-down sequences, the I/Os remain in tri-state until the power supply voltage is high enough to ensure reliable operation. In addition, leakage into I/O pins is controlled to within specified limits. This allows for easy integration with the rest of the system. These capabilities make the LatticeXP2 ideal for many multiple power supply and hot-swap applications.

# IEEE 1149.1-Compliant Boundary Scan Testability

All LatticeXP2 devices have boundary scan cells that are accessed through an IEEE 1149.1 compliant Test Access Port (TAP). This allows functional testing of the circuit board, on which the device is mounted, through a serial scan path that can access all critical logic nodes. Internal registers are linked internally, allowing test data to be shifted in

original backup configuration and try again. This all can be done without power cycling the system. For more information please see TN1220, <u>LatticeXP2 Dual Boot Feature</u>.

For more information on device configuration, please see TN1141, LatticeXP2 sysCONFIG Usage Guide.

## Soft Error Detect (SED) Support

LatticeXP2 devices have dedicated logic to perform Cyclic Redundancy Code (CRC) checks. During configuration, the configuration data bitstream can be checked with the CRC logic block. In addition, LatticeXP2 devices can be programmed for checking soft errors in SRAM. SED can be run on a programmed device when the user logic is not active. In the event a soft error occurs, the device can be programmed to either reload from a known good boot image (from internal Flash or external SPI memory) or generate an error signal.

For further information on SED support, please see TN1130, LatticeXP2 Soft Error Detection (SED) Usage Guide.

## **On-Chip Oscillator**

Every LatticeXP2 device has an internal CMOS oscillator that is used to derive a Master Clock (CCLK) for configuration. The oscillator and CCLK run continuously and are available to user logic after configuration is complete. The available CCLK frequencies are listed in Table 2-14. When a different CCLK frequency is selected during the design process, the following sequence takes place:

- 1. Device powers up with the default CCLK frequency.

- 2. During configuration, users select a different CCLK frequency.

- 3. CCLK frequency changes to the selected frequency after clock configuration bits are received.

This internal CMOS oscillator is available to the user by routing it as an input clock to the clock tree. For further information on the use of this oscillator for configuration or user mode, please see TN1141, <u>LatticeXP2 sysCON-FIG Usage Guide</u>.

| CCLK/Oscillator (MHz)                     |  |  |  |  |  |  |  |

|-------------------------------------------|--|--|--|--|--|--|--|

| 2.5 <sup>1</sup>                          |  |  |  |  |  |  |  |

| <b>3.1</b> <sup>2</sup>                   |  |  |  |  |  |  |  |

| 4.3                                       |  |  |  |  |  |  |  |

| 5.4                                       |  |  |  |  |  |  |  |

| 6.9                                       |  |  |  |  |  |  |  |

| 8.1                                       |  |  |  |  |  |  |  |

| 9.2                                       |  |  |  |  |  |  |  |

| 10                                        |  |  |  |  |  |  |  |

| 13                                        |  |  |  |  |  |  |  |

| 15                                        |  |  |  |  |  |  |  |

| 20                                        |  |  |  |  |  |  |  |

| 26                                        |  |  |  |  |  |  |  |

| 32                                        |  |  |  |  |  |  |  |

| 40                                        |  |  |  |  |  |  |  |

| 54                                        |  |  |  |  |  |  |  |

| 80 <sup>3</sup>                           |  |  |  |  |  |  |  |

| 163 <sup>3</sup>                          |  |  |  |  |  |  |  |

| 1. Software default oscillator frequency. |  |  |  |  |  |  |  |

1. Software default oscillator frequency.

2. Software default CCLK frequency.

3. Frequency not valid for CCLK.

# sysIO Differential Electrical Characteristics LVDS

| Parameter                         | Description                                    | Test Conditions                                                | Min.   | Тур. | Max.  | Units |

|-----------------------------------|------------------------------------------------|----------------------------------------------------------------|--------|------|-------|-------|

| V <sub>INP</sub> V <sub>INM</sub> | Input Voltage                                  |                                                                | 0      | _    | 2.4   | V     |

| V <sub>CM</sub>                   | Input Common Mode Voltage                      | Half the Sum of the Two Inputs                                 | 0.05   | _    | 2.35  | V     |

| V <sub>THD</sub>                  | Differential Input Threshold                   | Difference Between the Two Inputs                              | +/-100 |      |       | mV    |

| I <sub>IN</sub>                   | Input Current                                  | Power On or Power Off                                          | _      |      | +/-10 | μΑ    |

| V <sub>OH</sub>                   | Output High Voltage for $V_{OP}$ or $V_{OM}$   | R <sub>T</sub> = 100 Ohm                                       | _      | 1.38 | 1.60  | V     |

| V <sub>OL</sub>                   | Output Low Voltage for $V_{OP}$ or $V_{OM}$    | R <sub>T</sub> = 100 Ohm                                       | 0.9V   | 1.03 |       | V     |

| V <sub>OD</sub>                   | Output Voltage Differential                    | (V <sub>OP</sub> - V <sub>OM</sub> ), R <sub>T</sub> = 100 Ohm | 250    | 350  | 450   | mV    |

| ΔV <sub>OD</sub>                  | Change in V <sub>OD</sub> Between High and Low |                                                                | _      | _    | 50    | mV    |

| V <sub>OS</sub>                   | Output Voltage Offset                          | $(V_{OP} + V_{OM})/2, R_{T} = 100 \text{ Ohm}$                 | 1.125  | 1.20 | 1.375 | V     |

| $\Delta V_{OS}$                   | Change in V <sub>OS</sub> Between H and L      |                                                                | _      |      | 50    | mV    |

| I <sub>SA</sub>                   | Output Short Circuit Current                   | V <sub>OD</sub> = 0V Driver Outputs Shorted to<br>Ground       | —      | _    | 24    | mA    |

| I <sub>SAB</sub>                  | Output Short Circuit Current                   | V <sub>OD</sub> = 0V Driver Outputs Shorted to<br>Each Other   | _      | _    | 12    | mA    |

#### **Over Recommended Operating Conditions**

## Differential HSTL and SSTL

Differential HSTL and SSTL outputs are implemented as a pair of complementary single-ended outputs. All allowable single-ended output classes (class I and class II) are supported in this mode.

For further information on LVPECL, RSDS, MLVDS, BLVDS and other differential interfaces please see details in additional technical notes listed at the end of this data sheet.

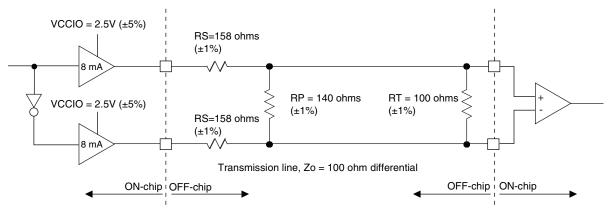

## LVDS25E

The top and bottom sides of LatticeXP2 devices support LVDS outputs via emulated complementary LVCMOS outputs in conjunction with a parallel resistor across the driver outputs. The scheme shown in Figure 3-1 is one possible solution for point-to-point signals.

# LatticeXP2 External Switching Characteristics (Continued)

|                          |                                                                  |        | -    | 7    | -    | 6    | -    |      |       |

|--------------------------|------------------------------------------------------------------|--------|------|------|------|------|------|------|-------|

| Parameter                | Description                                                      | Device | Min. | Max. | Min. | Max. | Min. | Max. | Units |

|                          |                                                                  | XP2-5  | 0.00 | —    | 0.00 | —    | 0.00 | —    | ns    |

|                          |                                                                  | XP2-8  | 0.00 | —    | 0.00 | —    | 0.00 | —    | ns    |

| t <sub>H_DELPLL</sub>    | Clock to Data Hold - PIO Input<br>Register with Input Data Delay | XP2-17 | 0.00 | —    | 0.00 | —    | 0.00 | —    | ns    |

|                          |                                                                  | XP2-30 | 0.00 | —    | 0.00 | —    | 0.00 | —    | ns    |

|                          |                                                                  | XP2-40 | 0.00 | —    | 0.00 | —    | 0.00 |      | ns    |

| DDR <sup>2</sup> and DDI | R2 <sup>3</sup> I/O Pin Parameters                               |        | •    | •    |      | •    | •    |      | •     |

| t <sub>DVADQ</sub>       | Data Valid After DQS<br>(DDR Read)                               | XP2    | _    | 0.29 | —    | 0.29 | —    | 0.29 | UI    |

| t <sub>DVEDQ</sub>       | Data Hold After DQS<br>(DDR Read)                                | XP2    | 0.71 | —    | 0.71 | —    | 0.71 | _    | UI    |

| t <sub>DQVBS</sub>       | Data Valid Before DQS                                            | XP2    | 0.25 | —    | 0.25 | —    | 0.25 | —    | UI    |

| t <sub>DQVAS</sub>       | Data Valid After DQS                                             | XP2    | 0.25 | —    | 0.25 | —    | 0.25 |      | UI    |

| f <sub>MAX_DDR</sub>     | DDR Clock Frequency                                              | XP2    | 95   | 200  | 95   | 166  | 95   | 133  | MHz   |

| f <sub>MAX_DDR2</sub>    | DDR Clock Frequency                                              | XP2    | 133  | 200  | 133  | 200  | 133  | 166  | MHz   |

| Primary Clock            | (                                                                |        |      |      |      |      |      |      |       |

| f <sub>MAX_PRI</sub>     | Frequency for Primary Clock<br>Tree                              | XP2    | _    | 420  | —    | 357  | —    | 311  | MHz   |

| t <sub>W_PRI</sub>       | Clock Pulse Width for Primary<br>Clock                           | XP2    | 1    | —    | 1    | —    | 1    | _    | ns    |

| t <sub>SKEW_PRI</sub>    | Primary Clock Skew Within a Bank                                 | XP2    | _    | 160  | —    | 160  | —    | 160  | ps    |

| Edge Clock (E            | CLK1 and ECLK2)                                                  |        | •    | •    |      | •    | •    |      | •     |

| fMAX_ECLK                | Frequency for Edge Clock                                         | XP2    | —    | 420  | —    | 357  | —    | 311  | MHz   |

| <sup>t</sup> w_eclk      | Clock Pulse Width for Edge<br>Clock                              | XP2    | 1    | —    | 1    | —    | 1    | —    | ns    |

| t <sub>SKEW_ECLK</sub>   | Edge Clock Skew Within an<br>Edge of the Device                  | XP2    | -    | 130  | _    | 130  | —    | 130  | ps    |

## **Over Recommended Operating Conditions**

1. General timing numbers based on LVCMOS 2.5, 12mA, 0pf load.

2. DDR timing numbers based on SSTL25.

3. DDR2 timing numbers based on SSTL18.

# LatticeXP2 Internal Switching Characteristics<sup>1</sup>

|                         |                                                   | -      | 7     | -      | 6     | -      |       |    |

|-------------------------|---------------------------------------------------|--------|-------|--------|-------|--------|-------|----|

| Parameter               | Description                                       | Min.   | Max.  | Min.   | Max.  | Min.   | Units |    |

|                         | ic Mode Timing                                    |        |       |        |       |        | Max.  | •• |

| t <sub>LUT4_PFU</sub>   | LUT4 delay (A to D inputs to F<br>output)         | _      | 0.216 | _      | 0.238 | _      | 0.260 | ns |

| t <sub>LUT6_PFU</sub>   | LUT6 delay (A to D inputs to OFX output)          | _      | 0.304 | _      | 0.399 | _      | 0.494 | ns |

| t <sub>LSR_PFU</sub>    | Set/Reset to output of PFU (Asyn-<br>chronous)    | _      | 0.720 | _      | 0.769 | —      | 0.818 | ns |

| t <sub>SUM_PFU</sub>    | Clock to Mux (M0,M1) Input<br>Setup Time          | 0.154  | _     | 0.151  | _     | 0.148  | _     | ns |

| t <sub>HM_PFU</sub>     | Clock to Mux (M0,M1) Input Hold<br>Time           | -0.061 | _     | -0.057 | _     | -0.053 | _     | ns |

| t <sub>SUD_PFU</sub>    | Clock to D input setup time                       | 0.061  | —     | 0.077  | —     | 0.093  | —     | ns |

| t <sub>HD_PFU</sub>     | Clock to D input hold time                        | 0.002  |       | 0.003  |       | 0.003  |       | ns |

| t <sub>CK2Q_PFU</sub>   | Clock to Q delay, (D-type Register Configuration) | _      | 0.342 | —      | 0.363 | —      | 0.383 | ns |

| t <sub>RSTREC_PFU</sub> | Asynchronous reset recovery<br>time for PFU Logic | —      | 0.520 | —      | 0.634 | _      | 0.748 | ns |

| t <sub>RST_PFU</sub>    | Asynchronous reset time for PFU Logic             | _      | 0.720 | —      | 0.769 | _      | 0.818 | ns |

| PFU Dual Por            | t Memory Mode Timing                              |        |       |        |       |        |       |    |

| t <sub>CORAM_PFU</sub>  | Clock to Output (F Port)                          | —      | 1.082 | —      | 1.267 | —      | 1.452 | ns |

| t <sub>SUDATA_PFU</sub> | Data Setup Time                                   | -0.206 | —     | -0.240 | _     | -0.274 | —     | ns |

| t <sub>HDATA_PFU</sub>  | Data Hold Time                                    | 0.239  | _     | 0.275  | _     | 0.312  | —     | ns |

| t <sub>SUADDR_PFU</sub> | Address Setup Time                                | -0.294 | _     | -0.333 | _     | -0.371 |       | ns |

| t <sub>HADDR_PFU</sub>  | Address Hold Time                                 | 0.295  | —     | 0.333  | _     | 0.371  | —     | ns |

| t <sub>SUWREN_PFU</sub> | Write/Read Enable Setup Time                      | -0.146 | —     | -0.169 | _     | -0.193 | —     | ns |

| t <sub>HWREN_PFU</sub>  | Write/Read Enable Hold Time                       | 0.158  | _     | 0.182  | _     | 0.207  | —     | ns |

| PIO Input/Out           | put Buffer Timing                                 |        |       |        |       |        |       |    |

| t <sub>IN_PIO</sub>     | Input Buffer Delay (LVCMOS25)                     | _      | 0.858 | —      | 0.766 | —      | 0.674 | ns |

| t <sub>OUT_PIO</sub>    | Output Buffer Delay (LVCMOS25)                    |        | 1.561 | _      | 1.403 | —      | 1.246 | ns |

| IOLOGIC Inpu            | it/Output Timing                                  |        |       |        |       |        |       |    |

| t <sub>SUI_PIO</sub>    | Input Register Setup Time (Data Before Clock)     | 0.583  | —     | 0.893  | _     | 1.201  | —     | ns |

| t <sub>HI_PIO</sub>     | Input Register Hold Time (Data after Clock)       | 0.062  | —     | 0.322  | _     | 0.482  | —     | ns |

| t <sub>COO_PIO</sub>    | Output Register Clock to Output<br>Delay          | _      | 0.608 | _      | 0.661 | _      | 0.715 | ns |

| t <sub>SUCE_PIO</sub>   | Input Register Clock Enable<br>Setup Time         | 0.032  | _     | 0.037  | _     | 0.041  | —     | ns |

| t <sub>HCE_PIO</sub>    | Input Register Clock Enable Hold<br>Time          | -0.022 | _     | -0.025 | _     | -0.028 | _     | ns |

| t <sub>SULSR_PIO</sub>  | Set/Reset Setup Time                              | 0.184  | —     | 0.201  |       | 0.217  | —     | ns |

| t <sub>HLSR_PIO</sub>   | Set/Reset Hold Time                               | -0.080 |       | -0.086 |       | -0.093 | _     | ns |

| t <sub>RSTREC_PIO</sub> | Asynchronous reset recovery time for IO Logic     | 0.228  | _     | 0.247  | _     | 0.266  | _     | ns |

### **Over Recommended Operating Conditions**

Note: Input data and address are registered at the positive edge of the clock and output data appears after the positive edge of the clock.

# LatticeXP2 Family Timing Adders<sup>1, 2, 3, 4</sup> (Continued)

| Buffer Type   | Description                              | -7    | -6    | -5    | Units |

|---------------|------------------------------------------|-------|-------|-------|-------|

| HSTL15_I      | HSTL_15 class I 4mA drive                | 0.32  | 0.69  | 1.06  | ns    |

| HSTL15D_I     | Differential HSTL 15 class I 4mA drive   | 0.32  | 0.69  | 1.06  | ns    |

| SSTL33_I      | SSTL_3 class I                           | -0.25 | 0.05  | 0.35  | ns    |

| SSTL33_II     | SSTL_3 class II                          | -0.31 | -0.02 | 0.27  | ns    |

| SSTL33D_I     | Differential SSTL_3 class I              | -0.25 | 0.05  | 0.35  | ns    |

| SSTL33D_II    | Differential SSTL_3 class II             | -0.31 | -0.02 | 0.27  | ns    |

| SSTL25_I      | SSTL_2 class I 8mA drive                 | -0.25 | 0.02  | 0.30  | ns    |

| SSTL25_II     | SSTL_2 class II 16mA drive               | -0.28 | 0.00  | 0.28  | ns    |

| SSTL25D_I     | Differential SSTL_2 class I 8mA drive    | -0.25 | 0.02  | 0.30  | ns    |

| SSTL25D_II    | Differential SSTL_2 class II 16mA drive  | -0.28 | 0.00  | 0.28  | ns    |

| SSTL18_I      | SSTL_1.8 class I                         | -0.17 | 0.13  | 0.43  | ns    |

| SSTL18_II     | SSTL_1.8 class II 8mA drive              | -0.18 | 0.12  | 0.42  | ns    |

| SSTL18D_I     | Differential SSTL_1.8 class I            | -0.17 | 0.13  | 0.43  | ns    |

| SSTL18D_II    | Differential SSTL_1.8 class II 8mA drive | -0.18 | 0.12  | 0.42  | ns    |

| LVTTL33_4mA   | LVTTL 4mA drive                          | -0.37 | -0.05 | 0.26  | ns    |

| LVTTL33_8mA   | LVTTL 8mA drive                          | -0.45 | -0.18 | 0.10  | ns    |

| LVTTL33_12mA  | LVTTL 12mA drive                         | -0.52 | -0.24 | 0.04  | ns    |

| LVTTL33_16mA  | LVTTL 16mA drive                         | -0.43 | -0.14 | 0.14  | ns    |

| LVTTL33_20mA  | LVTTL 20mA drive                         | -0.46 | -0.18 | 0.09  | ns    |

| LVCMOS33_4mA  | LVCMOS 3.3 4mA drive, fast slew rate     | -0.37 | -0.05 | 0.26  | ns    |

| LVCMOS33_8mA  | LVCMOS 3.3 8mA drive, fast slew rate     | -0.45 | -0.18 | 0.10  | ns    |

| LVCMOS33_12mA | LVCMOS 3.3 12mA drive, fast slew rate    | -0.52 | -0.24 | 0.04  | ns    |

| LVCMOS33_16mA | LVCMOS 3.3 16mA drive, fast slew rate    | -0.43 | -0.14 | 0.14  | ns    |

| LVCMOS33_20mA | LVCMOS 3.3 20mA drive, fast slew rate    | -0.46 | -0.18 | 0.09  | ns    |

| LVCMOS25_4mA  | LVCMOS 2.5 4mA drive, fast slew rate     | -0.42 | -0.15 | 0.13  | ns    |

| LVCMOS25_8mA  | LVCMOS 2.5 8mA drive, fast slew rate     | -0.48 | -0.21 | 0.05  | ns    |

| LVCMOS25_12mA | LVCMOS 2.5 12mA drive, fast slew rate    | 0.00  | 0.00  | 0.00  | ns    |

| LVCMOS25_16mA | LVCMOS 2.5 16mA drive, fast slew rate    | -0.45 | -0.18 | 0.08  | ns    |

| LVCMOS25_20mA | LVCMOS 2.5 20mA drive, fast slew rate    | -0.49 | -0.22 | 0.04  | ns    |

| LVCMOS18_4mA  | LVCMOS 1.8 4mA drive, fast slew rate     | -0.46 | -0.18 | 0.10  | ns    |

| LVCMOS18_8mA  | LVCMOS 1.8 8mA drive, fast slew rate     | -0.52 | -0.25 | 0.02  | ns    |

| LVCMOS18_12mA | LVCMOS 1.8 12mA drive, fast slew rate    | -0.56 | -0.30 | -0.03 | ns    |

| LVCMOS18_16mA | LVCMOS 1.8 16mA drive, fast slew rate    | -0.50 | -0.24 | 0.03  | ns    |

| LVCMOS15_4mA  | LVCMOS 1.5 4mA drive, fast slew rate     | -0.45 | -0.17 | 0.11  | ns    |

| LVCMOS15_8mA  | LVCMOS 1.5 8mA drive, fast slew rate     | -0.53 | -0.26 | 0.00  | ns    |

| LVCMOS12_2mA  | LVCMOS 1.2 2mA drive, fast slew rate     | -0.46 | -0.19 | 0.08  | ns    |

| LVCMOS12_6mA  | LVCMOS 1.2 6mA drive, fast slew rate     | -0.55 | -0.29 | -0.02 | ns    |

| LVCMOS33_4mA  | LVCMOS 3.3 4mA drive, slow slew rate     | 0.98  | 1.41  | 1.84  | ns    |

| LVCMOS33_8mA  | LVCMOS 3.3 8mA drive, slow slew rate     | 0.74  | 1.16  | 1.58  | ns    |

| LVCMOS33_12mA | LVCMOS 3.3 12mA drive, slow slew rate    | 0.56  | 0.97  | 1.38  | ns    |

| LVCMOS33_16mA | LVCMOS 3.3 16mA drive, slow slew rate    | 0.77  | 1.19  | 1.61  | ns    |

| LVCMOS33_20mA | LVCMOS 3.3 20mA drive, slow slew rate    | 0.57  | 0.98  | 1.40  | ns    |

## **Over Recommended Operating Conditions**

# LatticeXP2 sysCONFIG Port Timing Specifications

| Parameter            | Description                                                  | Min  | Max      | Units  |

|----------------------|--------------------------------------------------------------|------|----------|--------|

| sysCONFIG PC         | R, Initialization and Wake Up                                |      | <u> </u> |        |

| t <sub>ICFG</sub>    | Minimum Vcc to INITN High                                    |      | 50       | ms     |

| t <sub>VMC</sub>     | Time from t <sub>ICFG</sub> to valid Master CCLK             | _    | 2        | μs     |

| t <sub>PRGMRJ</sub>  | PROGRAMN Pin Pulse Rejection                                 | —    | 12       | ns     |

| t <sub>PRGM</sub>    | PROGRAMN Low Time to Start Configuration                     | 50   | —        | ns     |

| t <sub>DINIT</sub> 1 | PROGRAMN High to INITN High Delay                            |      | 1        | ms     |

| t <sub>DPPINIT</sub> | Delay Time from PROGRAMN Low to INITN Low                    |      | 50       | ns     |

| t <sub>DPPDONE</sub> | Delay Time from PROGRAMN Low to DONE Low                     | —    | 50       | ns     |

| t <sub>IODISS</sub>  | User I/O Disable from PROGRAMN Low                           |      | 35       | ns     |

| t <sub>IOENSS</sub>  | User I/O Enabled Time from CCLK Edge During Wake-up Sequence |      | 25       | ns     |

| t <sub>MWC</sub>     | Additional Wake Master Clock Signals after DONE Pin High     | 0    | —        | Cycles |

| sysCONFIG SP         | I Port (Master)                                              |      | •        |        |

| t <sub>CFGX</sub>    | INITN High to CCLK Low                                       | —    | 1        | μs     |

| t <sub>CSSPI</sub>   | INITN High to CSSPIN Low                                     | _    | 2        | μs     |

| t <sub>CSCCLK</sub>  | CCLK Low before CSSPIN Low                                   | 0    | —        | ns     |

| t <sub>SOCDO</sub>   | CCLK Low to Output Valid                                     | _    | 15       | ns     |

| t <sub>CSPID</sub>   | CSSPIN[0:1] Low to First CCLK Edge Setup Time                | 2cyc | 600+6cyc | ns     |

| f <sub>MAXSPI</sub>  | Max CCLK Frequency                                           | _    | 20       | MHz    |

| t <sub>SUSPI</sub>   | SOSPI Data Setup Time Before CCLK                            | 7    | —        | ns     |

| t <sub>HSPI</sub>    | SOSPI Data Hold Time After CCLK                              | 10   | —        | ns     |

| sysCONFIG SP         | I Port (Slave)                                               |      | •        |        |

| f <sub>MAXSPIS</sub> | Slave CCLK Frequency                                         | —    | 25       | MHz    |

| t <sub>RF</sub>      | Rise and Fall Time                                           | 50   | —        | mV/ns  |

| t <sub>stco</sub>    | Falling Edge of CCLK to SOSPI Active                         | —    | 20       | ns     |

| t <sub>STOZ</sub>    | Falling Edge of CCLK to SOSPI Disable                        |      | 20       | ns     |

| t <sub>STSU</sub>    | Data Setup Time (SISPI)                                      | 8    | —        | ns     |

| t <sub>STH</sub>     | Data Hold Time (SISPI)                                       | 10   | —        | ns     |

| t <sub>STCKH</sub>   | CCLK Clock Pulse Width, High                                 | 0.02 | 200      | μs     |

| t <sub>STCKL</sub>   | CCLK Clock Pulse Width, Low                                  | 0.02 | 200      | μs     |

| t <sub>STVO</sub>    | Falling Edge of CCLK to Valid SOSPI Output                   | _    | 20       | ns     |

| t <sub>SCS</sub>     | CSSPISN High Time                                            | 25   | —        | ns     |

| t <sub>SCSS</sub>    | CSSPISN Setup Time                                           | 25   | -        | ns     |

| t <sub>SCSH</sub>    | CSSPISN Hold Time                                            | 25   | —        | ns     |

#### **Over Recommended Operating Conditions**

1. Re-toggling the PROGRAMN pin is not permitted until the INITN pin is high. Avoid consecutive toggling of PROGRAMN.

# Pin Information Summary

|                                          | XP2-5          |              |             |             | XP2-8        |              |             |             | XP2-17       |             |              | XP2-30       |              |              | XP2-40   |              |          |

|------------------------------------------|----------------|--------------|-------------|-------------|--------------|--------------|-------------|-------------|--------------|-------------|--------------|--------------|--------------|--------------|----------|--------------|----------|

| Pin Ty                                   | pe             | 132<br>csBGA | 144<br>TQFP | 208<br>PQFP | 256<br>ftBGA | 132<br>csBGA | 144<br>TQFP | 208<br>PQFP | 256<br>ftBGA | 208<br>PQFP | 256<br>ftBGA | 484<br>fpBGA | 256<br>ftBGA | 484<br>fpBGA | 672      | 484<br>fpBGA | 672      |

| Single Ended User I/O                    |                | 86           | 100         | 146         | 172          | 86           | 100         | 146         | 201          | 146         | 201          | 358          | 201          | 363          | 472      | 363          | 540      |

| Differential Pair                        | Normal         | 35           | 39          | 57          | 66           | 35           | 39          | 57          | 77           | 57          | 77           | 135          | 77           | 137          | 180      | 137          | 204      |

| User I/O                                 | Highspeed      | 8            | 11          | 16          | 20           | 8            | 11          | 16          | 23           | 16          | 23           | 44           | 23           | 44           | 56       | 44           | 66       |

|                                          | TAP            | 5            | 5           | 5           | 5            | 5            | 5           | 5           | 5            | 5           | 5            | 5            | 5            | 5            | 5        | 5            | 5        |

| Configuration                            | Muxed          | 9            | 9           | 9           | 9            | 9            | 9           | 9           | 9            | 9           | 9            | 9            | 9            | 9            | 9        | 9            | 9        |

|                                          | Dedicated      | 1            | 1           | 1           | 1            | 1            | 1           | 1           | 1            | 1           | 1            | 1            | 1            | 1            | 1        | 1            | 1        |

| Non Configura-                           | Muxed          | 5            | 5           | 7           | 7            | 7            | 7           | 9           | 9            | 11          | 11           | 21           | 7            | 11           | 13       | 11           | 13       |

| tion                                     | Dedicated      | 1            | 1           | 1           | 1            | 1            | 1           | 1           | 1            | 1           | 1            | 1            | 1            | 1            | 1        | 1            | 1        |

| Vcc                                      |                | 6            | 4           | 9           | 6            | 6            | 4           | 9           | 6            | 9           | 6            | 16           | 6            | 16           | 20       | 16           | 20       |

| Vccaux                                   |                | 4            | 4           | 4           | 4            | 4            | 4           | 4           | 4            | 4           | 4            | 8            | 4            | 8            | 8        | 8            | 8        |

| VCCPLL                                   |                | 2            | 2           | 2           | -            | 2            | 2           | 2           | -            | 4           | -            | -            | -            | -            | -        | -            | -        |

|                                          | Bank0          | 2            | 2           | 2           | 2            | 2            | 2           | 2           | 2            | 2           | 2            | 4            | 2            | 4            | 4        | 4            | 4        |

|                                          | Bank1          | 1            | 1           | 2           | 2            | 1            | 1           | 2           | 2            | 2           | 2            | 4            | 2            | 4            | 4        | 4            | 4        |

|                                          | Bank2          | 2            | 2           | 2           | 2            | 2            | 2           | 2           | 2            | 2           | 2            | 4            | 2            | 4            | 4        | 4            | 4        |

| VCCIO                                    | Bank3          | 1            | 1           | 2           | 2            | 1            | 1           | 2           | 2            | 2           | 2            | 4            | 2            | 4            | 4        | 4            | 4        |

|                                          | Bank4          | 1            | 1           | 2           | 2            | 1            | 1           | 2           | 2            | 2           | 2            | 4            | 2            | 4            | 4        | 4            | 4        |

|                                          | Bank5          | 2            | 2           | 2           | 2            | 2            | 2           | 2           | 2            | 2           | 2            | 4            | 2            | 4            | 4        | 4            | 4        |

|                                          | Bank6          | 1            | 1           | 2           | 2            | 1            | 1           | 2           | 2            | 2           | 2            | 4            | 2            | 4            | 4        | 4            | 4        |

|                                          | Bank7          | 2            | 2           | 2           | 2            | 2            | 2           | 2           | 2            | 2           | 2            | 4            | 2            | 4            | 4        | 4            | 4        |

| GND, GND0-GNI                            | 77             | 15           | 15          | 20          | 20           | 15           | 15          | 22          | 20           | 22          | 20           | 56           | 20           | 56           | 64       | 56           | 64       |

| NC                                       | -              | -            | -           | 4           | 31           | -            | -           | 2           | 2            | -           | 2            | 7            | 2            | 2            | 69       | 2            | 1        |

|                                          | Bank0          | 18/9         | 20/10       | 20/10       | 26/13        | 18/9         | 20/10       | 20/10       | 28/14        | 20/10       | 28/14        | 52/26        | 28/14        | 52/26        | 70/35    | 52/26        | 70/35    |

|                                          | Bank1          | 4/2          | 6/3         | 18/9        | 18/9         | 4/2          | 6/3         | 18/9        | 22/11        | 18/9        | 22/11        | 36/18        | 22/11        | 36/18        | 54/27    | 36/18        | 70/35    |

| Qia ala Ea da di                         | Bank2          | 16/8         | 18/9        | 18/9        | 22/11        | 16/8         | 18/9        | 18/9        | 26/13        | 18/9        | 26/13        | 46/23        | 26/13        | 46/23        | 56/28    | 46/23        | 64/32    |

| Single Ended/<br>Differential I/O        | Bank3          | 4/2          | 4/2         | 16/8        | 20/10        | 4/2          | 4/2         | 16/8        | 24/12        | 16/8        | 24/12        | 44/22        | 24/12        | 46/23        | 56/28    | 46/23        | 66/33    |

| per Bank                                 | Bank4          | 8/4          | 8/4         | 18/9        | 18/9         | 8/4          | 8/4         | 18/9        | 26/13        | 18/9        | 26/13        | 36/18        | 26/13        | 38/19        | 54/27    | 38/19        | 70/35    |

|                                          | Bank5          | 14/7         | 18/9        | 20/10       | 24/12        | 14/7         | 18/9        | 20/10       | 24/12        | 20/10       | 24/12        | 52/26        | 24/12        | 53/26        | 70/35    | 53/26        | 70/35    |

|                                          | Bank6          | 6/3          | 8/4         | 18/9        | 22/11        | 6/3          | 8/4         | 18/9        | 27/13        | 18/9        | 27/13        | 46/23        | 27/13        | 46/23        | 56/28    | 46/23        | 66/33    |

|                                          | Bank7          | 16/8         | 18/9        | 18/9        | 22/11        | 16/8         | 18/9        | 18/9        | 24/12        | 18/9        | 24/12        | 46/23        | 24/12        | 46/23        | 56/28    | 46/23        | 64/32    |

|                                          | Bank0          | 0            | 0           | 0           | 0            | 0            | 0           | 0           | 0            | 0           | 0            | 0            | 0            | 0            | 0        | 0            | 0        |

|                                          | Bank1<br>Bank2 | 0<br>3       | 0<br>4      | 0<br>4      | 0            | 0            | 0           | 0           | 0            | 0<br>4      | 0            | 0<br>11      | 0            | 0            | 0        | 0<br>11      | 0        |

| True LVDS Pairs                          | Bank2<br>Bank3 | 3            | 4           | 4           | 5<br>5       | 3            | 4           | 4           | 6            | 4           | 6            | 11           | 6<br>6       | 11           | 14<br>14 | 11           | 16<br>17 |

| Bonding Out per                          | Bank4          | 0            | 0           | 4           | 0            | 0            | 0           | 4           | 0            | 4           | 0            | 0            | 0            | 0            | 0        | 0            | 0        |

| Bank                                     | Bank5          | 0            | 0           | 0           | 0            | 0            | 0           | 0           | 0            | 0           | 0            | 0            | 0            | 0            | 0        | 0            | 0        |

|                                          | Bank6          | 1            | 2           | 4           | 5            | 1            | 2           | 4           | 6            | 4           | 6            | 11           | 6            | 11           | 14       | 11           | 17       |

|                                          | Bank7          | 3            | 4           | 4           | 5            | 3            | 4           | 4           | 5            | 4           | 5            | 11           | 5            | 11           | 14       | 11           | 16       |

|                                          | Banko<br>Banko | 3<br>1       | 4           | 4           | 5            | 1            | 4           | 4           | 5            | 4           | 5            | 3            | 5            | 2            | 4        | 2            | 4        |

|                                          | Bank1          | 0            | 0           | 1           | 1            | 0            | 0           | 1           | 1            | 1           | 1            | 2            | 1            | 2            | 3        | 2            | 4        |

|                                          | Bank2          | 1            | 1           | 1           | 1            | 1            | 1           | 1           | 1            | 1           | 1            | 2            | 1            | 3            | 3        | 3            | 4        |

| DDR Banks                                | Bank3          | 0            | 0           | 1           | 1            | 0            | 0           | 1           | 1            | 1           | 1            | 2            | 1            | 3            | 3        | 3            | 4        |

| Bonding Out per<br>I/O Bank <sup>1</sup> | Bank4          | 0            | 0           | 1           | 1            | 0            | 0           | 1           | 1            | 1           | 1            | 2            | 1            | 2            | 3        | 2            | 4        |

| Dalik                                    | Bank5          | 1            | 1           | 1           | 1            | 1            | 1           | 1           | 1            | 1           | 1            | 3            | 1            | 2            | 4        | 2            | 4        |

|                                          | Bank6          | 0            | 0           | 1           | 1            | 0            | 0           | 1           | 1            | 1           | 1            | 2            | 1            | 3            | 3        | 3            | 4        |

|                                          | Bank7          | 1            | 1           | 1           | 1            | 1            | 1           | 1           | 1            | 1           | 1            | 2            | 1            | 3            | 3        | 3            | 4        |

|                                          | Junit          |              |             |             |              |              |             |             |              |             |              | <u> </u>     |              | 5            | 5        | 5            |          |

# LatticeXP2 Family Data Sheet Revision History

September 2014

Data Sheet DS1009

## **Revision History**

|                | Version | Section                             | Change Summary                                                                                                                                                                                                                                                     |

|----------------|---------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| May 2007       | 01.1    |                                     | Initial release.                                                                                                                                                                                                                                                   |

| September 2007 | 01.2    | DC and Switching<br>Characteristics | Added JTAG Port Timing Waveforms diagram.                                                                                                                                                                                                                          |

|                |         |                                     | Updated sysCLOCK PLL Timing table.                                                                                                                                                                                                                                 |

|                |         | Pinout Information                  | Added Thermal Management text section.                                                                                                                                                                                                                             |

| February 2008  | 01.3    | Architecture                        | Added LVCMOS33D to Supported Output Standards table.                                                                                                                                                                                                               |

|                |         |                                     | Clarified: "This Flash can be programmed through either the JTAG or<br>Slave SPI ports of the device. The SRAM configuration space can also<br>be infinitely reconfigured through the JTAG and Master SPI ports."                                                  |

|                |         |                                     | Added External Slave SPI Port to Serial TAG Memory section. Updated Serial TAG Memory diagram.                                                                                                                                                                     |

|                |         | DC and Switching<br>Characteristics | Updated Flash Programming Specifications table.                                                                                                                                                                                                                    |

|                |         |                                     | Added "8W" specification to Hot Socketing Specifications table.                                                                                                                                                                                                    |

|                |         |                                     | Updated Timing Tables                                                                                                                                                                                                                                              |

|                |         |                                     | Clarifications for IIH in DC Electrical Characteristics table.                                                                                                                                                                                                     |

|                |         |                                     | Added LVCMOS33D section                                                                                                                                                                                                                                            |

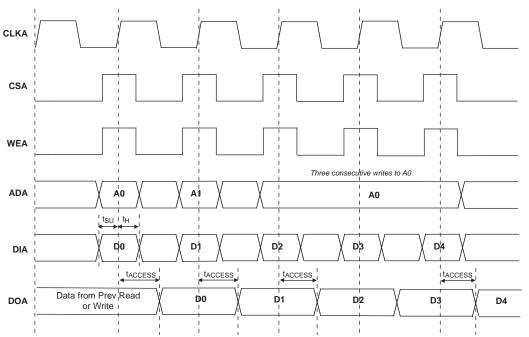

|                |         |                                     | Updated DOA and DOA (Regs) to EBR Timing diagrams.                                                                                                                                                                                                                 |

|                |         |                                     | Removed Master Clock Frequency and Duty Cycle sections from the LatticeXP2 sysCONFIG Port Timing Specifications table. These are listed on the On-chip Oscillator and Configuration Master Clock Characteristics table.                                            |

|                |         |                                     | Changed CSSPIN to CSSPISN in description of $t_{SCS},t_{SCSS},$ and $t_{SCSH}$ parameters. Removed $t_{SOE}$ parameter.                                                                                                                                            |

|                |         |                                     | Clarified On-chip Oscillator documentation                                                                                                                                                                                                                         |

|                |         |                                     | Added Switching Test Conditions                                                                                                                                                                                                                                    |

|                |         | Pinout Information                  | Added "True LVDS Pairs Bonding Out per Bank," "DDR Banks Bonding<br>Out per I/O Bank," and "PCI capable I/Os Bonding Out per Bank" to Pin<br>Information Summary in place of previous blank table "PCI and DDR<br>Capabilities of the Device-Package Combinations" |

|                |         |                                     | Removed pinout listing. This information is available on the LatticeXP2 product web pages                                                                                                                                                                          |

|                |         | Ordering Information                | Added XP2-17 "8W" and all other family OPNs.                                                                                                                                                                                                                       |

| April 2008     | 01.4    | DC and Switching                    | Updated Absolute Maximum Ratings footnotes.                                                                                                                                                                                                                        |

|                |         | Characteristics                     | Updated Recommended Operating Conditions Table footnotes.                                                                                                                                                                                                          |

|                |         |                                     | Updated Supply Current (Standby) Table                                                                                                                                                                                                                             |

|                |         |                                     | Updated Initialization Supply Current Table                                                                                                                                                                                                                        |

|                |         |                                     | Updated Programming and Erase Flash Supply Current Table                                                                                                                                                                                                           |

|                |         |                                     | Updated Register to Register Performance Table                                                                                                                                                                                                                     |

|                |         |                                     | Updated LatticeXP2 External Switching Characteristics Table                                                                                                                                                                                                        |

|                |         |                                     | Updated LatticeXP2 Internal Switching Characteristics Table                                                                                                                                                                                                        |

|                |         |                                     | Updated sysCLOCK PLL Timing Table                                                                                                                                                                                                                                  |

© 2014 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.