Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                                             |

|--------------------------------|-----------------------------------------------------------------------------|

| Product Status                 | Active                                                                      |

| Number of LABs/CLBs            | 625                                                                         |

| Number of Logic Elements/Cells | 5000                                                                        |

| Total RAM Bits                 | 169984                                                                      |

| Number of I/O                  | 146                                                                         |

| Number of Gates                | -                                                                           |

| Voltage - Supply               | 1.14V ~ 1.26V                                                               |

| Mounting Type                  | Surface Mount                                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                             |

| Package / Case                 | 208-BFQFP                                                                   |

| Supplier Device Package        | 208-PQFP (28x28)                                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfxp2-5e-7qn208c |

|                                |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

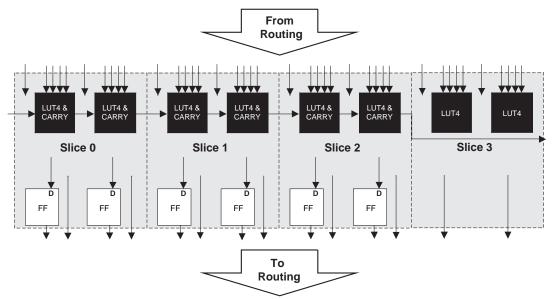

### Figure 2-2. PFU Diagram

## Slice

Slice 0 through Slice 2 contain two 4-input combinatorial Look-Up Tables (LUT4), which feed two registers. Slice 3 contains two LUT4s and no registers. For PFUs, Slice 0 and Slice 2 can also be configured as distributed memory, a capability not available in PFF blocks. Table 2-1 shows the capability of the slices in both PFF and PFU blocks along with the operation modes they enable. In addition, each PFU contains logic that allows the LUTs to be combined to perform functions such as LUT5, LUT6, LUT7 and LUT8. There is control logic to perform set/reset functions (programmable as synchronous/asynchronous), clock select, chip-select and wider RAM/ROM functions. Figure 2-3 shows an overview of the internal logic of the slice. The registers in the slice can be configured as positive/negative edge triggered or level sensitive clocks.

| Table 2-1. | Resources | and Modes | Available    | per Slice |

|------------|-----------|-----------|--------------|-----------|

|            |           |           | / IT analoio |           |

|         | PFU                     | 3Lock                   | PFF Block               |                    |  |

|---------|-------------------------|-------------------------|-------------------------|--------------------|--|

| Slice   | Resources               | Modes                   | Resources               | Modes              |  |

| Slice 0 | 2 LUT4s and 2 Registers | Logic, Ripple, RAM, ROM | 2 LUT4s and 2 Registers | Logic, Ripple, ROM |  |

| Slice 1 | 2 LUT4s and 2 Registers | Logic, Ripple, ROM      | 2 LUT4s and 2 Registers | Logic, Ripple, ROM |  |

| Slice 2 | 2 LUT4s and 2 Registers | Logic, Ripple, RAM, ROM | 2 LUT4s and 2 Registers | Logic, Ripple, ROM |  |

| Slice 3 | 2 LUT4s                 | Logic, ROM              | 2 LUT4s                 | Logic, ROM         |  |

Slice 0 through Slice 2 have 14 input signals: 13 signals from routing and one from the carry-chain (from the adjacent slice or PFU). There are seven outputs: six to routing and one to carry-chain (to the adjacent PFU). Slice 3 has 13 input signals from routing and four signals to routing. Table 2-2 lists the signals associated with Slice 0 to Slice 2.

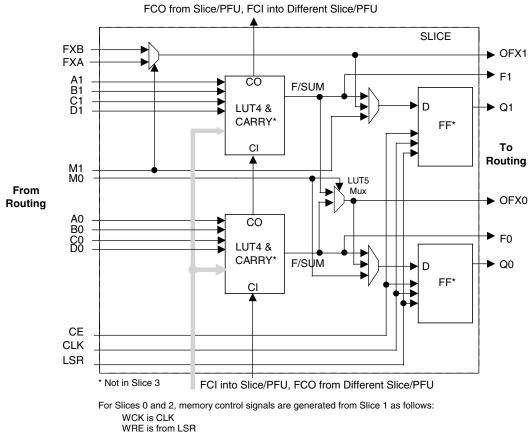

#### Figure 2-3. Slice Diagram

DI[3:2] for Slice 2 and DI[1:0] for Slice 0 data

WAD [A:D] is a 4bit address from slice 1 LUT input

Table 2-2. Slice Signal Descriptions

| Function | Туре               | Signal Names   | Description                                                          |

|----------|--------------------|----------------|----------------------------------------------------------------------|

| Input    | Data signal        | A0, B0, C0, D0 | Inputs to LUT4                                                       |

| Input    | Data signal        | A1, B1, C1, D1 | Inputs to LUT4                                                       |

| Input    | Multi-purpose      | MO             | Multipurpose Input                                                   |

| Input    | Multi-purpose      | M1             | Multipurpose Input                                                   |

| Input    | Control signal     | CE             | Clock Enable                                                         |

| Input    | Control signal     | LSR            | Local Set/Reset                                                      |

| Input    | Control signal     | CLK            | System Clock                                                         |

| Input    | Inter-PFU signal   | FCI            | Fast Carry-In <sup>1</sup>                                           |

| Input    | Inter-slice signal | FXA            | Intermediate signal to generate LUT6 and LUT7                        |

| Input    | Inter-slice signal | FXB            | Intermediate signal to generate LUT6 and LUT7                        |

| Output   | Data signals       | F0, F1         | LUT4 output register bypass signals                                  |

| Output   | Data signals       | Q0, Q1         | Register outputs                                                     |

| Output   | Data signals       | OFX0           | Output of a LUT5 MUX                                                 |

| Output   | Data signals       | OFX1           | Output of a LUT6, LUT7, LUT8 <sup>2</sup> MUX depending on the slice |

| Output   | Inter-PFU signal   | FCO            | Slice 2 of each PFU is the fast carry chain output <sup>1</sup>      |

1. See Figure 2-3 for connection details.

2. Requires two PFUs.

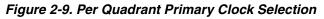

## Primary Clock Routing

The clock routing structure in LatticeXP2 devices consists of a network of eight primary clock lines (CLK0 through CLK7) per quadrant. The primary clocks of each quadrant are generated from muxes located in the center of the device. All the clock sources are connected to these muxes. Figure 2-9 shows the clock routing for one quadrant. Each quadrant mux is identical. If desired, any clock can be routed globally.

## **Dynamic Clock Select (DCS)**

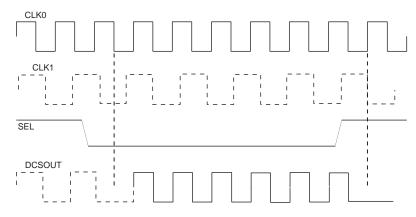

The DCS is a smart multiplexer function available in the primary clock routing. It switches between two independent input clock sources without any glitches or runt pulses. This is achieved irrespective of when the select signal is toggled. There are two DCS blocks per quadrant; in total, eight DCS blocks per device. The inputs to the DCS block come from the center muxes. The output of the DCS is connected to primary clocks CLK6 and CLK7 (see Figure 2-9).

Figure 2-10 shows the timing waveforms of the default DCS operating mode. The DCS block can be programmed to other modes. For more information on the DCS, please see TN1126, <u>LatticeXP2 sysCLOCK PLL Design and</u> <u>Usage Guide</u>.

#### Figure 2-10. DCS Waveforms

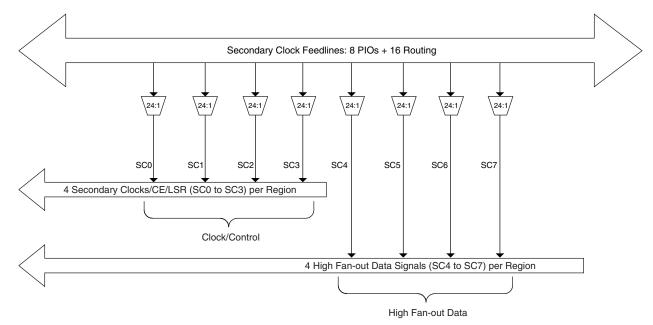

## Secondary Clock/Control Routing

Secondary clocks in the LatticeXP2 devices are region-based resources. The benefit of region-based resources is the relatively low injection delay and skew within the region, as compared to primary clocks. EBR rows, DSP rows and a special vertical routing channel bound the secondary clock regions. This special vertical routing channel aligns with either the left edge of the center DSP block in the DSP row or the center of the DSP row. Figure 2-11 shows this special vertical routing channel and the eight secondary clock regions for the LatticeXP2-40.

#### Figure 2-12. Secondary Clock Selection

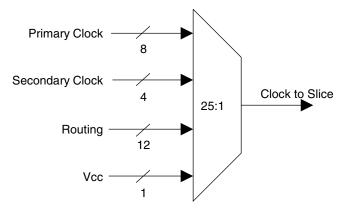

## Slice Clock Selection

Figure 2-13 shows the clock selections and Figure 2-14 shows the control selections for Slice0 through Slice2. All the primary clocks and the four secondary clocks are routed to this clock selection mux. Other signals, via routing, can be used as clock inputs to the slices. Slice controls are generated from the secondary clocks or other signals connected via routing.

If none of the signals are selected for both clock and control, then the default value of the mux output is 1. Slice 3 does not have any registers; therefore it does not have the clock or control muxes.

#### Figure 2-13. Slice0 through Slice2 Clock Selection

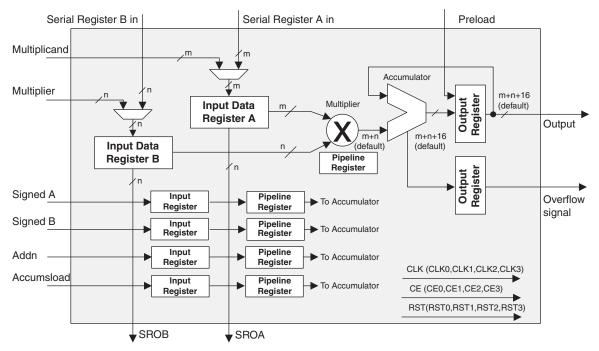

## MAC sysDSP Element

In this case, the two operands, A and B, are multiplied and the result is added with the previous accumulated value. This accumulated value is available at the output. The user can enable the input and pipeline registers but the output register is always enabled. The output register is used to store the accumulated value. The Accumulators in the DSP blocks in LatticeXP2 family can be initialized dynamically. A registered overflow signal is also available. The overflow conditions are provided later in this document. Figure 2-21 shows the MAC sysDSP element.

#### Figure 2-21. MAC sysDSP

### Tristate Register Block

The tristate register block provides the ability to register tri-state control signals from the core of the device before they are passed to the sysIO buffers. The block contains a register for SDR operation and an additional latch for DDR operation. Figure 2-27 shows the Tristate Register Block with the Output Block

In SDR mode, ONEG1 feeds one of the flip-flops that then feeds the output. The flip-flop can be configured as Dtype or latch. In DDR mode, ONEG1 and OPOS1 are fed into registers on the positive edge of the clock. Then in the next clock the registered OPOS1 is latched. A multiplexer running off the same clock cycle selects the correct register for feeding to the output (D0).

## **Control Logic Block**

The control logic block allows the selection and modification of control signals for use in the PIO block. A clock signal is selected from general purpose routing, ECLK1, ECLK2 or a DQS signal (from the programmable DQS pin) and is provided to the input register block. The clock can optionally be inverted.

## **DDR Memory Support**

PICs have additional circuitry to allow implementation of high speed source synchronous and DDR memory interfaces.

PICs have registered elements that support DDR memory interfaces. Interfaces on the left and right edges are designed for DDR memories that support 16 bits of data, whereas interfaces on the top and bottom are designed for memories that support 18 bits of data. One of every 16 PIOs on the left and right and one of every 18 PIOs on the top and bottom contain delay elements to facilitate the generation of DQS signals. The DQS signals feed the DQS buses which span the set of 16 or 18 PIOs. Figure 2-28 and Figure 2-29 show the DQS pin assignments in each set of PIOs.

The exact DQS pins are shown in a dual function in the Logic Signal Connections table in this data sheet. Additional detail is provided in the Signal Descriptions table. The DQS signal from the bus is used to strobe the DDR data from the memory into input register blocks. For additional information on using DDR memory support please see TN1138, <u>LatticeXP2 High Speed I/O Interface</u>.

# **Density Shifting**

The LatticeXP2 family is designed to ensure that different density devices in the same family and in the same package have the same pinout. Furthermore, the architecture ensures a high success rate when performing design migration from lower density devices to higher density devices. In many cases, it is also possible to shift a lower utilization design targeted for a high-density device to a lower density device. However, the exact details of the final resource utilization will impact the likely success in each case.

# Initialization Supply Current<sup>1, 2, 3, 4, 5</sup>

#### **Over Recommended Operating Conditions**

| Symbol             | Parameter                                                                                                            | Device | Typical<br>(25°C, Max. Supply) <sup>6</sup> | Units |

|--------------------|----------------------------------------------------------------------------------------------------------------------|--------|---------------------------------------------|-------|

|                    |                                                                                                                      | XP2-5  | 20                                          | mA    |

|                    |                                                                                                                      | XP2-8  | (25°C, Max. Supply) <sup>6</sup>            | mA    |

| I <sub>CC</sub>    | Core Power Supply Current                                                                                            | XP2-17 | 44                                          | mA    |

|                    |                                                                                                                      | XP2-30 | 58                                          | mA    |

|                    |                                                                                                                      | XP2-40 | 62                                          | mA    |

|                    |                                                                                                                      | XP2-5  | 67                                          | mA    |

|                    |                                                                                                                      | XP2-8  | 74                                          | mA    |

| I <sub>CCAUX</sub> | Auxiliary Power Supply Current <sup>7</sup>                                                                          | XP2-17 | 112                                         | mA    |

|                    | XP2-5         67           XP2-8         74           Auxiliary Power Supply Current <sup>7</sup> XP2-17         112 | 124    | mA                                          |       |

|                    |                                                                                                                      | XP2-40 | 130                                         | mA    |

| I <sub>CCPLL</sub> | PLL Power Supply Current (per PLL)                                                                                   |        | 1.8                                         | mA    |

| I <sub>CCIO</sub>  | Bank Power Supply Current (per Bank)                                                                                 |        | 6.4                                         | mA    |

| I <sub>CCJ</sub>   | VCCJ Power Supply Current                                                                                            |        | 1.2                                         | mA    |

1. For further information on supply current, please see TN1139, Power Estimation and Management for LatticeXP2 Devices.

2. Assumes all outputs are tristated, all inputs are configured as LVCMOS and held at the V<sub>CCIO</sub> or GND.

3. Frequency 0 MHz.

4. Does not include additional current from bypass or decoupling capacitor across the supply.

5. A specific configuration pattern is used that scales with the size of the device; consists of 75% PFU utilization, 50% EBR, and 25% I/O configuration.

6.  $T_J = 25^{\circ}C$ , power supplies at nominal voltage.

In fpBGA and ftBGA packages the PLLs are connected to and powered from the auxiliary power supply. For these packages, the actual

auxiliary supply current is the sum of I<sub>CCAUX</sub> and I<sub>CCPLL</sub>. For csBGA, PQFP and TQFP packages the PLLs are powered independent of the

auxiliary power supply.

# sysIO Recommended Operating Conditions

|                                                       | · · · · · · · · · · · · · · · · · · · |                   | ended Operating | goonanions |                      |       |

|-------------------------------------------------------|---------------------------------------|-------------------|-----------------|------------|----------------------|-------|

|                                                       |                                       | V <sub>CCIO</sub> |                 |            | V <sub>REF</sub> (V) |       |

| Standard                                              | Min.                                  | Тур.              | Max.            | Min.       | Тур.                 | Max.  |

| LVCMOS33 <sup>2</sup>                                 | 3.135                                 | 3.3               | 3.465           | —          | —                    | —     |

| LVCMOS25 <sup>2</sup>                                 | 2.375                                 | 2.5               | 2.625           | —          | —                    | —     |

| LVCMOS18                                              | 1.71                                  | 1.8               | 1.89            | —          | —                    | —     |

| LVCMOS15                                              | 1.425                                 | 1.5               | 1.575           | —          | —                    | —     |

| LVCMOS12 <sup>2</sup>                                 | 1.14                                  | 1.2               | 1.26            | —          | —                    | —     |

| LVTTL33 <sup>2</sup>                                  | 3.135                                 | 3.3               | 3.465           | —          | —                    | —     |

| PCI33                                                 | 3.135                                 | 3.3               | 3.465           | —          | —                    | —     |

| SSTL18_I <sup>2</sup> ,<br>SSTL18_II <sup>2</sup>     | 1.71                                  | 1.8               | 1.89            | 0.833      | 0.9                  | 0.969 |

| SSTL25_I <sup>2</sup> ,<br>SSTL25_II <sup>2</sup>     | 2.375                                 | 2.5               | 2.625           | 1.15       | 1.25                 | 1.35  |

| SSTL33_I <sup>2</sup> ,<br>SSTL33_II <sup>2</sup>     | 3.135                                 | 3.3               | 3.465           | 1.3        | 1.5                  | 1.7   |

| HSTL15_I <sup>2</sup>                                 | 1.425                                 | 1.5               | 1.575           | 0.68       | 0.75                 | 0.9   |

| HSTL18_I <sup>2</sup> ,<br>HSTL18_II <sup>2</sup>     | 1.71                                  | 1.8               | 1.89            | 0.816      | 0.9                  | 1.08  |

| LVDS25 <sup>2</sup>                                   | 2.375                                 | 2.5               | 2.625           |            | —                    | —     |

| MLVDS251                                              | 2.375                                 | 2.5               | 2.625           |            | —                    | —     |

| LVPECL33 <sup>1, 2</sup>                              | 3.135                                 | 3.3               | 3.465           |            | —                    | —     |

| BLVDS25 <sup>1, 2</sup>                               | 2.375                                 | 2.5               | 2.625           |            | —                    | —     |

| RSDS <sup>1, 2</sup>                                  | 2.375                                 | 2.5               | 2.625           |            | —                    | —     |

| SSTL18D_I <sup>2</sup> ,<br>SSTL18D_II <sup>2</sup>   | 1.71                                  | 1.8               | 1.89            | _          | _                    | _     |

| SSTL25D_ I <sup>2</sup> ,<br>SSTL25D_II <sup>2</sup>  | 2.375                                 | 2.5               | 2.625           | _          | _                    | _     |

| SSTL33D_ I <sup>2</sup> ,<br>SSTL33D_ II <sup>2</sup> | 3.135                                 | 3.3               | 3.465           | —          | —                    | —     |

| HSTL15D_ I <sup>2</sup>                               | 1.425                                 | 1.5               | 1.575           |            | —                    | —     |

| HSTL18D_ I²,<br>HSTL18D_ II²                          | 1.71                                  | 1.8               | 1.89            | —          | _                    | —     |

#### **Over Recommended Operating Conditions**

1. Inputs on chip. Outputs are implemented with the addition of external resistors. 2. Input on this standard does not depend on the value of  $V_{CCIO}$ .

## BLVDS

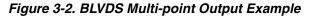

The LatticeXP2 devices support the BLVDS standard. This standard is emulated using complementary LVCMOS outputs in conjunction with a parallel external resistor across the driver outputs. BLVDS is intended for use when multi-drop and bi-directional multi-point differential signaling is required. The scheme shown in Figure 3-2 is one possible solution for bi-directional multi-point differential signals.

#### Table 3-2. BLVDS DC Conditions<sup>1</sup>

|                   |                                                      | Typical          |                  |       |

|-------------------|------------------------------------------------------|------------------|------------------|-------|

| Parameter         | Description                                          | <b>Ζο = 45</b> Ω | <b>Ζο = 90</b> Ω | Units |

| V <sub>CCIO</sub> | Output Driver Supply (+/- 5%)                        | 2.50             | 2.50             | V     |

| Z <sub>OUT</sub>  | Driver Impedance                                     | 10.00            | 10.00            | Ω     |

| R <sub>S</sub>    | Driver Series Resistor (+/- 1%)                      | 90.00            | 90.00            | Ω     |

| R <sub>TL</sub>   | Driver Parallel Resistor (+/- 1%)                    | 45.00            | 90.00            | Ω     |

| R <sub>TR</sub>   | Receiver Termination (+/- 1%)                        | 45.00            | 90.00            | Ω     |

| V <sub>OH</sub>   | Output High Voltage (After R <sub>TL</sub> )         | 1.38             | 1.48             | V     |

| V <sub>OL</sub>   | Output Low Voltage (After R <sub>TL</sub> )          | 1.12             | 1.02             | V     |

| V <sub>OD</sub>   | Output Differential Voltage (After R <sub>TL</sub> ) | 0.25             | 0.46             | V     |

| V <sub>CM</sub>   | Output Common Mode Voltage                           | 1.25             | 1.25             | V     |

| I <sub>DC</sub>   | DC Output Current                                    | 11.24            | 10.20            | mA    |

**Over Recommended Operating Conditions**

1. For input buffer, see LVDS table.

## LVPECL

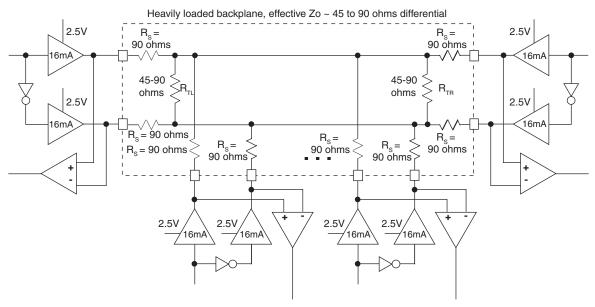

The LatticeXP2 devices support the differential LVPECL standard. This standard is emulated using complementary LVCMOS outputs in conjunction with a parallel resistor across the driver outputs. The LVPECL input standard is supported by the LVDS differential input buffer. The scheme shown in Figure 3-3 is one possible solution for point-to-point signals.

#### Figure 3-3. Differential LVPECL

#### Table 3-3. LVPECL DC Conditions<sup>1</sup>

| Parameter         | Description                                         | Typical | Units |

|-------------------|-----------------------------------------------------|---------|-------|

| V <sub>CCIO</sub> | Output Driver Supply (+/-5%)                        | 3.30    | V     |

| Z <sub>OUT</sub>  | Driver Impedance                                    | 10      | Ω     |

| R <sub>S</sub>    | Driver Series Resistor (+/-1%)                      | 93      | Ω     |

| R <sub>P</sub>    | Driver Parallel Resistor (+/-1%)                    | 196     | Ω     |

| R <sub>T</sub>    | Receiver Termination (+/-1%)                        | 100     | Ω     |

| V <sub>OH</sub>   | Output High Voltage (After R <sub>P</sub> )         | 2.05    | V     |

| V <sub>OL</sub>   | Output Low Voltage (After R <sub>P</sub> )          | 1.25    | V     |

| V <sub>OD</sub>   | Output Differential Voltage (After R <sub>P</sub> ) | 0.80    | V     |

| V <sub>CM</sub>   | Output Common Mode Voltage                          | 1.65    | V     |

| Z <sub>BACK</sub> | Back Impedance                                      | 100.5   | Ω     |

| I <sub>DC</sub>   | DC Output Current                                   | 12.11   | mA    |

#### **Over Recommended Operating Conditions**

1. For input buffer, see LVDS table.

## **Register-to-Register Performance (Continued)**

| Function                         | -7 Timing | Units |

|----------------------------------|-----------|-------|

| DSP IP Functions                 |           |       |

| 16-Tap Fully-Parallel FIR Filter | 198       | MHz   |

| 1024-pt FFT                      | 221       | MHz   |

| 8X8 Matrix Multiplication        | 196       | MHz   |

1. These timing numbers were generated using the ispLEVER design tool. Exact performance may vary with device, design and tool version. The tool uses internal parameters that have been characterized but are not tested on every device.

# **Derating Timing Tables**

Logic timing provided in the following sections of this data sheet and the Diamond design tools are worst case numbers in the operating range. Actual delays at nominal temperature and voltage for best case process, can be much better than the values given in the tables. The Diamond design tool can provide logic timing numbers at a particular temperature and voltage.

# LatticeXP2 External Switching Characteristics (Continued)

|                          |                                                                  |        | -7   |      | -6   |      | -5   |      |       |

|--------------------------|------------------------------------------------------------------|--------|------|------|------|------|------|------|-------|

| Parameter                | Description                                                      | Device | Min. | Max. | Min. | Max. | Min. | Max. | Units |

|                          |                                                                  | XP2-5  | 0.00 | —    | 0.00 | —    | 0.00 | —    | ns    |

|                          |                                                                  | XP2-8  | 0.00 | —    | 0.00 | —    | 0.00 | —    | ns    |

| t <sub>H_DELPLL</sub>    | Clock to Data Hold - PIO Input<br>Register with Input Data Delay | XP2-17 | 0.00 | —    | 0.00 | —    | 0.00 | —    | ns    |

|                          |                                                                  | XP2-30 | 0.00 | —    | 0.00 | —    | 0.00 | —    | ns    |

|                          |                                                                  | XP2-40 | 0.00 | —    | 0.00 | —    | 0.00 |      | ns    |

| DDR <sup>2</sup> and DDI | R2 <sup>3</sup> I/O Pin Parameters                               |        | •    | •    |      | •    | •    |      | •     |

| t <sub>DVADQ</sub>       | Data Valid After DQS<br>(DDR Read)                               | XP2    | _    | 0.29 | —    | 0.29 | —    | 0.29 | UI    |

| t <sub>DVEDQ</sub>       | Data Hold After DQS<br>(DDR Read)                                | XP2    | 0.71 | —    | 0.71 | —    | 0.71 | _    | UI    |

| t <sub>DQVBS</sub>       | Data Valid Before DQS                                            | XP2    | 0.25 | —    | 0.25 | —    | 0.25 | —    | UI    |

| t <sub>DQVAS</sub>       | Data Valid After DQS                                             | XP2    | 0.25 | —    | 0.25 | —    | 0.25 |      | UI    |

| f <sub>MAX_DDR</sub>     | DDR Clock Frequency                                              | XP2    | 95   | 200  | 95   | 166  | 95   | 133  | MHz   |

| f <sub>MAX_DDR2</sub>    | DDR Clock Frequency                                              | XP2    | 133  | 200  | 133  | 200  | 133  | 166  | MHz   |

| Primary Clock            | C C C C C C C C C C C C C C C C C C C                            |        |      |      |      |      |      |      |       |

| f <sub>MAX_PRI</sub>     | Frequency for Primary Clock<br>Tree                              | XP2    | _    | 420  | —    | 357  | —    | 311  | MHz   |

| t <sub>W_PRI</sub>       | Clock Pulse Width for Primary<br>Clock                           | XP2    | 1    | —    | 1    | —    | 1    | _    | ns    |

| t <sub>SKEW_PRI</sub>    | Primary Clock Skew Within a Bank                                 | XP2    | _    | 160  | —    | 160  | —    | 160  | ps    |

| Edge Clock (E            | CLK1 and ECLK2)                                                  |        | •    | •    |      | •    | •    |      | •     |

| f <sub>MAX_ECLK</sub>    | Frequency for Edge Clock                                         | XP2    | —    | 420  |      | 357  | —    | 311  | MHz   |

| <sup>t</sup> w_eclk      | Clock Pulse Width for Edge<br>Clock                              | XP2    | 1    | —    | 1    | —    | 1    | —    | ns    |

| t <sub>SKEW_ECLK</sub>   | Edge Clock Skew Within an<br>Edge of the Device                  | XP2    | -    | 130  | —    | 130  | —    | 130  | ps    |

## **Over Recommended Operating Conditions**

1. General timing numbers based on LVCMOS 2.5, 12mA, 0pf load.

2. DDR timing numbers based on SSTL25.

3. DDR2 timing numbers based on SSTL18.

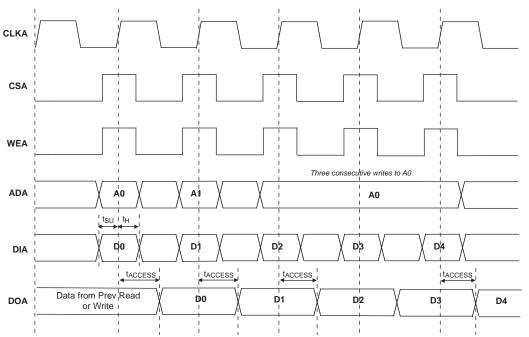

Note: Input data and address are registered at the positive edge of the clock and output data appears after the positive edge of the clock.

# LatticeXP2 Family Timing Adders<sup>1, 2, 3, 4</sup> (Continued)

| Buffer Type   | Description                              | -7    | -6    | -5    | Units |

|---------------|------------------------------------------|-------|-------|-------|-------|

| HSTL15_I      | HSTL_15 class I 4mA drive                | 0.32  | 0.69  | 1.06  | ns    |

| HSTL15D_I     | Differential HSTL 15 class I 4mA drive   | 0.32  | 0.69  | 1.06  | ns    |

| SSTL33_I      | SSTL_3 class I                           | -0.25 | 0.05  | 0.35  | ns    |

| SSTL33_II     | SSTL_3 class II                          | -0.31 | -0.02 | 0.27  | ns    |

| SSTL33D_I     | Differential SSTL_3 class I              | -0.25 | 0.05  | 0.35  | ns    |

| SSTL33D_II    | Differential SSTL_3 class II             | -0.31 | -0.02 | 0.27  | ns    |

| SSTL25_I      | SSTL_2 class I 8mA drive                 | -0.25 | 0.02  | 0.30  | ns    |

| SSTL25_II     | SSTL_2 class II 16mA drive               | -0.28 | 0.00  | 0.28  | ns    |

| SSTL25D_I     | Differential SSTL_2 class I 8mA drive    | -0.25 | 0.02  | 0.30  | ns    |

| SSTL25D_II    | Differential SSTL_2 class II 16mA drive  | -0.28 | 0.00  | 0.28  | ns    |

| SSTL18_I      | SSTL_1.8 class I                         | -0.17 | 0.13  | 0.43  | ns    |

| SSTL18_II     | SSTL_1.8 class II 8mA drive              | -0.18 | 0.12  | 0.42  | ns    |

| SSTL18D_I     | Differential SSTL_1.8 class I            | -0.17 | 0.13  | 0.43  | ns    |

| SSTL18D_II    | Differential SSTL_1.8 class II 8mA drive | -0.18 | 0.12  | 0.42  | ns    |

| LVTTL33_4mA   | LVTTL 4mA drive                          | -0.37 | -0.05 | 0.26  | ns    |

| LVTTL33_8mA   | LVTTL 8mA drive                          | -0.45 | -0.18 | 0.10  | ns    |

| LVTTL33_12mA  | LVTTL 12mA drive                         | -0.52 | -0.24 | 0.04  | ns    |

| LVTTL33_16mA  | LVTTL 16mA drive                         | -0.43 | -0.14 | 0.14  | ns    |

| LVTTL33_20mA  | LVTTL 20mA drive                         | -0.46 | -0.18 | 0.09  | ns    |

| LVCMOS33_4mA  | LVCMOS 3.3 4mA drive, fast slew rate     | -0.37 | -0.05 | 0.26  | ns    |

| LVCMOS33_8mA  | LVCMOS 3.3 8mA drive, fast slew rate     | -0.45 | -0.18 | 0.10  | ns    |

| LVCMOS33_12mA | LVCMOS 3.3 12mA drive, fast slew rate    | -0.52 | -0.24 | 0.04  | ns    |

| LVCMOS33_16mA | LVCMOS 3.3 16mA drive, fast slew rate    | -0.43 | -0.14 | 0.14  | ns    |

| LVCMOS33_20mA | LVCMOS 3.3 20mA drive, fast slew rate    | -0.46 | -0.18 | 0.09  | ns    |

| LVCMOS25_4mA  | LVCMOS 2.5 4mA drive, fast slew rate     | -0.42 | -0.15 | 0.13  | ns    |

| LVCMOS25_8mA  | LVCMOS 2.5 8mA drive, fast slew rate     | -0.48 | -0.21 | 0.05  | ns    |

| LVCMOS25_12mA | LVCMOS 2.5 12mA drive, fast slew rate    | 0.00  | 0.00  | 0.00  | ns    |

| LVCMOS25_16mA | LVCMOS 2.5 16mA drive, fast slew rate    | -0.45 | -0.18 | 0.08  | ns    |

| LVCMOS25_20mA | LVCMOS 2.5 20mA drive, fast slew rate    | -0.49 | -0.22 | 0.04  | ns    |

| LVCMOS18_4mA  | LVCMOS 1.8 4mA drive, fast slew rate     | -0.46 | -0.18 | 0.10  | ns    |

| LVCMOS18_8mA  | LVCMOS 1.8 8mA drive, fast slew rate     | -0.52 | -0.25 | 0.02  | ns    |

| LVCMOS18_12mA | LVCMOS 1.8 12mA drive, fast slew rate    | -0.56 | -0.30 | -0.03 | ns    |

| LVCMOS18_16mA | LVCMOS 1.8 16mA drive, fast slew rate    | -0.50 | -0.24 | 0.03  | ns    |

| LVCMOS15_4mA  | LVCMOS 1.5 4mA drive, fast slew rate     | -0.45 | -0.17 | 0.11  | ns    |

| LVCMOS15_8mA  | LVCMOS 1.5 8mA drive, fast slew rate     | -0.53 | -0.26 | 0.00  | ns    |

| LVCMOS12_2mA  | LVCMOS 1.2 2mA drive, fast slew rate     | -0.46 | -0.19 | 0.08  | ns    |

| LVCMOS12_6mA  | LVCMOS 1.2 6mA drive, fast slew rate     | -0.55 | -0.29 | -0.02 | ns    |

| LVCMOS33_4mA  | LVCMOS 3.3 4mA drive, slow slew rate     | 0.98  | 1.41  | 1.84  | ns    |

| LVCMOS33_8mA  | LVCMOS 3.3 8mA drive, slow slew rate     | 0.74  | 1.16  | 1.58  | ns    |

| LVCMOS33_12mA | LVCMOS 3.3 12mA drive, slow slew rate    | 0.56  | 0.97  | 1.38  | ns    |

| LVCMOS33_16mA | LVCMOS 3.3 16mA drive, slow slew rate    | 0.77  | 1.19  | 1.61  | ns    |

| LVCMOS33_20mA | LVCMOS 3.3 20mA drive, slow slew rate    | 0.57  | 0.98  | 1.40  | ns    |

## **Over Recommended Operating Conditions**

# sysCLOCK PLL Timing

| Parameter                      | Description                              | Conditions                               | Min.  | Тур. | Max.  | Units |

|--------------------------------|------------------------------------------|------------------------------------------|-------|------|-------|-------|

| f <sub>IN</sub>                | Input Clock Frequency (CLKI, CLKFB)      |                                          | 10    | —    | 435   | MHz   |

| f <sub>OUT</sub>               | Output Clock Frequency (CLKOP,<br>CLKOS) |                                          | 10    | _    | 435   | MHz   |

| f                              | K-Divider Output Frequency               | CLKOK                                    | 0.078 | —    | 217.5 | MHz   |

| f <sub>OUT2</sub>              | R-Divider Output Frequency               | CLKOK2                                   | 3.3   |      | 145   | MHz   |

| f <sub>VCO</sub>               | PLL VCO Frequency                        |                                          | 435   |      | 870   | MHz   |

| f <sub>PFD</sub>               | Phase Detector Input Frequency           |                                          | 10    |      | 435   | MHz   |

| AC Characte                    | eristics                                 | •                                        |       |      | •     |       |

| t <sub>DT</sub>                | Output Clock Duty Cycle                  | Default duty cycle selected <sup>3</sup> | 45    | 50   | 55    | %     |

| t <sub>CPA</sub>               | Coarse Phase Adjust                      |                                          | -5    | 0    | 5     | %     |

| t <sub>PH</sub> <sup>4</sup>   | Output Phase Accuracy                    |                                          | -5    | 0    | 5     | %     |

|                                |                                          | f <sub>OUT</sub> > 400 MHz               | _     |      | ±50   | ps    |

| t <sub>OPJIT</sub> 1           | Output Clock Period Jitter               | 100 MHz < f <sub>OUT</sub> < 400 MHz     | _     |      | ±125  | ps    |

|                                |                                          | f <sub>OUT</sub> < 100 MHz               | _     |      | 0.025 | UIPP  |

| t <sub>SK</sub>                | Input Clock to Output Clock Skew         | N/M = integer                            |       |      | ±240  | ps    |

| t <sub>OPW</sub>               | Output Clock Pulse Width                 | At 90% or 10%                            | 1     |      | —     | ns    |

| <b>•</b> 2                     | PLL Lock-in Time                         | 25 to 435 MHz                            | _     |      | 50    | μs    |

| t <sub>LOCK</sub> <sup>2</sup> |                                          | 10 to 25 MHz                             | _     |      | 100   | μs    |

| t <sub>IPJIT</sub>             | Input Clock Period Jitter                |                                          | —     |      | ±200  | ps    |

| t <sub>FBKDLY</sub>            | External Feedback Delay                  |                                          |       |      | 10    | ns    |

| t <sub>HI</sub>                | Input Clock High Time                    | 90% to 90%                               | 0.5   |      | —     | ns    |

| t <sub>LO</sub>                | Input Clock Low Time                     | 10% to 10%                               | 0.5   | —    | —     | ns    |

| t <sub>RSTKW</sub>             | Reset Signal Pulse Width (RSTK)          |                                          | 10    | —    | —     | ns    |

| t <sub>RSTW</sub>              | Reset Signal Pulse Width (RST)           |                                          | 500   | —    | —     | ns    |

#### **Over Recommended Operating Conditions**

1. Jitter sample is taken over 10,000 samples of the primary PLL output with clean reference clock.

2. Output clock is valid after t<sub>LOCK</sub> for PLL reset and dynamic delay adjustment.

3. Using LVDS output buffers.

4. Relative to CLKOP.

## **Switching Test Conditions**

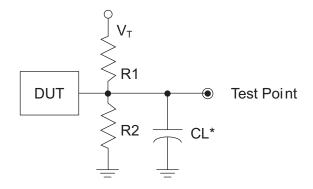

Figure 3-11 shows the output test load that is used for AC testing. The specific values for resistance, capacitance, voltage, and other test conditions are shown in Table 3-6.

#### Figure 3-11. Output Test Load, LVTTL and LVCMOS Standards

\*CL Includes Test Fixture and Probe Capacitance

Table 3-6. Test Fixture Required Components, Non-Terminated Interfaces

| Test Condition                                   | R <sub>1</sub> | R <sub>2</sub> | CL  | Timing Ref.                       | VT                |

|--------------------------------------------------|----------------|----------------|-----|-----------------------------------|-------------------|

| LVTTL and other LVCMOS settings (L -> H, H -> L) | x              | œ              | 0pF | LVCMOS 3.3 = 1.5V                 | —                 |

|                                                  |                |                |     | LVCMOS 2.5 = $V_{CCIO}/2$         | —                 |

|                                                  |                |                |     | LVCMOS 1.8 = V <sub>CCIO</sub> /2 | —                 |

|                                                  |                |                |     | LVCMOS 1.5 = $V_{CCIO}/2$         | —                 |

|                                                  |                |                |     | LVCMOS 1.2 = V <sub>CCIO</sub> /2 | —                 |

| LVCMOS 2.5 I/O (Z -> H)                          | $\infty$       | 1MΩ            |     | V <sub>CCIO</sub> /2              | —                 |

| LVCMOS 2.5 I/O (Z -> L)                          | 1MΩ            | $\infty$       |     | V <sub>CCIO</sub> /2              | V <sub>CCIO</sub> |

| LVCMOS 2.5 I/O (H -> Z)                          | $\infty$       | 100            |     | V <sub>OH</sub> - 0.10            | —                 |

| LVCMOS 2.5 I/O (L -> Z)                          | 100            | $\infty$       |     | V <sub>OL</sub> + 0.10            | V <sub>CCIO</sub> |

Note: Output test conditions for all other interfaces are determined by the respective standards.

# LatticeXP2 Family Data Sheet Ordering Information

#### February 2012

Data Sheet DS1009

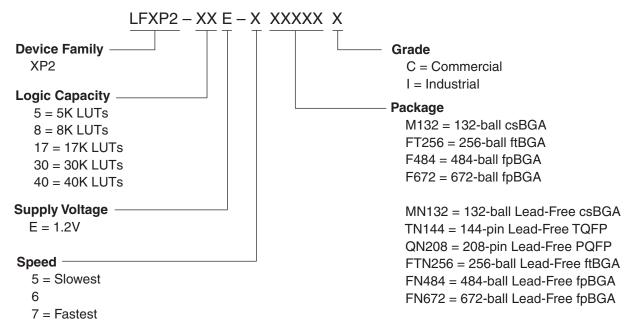

## **Part Number Description**

## **Ordering Information**

The LatticeXP2 devices are marked with a single temperature grade, either Commercial or Industrial, as shown below.

© 2012 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

# LatticeXP2 Family Data Sheet Supplemental Information

#### February 2012

Data Sheet DS1009

## **For Further Information**

A variety of technical notes for the LatticeXP2 FPGA family are available on the Lattice Semiconductor web site at <u>www.latticesemi.com</u>.

- TN1136, LatticeXP2 sysIO Usage Guide

- TN1137, LatticeXP2 Memory Usage Guide

- TN1138, LatticeXP2 High Speed I/O Interface

- TN1126, LatticeXP2 sysCLOCK PLL Design and Usage Guide

- TN1139, Power Estimation and Management for LatticeXP2 Devices

- TN1140, LatticeXP2 sysDSP Usage Guide

- TN1141, LatticeXP2 sysCONFIG Usage Guide

- TN1142, LatticeXP2 Configuration Encryption and Security Usage Guide

- TN1087, Minimizing System Interruption During Configuration Using TransFR Technology

- TN1220, LatticeXP2 Dual Boot Feature

- TN1130, LatticeXP2 Soft Error Detection (SED) Usage Guide

- TN1143, LatticeXP2 Hardware Checklist

For further information on interface standards refer to the following websites:

- JEDEC Standards (LVTTL, LVCMOS, SSTL, HSTL): www.jedec.org

- PCI: <u>www.pcisig.com</u>

© 2012 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

# LatticeXP2 Family Data Sheet Revision History

September 2014

Data Sheet DS1009

## **Revision History**

|                                                                                              | Version         | Section                                                                                                                                                                                                                 | Change Summary                                                                                                                                                                                                                                                     |  |  |

|----------------------------------------------------------------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| May 2007                                                                                     | 01.1            | _                                                                                                                                                                                                                       | Initial release.                                                                                                                                                                                                                                                   |  |  |

| September 2007                                                                               | 01.2            | 01.2 DC and Switching<br>Characteristics Added JTAG Port Timing Waveforms diagram.                                                                                                                                      |                                                                                                                                                                                                                                                                    |  |  |

|                                                                                              |                 |                                                                                                                                                                                                                         | Updated sysCLOCK PLL Timing table.                                                                                                                                                                                                                                 |  |  |

|                                                                                              |                 | Pinout Information                                                                                                                                                                                                      | Added Thermal Management text section.                                                                                                                                                                                                                             |  |  |

| February 2008       01.3       Architecture         DC and Switching       DC haracteristics | 01.3            | Architecture                                                                                                                                                                                                            | Added LVCMOS33D to Supported Output Standards table.                                                                                                                                                                                                               |  |  |

|                                                                                              |                 |                                                                                                                                                                                                                         | Clarified: "This Flash can be programmed through either the JTAG or<br>Slave SPI ports of the device. The SRAM configuration space can also<br>be infinitely reconfigured through the JTAG and Master SPI ports."                                                  |  |  |

|                                                                                              |                 |                                                                                                                                                                                                                         | Added External Slave SPI Port to Serial TAG Memory section. Updated Serial TAG Memory diagram.                                                                                                                                                                     |  |  |

|                                                                                              |                 |                                                                                                                                                                                                                         | Updated Flash Programming Specifications table.                                                                                                                                                                                                                    |  |  |

|                                                                                              |                 |                                                                                                                                                                                                                         | Added "8W" specification to Hot Socketing Specifications table.                                                                                                                                                                                                    |  |  |

|                                                                                              |                 |                                                                                                                                                                                                                         | Updated Timing Tables                                                                                                                                                                                                                                              |  |  |

|                                                                                              |                 |                                                                                                                                                                                                                         | Clarifications for IIH in DC Electrical Characteristics table.                                                                                                                                                                                                     |  |  |

|                                                                                              |                 |                                                                                                                                                                                                                         | Added LVCMOS33D section                                                                                                                                                                                                                                            |  |  |

|                                                                                              |                 | Updated DOA and DOA (Regs) to EBR Timing diagrams.                                                                                                                                                                      |                                                                                                                                                                                                                                                                    |  |  |

|                                                                                              |                 | Removed Master Clock Frequency and Duty Cycle sections from the LatticeXP2 sysCONFIG Port Timing Specifications table. These are listed on the On-chip Oscillator and Configuration Master Clock Characteristics table. |                                                                                                                                                                                                                                                                    |  |  |

|                                                                                              |                 | Changed CSSPIN to CSSPISN in description of $t_{SCS},t_{SCSS},$ and $t_{SCSH}$ parameters. Removed $t_{SOE}$ parameter.                                                                                                 |                                                                                                                                                                                                                                                                    |  |  |

|                                                                                              |                 |                                                                                                                                                                                                                         | Clarified On-chip Oscillator documentation                                                                                                                                                                                                                         |  |  |

|                                                                                              |                 |                                                                                                                                                                                                                         | Added Switching Test Conditions                                                                                                                                                                                                                                    |  |  |

|                                                                                              |                 | Pinout Information                                                                                                                                                                                                      | Added "True LVDS Pairs Bonding Out per Bank," "DDR Banks Bonding<br>Out per I/O Bank," and "PCI capable I/Os Bonding Out per Bank" to Pin<br>Information Summary in place of previous blank table "PCI and DDR<br>Capabilities of the Device-Package Combinations" |  |  |

|                                                                                              |                 |                                                                                                                                                                                                                         | Removed pinout listing. This information is available on the LatticeXP2 product web pages                                                                                                                                                                          |  |  |

|                                                                                              |                 | Ordering Information                                                                                                                                                                                                    | Added XP2-17 "8W" and all other family OPNs.                                                                                                                                                                                                                       |  |  |

| April 2008                                                                                   | 01.4            | DC and Switching                                                                                                                                                                                                        | Updated Absolute Maximum Ratings footnotes.                                                                                                                                                                                                                        |  |  |

| Chara                                                                                        | Characteristics | Updated Recommended Operating Conditions Table footnotes.                                                                                                                                                               |                                                                                                                                                                                                                                                                    |  |  |

|                                                                                              |                 |                                                                                                                                                                                                                         | Updated Supply Current (Standby) Table                                                                                                                                                                                                                             |  |  |

|                                                                                              |                 |                                                                                                                                                                                                                         | Updated Initialization Supply Current Table                                                                                                                                                                                                                        |  |  |

|                                                                                              |                 |                                                                                                                                                                                                                         | Updated Programming and Erase Flash Supply Current Table                                                                                                                                                                                                           |  |  |

|                                                                                              |                 |                                                                                                                                                                                                                         | Updated Register to Register Performance Table                                                                                                                                                                                                                     |  |  |

|                                                                                              |                 |                                                                                                                                                                                                                         | Updated LatticeXP2 External Switching Characteristics Table                                                                                                                                                                                                        |  |  |

|                                                                                              |                 |                                                                                                                                                                                                                         | Updated LatticeXP2 Internal Switching Characteristics Table                                                                                                                                                                                                        |  |  |

|                                                                                              |                 |                                                                                                                                                                                                                         | Updated sysCLOCK PLL Timing Table                                                                                                                                                                                                                                  |  |  |

© 2014 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.