Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 11                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 11x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

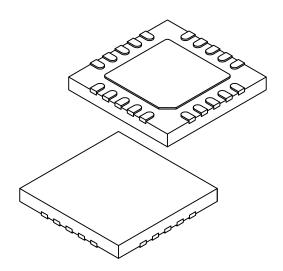

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 16-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 16-QFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1554-e-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name                                                                     | Function | Input<br>Type    | Output<br>Type | Description                            |  |  |

|--------------------------------------------------------------------------|----------|------------------|----------------|----------------------------------------|--|--|

|                                                                          | RA0      | TTL              | CMOS           | General Purpose I/O                    |  |  |

|                                                                          | AN0      | AN               | _              | ADC Channel Input                      |  |  |

| RA0/AN0/ISCPDAT/ICDDAT                                                   | ICSPDAT  | ST               | CMOS           | ICSP™ Data I/O                         |  |  |

|                                                                          | ICDDAT   | ST               | CMOS           | In-Circuit Debug Data                  |  |  |

|                                                                          | RA1      | TTL              | CMOS           | General Purpose I/O                    |  |  |

|                                                                          | AN1      | AN               | _              | ADC Channel Input                      |  |  |

| RA1/AN1/VREF+/ICSPCLK/ICDCLK                                             | VREF+    | AN               | _              | ADC Positive Voltage Reference Input   |  |  |

|                                                                          | ICSPCLK  | ST               | CMOS           | ICSP Programming Clock                 |  |  |

|                                                                          | ICDCLK   | ST               | CMOS           | In-Circuit Debug Clock                 |  |  |

|                                                                          | RA2      | TTL              | CMOS           | General Purpose I/O                    |  |  |

|                                                                          | AN2      | AN               | _              | ADC Channel Input                      |  |  |

| RA2/AN2/TOCKI/INT/                                                       | TOCKI    | ST               | —              | Timer0 Clock Input                     |  |  |

|                                                                          | INT      | ST               | _              | External Interrupt                     |  |  |

|                                                                          | RA3      | TTL              | CMOS           | General Purpose Input with IOC and WPU |  |  |

|                                                                          | Vpp      | HV               | _              | Programming Voltage                    |  |  |

| RA3/VPP/SS <sup>(1)</sup> /SDA <sup>(1)</sup> /SDI <sup>(1)</sup> / MCLR | SS       | ST               | _              | Slave Select Input                     |  |  |

|                                                                          | SDA      | l <sup>2</sup> C | OD             | I <sup>2</sup> C Data Input/Output     |  |  |

|                                                                          | SDI      | CMOS             | _              | SPI Data Input                         |  |  |

|                                                                          | MCLR     | ST               | _              | Master Clear with Internal Pull-up     |  |  |

|                                                                          | RA4      | TTL              | CMOS           | General Purpose I/O                    |  |  |

|                                                                          | AN10     | AN               | -              | ADC Channel Input                      |  |  |

|                                                                          | ADTRIG   | ST               | _              | ADC Conversion Trigger Input           |  |  |

| RA4/AN10/ADTRIG/CLKOUT/                                                  | CLKOUT   | —                | CMOS           | Fosc/4 Output                          |  |  |

| RX <sup>(1)</sup> /DT <sup>(1)</sup> /SDO <sup>(1)</sup> /T1G            | RX       | ST               | _              | USART Asynchronous Input               |  |  |

|                                                                          | DT       | ST               | CMOS           | USART Synchronous Data                 |  |  |

|                                                                          | SDO      | _                | CMOS           | SPI Data Output                        |  |  |

|                                                                          | T1G      | ST               | _              | Timer1 Gate Input                      |  |  |

|                                                                          | RA5      | TTL              | CMOS           | General Purpose I/O                    |  |  |

|                                                                          | AN20     | AN               | _              | ADC Channel Input                      |  |  |

| RA5/AN20/CLKIN/T1CKI                                                     | CLKIN    | CMOS             | _              | External Clock Input (EC mode)         |  |  |

|                                                                          | T1CKI    | ST               | _              | Timer1 Clock Input                     |  |  |

|                                                                          | RC0      | TTL              | CMOS           | General Purpose I/O                    |  |  |

|                                                                          | AN13     | AN               | _              | ADC Channel Input                      |  |  |

| RC0/AN13/SCL/SCK                                                         | SCL      | l <sup>2</sup> C | OD             | I <sup>2</sup> C Clock                 |  |  |

|                                                                          | SCK      | ST               | CMOS           | SPI Clock                              |  |  |

TABLE 1-2: PIC16LF1554 PINOUT DESCRIPTION

**Note 1:** Alternate pin function selected with the APFCON (Register 11-1) register.

#### **TABLE 1-3:** PIC16LF1559 PINOUT DESCRIPTION (CONTINUED)

|                                     |          |               | -              |                           |

|-------------------------------------|----------|---------------|----------------|---------------------------|

| Name                                | Function | Input<br>Type | Output<br>Type | Description               |

|                                     | RC6      | TTL           | CMOS           | General Purpose I/O       |

| RC6/AN14/SS <sup>(1)</sup>          | AN14     | AN            |                | ADC Channel Input         |

|                                     | SS       | ST            |                | Slave Select Input        |

|                                     | RC7      | TTL           | CMOS           | General Purpose I/O       |

| RC7/AN24/SDO                        | AN24     | AN            |                | ADC Channel Input         |

|                                     | SDO      | —             | CMOS           | SPI Data Output           |

| Legend: AN = Analog input or output | CMOS= CN | /IOS compa    | atible input   | or output OD = Open-Drain |

Legend: AN = Analog input or output CMOS = CMOS compatible input or output OD

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels  $I^2C$ = Schmitt Trigger input with  $I^2C$ HV = High Voltage XTAL = Crystal levels

Note 1: Alternate pin function selected with the APFCON (Register 11-1) register.

| Address | Name                               | Bit 7        | Bit 6                       | Bit 5          | Bit 4            | Bit 3           | Bit 2           | Bit 1          | Bit 0         | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|------------------------------------|--------------|-----------------------------|----------------|------------------|-----------------|-----------------|----------------|---------------|-----------------------|---------------------------------|

| Bank 1  |                                    |              |                             |                |                  |                 |                 |                |               |                       |                                 |

| 080h    | INDF0 <sup>(1)</sup>               | Addressing t | his location us             | es contents of | FSR0H/FSR0       | L to address    | data memory     | y (not a physi | cal register) | xxxx xxxx             | uuuu uuuu                       |

| 081h    | INDF1 <sup>(1)</sup>               | Addressing t | his location us             | es contents of | FSR1H/FSR1       | L to address    | data memory     | y (not a physi | cal register) | xxxx xxxx             | uuuu uuuu                       |

| 082h    | PCL <sup>(1)</sup>                 |              |                             | Program C      | ounter (PC) L    | east Significa  | int Byte        |                |               | 0000 0000             | 0000 0000                       |

| 083h    | STATUS <sup>(1)</sup>              | _            | —                           | _              | TO               | PD              | Z               | DC             | С             | 1 1000                | q quuu                          |

| 084h    | FSR0L <sup>(1)</sup>               |              |                             | Indirect Da    | ita Memory Ad    | dress 0 Low     | Pointer         |                |               | 0000 0000             | uuuu uuuu                       |

| 085h    | FSR0H <sup>(1)</sup>               |              |                             | Indirect Da    | ta Memory Ad     | dress 0 High    | Pointer         |                |               | 0000 0000             | 0000 0000                       |

| 086h    | FSR1L <sup>(1)</sup>               |              |                             | Indirect Da    | ita Memory Ad    | dress 1 Low     | Pointer         |                |               | 0000 0000             | uuuu uuuu                       |

| 087h    | FSR1H <sup>(1)</sup>               |              |                             | Indirect Da    | ta Memory Ad     | dress 1 High    | Pointer         |                |               | 0000 0000             | 0000 0000                       |

| 088h    | BSR <sup>(1)</sup>                 | _            | _                           | _              |                  |                 | BSR<4:0>        |                |               | 0 0000                | 0 0000                          |

| 089h    | WREG <sup>(1)</sup>                |              |                             |                | Working Re       | egister         |                 |                |               | 0000 0000             | uuuu uuuu                       |

| 08Ah    | PCLATH <sup>(1)</sup>              | _            |                             | Write But      | ffer for the upp | er 7 bits of th | e Program C     | ounter         |               | -000 0000             | -000 0000                       |

| 08Bh    | INTCON <sup>(1)</sup>              | GIE          | PEIE                        | TMR0IE         | INTE             | IOCIE           | TMR0IF          | INTF           | IOCIF         | 0000 0000             | 0000 0000                       |

| 08Ch    | TRISA                              | _            | _                           | TRISA5         | TRISA4           | _               | TRISA2          | TRISA1         | TRISA0        | 11 1111               | 11 1111                         |

| 08Dh    | TRISB <sup>(2)</sup>               |              |                             |                | Unimplem         | ented           |                 |                |               | _                     | _                               |

| 06011   | TRISB <sup>(3)</sup>               | TRISB7       | TRISB6                      | TRISB5         | TRISB4           | _               | _               | _              | _             | 1111                  | 1111                            |

| 08Eh    | TRISC <sup>(2)</sup>               |              |                             | TRISC5         | TRISC4           | TRISC3          | TRISC2          | TRISC1         | TRISC0        | 11 1111               | 11 1111                         |

| UOEII   | TRISC <sup>(3)</sup>               | TRISC7       | TRISC6                      | TRISC5         | TRISC4           | TRISC3          | TRISC2          | TRISC1         | TRISC0        | 1111 1111             | 1111 1111                       |

| 091h    | PIE1                               | TMR1GIE      | AD1IE                       | RCIE           | TXIE             | SSP1IE          |                 | TMR2IE         | TMR1IE        | 0000 0-00             | 0000 0-00                       |

| 092h    | PIE2                               |              | AD2IE                       |                |                  | BCLIE           |                 | —              | —             | -0 0                  | -0 0                            |

| 095h    | OPTION_REG                         | WPUEN        | INTEDG                      | TMR0CS         | TMR0SE           | PSA             |                 | PS<2:0>        |               | 1111 1111             | 1111 1111                       |

| 096h    | PCON                               | STKOVF       | STKUNF                      |                | RWDT             | RMCLR           | RI              | POR            | BOR           | 00-1 11qq             | 00-q qquu                       |

| 097h    | WDTCON                             |              |                             |                | W                | /DTPS<4:0>      |                 |                | SWDTEN        | 01 0110               | 01 0110                         |

| 098h    | —                                  |              |                             |                | Unimplem         | ented           |                 |                |               | —                     | _                               |

| 099h    | OSCCON                             | SPLLEN       |                             | IRCF<          | <3:0>            |                 |                 | SCS            | <1:0>         | 0011 1-00             | 0011 1-00                       |

| 09Ah    | OSCSTAT                            |              | PLLSR                       | _              | HFIOFR           |                 |                 | LFIOFR         | HFIOFS        | -0-000                | -d-d -d0d                       |

| 09Bh    | ADRESL/<br>AD1RES0L <sup>(4)</sup> |              |                             | A              | DC1 Result Re    | gister 0 Low    |                 |                |               | XXXX XXXX             | uuuu uuuu                       |

| 09Ch    | ADRESH/<br>AD1RES0H <sup>(4)</sup> |              | ADC1 Result Register 0 High |                |                  |                 |                 |                |               | XXXX XXXX             | uuuu uuuu                       |

| 09Dh    | ADCON0/<br>AD1CON0 <sup>(4)</sup>  | _            | CHS4                        | CHS3           | CHS2             | CHS1            | CHS0            | GO/DONE1       | AD10N         | -000 0000             | -000 0000                       |

| 09Eh    | ADCON1/<br>ADCOMCON <sup>(4)</sup> | ADFM         |                             | ADCS<2:0>      |                  | _               | GO/<br>DONE_ALL | ADPRE          | EF<1:0>       | 0000 -000             | 0000 -000                       |

| 09Fh    | ADCON2/<br>AD1CON2 <sup>(4)</sup>  | _            | 1                           | RIGSEL<2:0>    | >                | _               | _               | _              | _             | -000                  | -000                            |

#### **TABLE 3-9:** SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'. Note

These registers can be accessed from any bank. 1:

PIC16LF1554. 2:

3: PIC16LF1559.

These registers/bits are available at two address locations, in Bank 1 and Bank 14. 4:

| Address | Name                  | Bit 7         | Bit 6                                                               | Bit 5          | Bit 4            | Bit 3          | Bit 2          | Bit 1         | Bit 0          | Value on:<br>POR, BOR | Value on<br>all other |

|---------|-----------------------|---------------|---------------------------------------------------------------------|----------------|------------------|----------------|----------------|---------------|----------------|-----------------------|-----------------------|

| Bank 31 |                       |               |                                                                     |                |                  |                |                |               |                |                       | Resets                |

| F80h    | INDF0 <sup>(1)</sup>  | Addressing t  | his location us                                                     | es contents of | ESROH/ESRO       | I to address   | data memor     | v (not a nhvs | ical register) | XXXX XXXX             | uuuu uuuu             |

| F81h    | INDF1 <sup>(1)</sup>  | 0             |                                                                     | es contents of |                  |                |                |               | 0 /            | XXXX XXXX             | uuuu uuuu             |

| F82h    | PCL <sup>(1)</sup>    | / duressing t |                                                                     |                | Counter (PC) L   |                |                | y (not a phys |                | 0000 0000             | 0000 0000             |

| F83h    | STATUS <sup>(1)</sup> | _             | _                                                                   |                |                  |                | 7              | DC            | С              | 1 1000                | q quuu                |

| F84h    | FSR0L <sup>(1)</sup>  |               |                                                                     | Indirect Da    | ata Memory Ac    | . 5            | -              | 80            | Ū              | 0000 0000             | uuuu uuuu             |

| F85h    | FSR0H <sup>(1)</sup>  |               |                                                                     |                | ita Memory Ad    |                |                |               |                | 0000 0000             | 0000 0000             |

| F86h    | FSR1L <sup>(1)</sup>  |               |                                                                     |                | ata Memory Ac    | 0              |                |               |                | 0000 0000             | uuuu uuuu             |

| F87h    | FSR1H <sup>(1)</sup>  |               |                                                                     |                | ita Memory Ad    |                |                |               |                | 0000 0000             | 0000 0000             |

| F88h    | BSR <sup>(1)</sup>    |               | _                                                                   |                |                  | arcos i riigii | BSR<4:0>       |               |                | 0 0000                | 0 0000                |

| F89h    | WREG <sup>(1)</sup>   |               |                                                                     |                | Working R        | enister        | 0011-4.02      |               |                | 0000 0000             | uuuu uuuu             |

| F8Ah    | PCLATH <sup>(1)</sup> |               |                                                                     | Write Bu       | ffer for the upp | •              | Program (      | ounter        |                | -000 0000             | -000 0000             |

| F8Bh    | INTCON <sup>(1)</sup> | GIE           | PEIE                                                                | TMR0IE         |                  |                | TMR0IF         | INTF          | IOCIF          | 0000 0000             | 0000 0000             |

| F8Ch    | _                     | UIL           |                                                                     |                | Unimplem         |                | TWITCH         |               | 10011          |                       |                       |

| _       | _                     |               |                                                                     |                | Unimplem         | enteu          |                |               |                |                       |                       |

| FE2h    |                       |               |                                                                     |                |                  |                |                |               |                |                       |                       |

| FE3h    |                       |               |                                                                     |                | Unimplem         | ented          | 1              |               | 1              |                       | _                     |

| FE4h    | STATUS<br>SHAD        | —             | _                                                                   | —              | —                | —              | Z              | DC            | С              | xxx                   | uuu                   |

| FE5h    | WREG_SHAD             |               |                                                                     | Working R      | egister Norma    | l (Non-ICD) S  | Shadow         |               |                | xxxx xxxx             | uuuu uuuu             |

| FE6h    | BSR_SHAD              | —             |                                                                     | —              | Bank             | Select Regis   | ster Normal (I | Non-ICD) Sha  | adow           | x xxxx                | u uuuu                |

| FE7h    | PCLATH<br>SHAD        | —             |                                                                     | Program Cou    | nter Latch Hig   | h Register No  | ormal (Non-IC  | CD) Shadow    |                | -xxx xxxx             | uuuu uuuu             |

| FE8h    | FSR0L_SHAD            |               | Indirect Da                                                         | ata Memory Ad  | ddress 0 Low I   | Pointer Norm   | al (Non-ICD)   | Shadow        |                | xxxx xxxx             | uuuu uuuu             |

| FE9h    | FSR0H_SHAD            |               | Indirect Da                                                         | ata Memory Ac  | dress 0 High     | Pointer Norm   | al (Non-ICD)   | Shadow        |                | xxxx xxxx             | uuuu uuuu             |

| FEAh    | FSR1L_SHAD            |               | Indirect Da                                                         | ata Memory Ad  | ddress 1 Low I   | Pointer Norm   | al (Non-ICD)   | Shadow        |                | xxxx xxxx             | uuuu uuuu             |

| FEBh    | FSR1H_SHAD            |               | Indirect Data Memory Address 1 High Pointer Normal (Non-ICD) Shadow |                |                  |                |                |               |                | xxxx xxxx             | uuuu uuuu             |

| FECh    | _                     |               |                                                                     |                | Unimplem         | ented          |                |               |                | _                     | —                     |

| FEDh    | STKPTR                | —             | —                                                                   | —              |                  | Curr           | ent Stack poi  | nter          |                | 1 1111                | 1 1111                |

| FEEh    | TOSL                  |               |                                                                     |                | Top of Stack     | Low byte       |                |               |                | xxxx xxxx             | uuuu uuuu             |

| FEFh    | TOSH                  | —             |                                                                     |                | Top of           | Stack High b   | yte            |               |                | -xxx xxxx             | -uuu uuuu             |

### TABLE 3-9: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

Note 1: These registers can be accessed from any bank.

2: PIC16LF1554.

3: PIC16LF1559.

4: These registers/bits are available at two address locations, in Bank 1 and Bank 14.

### 6.12 Determining the Cause of a Reset

Upon any Reset, multiple bits in the STATUS and PCON registers are updated to indicate the cause of the Reset. Table 6-3 and Table 6-4 show the Reset conditions of these registers.

| STKOVF | STKUNF | RWDT | RMCLR | RI | POR | BOR | то | PD | Condition                                           |

|--------|--------|------|-------|----|-----|-----|----|----|-----------------------------------------------------|

| 0      | 0      | 1    | 1     | 1  | 0   | х   | 1  | 1  | Power-on Reset                                      |

| 0      | 0      | 1    | 1     | 1  | 0   | х   | 0  | x  | Illegal, TO is set on POR                           |

| 0      | 0      | 1    | 1     | 1  | 0   | x   | x  | 0  | Illegal, $\overline{PD}$ is set on $\overline{POR}$ |

| 0      | 0      | u    | 1     | 1  | u   | 0   | 1  | 1  | Brown-out Reset                                     |

| u      | u      | 0    | u     | u  | u   | u   | 0  | u  | WDT Reset                                           |

| u      | u      | u    | u     | u  | u   | u   | 0  | 0  | WDT Wake-up from Sleep                              |

| u      | u      | u    | u     | u  | u   | u   | 1  | 0  | Interrupt Wake-up from Sleep                        |

| u      | u      | u    | 0     | u  | u   | u   | u  | u  | MCLR Reset during normal operation                  |

| u      | u      | u    | 0     | u  | u   | u   | 1  | 0  | MCLR Reset during Sleep                             |

| u      | u      | u    | u     | 0  | u   | u   | u  | u  | RESET Instruction Executed                          |

| 1      | u      | u    | u     | u  | u   | u   | u  | u  | Stack Overflow Reset (STVREN = 1)                   |

| u      | 1      | u    | u     | u  | u   | u   | u  | u  | Stack Underflow Reset (STVREN = 1)                  |

TABLE 6-3: RESET STATUS BITS AND THEIR SIGNIFICANCE

### TABLE 6-4: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 0000h                 | 1 1000             | 00 110x          |

| MCLR Reset during normal operation | 0000h                 | u uuuu             | uu Ouuu          |

| MCLR Reset during Sleep            | 0000h                 | 1 Ouuu             | uu Ouuu          |

| WDT Reset                          | 0000h                 | 0 uuuu             | uu uuuu          |

| WDT Wake-up from Sleep             | PC + 1                | 0 Ouuu             | uu uuuu          |

| Brown-out Reset                    | 0000h                 | 1 luuu             | 00 11u0          |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | 1 Ouuu             | uu uuuu          |

| RESET Instruction Executed         | 0000h                 | u uuuu             | uu u0uu          |

| Stack Overflow Reset (STVREN = 1)  | 0000h                 | u uuuu             | lu uuuu          |

| Stack Underflow Reset (STVREN = 1) | 0000h                 | u uuuu             | ul uuuu          |

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and the Global Interrupt Enable bit (GIE) is set, the return address is pushed on the stack and PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

| REGISTER        |                   |                                |                  |                 | REGISTER 1               |                  |              |

|-----------------|-------------------|--------------------------------|------------------|-----------------|--------------------------|------------------|--------------|

| R/W-0/0         | R/W-0/0           | R/W-0/0                        | R/W-0/0          | R/W-0/0         | U-0                      | R/W-0/0          | R/W-0/0      |

| TMR1GIE         | AD1IE             | RCIE                           | TXIE             | SSP1IE          |                          | TMR2IE           | TMR1IE       |

| bit 7           |                   |                                |                  |                 |                          |                  | bit          |

| Lonondi         |                   |                                |                  |                 |                          |                  |              |

| Legend:         | - h:t             |                                | L 14             |                 | we are to all hit are ad | (0)              |              |

| R = Readabl     |                   | W = Writable                   |                  | •               | mented bit, read         |                  |              |

| u = Bit is und  | 0                 | x = Bit is unk                 |                  | -n/n = value    | at POR and BOI           | R/Value at all c | other Resets |

| '1' = Bit is se | et                | '0' = Bit is cle               | ared             |                 |                          |                  |              |

| bit 7           | TMR1GIE: T        | ïmer1 Gate Inte                | errupt Enable    | bit             |                          |                  |              |

|                 | 1 = Enables       | the Timer1 gate                | e acquisition in | nterrupt        |                          |                  |              |

|                 | 0 = Disables      | the Timer1 gat                 | e acquisition i  | nterrupt        |                          |                  |              |

| bit 6           | AD1IE: Anal       | og-to-Digital Co               | onverter (ADC    | 1) Interrupt Er | nable bit                |                  |              |

|                 |                   | the ADC interru                |                  |                 |                          |                  |              |

|                 | 0 = Disables      | the ADC interr                 | upt              |                 |                          |                  |              |

| bit 5           | RCIE: USAR        | RT Receive Inte                | rrupt Enable b   | bit             |                          |                  |              |

|                 |                   | the USART rec                  | •                |                 |                          |                  |              |

|                 |                   | the USART re                   | -                |                 |                          |                  |              |

| bit 4           |                   | T Transmit Inte                | •                |                 |                          |                  |              |

|                 |                   | the USART tra<br>the USART tra | •                |                 |                          |                  |              |

| bit 3           | SSP1IE: Syr       | nchronous Seria                | al Port (MSSP    | ) Interrupt Ena | able bit                 |                  |              |

|                 | 1 = Enables       | the MSSP inter                 | rupt             |                 |                          |                  |              |

|                 | 0 = Disables      | the MSSP inte                  | rrupt            |                 |                          |                  |              |

| bit 2           | Unimpleme         | nted: Read as '                | 0'               |                 |                          |                  |              |

| bit 1           | TMR2IE: TM        | IR2 to PR2 Mat                 | ch Interrupt E   | nable bit       |                          |                  |              |

|                 |                   | the Timer2 to F                |                  |                 |                          |                  |              |

|                 | 0 = Disables      | the Timer2 to I                | PR2 match int    | errupt          |                          |                  |              |

| bit 0           | TMR1IE: Tin       | ner1 Overflow I                | nterrupt Enabl   | le bit          |                          |                  |              |

|                 |                   | the Timer1 ove                 |                  |                 |                          |                  |              |

|                 | 0 = Disables      | the Timer1 ove                 | erflow interrup  | t               |                          |                  |              |

|                 |                   |                                |                  |                 |                          |                  |              |

| Note: B         | it PEIE of the IN | ITCON register                 | must be          |                 |                          |                  |              |

set to enable any peripheral interrupt.

|                |               |                   |               | I I KEQOEO     |                  | -                 |             |

|----------------|---------------|-------------------|---------------|----------------|------------------|-------------------|-------------|

| U-0            | R/W-0/0       | U-0               | U-0           | R/W-0/0        | U-0              | U-0               | U-0         |

|                | AD2IF         | —                 |               | BCLIF          | —                | —                 |             |

| bit 7          |               |                   |               |                |                  |                   | bit 0       |

| Lowende        |               |                   |               |                |                  |                   |             |

| Legend:        |               |                   |               |                |                  |                   |             |

| R = Readab     | ole bit       | W = Writable      | bit           | U = Unimpler   | mented bit, read | as '0'            |             |

| u = Bit is ur  | nchanged      | x = Bit is unkn   | own           | -n/n = Value a | at POR and BOF   | R/Value at all of | ther Resets |

| '1' = Bit is s | et            | '0' = Bit is clea | ared          |                |                  |                   |             |

|                |               |                   |               |                |                  |                   |             |

| bit 7          | Unimpleme     | nted: Read as 'o  | )'            |                |                  |                   |             |

| bit 6          | AD2IF: ADC    | 2 Interrupt Flag  | bit           |                |                  |                   |             |

|                | 1 = Interrupt |                   |               |                |                  |                   |             |

|                | 0 = Interrupt | is not pending    |               |                |                  |                   |             |

| bit 5-4        | Unimpleme     | nted: Read as '   | )'            |                |                  |                   |             |

| bit 3          | BCLIF: MSS    | P Bus Collision   | Interrupt Fla | ıg bit         |                  |                   |             |

|                | 1 = Interrupt | is pending        |               |                |                  |                   |             |

|                | 0 = Interrupt | is not pending    |               |                |                  |                   |             |

| bit 2-0        | Unimpleme     | nted: Read as 'd  | )'            |                |                  |                   |             |

|                |               |                   |               |                |                  |                   |             |

|                |               |                   |               |                |                  |                   |             |

| Note: | Interrupt flag bits are set when an interrupt   |

|-------|-------------------------------------------------|

|       | condition occurs, regardless of the state of    |

|       | its corresponding enable bit or the Global      |

|       | Interrupt Enable bit, GIE of the INTCON         |

|       | register. User software should ensure the       |

|       | appropriate interrupt flag bits are clear prior |

|       | to enabling an interrupt.                       |

### TABLE 7-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS

| Name       | Bit 7   | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2   | Bit 1  | Bit 0  | Register<br>on Page |

|------------|---------|--------|--------|--------|--------|---------|--------|--------|---------------------|

| INTCON     | GIE     | PEIE   | TMR0IE | INTE   | IOCIE  | TMR0IF  | INTF   | IOCIF  | 77                  |

| OPTION_REG | WPUEN   | INTEDG | TMR0CS | TMR0SE | PSA    | PS<2:0> |        |        | 166                 |

| PIE1       | TMR1GIE | AD1IE  | RCIE   | TXIE   | SSP1IE | _       | TMR2IE | TMR1IE | 78                  |

| PIE2       | _       | AD2IE  | _      | _      | BCLIE  | _       | _      | —      | 79                  |

| PIR1       | TMR1GIF | AD1IF  | RCIF   | TXIF   | SSP1IF |         | TMR2IF | TMR1IF | 80                  |

| PIR2       |         | AD2IF  |        |        | BCLIF  |         |        | _      | 81                  |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by interrupts.

### REGISTER 10-3: PMADRL: PROGRAM MEMORY ADDRESS LOW BYTE REGISTER

| R/W-0/0          | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0      |

|------------------|---------|-------------------|---------|----------------|------------------|------------------|--------------|

|                  |         |                   | PMAC    | )R<7:0>        |                  |                  |              |

| bit 7            |         |                   |         |                |                  |                  | bit 0        |

|                  |         |                   |         |                |                  |                  |              |

| Legend:          |         |                   |         |                |                  |                  |              |

| R = Readable     | bit     | W = Writable      | bit     | U = Unimpler   | mented bit, read | l as '0'         |              |

| u = Bit is unch  | anged   | x = Bit is unkr   | nown    | -n/n = Value a | at POR and BO    | R/Value at all c | other Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                  |              |

bit 7-0 **PMADR<7:0>**: Specifies the Least Significant bits for program memory address

### REGISTER 10-4: PMADRH: PROGRAM MEMORY ADDRESS HIGH BYTE REGISTER

| U-1   | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0    | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|---------|---------|---------|------------|---------|---------|---------|

| —     |         |         |         | PMADR<14:8 | >       |         |         |

| bit 7 |         |         |         |            |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7 Unimplemented: Read as '1'

bit 6-0 **PMADR<14:8>**: Specifies the Most Significant bits for program memory address

### 13.3 Register Definitions: FVR Control

| REGISTE                     |                                           | ON: FIXED V                                                                            |                                                 |                                                       |                                                  |          |              |

|-----------------------------|-------------------------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------|-------------------------------------------------------|--------------------------------------------------|----------|--------------|

| R/W-0/0                     | 0 R-q/q                                   | R/W-0/0                                                                                | R/W-0/0                                         | U-0                                                   | U-0                                              | R/W-0/0  | R/W-0/0      |

| FVREN                       | FVRRDY                                    | TSEN                                                                                   | TSRNG                                           |                                                       | —                                                | ADFV     | R<1:0>       |

| bit 7                       |                                           |                                                                                        |                                                 |                                                       |                                                  |          | bit 0        |

| Levende                     |                                           |                                                                                        |                                                 |                                                       |                                                  |          |              |

| <b>Legend:</b><br>R = Reada | able bit                                  | W = Writable                                                                           | hit                                             |                                                       | montod bit road                                  | 1 00 (0) |              |

|                             |                                           |                                                                                        |                                                 |                                                       | mented bit, read<br>at POR and BC                |          | thar Deceta  |

|                             | inchanged                                 | x = Bit is unk                                                                         |                                                 |                                                       |                                                  |          | liner Resels |

| '1' = Bit is                | set                                       | '0' = Bit is cle                                                                       | ared                                            | q = value de                                          | pends on condi                                   | tion     |              |

| bit 7                       | 1 = Fixed Vo                              | ed Voltage Refe<br>oltage Referenc<br>oltage Referenc                                  | e is enabled                                    | bit                                                   |                                                  |          |              |

| bit 6                       | 1 = Fixed Vo                              | xed Voltage Re<br>bltage Referenc<br>bltage Referenc                                   | e output is rea                                 | ady for use                                           | enabled                                          |          |              |

| bit 5                       | 1 = Tempera                               | erature Indicato<br>ature Indicator i<br>ature Indicator i                             | s enabled                                       | )                                                     |                                                  |          |              |

| bit 4                       | 1 = VOUT = '                              | nperature Indica<br>VDD - 4VT (High<br>VDD - 2VT (Low                                  | n Range)                                        | election bit <sup>(1)</sup>                           |                                                  |          |              |

| bit 3-2                     | Unimpleme                                 | nted: Read as '                                                                        | 0'                                              |                                                       |                                                  |          |              |

| bit 1-0                     | 11 = ADC Fi<br>10 = ADC Fi<br>01 = ADC Fi | >: ADC Fixed V<br>xed Voltage Re<br>xed Voltage Re<br>xed Voltage Re<br>xed Voltage Re | ference Perip<br>ference Perip<br>ference Perip | heral output is<br>heral output is<br>heral output is | off<br>2x (2.048V) <sup>(2)</sup><br>1x (1.024V) |          |              |

| Note 1:                     | See Section 14.0                          | "Temperature                                                                           | Indicator Mo                                    | odule" for addi                                       | tional information                               | on.      |              |

| 2:                          | Fixed Voltage Ref                         | ference output of                                                                      | cannot exceed                                   | VDD.                                                  |                                                  |          |              |

|                             |                                           |                                                                                        |                                                 |                                                       |                                                  |          |              |

### REGISTER 13-1: FVRCON: FIXED VOLTAGE REFERENCE CONTROL REGISTER

### TABLE 13-2: SUMMARY OF REGISTERS ASSOCIATED WITH THE FIXED VOLTAGE REFERENCE

| Name   | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Register<br>on page |

|--------|-------|--------|-------|-------|-------|-------|-------|--------|---------------------|

| FVRCON | FVREN | FVRRDY | TSEN  | TSRNG | _     | —     | ADFV  | R<1:0> | 124                 |

Legend: Shaded cells are unused by the Fixed Voltage Reference module.

|                                       |                   |                           |                | <b>OONTINOL</b> |                  |                  |              |

|---------------------------------------|-------------------|---------------------------|----------------|-----------------|------------------|------------------|--------------|

| U-0                                   | R/W-0/0           | R/W-0/0                   | R/W-0/0        | U-0             | U-0              | U-0              | U-0          |

| —                                     |                   | TRIGSEL<2:0>(1            | )              |                 | —                | —                | _            |

| bit 7                                 |                   |                           |                | •               | •                | •                | bit 0        |

|                                       |                   |                           |                |                 |                  |                  |              |

| Legend:                               |                   |                           |                |                 |                  |                  |              |

| R = Readable                          | bit               | W = Writable I            | oit            | U = Unimpler    | mented bit, read | d as '0'         |              |

| u = Bit is uncha                      | anged             | x = Bit is unkn           | own            | -n/n = Value a  | at POR and BC    | R/Value at all o | other Resets |

| '1' = Bit is set '0' = Bit is cleared |                   |                           |                |                 |                  |                  |              |

|                                       |                   |                           |                |                 |                  |                  |              |

| bit 7                                 | Unimpleme         | nted: Read as '           | )'             |                 |                  |                  |              |

| bit 6-4                               | TRIGSEL<2         | ::0>: Auto-Conve          | ersion Trigger | Selection bits  |                  |                  |              |

|                                       | 000 <b>= No A</b> | uto Conversion T          | rigger selecte | ed              |                  |                  |              |

|                                       | 001 = Rese        |                           |                |                 |                  |                  |              |

|                                       | 010 = Rese        |                           |                |                 |                  |                  |              |

|                                       |                   | 0 Overflow <sup>(2)</sup> |                |                 |                  |                  |              |

|                                       |                   | 1 Overflow <sup>(2)</sup> | 2)             |                 |                  |                  |              |

|                                       |                   | 2 Match to PR2            | 2)             |                 |                  |                  |              |

|                                       |                   | RIG Rising Edge           |                |                 |                  |                  |              |

|                                       | 111 = ADTF        | RIG Falling Edge          |                |                 |                  |                  |              |

| bit 3-0                               | Unimpleme         | nted: Read as '           | )'             |                 |                  |                  |              |

| Note 1: See                           | Section 16.       | 1.11 "Hardware            | CVD Registe    | er Mapping" fo  | r more informat  | tion.            |              |

### REGISTER 16-6: AADxCON2: HARDWARE CVD CONTROL REGISTER 2<sup>(1)</sup>

See Section 16.1.11 "Hardware CVD Register Mapping" for more information. 1:

2: Signal used to set the corresponding interrupt flag.

| Name                 | Bit 7    | Bit 6                      | Bit 5      | Bit 4        | Bit 3       | Bit 2       | Bit 1    | Bit 0   | Register<br>on Page |

|----------------------|----------|----------------------------|------------|--------------|-------------|-------------|----------|---------|---------------------|

| AADxCAP              | —        | —                          | _          | —            |             | ADDxCAF     | P<3:0>   | 160     |                     |

| AAD1CON0             | —        | CHS4                       | CHS3       | CHS2         | CHS1        | CHS0        | GO/DONE1 | AD10N   | 150                 |

| AAD2CON0             | —        | CHS4                       | CHS3       | CHS2         | CHS1        | CHS0        | GO/DONE2 | AD2ON   | 151                 |

| AADCON1/<br>ADCOMCON | ADFM     |                            | ADCS<2:0>  | •            | _           | GO/DONE_ALL | ADPRE    | F<1:0>  | 154                 |

| AADxCON2             | —        | Т                          | RIGSEL<2:0 | >            | _           | _           | —        | _       | 155                 |

| AADxCON3             | ADxEPPOL | ADxIPPOL                   | _          | _            | _           | _           | ADxIPEN  | ADxDSEN | 156                 |

| AADxGRD              | GRDxBOE  | GRDxAOE                    | GRDxPOL    | _            | _           | _           | —        | _       | 159                 |

| AADxPRE              | —        |                            |            |              | ADxPRE<6    | :0>         |          |         | 158                 |

| AADxRES0H            |          |                            | /          | ADC Result 0 | Register Hi | igh         |          |         | 161                 |

| AADxRES0L            |          | ADC Result 0 Register Low  |            |              |             |             |          |         | 161                 |

| AADxRES1H            |          | ADC Result 1 Register High |            |              |             |             |          |         | 162                 |

| AADxRES1L            |          |                            |            | ADC Result 1 | Register Lo | w           |          |         | 162                 |

| AADSTAT              | —        | AD2CONV                    | AD2ST      | G<1:0>       | _           | AD1CONV     | AD1ST    | G<1:0>  | 157                 |

| AADxACQ              | —        |                            |            | ŀ            | ADxACQ<6    | 6:0>        |          |         | 158                 |

| ANSELA               | —        | —                          | ANSA5      | ANSA4        | _           | ANSA2       | ANSA1    | ANSA0   | 109                 |

| ANSELB               | ANSB7    | ANSB6                      | ANSB5      | ANSB4        | _           | _           | —        | _       | 113                 |

| ANSELC               | ANSC7    | ANSC6                      | ANSC5      | ANSC4        | ANSC3       | ANSC2       | ANSC1    | ANSC0   | 117                 |

| FVRCON               | FVREN    | FVRRDY                     | TSEN       | TSRNG        | _           | _           | ADFVI    | R<1:0>  | 124                 |

| INTCON               | GIE      | PEIE                       | TMR0IE     | INTE         | IOCIE       | TMR0IF      | INTF     | IOCIF   | 77                  |

| PIE1                 | TMR1GIE  | AD1IE                      | RCIE       | TXIE         | SSP1IE      | —           | TMR2IE   | TMR1IE  | 78                  |

| PIE2                 | —        | AD2IE                      | _          | _            | BCLIE       | —           | —        | —       | 79                  |

| PIR1                 | TMR1GIF  | AD1IF                      | RCIF       | TXIF         | SSP1IF      |             | TMR2IF   | TMR1IF  | 80                  |

| PIR2                 | —        | AD2IF                      | _          | _            | BCLIF       | _           | _        | _       | 81                  |

| TRISA                | —        | —                          | TRISA5     | TRISA4       | _(1)        | TRISA2      | TRISA1   | TRISA0  | 108                 |

| TRISB                | TRISB7   | TRISB6                     | TRISB5     | TRISB4       | _           | _           | —        | —       | 112                 |

| TRISC                | TRISC7   | TRISC6                     | TRISC5     | TRISC4       | TRISC3      | TRISC2      | TRISC1   | TRISC0  | 116                 |

| TABLE 16-2: | SUMMARY OF REGISTERS ASSOCIATED WITH HARDWARE CVD |

|-------------|---------------------------------------------------|

|-------------|---------------------------------------------------|

Legend: — = unimplemented read as '0'. Shaded cells are not used for hardware CVD module.

**Note 1:** Unimplemented, read as '1'.

| FIGURE 18-6: TIMER1 G | ATE SINGLE-PULSE AND TOGGLE COMBINED MODE                         |               |

|-----------------------|-------------------------------------------------------------------|---------------|

| TMR1GE                |                                                                   |               |

| T1GPOL                |                                                                   |               |

| T1GSPM                |                                                                   |               |

| T1GTM                 | Cleared by hardv                                                  | vare on       |

| DONE Cour             | et by software falling edge of T1                                 | GVAL          |

| t1g_in                | ing edge of T1G                                                   |               |

| т1СКІ                 |                                                                   |               |

| T1GV <u>AL</u>        |                                                                   |               |

| Timer1 N              | <u>N+1</u> <u>N+2</u> <u>N+3</u> <u>N+4</u>                       |               |

| TMR1GIF Cleared by    | Set by hardware on Clear<br>software falling edge of T1GVAL Clear | ed by<br>vare |

© 2014-2016 Microchip Technology Inc.

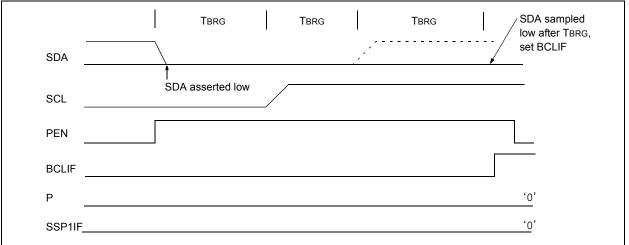

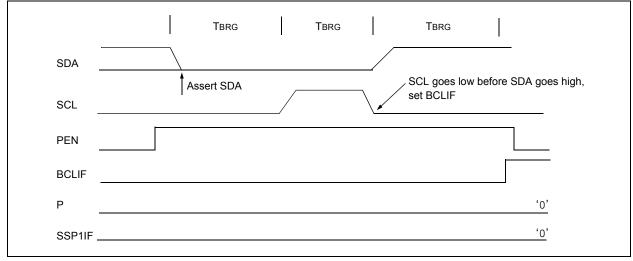

### 20.6.13.3 Bus Collision During a Stop Condition

Bus collision occurs during a Stop condition if:

- a) After the SDA pin has been deasserted and allowed to float high, SDA is sampled low after the BRG has timed out (Case 1).

- b) After the SCL pin is deasserted, SCL is sampled low before SDA goes high (Case 2).

The Stop condition begins with SDA asserted low. When SDA is sampled low, the SCL pin is allowed to float. When the pin is sampled high (clock arbitration), the Baud Rate Generator is loaded with SSPADD and counts down to 0. After the BRG times out, SDA is sampled. If SDA is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0' (Figure 20-38). If the SCL pin is sampled low before SDA is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 20-39).

### FIGURE 20-38: BUS COLLISION DURING A STOP CONDITION (CASE 1)

### FIGURE 20-39: BUS COLLISION DURING A STOP CONDITION (CASE 2)

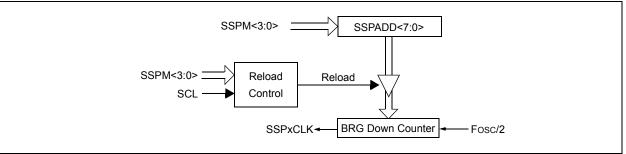

### 20.7 BAUD RATE GENERATOR

The MSSP module has a Baud Rate Generator available for clock generation in both  $I^2C$  and SPI Master modes. The Baud Rate Generator (BRG) reload value is placed in the SSPADD register (Register 20-6). When a write occurs to SSPBUF, the Baud Rate Generator will automatically begin counting down.

Once the given operation is complete, the internal clock will automatically stop counting and the clock pin will remain in its last state.

An internal signal "Reload" in Figure 20-40 triggers the value from SSPADD to be loaded into the BRG counter. This occurs twice for each oscillation of the module clock line. The logic dictating when the reload signal is asserted depends on the mode the MSSP is being operated in.

Table 20-4 demonstrates clock rates based on instruction cycles and the BRG value loaded into SSPADD.

#### EQUATION 20-1:

$$FCLOCK = \frac{FOSC}{(SSPxADD + 1)(4)}$$

### FIGURE 20-40: BAUD RATE GENERATOR BLOCK DIAGRAM

**Note:** Values of 0x00, 0x01 and 0x02 are not valid for SSPADD when used as a Baud Rate Generator for I<sup>2</sup>C. This is an implementation limitation.

### TABLE 20-4: MSSP CLOCK RATE W/BRG

| Fosc   | Fcy   | BRG Value | FcLock<br>(2 Rollovers of BRG) |

|--------|-------|-----------|--------------------------------|

| 32 MHz | 8 MHz | 13h       | 400 kHz <sup>(1)</sup>         |

| 32 MHz | 8 MHz | 19h       | 308 kHz                        |

| 32 MHz | 8 MHz | 4Fh       | 100 kHz                        |

| 16 MHz | 4 MHz | 09h       | 400 kHz <sup>(1)</sup>         |

| 16 MHz | 4 MHz | 0Ch       | 308 kHz                        |

| 16 MHz | 4 MHz | 27h       | 100 kHz                        |

| 4 MHz  | 1 MHz | 09h       | 100 kHz                        |

**Note 1:** Refer to the I/O port electrical and timing specifications in Table 25-9 and Figure 25-5 to ensure the system is designed to support the I/O timing requirements.

### 20.7.1 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function register, APFCON. To determine which pins can be moved and what their default locations are upon a Reset, see **Section 11.1 "Alternate Pin Function"** for more information.

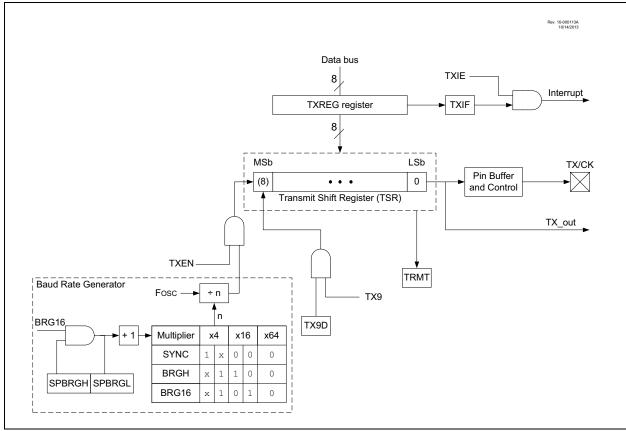

### 21.0 ENHANCED UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (EUSART)

The Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) module is a serial I/O communications peripheral. It contains all the clock generators, shift registers and data buffers necessary to perform an input or output serial data transfer independent of device program execution. The EUSART, also known as a Serial Communications Interface (SCI), can be configured as a full-duplex asynchronous system or half-duplex synchronous system. Full-Duplex mode is useful for communications with peripheral systems, such as CRT terminals and personal computers. Half-Duplex Synchronous mode is intended for communications with peripheral devices, such as ADC or DAC integrated circuits, serial EEPROMs or other microcontrollers. These devices typically do not have internal clocks for baud rate generation and require the external clock signal provided by a master synchronous device.

The EUSART module includes the following capabilities:

- · Full-duplex asynchronous transmit and receive

- · Two-character input buffer

- · One-character output buffer

- · Programmable 8-bit or 9-bit character length

- · Address detection in 9-bit mode

- · Input buffer overrun error detection

- · Received character framing error detection

- Half-duplex synchronous master

- · Half-duplex synchronous slave

- Programmable clock polarity in synchronous modes

- · Sleep operation

The EUSART module implements the following additional features, making it ideally suited for use in Local Interconnect Network (LIN) bus systems:

- · Automatic detection and calibration of the baud rate

- · Wake-up on Break reception

- 13-bit Break character transmit

Block diagrams of the EUSART transmitter and receiver are shown in Figure 21-1 and Figure 21-2.

The EUSART transmit output (TX\_out) is available to the TX/CK pin and internally to the following peripherals:

Configurable Logic Cell (CLC)

### FIGURE 21-1: EUSART TRANSMIT BLOCK DIAGRAM

### TABLE 25-18: I<sup>2</sup>C BUS DATA REQUIREMENTS

| Standard      | operating | ,                    |              | -,         |      |       | 1                                             |

|---------------|-----------|----------------------|--------------|------------|------|-------|-----------------------------------------------|

| Param.<br>No. | Symbol    | Charact              | eristic      | Min.       | Max. | Units | Conditions                                    |

| SP100*        | Тнідн     | Clock high time      | 100 kHz mode | 4.0        |      | μS    | Device must operate at a minimum of 1.5 MHz   |

|               |           |                      | 400 kHz mode | 0.6        |      | μS    | Device must operate at a<br>minimum of 10 MHz |

|               |           |                      | SSP module   | 1.5TCY     | _    |       |                                               |

| SP101*        | TLOW      | Clock low time       | 100 kHz mode | 4.7        | _    | μS    | Device must operate at a minimum of 1.5 MHz   |

|               |           |                      | 400 kHz mode | 1.3        | _    | μS    | Device must operate at a minimum of 10 MHz    |

|               |           |                      | SSP module   | 1.5TCY     | _    |       |                                               |

| SP102*        | TR        | SDA and SCL rise     | 100 kHz mode | —          | 1000 | ns    |                                               |

|               |           | time                 | 400 kHz mode | 20 + 0.1Св | 300  | ns    | CB is specified to be from 10-400 pF          |

| SP103*        | TF        | SDA and SCL fall     | 100 kHz mode | —          | 250  | ns    |                                               |

|               |           | time                 | 400 kHz mode | 20 + 0.1Св | 250  | ns    | CB is specified to be from 10-400 pF          |

| SP106*        | THD:DAT   | Data input hold      | 100 kHz mode | 0          |      | ns    |                                               |

|               |           | time                 | 400 kHz mode | 0          | 0.9  | μS    |                                               |

| SP107*        | TSU:DAT   | Data input setup     | 100 kHz mode | 250        |      | ns    | (Note 2)                                      |

|               |           | time                 | 400 kHz mode | 100        |      | ns    |                                               |

| SP109*        | ΤΑΑ       | Output valid from    | 100 kHz mode | _          | 3500 | ns    | (Note 1)                                      |

|               |           | clock                | 400 kHz mode | —          | _    | ns    |                                               |

| SP110*        | TBUF      | Bus free time        | 100 kHz mode | 4.7        |      | μS    | Time the bus must be free                     |

|               |           |                      | 400 kHz mode | 1.3        | _    | μS    | before a new transmis-<br>sion can start      |

| SP111         | Св        | Bus capacitive loadi | ng           | _          | 400  | pF    |                                               |

\* These parameters are characterized but not tested.

**Note 1:** As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of Start or Stop conditions.

2: A Fast mode (400 kHz) I<sup>2</sup>C bus device can be used in a Standard mode (100 kHz) I<sup>2</sup>C bus system, but the requirement TsU:DAT ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the low period of the SCL signal. If such a device does stretch the low period of the SCL signal, it must output the next data bit to the SDA line TR max. + TSU:DAT = 1000 + 250 = 1250 ns (according to the Standard mode I<sup>2</sup>C bus specification), before the SCL line is released.

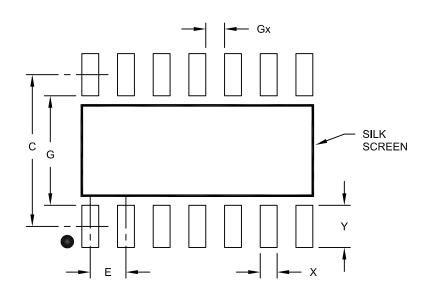

14-Lead Plastic Small Outline (SL) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

### RECOMMENDED LAND PATTERN

|                       | Units  | MILLIMETERS |      |      |  |

|-----------------------|--------|-------------|------|------|--|

| Dimension             | Limits | MIN         | NOM  | MAX  |  |

| Contact Pitch         | E      | 1.27 BSC    |      |      |  |

| Contact Pad Spacing   | С      |             | 5.40 |      |  |

| Contact Pad Width     | X      |             |      | 0.60 |  |

| Contact Pad Length    | Y      |             |      | 1.50 |  |

| Distance Between Pads | Gx     | 0.67        |      |      |  |

| Distance Between Pads | G      | 3.90        |      |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2065A

### 20-Lead Ultra Thin Plastic Quad Flat, No Lead Package (GZ) - 4x4x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | Units |           | MILLIMETERS |      |  |

|-------------------------|-------|-----------|-------------|------|--|

| Dimension Limits        |       | MIN       | NOM         | MAX  |  |

| Number of Terminals     | N     | 20        |             |      |  |

| Pitch                   | е     | 0.50 BSC  |             |      |  |

| Overall Height          | Α     | 0.45      | 0.50        | 0.55 |  |

| Standoff                | A1    | 0.00      | 0.02        | 0.05 |  |

| Terminal Thickness      | A3    | 0.127 REF |             |      |  |

| Overall Width           | E     | 4.00 BSC  |             |      |  |

| Exposed Pad Width       | E2    | 2.60      | 2.70        | 2.80 |  |

| Overall Length          | D     | 4.00 BSC  |             |      |  |

| Exposed Pad Length      | D2    | 2.60      | 2.70        | 2.80 |  |

| Terminal Width          | b     | 0.20      | 0.25        | 0.30 |  |

| Terminal Length         | L     | 0.30      | 0.40        | 0.50 |  |

| Terminal-to-Exposed-Pad | K     | 0.20      | -           | -    |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated

3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-255A Sheet 2 of 2